# POWER

# ONTROL

**MPC500 Family**

MPC509 User's Manual

| Paragraph<br>Number | TABLE OF CONTENTS                           | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| Hambo.              | PREFACE                                     |                |

|                     | Section 1 INTRODUCTION                      |                |

| 1.1 Features.       |                                             | 1-1            |

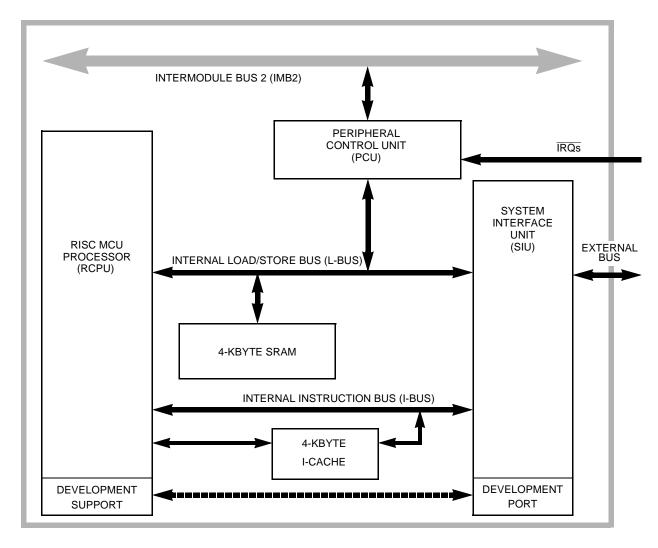

| 1.2 Block Diag      | gram                                        | 1-2            |

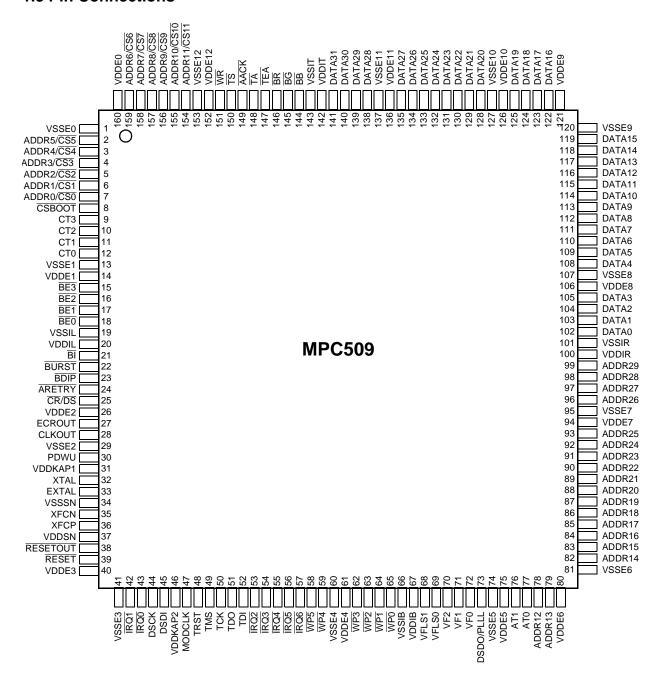

| 1.3 Pin Conne       | ections                                     | 1-3            |

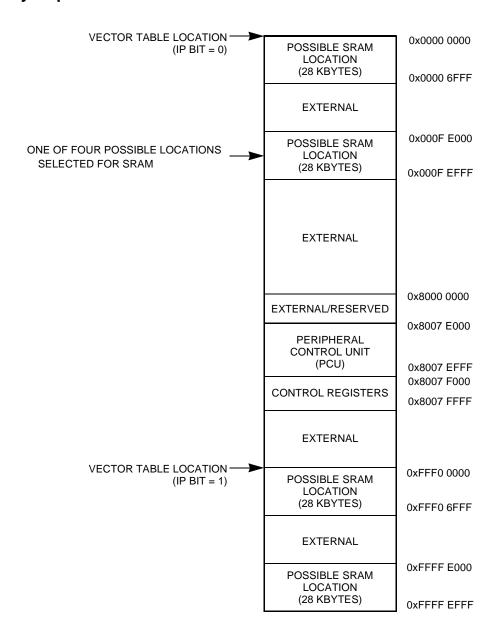

| 1.4 Memory M        | 1ар                                         | 1-5            |

|                     | Section 2 SIGNAL DESCRIPTIONS               |                |

| 2.1 Pin List        |                                             | 2-1            |

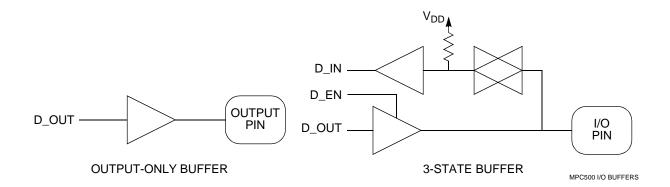

|                     | cteristics                                  |                |

| 2.3 Power Co        | nnections                                   | 2-3            |

|                     | nternal Pull-Ups and Pulldowns              |                |

|                     | scriptions                                  |                |

| 2.5.1 Bus           | Arbitration and Reservation Support Signals | 2-6            |

|                     | Bus Request (BR)                            |                |

|                     | Bus Grant (BG)                              |                |

| 2.5.1.3             | Bus Busy (BB)                               | 2-8            |

| 2.5.1.4             | Cancel Reservation (CR)                     | 2-8            |

| 2.5.2 Add           | ress Phase Signals                          | 2-8            |

| 2.5.2.1             | Address Bus (ADDR[0:29])                    | 2-9            |

| 2.5.2.2             | Write/Read (WR)                             | 2-9            |

| 2.5.2.3             | Burst Indicator (BURST)                     | 2-9            |

| 2.5.2.4             | Byte Enables (BE[0:3])                      | 2-10           |

| 2.5.2.5             | Transfer Start (TS)                         | 2-10           |

| 2.5.2.6             | Address Acknowledge (AACK)                  | 2-10           |

|                     | Burst Inhibit (BI)                          |                |

| 2.5.2.8             | Address Retry (ARETRY)                      | 2-12           |

| 2.5.2.9             | Address Type (AT[0:1])                      | 2-12           |

| 2.5.2.10            | 0 Cycle Types (CT[0:3])                     | 2-13           |

| 2.5.3 Data          | a Phase Signals                             | 2-13           |

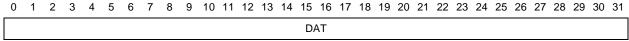

| 2.5.3.1             | Data Bus (DATA[0:31])                       | 2-13           |

| 2.5.3.2             | Burst Data in Progress (BDIP)               | 2-14           |

|                     | Transfer Acknowledge (TA)                   |                |

| 2.5.3.4             | Transfer Error Acknowledge (TEA)            | 2-15           |

|                     | Data Strobe (DS)                            |                |

|                     | elopment Support Signals                    |                |

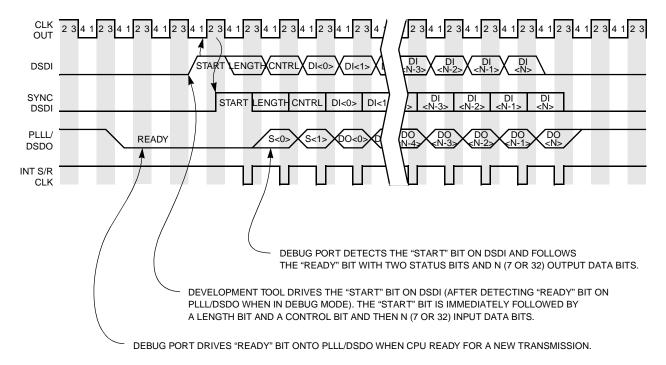

|                     | Development Port Serial Data Out (DSDO)     |                |

| 2.5.4.2             | Development Port Serial Data In (DSDI)      | 2-16           |

| Paragraph     |                                                          | Page   |

|---------------|----------------------------------------------------------|--------|

| Number        |                                                          | Number |

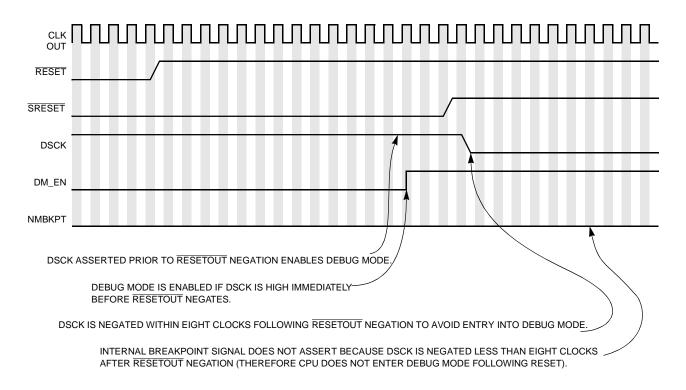

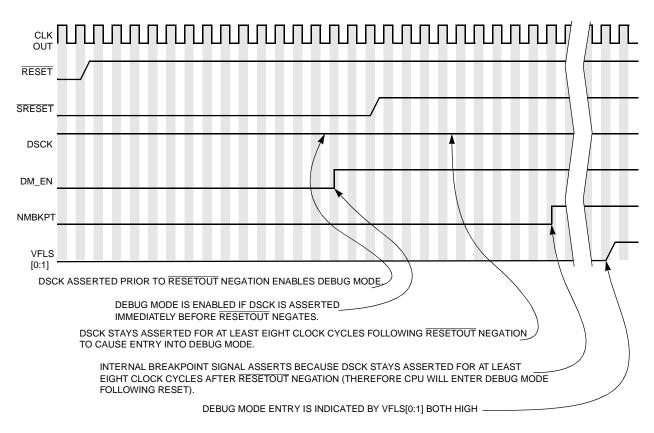

| 2.5.4.3       | Development Port Serial Clock Input (DSCK)               | 2-16   |

| 2.5.4.4       | nstruction Fetch Visibility Signals (VF[0:2])            | 2-17   |

| 2.5.4.5 I     | nstruction Flush Count (VFLS[0:1])                       | 2-17   |

| 2.5.4.6 V     | Watchpoints (WP[0:5])                                    | 2-17   |

| 2.5.5 Chip-9  | Select Signals                                           | 2-17   |

| 2.5.5.1 (     | Chip Select for System Boot Memory (CSBOOT)              | 2-17   |

| 2.5.5.2 (     | Chip Selects for External Memory (CS[0:11])              | 2-18   |

| 2.5.6 Clock   | Signals                                                  | 2-18   |

| 2.5.6.1 (     | Clock Output (CLKOUT)                                    | 2-18   |

| 2.5.6.2 E     | Engineering Clock Output (ECROUT)                        | 2-19   |

| 2.5.6.3       | Crystal Oscillator Connections (EXTAL, XTAL)             | 2-19   |

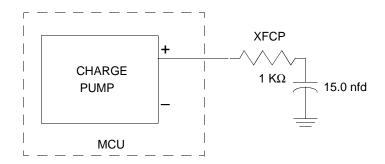

| 2.5.6.4 E     | External Filter Capacitor Pins (XFCP, XFCN)              | 2-19   |

| 2.5.6.5       | Clock Mode (MODCLK)                                      | 2-19   |

| 2.5.6.6 F     | Phase-Locked Loop Lock Signal (PLLL)                     | 2-19   |

| 2.5.6.7 F     | Power-Down Wake-Up (PDWU)                                | 2-19   |

| 2.5.7 Reset   | t Signals                                                | 2-20   |

| 2.5.7.1 F     | Reset (RESET)                                            | 2-20   |

| 2.5.7.2 F     | Reset Output (RESETOUT)                                  | 2-20   |

| 2.5.8 SIU G   | General-Purpose Input/Output Signals                     | 2-20   |

| 2.5.8.1 F     | Ports A and B (PA[0:7], PB[0:7])                         | 2-20   |

| 2.5.8.2 F     | Ports I, J, K, and L (PI[0:7], PJ[0:7], PK[0:7], PL[2:7] | 2-21   |

| 2.5.8.3 F     | Port M (PM[3:7])                                         | 2-21   |

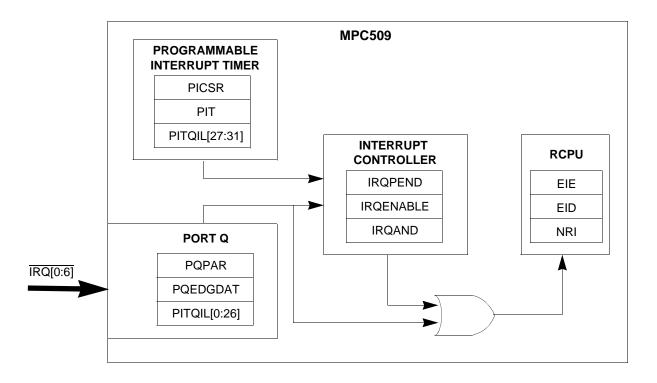

| 2.5.9 Interru | upts and Port Q Signals                                  | 2-21   |

| 2.5.9.1 l     | nterrupt Requests (IRQ[0:6])                             | 2-21   |

| 2.5.9.2 F     | Port Q (PQ[0:6])                                         | 2-22   |

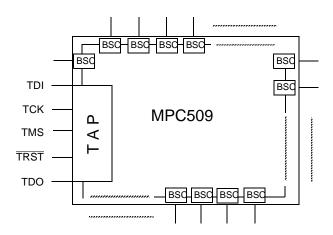

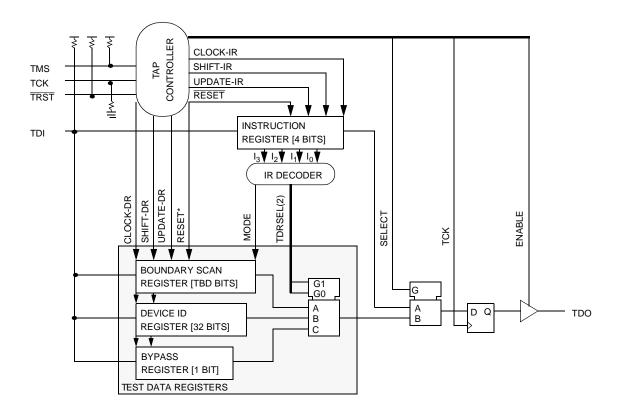

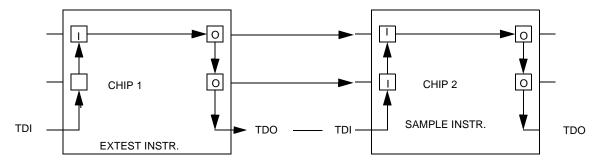

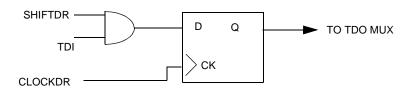

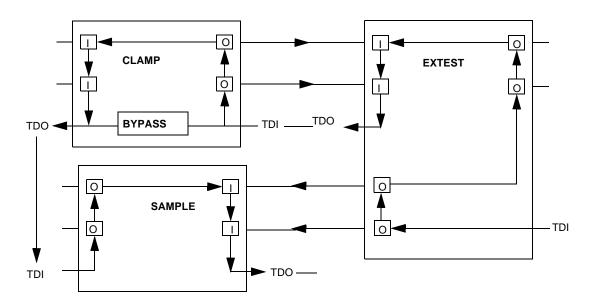

| 2.5.10 JTA    | G Interface Signals                                      | 2-22   |

| 2.5.10.1      | Test Data Input (TDI)                                    | 2-22   |

| 2.5.10.2      | Test Data Output (TDO)                                   | 2-22   |

| 2.5.10.3      | Test Mode Select (TMS)                                   | 2-22   |

| 2.5.10.4      | Test Clock (TCK)                                         | 2-22   |

| 2.5.10.5      | Test Reset (TRST)                                        | 2-23   |

|               | Section 3                                                |        |

|               | CENTRAL PROCESSING UNI                                   | Т      |

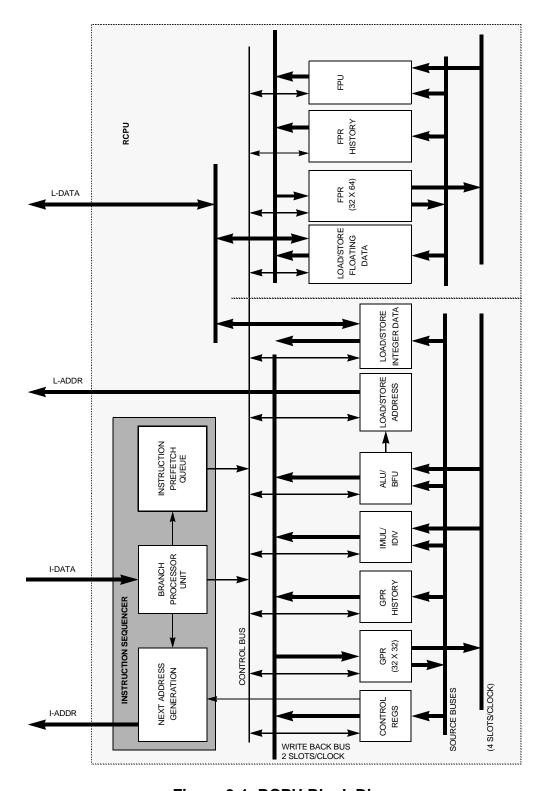

| 3.1 RCPU Feat | ures                                                     |        |

|               | k Diagram                                                |        |

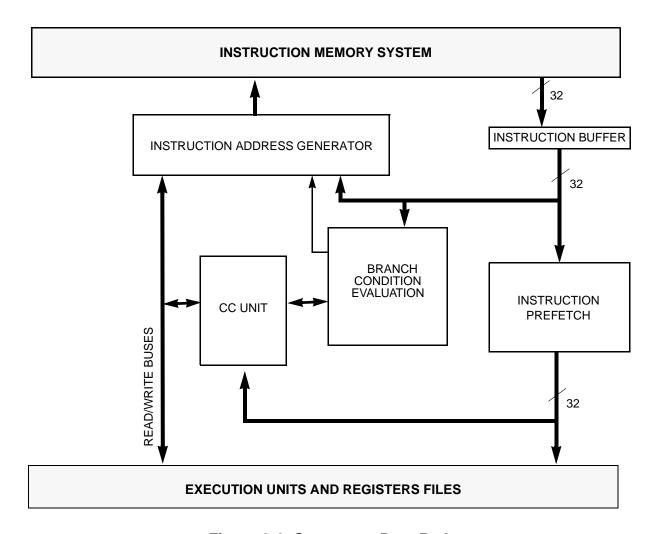

|               | Sequencer                                                |        |

|               | t Execution Units                                        |        |

| •             | ch Processing Unit (BPU)                                 |        |

|               | er Unit (IU)                                             |        |

|               | Store Unit (LSU)                                         |        |

|               | ng-Point Unit (FPU)                                      |        |

|               | e PowerPC Architecture                                   |        |

| Paragraph                                                          | Page   |

|--------------------------------------------------------------------|--------|

| Number                                                             | Number |

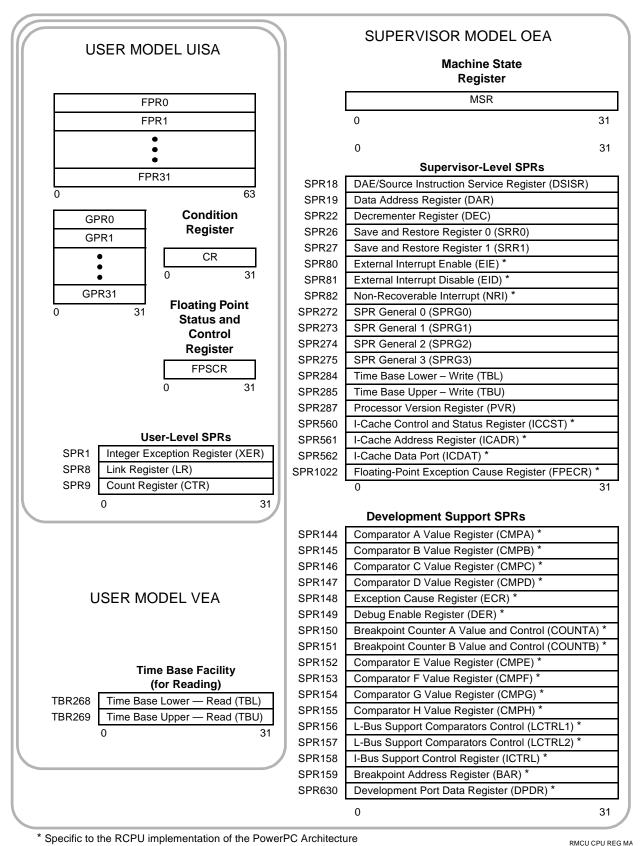

| 3.6 RCPU Programming Model                                         | 3-7    |

| 3.7 PowerPC UISA Register Set                                      | 3-10   |

| 3.7.1 General-Purpose Registers (GPRs)                             | 3-10   |

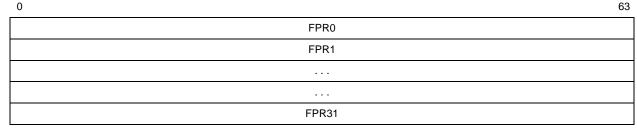

| 3.7.2 Floating-Point Registers (FPRs)                              | 3-10   |

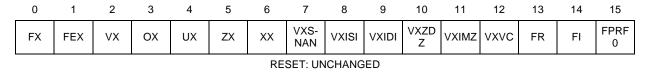

| 3.7.3 Floating-Point Status and Control Register (FPSCR)           | 3-11   |

| 3.7.4 Condition Register (CR)                                      | 3-13   |

| 3.7.4.1 Condition Register CR0 Field Definition                    | 3-14   |

| 3.7.4.2 Condition Register CR1 Field Definition                    | 3-14   |

| 3.7.4.3 Condition Register CR <i>n</i> Field — Compare Instruction | 3-15   |

| 3.7.5 Integer Exception Register (XER)                             | 3-15   |

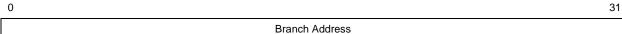

| 3.7.6 Link Register (LR)                                           | 3-16   |

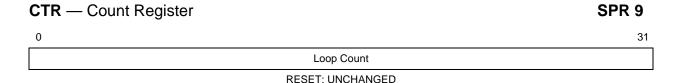

| 3.7.7 Count Register (CTR)                                         | 3-17   |

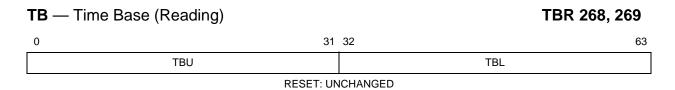

| 3.8 PowerPC VEA Register Set — Time Base                           | 3-17   |

| 3.9 PowerPC OEA Register Set                                       | 3-18   |

| 3.9.1 Machine State Register (MSR)                                 | 3-18   |

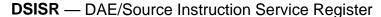

| 3.9.2 DAE/Source Instruction Service Register (DSISR)              | 3-19   |

| 3.9.3 Data Address Register (DAR)                                  | 3-20   |

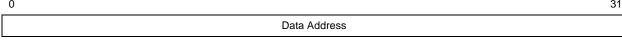

| 3.9.4 Time Base Facility (TB) — OEA                                | 3-20   |

| 3.9.5 Decrementer Register (DEC)                                   | 3-20   |

| 3.9.6 Machine Status Save/Restore Register 0 (SRR0)                | 3-21   |

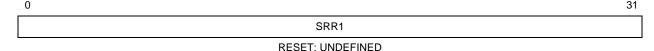

| 3.9.7 Machine Status Save/Restore Register 1 (SRR1)                | 3-22   |

| 3.9.8 General SPRs (SPRG0–SPRG3)                                   | 3-22   |

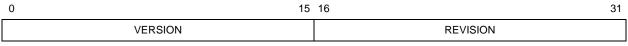

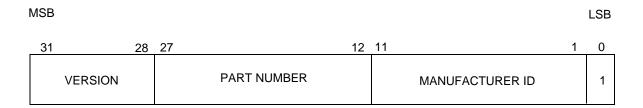

| 3.9.9 Processor Version Register (PVR)                             | 3-22   |

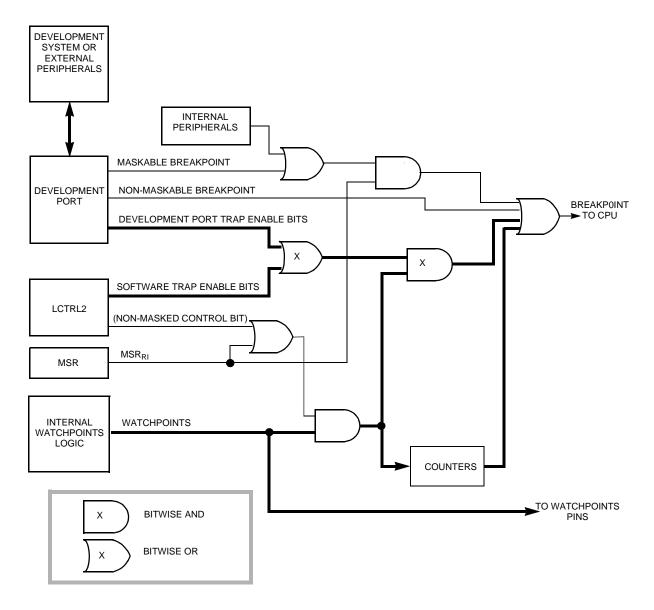

| 3.9.10 Implementation-Specific SPRs                                | 3-23   |

| 3.9.10.1 EIE, EID, and NRI Special-Purpose Registers               |        |

| 3.9.10.2 Instruction-Cache Control Registers                       |        |

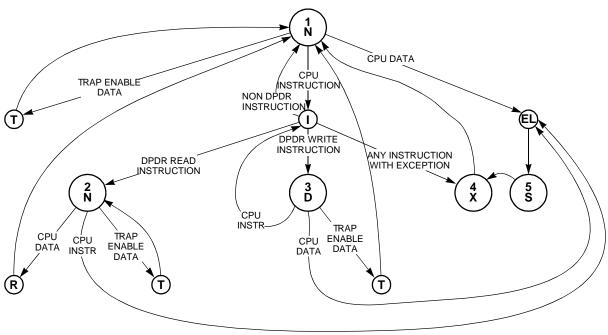

| 3.9.10.3 Development Support Registers                             |        |

| 3.9.10.4 Floating-Point Exception Cause Register (FPECR)           |        |

| 3.10 Instruction Set                                               |        |

| 3.10.1 Instruction Set Summary                                     |        |

| 3.10.2 Recommended Simplified Mnemonics                            |        |

| 3.10.3 Calculating Effective Addresses                             |        |

| 3.11 Exception Model                                               |        |

| 3.11.1 Exception Classes                                           |        |

| 3.11.2 Ordered Exceptions                                          |        |

| 3.11.3 Unordered Exceptions                                        |        |

| 3.11.4 Precise Exceptions                                          |        |

| 3.11.5 Exception Vector Table                                      |        |

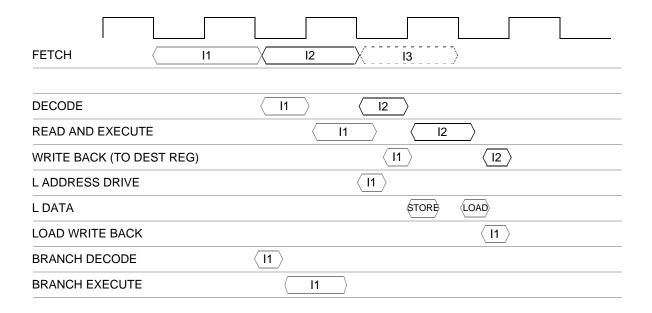

| 3.12 Instruction Timing.                                           | 3-33   |

| Parag | raph Page                                                                |

|-------|--------------------------------------------------------------------------|

| Nun   |                                                                          |

|       | Section 4                                                                |

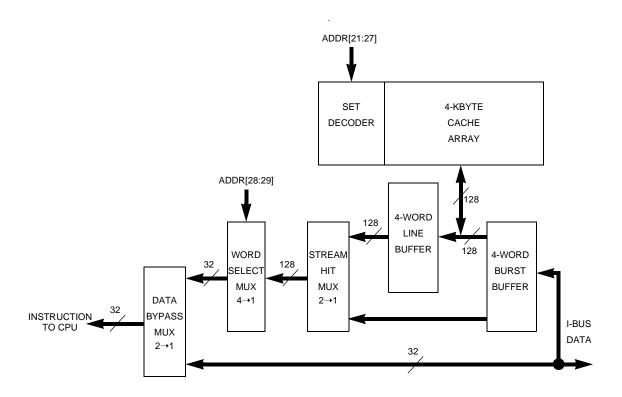

|       | INSTRUCTION CACHE                                                        |

| 4.1   | Instruction Cache Features                                               |

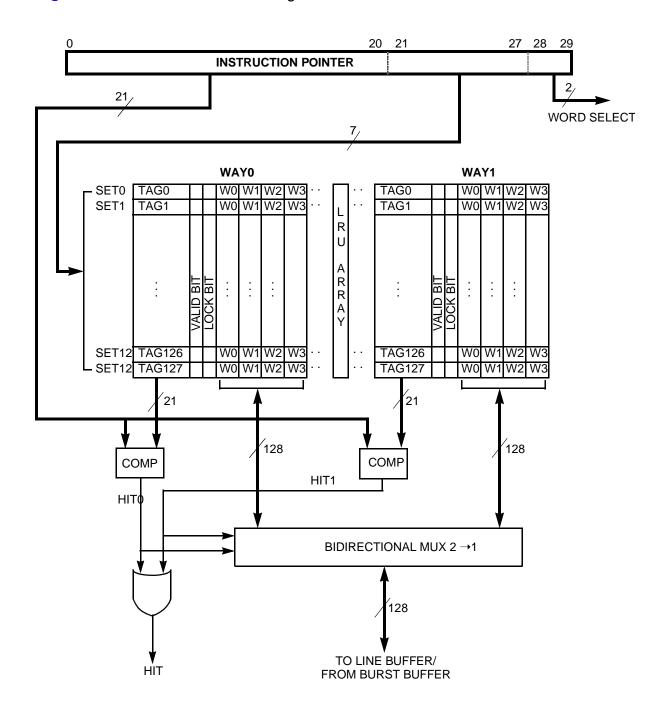

|       | Instruction Cache Organization                                           |

|       | Instruction Cache Programming Model                                      |

|       | Cache Operation                                                          |

| 4.5   | Cache Commands                                                           |

|       | Section 5                                                                |

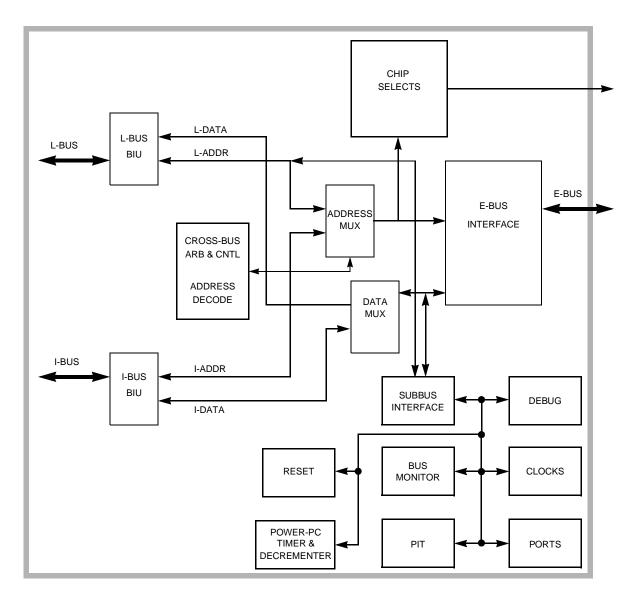

|       | SYSTEM INTERFACE UNIT                                                    |

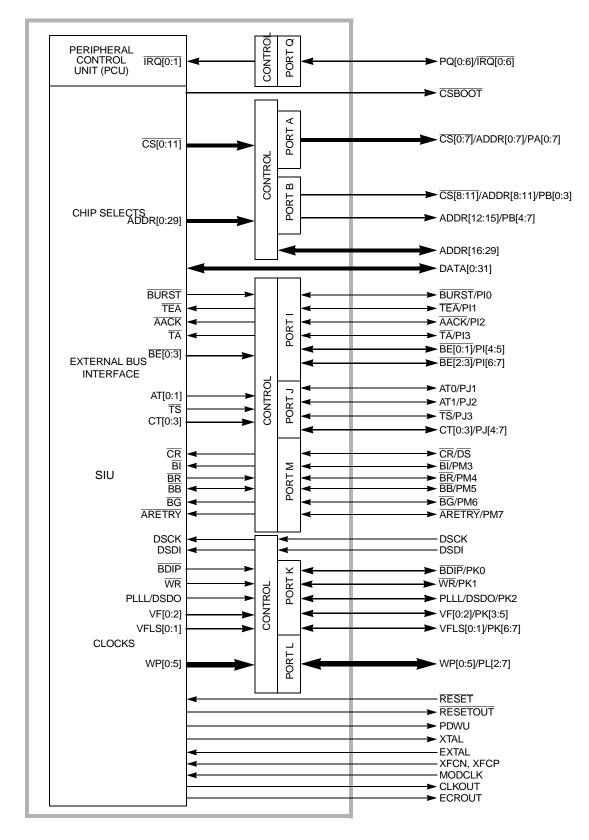

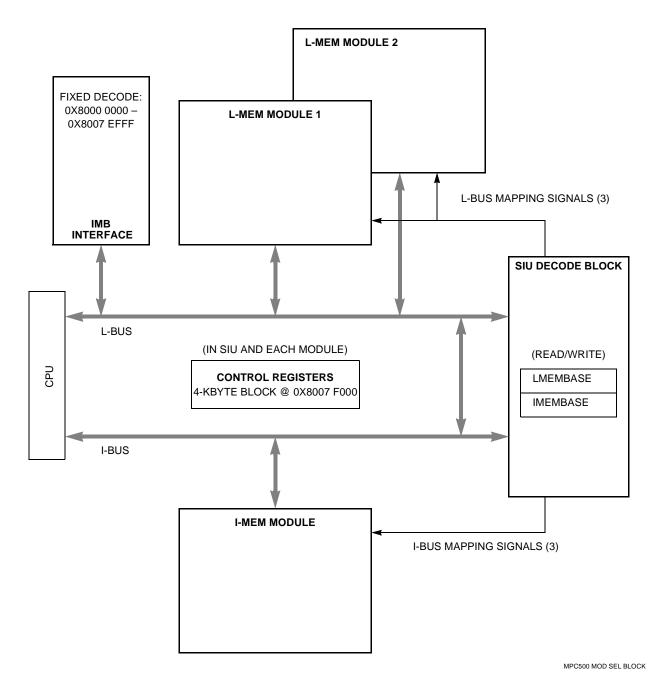

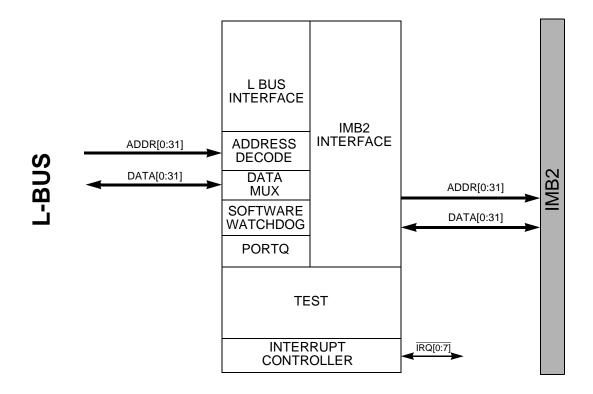

| 5.1   | SIU Block Diagram                                                        |

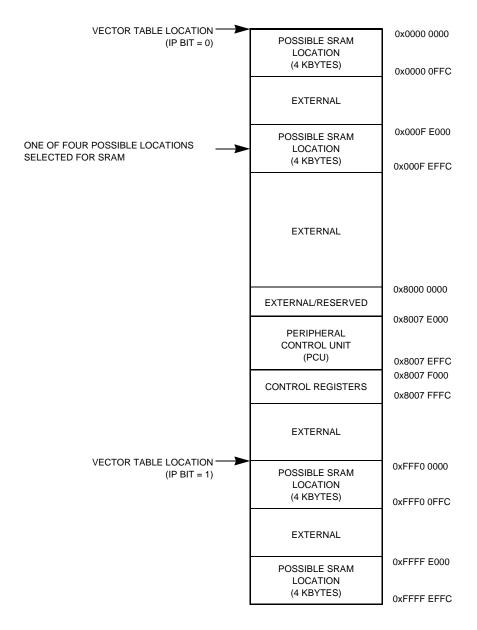

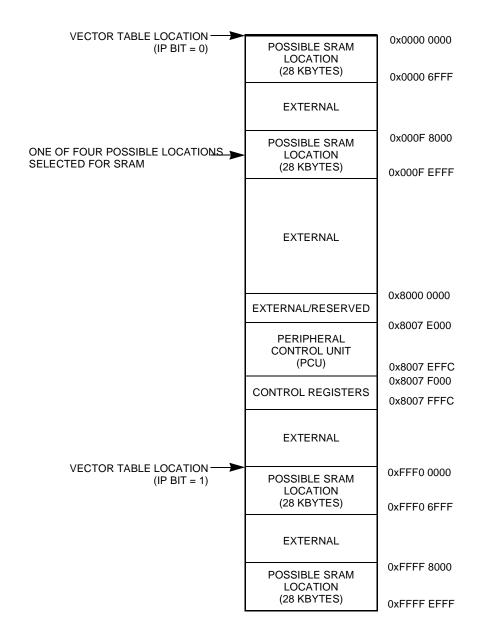

|       | SIU Address Map                                                          |

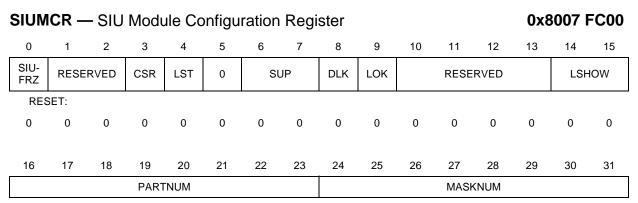

|       | SIU Module Configuration                                                 |

|       | 5.3.1 SIU Module Configuration Register                                  |

|       | 5.3.2 Memory Mapping Register                                            |

|       | 5.3.3 Internal Module Select Logic                                       |

|       | 5.3.3.1 Memory Block Mapping                                             |

|       | 5.3.3.2 Accesses to Unimplemented Internal Memory Locations 5-9          |

|       | 5.3.3.3 Control Register Block                                           |

|       | 5.3.3.4 Internal Memory Mapping Field (LMEMBASE)                         |

|       | 5.3.3.5 Memory Mapping Conflicts                                         |

|       | 5.3.4 Internal Cross-Bus Accesses                                        |

|       | 5.3.5 Response to Freeze Assertion                                       |

|       | 5.3.5.1 Effects of Freeze and Debug Mode on the Bus Monitor 5-11         |

|       | 5.3.5.2 Effects of Freeze on the Programmable Interrupt Timer (PIT) 5-11 |

|       | 5.3.5.3 Effects of Freeze on the Decrementer                             |

|       | 5.3.5.4 Effects of Freeze on Register Lock Bits                          |

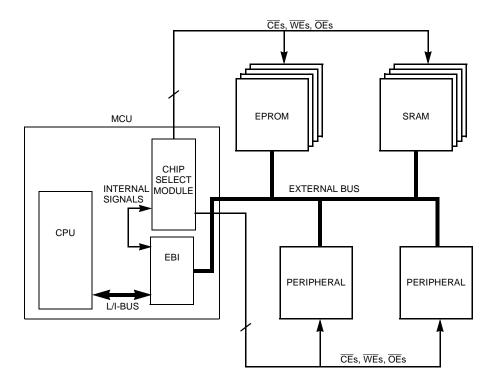

| 5.4   | External Bus Interface                                                   |

|       | 5.4.1 Features                                                           |

|       | 5.4.2 External Bus Signals                                               |

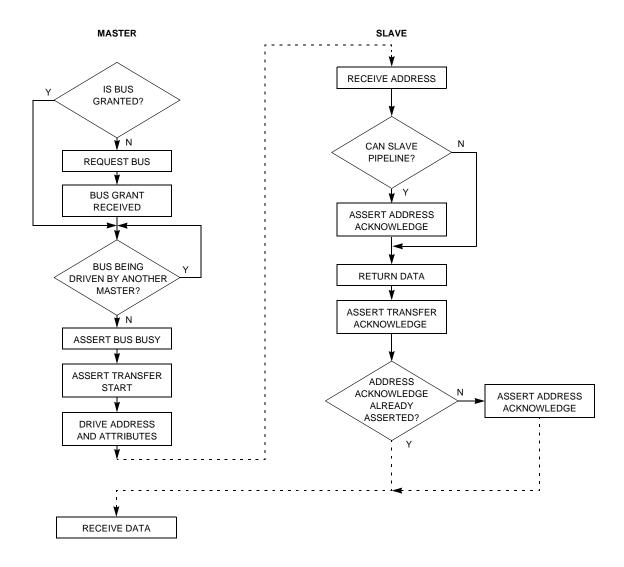

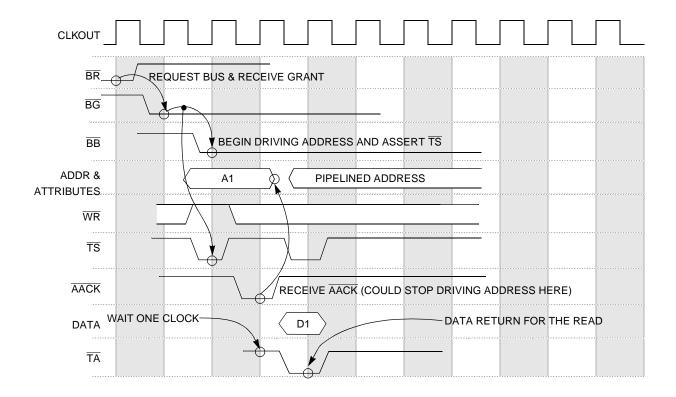

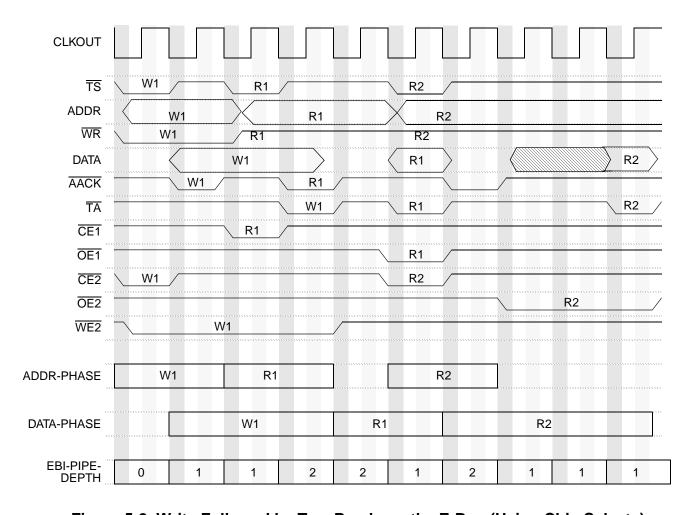

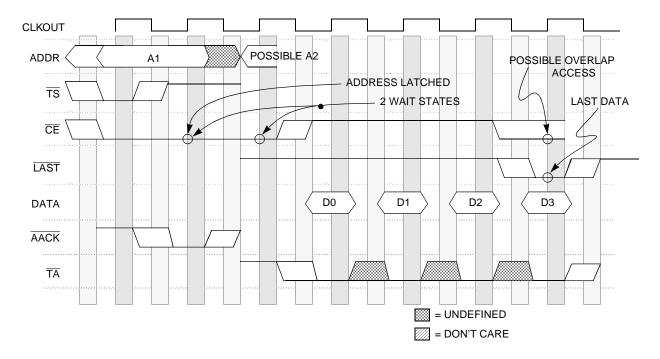

|       | 5.4.3 Basic Bus Cycle                                                    |

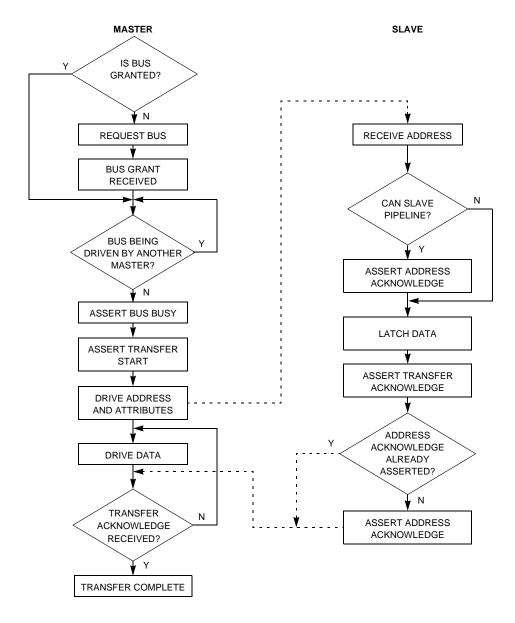

|       | 5.4.3.1 Read Cycle Flow                                                  |

|       | 5.4.3.2 Write Cycle Flow                                                 |

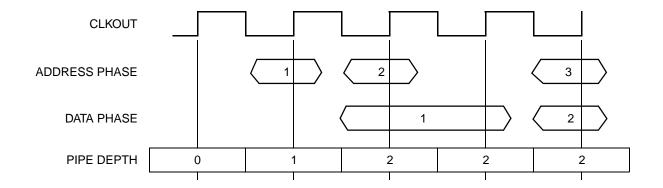

|       | 5.4.4 Basic Pipeline                                                     |

|       | 5.4.5 Bus Cycle Phases                                                   |

|       | 5.4.5.1 Arbitration Phase                                                |

|       | 5.4.5.2 Address Phase                                                    |

|       | 5.4.5.3 Data Phase                                                       |

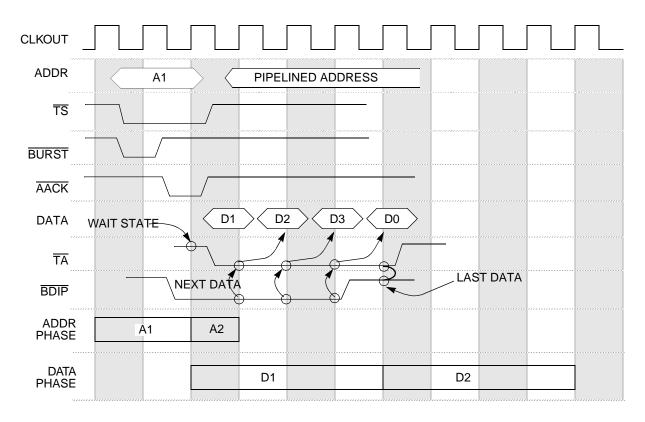

|       | 5.4.6 Burst Cycles                                                       |

|       | 5.4.6.1 Termination of Burst Cycles                                      |

|       | 5.4.6.2 Burst Inhibit Cycles                                             |

|       | 5.4.7 Decomposed Cycles and Address Wrapping 5-24                        |

|       | 5.4.8 Preventing Speculative Loads                                       |

| Paragraph                                              | Page   |

|--------------------------------------------------------|--------|

| Number                                                 | Number |

| 5.4.9 Accesses to 16-Bit Ports                         |        |

| 5.4.10 Address Retry                                   | 5-28   |

| 5.4.11 Transfer Error Acknowledge Cycles               | 5-28   |

| 5.4.12 Cycle Types                                     |        |

| 5.4.13 Show Cycles                                     | 5-30   |

| 5.4.14 Storage Reservation Support                     | 5-31   |

| 5.4.14.1 PowerPC Architecture Reservation Requirements | 5-32   |

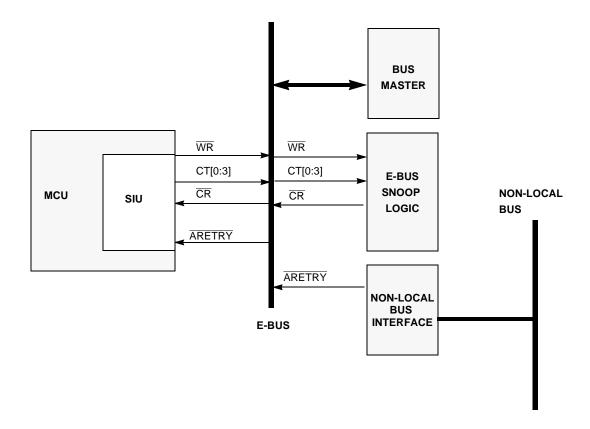

| 5.4.14.2 E-bus Storage Reservation Implementation      | 5-33   |

| 5.4.14.3 Reservation Storage Signals                   | 5-33   |

| 5.5 Chip Selects                                       | 5-34   |

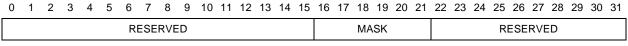

| 5.5.1 Chip-Select Features                             | 5-35   |

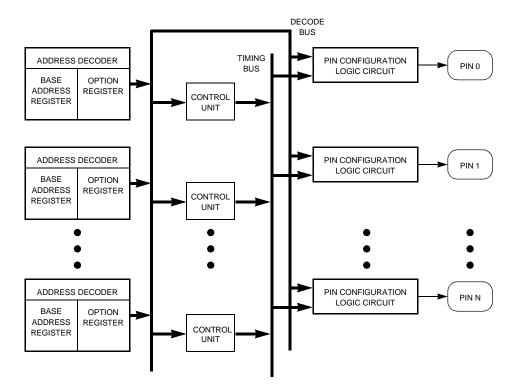

| 5.5.2 Chip-Select Block Diagram                        | 5-35   |

| 5.5.3 Chip-Select Pins                                 | 5-36   |

| 5.5.4 Chip-Select Registers and Address Map            | 5-37   |

| 5.5.4.1 Chip-Select Base Address Registers             | 5-39   |

| 5.5.4.2 Chip-Select Option Registers                   | 5-40   |

| 5.5.5 Chip-Select Regions                              | 5-44   |

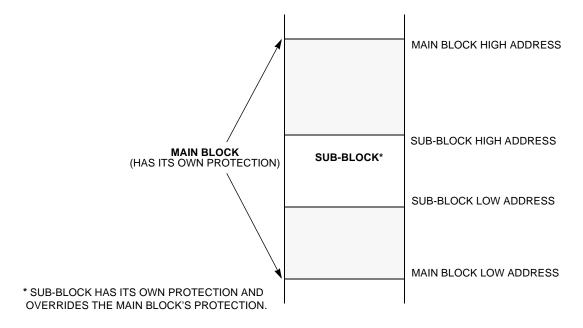

| 5.5.6 Multi-Level Protection                           | 5-46   |

| 5.5.6.1 Main Block and Sub-Block Pairings              | 5-46   |

| 5.5.6.2 Programming the Sub-Block Option Register      | 5-47   |

| 5.5.6.3 Multi-Level Protection for CSBOOT              | 5-47   |

| 5.5.7 Access Protection                                | 5-48   |

| 5.5.7.1 Supervisor Space Protection                    | 5-48   |

| 5.5.7.2 Data Space Protection                          | 5-48   |

| 5.5.7.3 Write Protection                               |        |

| 5.5.8 Cache Inhibit Control                            |        |

| 5.5.9 Handshaking Control                              |        |

| 5.5.10 Wait State Control                              |        |

| 5.5.11 Port Size                                       |        |

| 5.5.12 Chip-Select Pin Control                         |        |

| 5.5.12.1 Pin Configuration                             |        |

| 5.5.12.2 Byte Enable Control                           |        |

| 5.5.12.3 Region Control                                |        |

| 5.5.13 Interface Types                                 |        |

| 5.5.13.1 Interface Type Descriptions                   |        |

| 5.5.13.2 Turn-Off Times for Different Interface Types  |        |

| 5.5.13.3 Interface Type and BI Generation              |        |

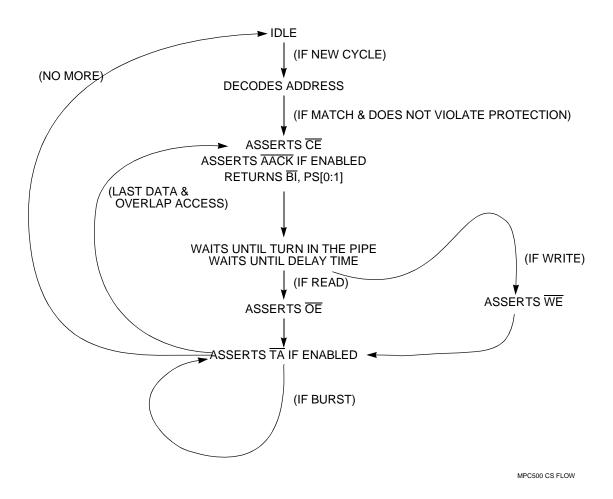

| 5.5.14 Chip-Select Operation Flowchart                 |        |

| 5.5.15 Pipe Tracking                                   |        |

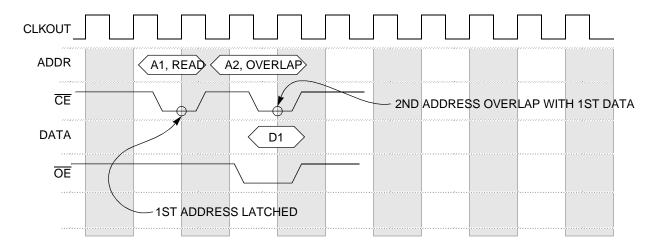

| 5.5.15.1 Pipelined Accesses to the Same Region         |        |

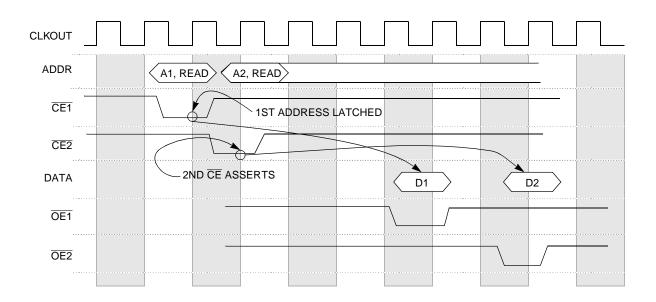

| 5.5.15.2 Pipelined Accesses to Different Regions       |        |

| 5.5.16 Chip-Select Timing Diagrams                     |        |

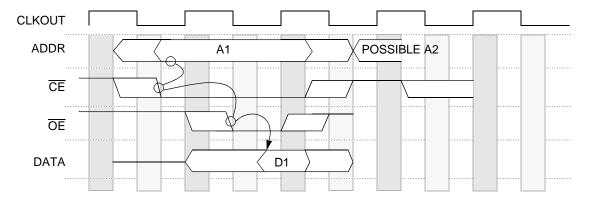

| 5.5.16.1 Asynchronous Interface                        | 5-59   |

| Paragraph                                                         | Page   |

|-------------------------------------------------------------------|--------|

| Number                                                            | Number |

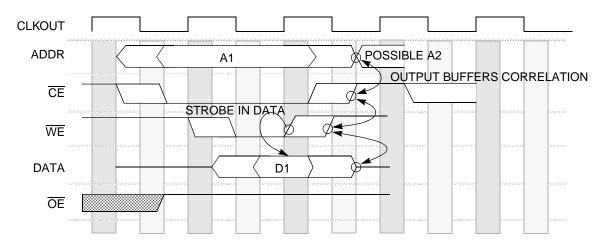

| 5.5.16.2 Asynchronous Interface with Latch Enable                 | 5-60   |

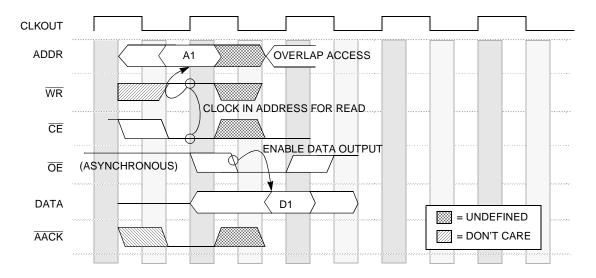

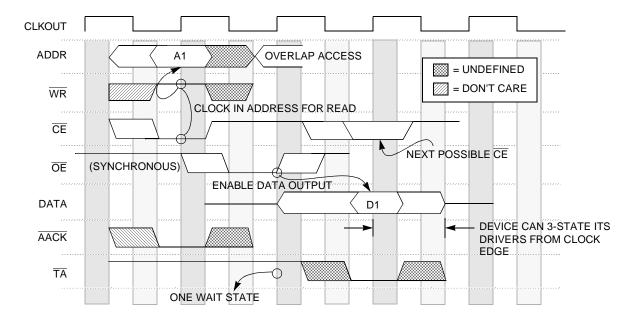

| 5.5.16.3 Synchronous Interface with Asynchronous OE               | 5-60   |

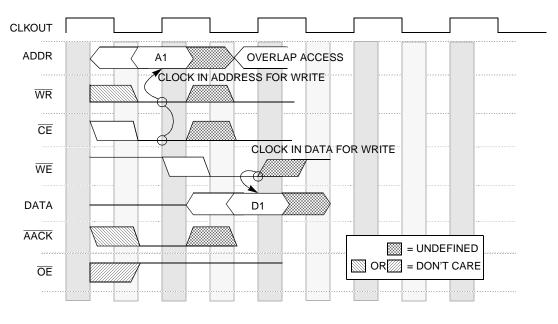

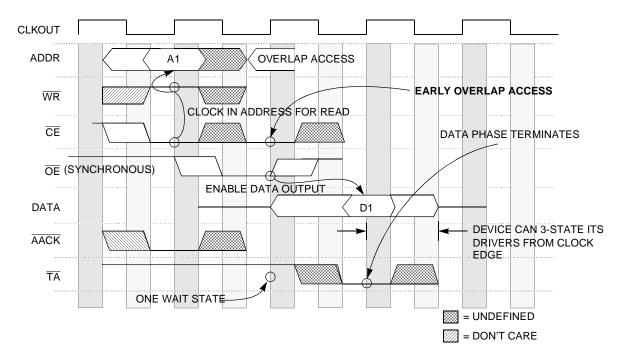

| 5.5.16.4 Synchronous Interface with Early Synchronous OE          | 5-61   |

| 5.5.16.5 Synchronous Interface with Synchronous OE, Early Overlap | 5-62   |

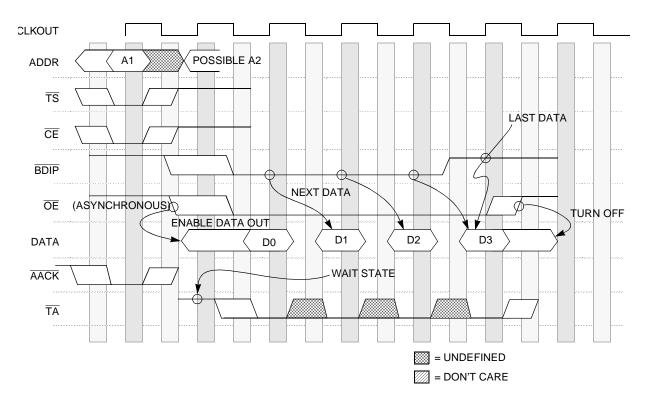

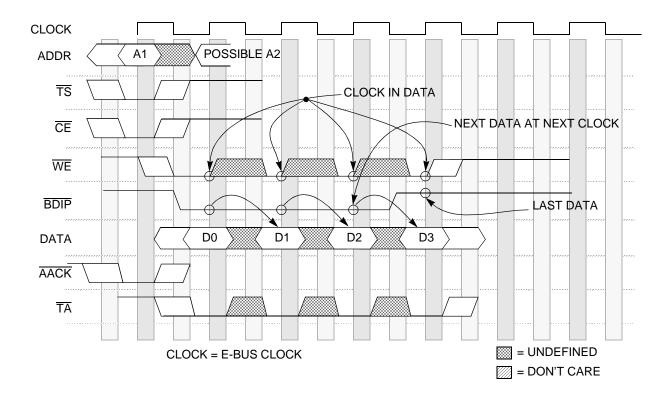

| 5.5.16.6 Synchronous Burst Interface                              | 5-63   |

| 5.5.17 Burst Handling                                             | 5-66   |

| 5.5.18 Chip-Select Reset Operation                                | 5-67   |

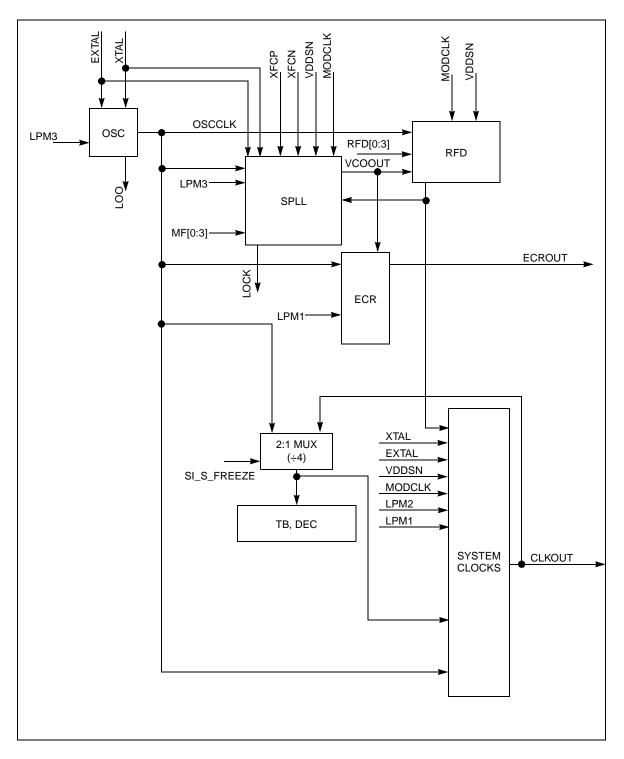

| 5.6 Clock Submodule                                               | 5-67   |

| 5.6.1 Clock Submodule Signal Descriptions                         | 5-70   |

| 5.6.2 Clock Power Supplies                                        | 5-70   |

| 5.6.3 System Clock Sources                                        | 5-71   |

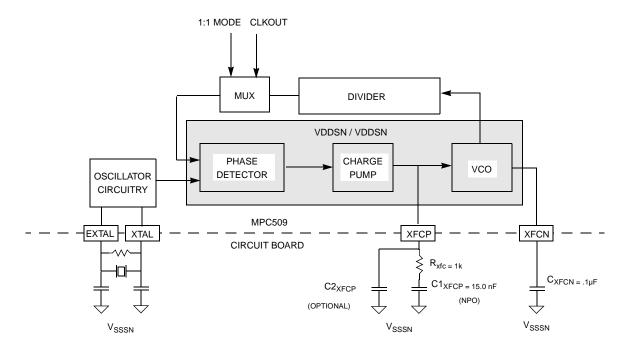

| 5.6.4 Phase-Locked Loop                                           | 5-71   |

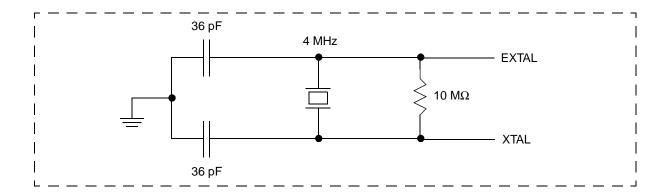

| 5.6.4.1 Crystal Oscillator                                        | 5-72   |

| 5.6.4.2 Phase Detector                                            | 5-73   |

| 5.6.4.3 Charge Pump and Loop Filter                               | 5-73   |

| 5.6.4.4 VCO                                                       | 5-74   |

| 5.6.4.5 Multiplication Factor Divider                             | 5-74   |

| 5.6.4.6 Clock Delay                                               | 5-74   |

| 5.6.5 CLKOUT Frequency Control                                    | 5-74   |

| 5.6.5.1 Multiplication Factor (MF) Bits                           | 5-75   |

| 5.6.5.2 Reduced Frequency Divider (RFD[0:3])                      | 5-77   |

| 5.6.6 Low-Power Modes                                             | 5-78   |

| 5.6.6.1 Normal Mode                                               | 5-78   |

| 5.6.6.2 Single-Chip Mode                                          | 5-78   |

| 5.6.6.3 Doze Mode                                                 | 5-78   |

| 5.6.6.4 Sleep Mode                                                | 5-79   |

| 5.6.6.5 Exiting Low-Power Mode                                    | 5-79   |

| 5.6.7 System Clock Lock Bits                                      | 5-79   |

| 5.6.8 Power-Down Wake Up                                          | 5-80   |

| 5.6.9 Time Base and Decrementer Support                           | 5-80   |

| 5.6.9.1 Time Base and Decrementer Clock Source                    | 5-81   |

| 5.6.9.2 Time Base/Decrementer and Freeze Assertion                | 5-81   |

| 5.6.9.3 Decrementer Clock Enable (DCE) Bit                        | 5-81   |

| 5.6.10 Clock Resets                                               | 5-81   |

| 5.6.10.1 Loss of PLL Lock                                         | 5-82   |

| 5.6.10.2 Loss of Oscillator                                       | 5-82   |

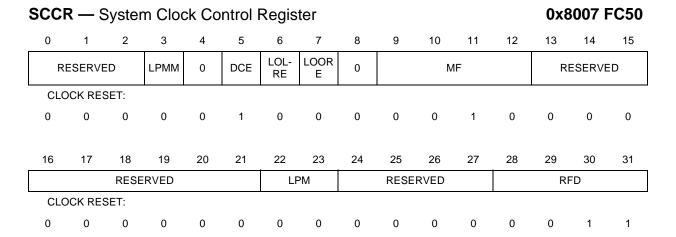

| 5.6.11 System Clock Control Register (SCCR)                       | 5-83   |

| 5.6.12 System Clock Lock and Status Register (SCLSR)              | 5-84   |

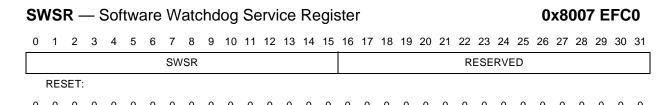

| 5.7 System Protection                                             | 5-85   |

| 5.7.1 System Protection Features                                  | 5-85   |

| 5.7.2 System Protection Registers                                 | 5-86   |

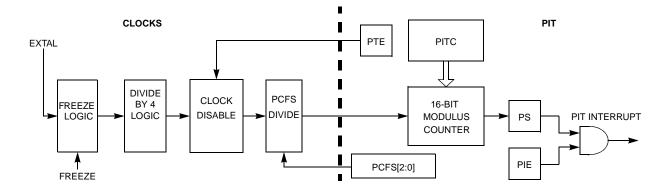

| 5.7.3 Periodic Interrupt Timer (PIT)                              | 5-86   |

| 5.7.3.1 PIT Clock Frequency Selection                             | 5-87   |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Number |

| 5.7.3.2 PIT Time-Out Period Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| 5.7.3.3 PIT Enable Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-89   |

| 5.7.3.4 PIT Interrupt Request Level and Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-89   |

| 5.7.3.5 Periodic Interrupt Control and Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-89   |

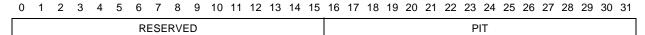

| 5.7.3.6 Periodic Interrupt Timer Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-90   |

| 5.7.4 Hardware Bus Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-90   |

| 5.7.4.1 Bus Monitor Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-91   |

| 5.7.4.2 Bus Monitor Lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-91   |

| 5.7.4.3 Bus Monitor Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-91   |

| 5.7.4.4 Bus Monitor Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-91   |

| 5.8 Reset Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-92   |

| 5.8.1 Reset Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-92   |

| 5.8.2 Reset Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-93   |

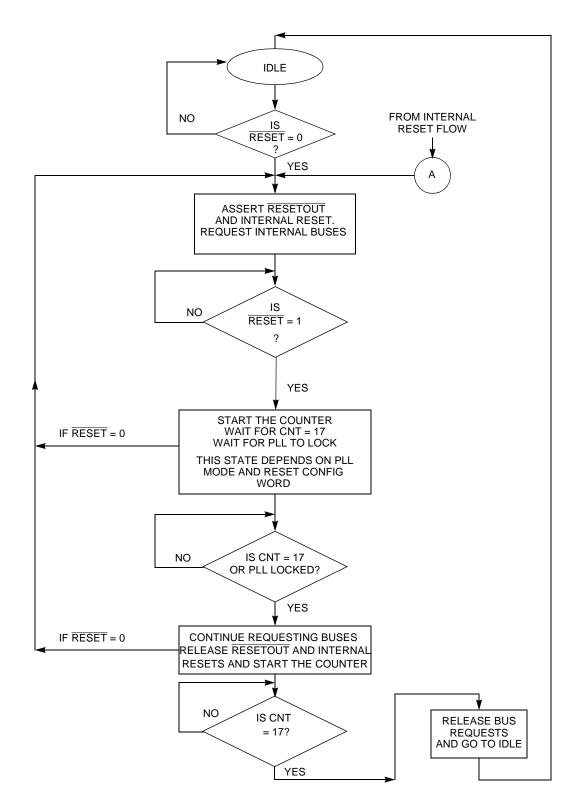

| 5.8.2.1 External Reset Request Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-93   |

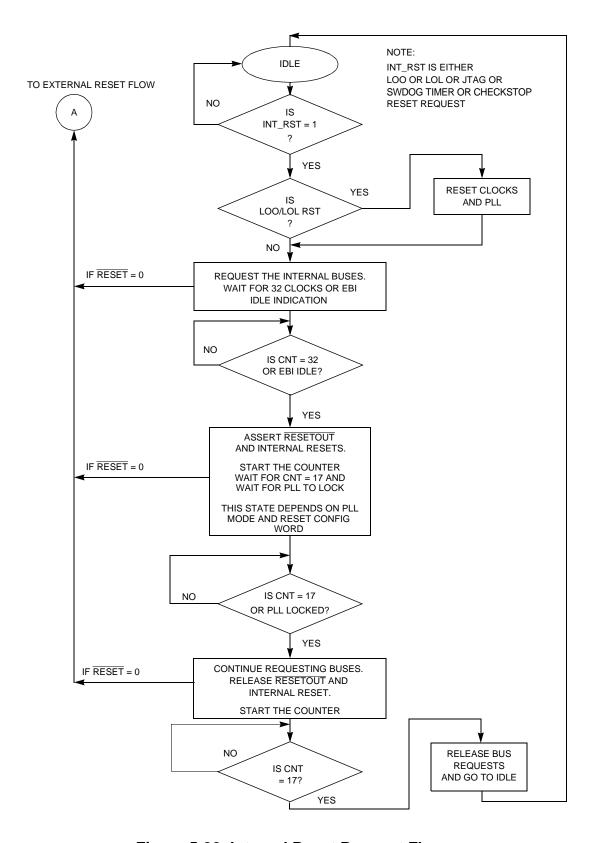

| 5.8.2.2 Internal Reset Request Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-95   |

| 5.8.2.3 Reset Behavior for Different Clock Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-97   |

| 5.8.3 Configuration During Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-98   |

| 5.8.3.1 Data Bus Configuration Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-98   |

| 5.8.3.2 Internal Default Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-99   |

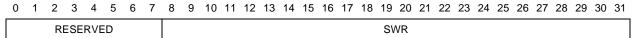

| 5.8.3.3 Data Bus Reset Configuration Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-99   |

| 5.8.4 Power-On Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-101  |

| 5.9 General-Purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-101  |

| 5.9.1 Port Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-102  |

| 5.9.2 Port M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-103  |