# **MPC509**

# *Technical Summary* **PowerPC™ MPC509 RISC Microcontroller**

The MPC509 is a member of the PowerPC Family of reduced instruction set computer (RISC) microcontrollers (MCUs). The MPC509 implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits.

The RISC MCU processor (RCPU) integrates four execution units: an integer unit (IU), a load/store unit (LSU), a branch processing unit (BPU), and a floating-point unit (FPU). The RCPU is capable of issuing one sequential (non-branch) instruction per clock. In addition, branch instructions are evaluated ahead of time when possible, resulting in zero-cycle execution time for many branch instructions. Instructions can complete out of order for increased performance; however, the MPC509 makes them appear sequential.

The MPC509 includes an on-chip, 4-Kbyte, two-way set associative, physically addressed instruction cache, chip-select logic to reduce or eliminate external decoding logic, 28 Kbytes of static RAM, and extensive processor debugging functionality.

The MPC509 has a high-bandwidth, 32-bit data bus and a 32-bit address bus. The MCU supports 16bit and 32-bit memories and both single-beat and burst data memory accesses.

The MPC509 uses an advanced, 3.3-V CMOS process technology and maintains full interface compatibility with TTL devices.

Refer to the current product selector guide (SG166/D) for current part availability.

PowerPC is a trademark of International Business Machines Corporation.

This document contains information on a new product under development. Specifications and information herein are subject to change without notice. See disclaimers on the last page of this document.

# TABLE OF CONTENTS

# Section

| 1 |              | Introduction                                                 | 4         |

|---|--------------|--------------------------------------------------------------|-----------|

|   | 1.1          | Features                                                     |           |

|   | 1.2          | Block Diagram                                                |           |

|   | 1.3          | Pin Connections                                              |           |

| _ | 1.4          | Memory Map                                                   |           |

| 2 |              | Signal Descriptions                                          | 9         |

| 3 |              | - · · · · · · · · · · · · · · · · · · ·                      | 13        |

|   | 3.1          | RCPU Features                                                |           |

|   | 3.2          | RCPU Block Diagram                                           |           |

|   | 3.3<br>3.4   | Instruction Sequencer<br>Independent Execution Units         |           |

|   | 3.4<br>3.5   | Levels of the PowerPC Architecture                           |           |

|   | 3.6          | RCPU Programming Model                                       |           |

|   | 3.7          | PowerPC UISA Register Set                                    |           |

|   | 3.8          | PowerPC VEA Register Set — Time Base                         |           |

|   | 3.9          | PowerPC OEA Register Set                                     |           |

|   | 3.10         | Instruction Set                                              |           |

|   | 3.11<br>3.12 | Exception Model<br>Instruction Timing                        |           |

|   | 3.12         | с                                                            |           |

| 4 |              |                                                              | 42        |

|   | 4.1<br>4.2   | Instruction Cache Features<br>Instruction Cache Organization |           |

|   | 4.2<br>4.3   | Programming Model                                            |           |

|   | 4.4          | Cache Operation                                              |           |

|   | 4.5          | Cache Commands                                               |           |

| 5 |              | System Interface Unit                                        | 50        |

|   | 5.1          | SIU Address Map                                              | 51        |

|   | 5.2          | SIU Module Configuration                                     | 52        |

|   | 5.3          | External Bus Interface                                       |           |

|   | 5.4          | Chip Selects                                                 |           |

|   | 5.5<br>5.6   | System Protection<br>Clock Submodule                         |           |

|   | 5.0<br>5.7   | Reset                                                        |           |

|   | 5.8          | General-Purpose I/O                                          |           |

| 6 |              | Peripheral Control Unit                                      | 89        |

| Ŭ | 6.1          | PCU Address Map                                              |           |

|   | 6.2          | Peripheral Control Unit Configuration                        |           |

|   | 6.3          | Software Watchdog                                            |           |

|   | 6.4          | Interrupt Controller                                         |           |

|   | 6.5          | Port Q                                                       |           |

| 7 |              |                                                              | 97        |

|   | 7.1          | Features                                                     |           |

|   | 7.2<br>7.3   | Programmer's Model<br>SRAM Module Registers                  |           |

| 8 | 1.5          |                                                              |           |

| ο | 0.4          |                                                              | <b>01</b> |

|   | 8.1<br>8.2   | Breakpoint Features                                          |           |

|   | 8.3          | Program Flow Tracking Features                               |           |

|   | 8.4          | Debug Modes                                                  |           |

|   | 8.5          | Development Port Features1                                   | 02        |

|   | 8.6          | Development Port and Debug Mode Configuration1               |           |

|   | 8.7          | Signal Descriptions                                          |           |

|   | 8.8          | Programming Model1                                           | 03        |

# **TABLE OF CONTENTS (Continued)**

# SectionPage9IEEE 1149.1-Compliant Interface1049.1TAP Controller1049.2Instruction Register104

# **1** Introduction

#### 1.1 Features

- Fully-Integrated Single-Chip Microcontroller

- RISC MCU Central Processing Unit (RCPU)

- 32-Bit PowerPC Architecture (Compliant with PowerPC Architecture Book 1)

- Single-Issue Processor

- Integrated Floating-Point Unit

- Branch Prediction for Prefetch

- 32 Bit x 32 Bit General-Purpose Register File

- 32 Bit x 64 Bit Floating-Point Register File

- Precise Exception Model

- Internal Harvard Architecture: Load/Store Bus (L-Bus), Instruction Bus (I-Bus)

- PowerPC Time Base and Decrementer

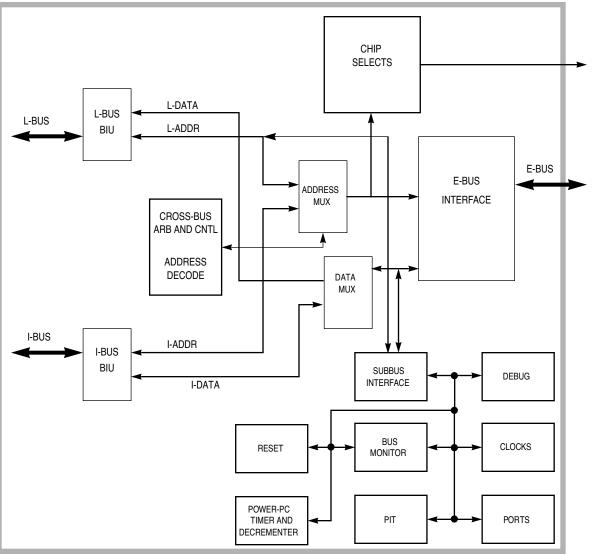

- System Interface Unit (SIU)

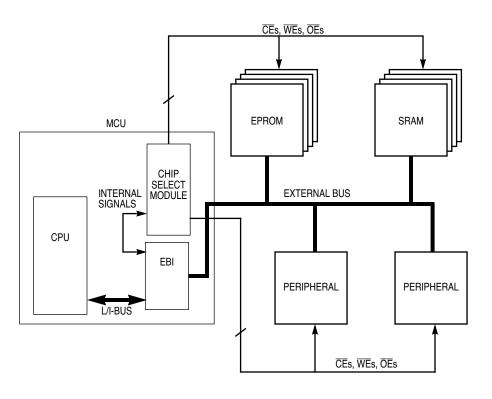

- Chip-Select Logic to Reduce or Eliminate External Decoding Logic

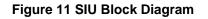

- External Bus Interface (EBI) that Supports Synchronous, Asynchronous, Burst Transfer, and Pipeline Transfer Memory Types

- System Protection Features Including Bus Monitor and Periodic Interrupt Timer

- On-Chip Phase-Locked Loop (PLL), 16 MHz to 44 MHz

- Five Dual-Purpose I/O Ports, Two Dual-Purpose Output Ports

- Peripheral Control Unit (PCU)

- Software Watchdog

- Interrupt Controller to Manage External and Internal Interrupts to the CPU

- Dual-Purpose I/O Port

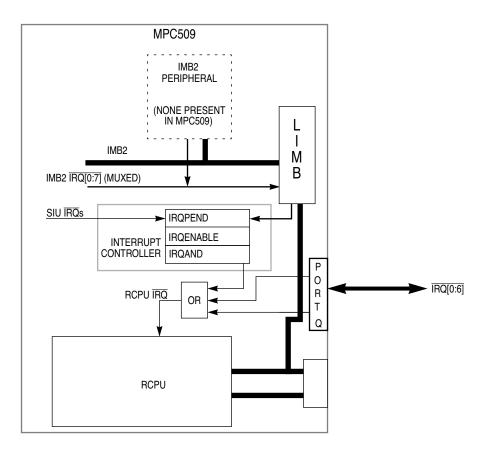

- L-Bus IMB Interface (LIMB) Connecting L-Bus to Intermodule Bus 2 (IMB2)

- 4-Kbyte On-Chip Instruction Cache (I-Cache)

- 28-Kbyte On-Chip Static Data RAM (SRAM)

- 3.3-V Supply Voltage

- Tolerates Input Signals from 5-V Peripherals

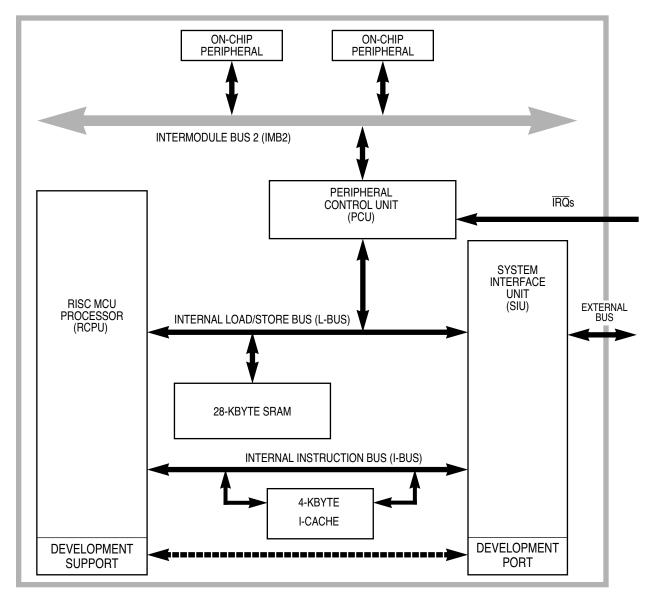

#### 1.2 Block Diagram

Figure 1 MPC509 Block Diagram

Notice in **Figure 1** that the IMB2 connects the processor to any on-chip peripherals. Although the MPC509 has no on-chip peripherals, the diagram is intended to show the operation of the IMB2 across the MPC family.

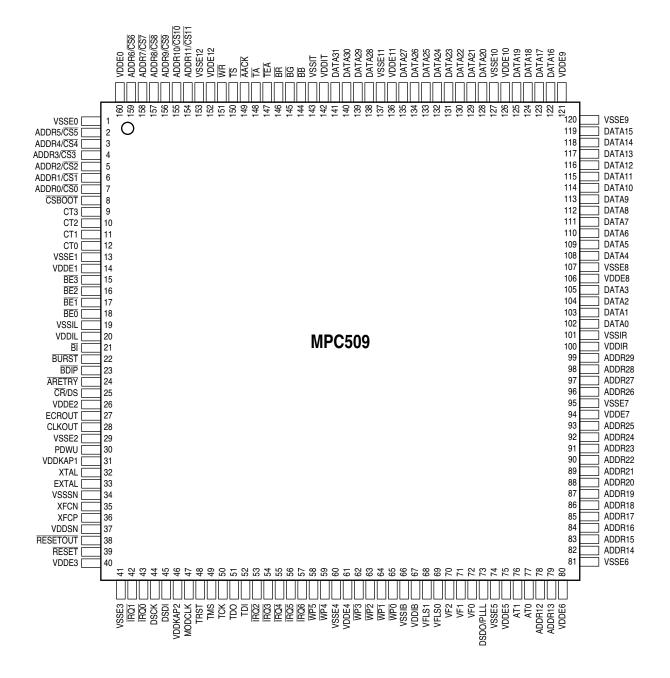

Figure 2 MPC509 Pin Assignments

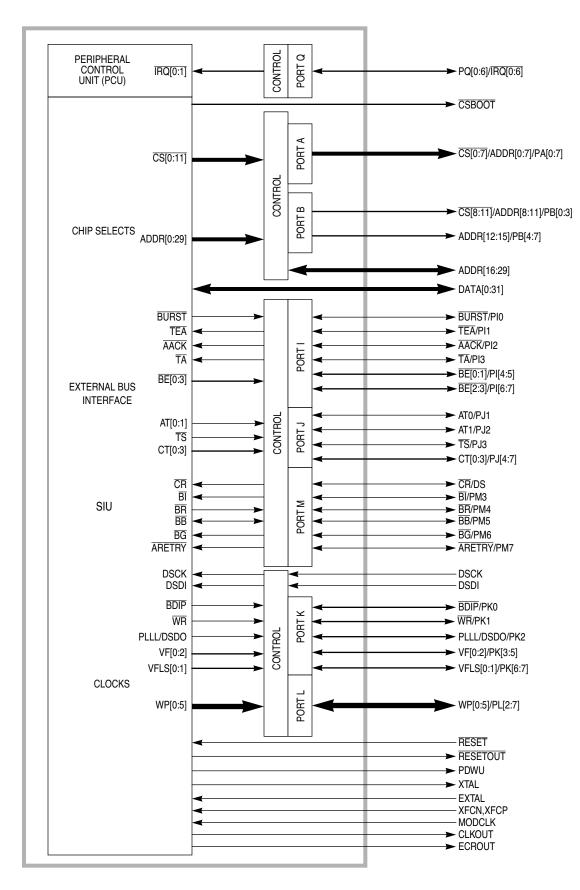

# Figure 3 MPC509 Signals

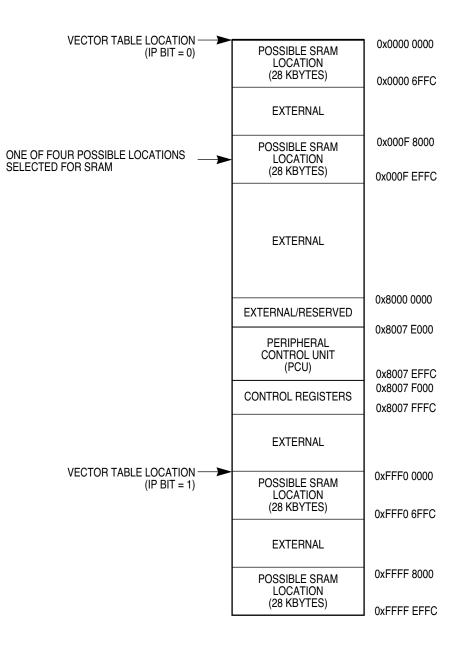

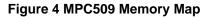

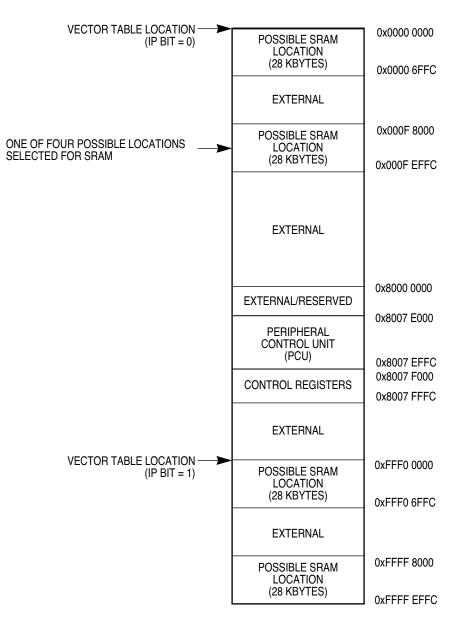

The MPC family has a unified memory map including instruction memory (I-Mem), load/store memory (L-Mem), and all memory-mapped registers. I-Mem resides on the instruction bus; L-Mem resides on the load/store bus. The locations of I-Mem and L-Mem are selected in the MEMMAP register located in the SIU. In the MPC509, the SRAM module serves as L-Mem. The MPC509 has no I-Mem module.

# **2 Signal Descriptions**

| ·                  |

|--------------------|

| Port Function      |

| Bus, Chip Selects  |

| PA[0:7], PB[0:3]   |

| PB[4:7]            |

| —                  |

| —                  |

| _                  |

| evelopment Support |

| PI[0:7]            |

| PJ[1:7]            |

| PK[0:7]            |

| PL[2:7]            |

| PM[3:7]            |

| —                  |

| —                  |

| _                  |

| errupts            |

| _                  |

| PQ[0:6]            |

| t                  |

| _                  |

| er                 |

| —                  |

| _                  |

| —                  |

| _                  |

|                    |

# Table 1 MPC509 Pin List

# Table 2 MPC509 Power Connections

| Pin                                   | Description                                                              |

|---------------------------------------|--------------------------------------------------------------------------|

| V <sub>DDE</sub> , V <sub>SSE</sub>   | External periphery power                                                 |

| V <sub>DDI</sub> , V <sub>SSI</sub>   | Internal module power                                                    |

| V <sub>DDSN</sub> , V <sub>SSSN</sub> | Clock synthesizer power                                                  |

| VDDKAP1                               | Keep-alive power for the internal oscillator, time base, and decrementer |

| VDDKAP2                               | Keep-alive power for the SRAM array                                      |

| Pin      | Pullup/Pulldown |  |

|----------|-----------------|--|

| TA       |                 |  |

| TEA      |                 |  |

| AACK     |                 |  |

| ARETRY   |                 |  |

| CR       |                 |  |

| BI       | Pullup          |  |

| BB       |                 |  |

| IRQ[0:6] |                 |  |

| TMS      |                 |  |

| TRST     |                 |  |

| TDI      |                 |  |

| BG       |                 |  |

| DSCK     | Dulldown        |  |

| DSDI     | – Pulldown      |  |

| ТСК      |                 |  |

# Table 3 Pins with Internal Pullups/Pulldowns

# **Table 4 Signal Descriptions**

| Mnemonic                                                                                        | Module | Direction                                                    | Description                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR[0:29]                                                                                      | EBI    | Output                                                       | 32-bit address bus. Driven by the bus master to index the bus slave.<br>Low-order bit (ADDR31) not pinned out — use byte enables instead.<br>BE2 functions as ADDR30 during accesses to 16-bit ports.  |

| AACK                                                                                            | EBI    | Input                                                        | Address acknowledge. When asserted, indicates the slave has received the address from the bus master.                                                                                                  |

| ARETRY                                                                                          | EBI    | Input                                                        | When asserted, indicates the master needs to retry its address phase.                                                                                                                                  |

| AT[0:1]                                                                                         | EBI    | Output                                                       | Address types. Define addressed space as user or supervisor, data or instruction.                                                                                                                      |

| BB                                                                                              | EBI    | Input/Output                                                 | Bus busy. Asserted by current bus master to indicate the bus is currently<br>in use. Prospective new master should wait until the current master ne-<br>gates this signal.                             |

| BDIP                                                                                            | EBI    | Output                                                       | Burst data in progress. Asserted at the beginning of a burst cycle and negated prior to the last beat. This signal can be negated prior to the end of a burst to terminate the burst data phase early. |

| BE[0:3]         EBI         Output         Byte enables. One byte enable per byte lane of the c |        | Byte enables. One byte enable per byte lane of the data bus. |                                                                                                                                                                                                        |

| BG                                                                                              | EBI    | Input                                                        | Bus grant. When asserted by bus arbiter, the bus is granted to the bus master. Each master has its own bus grant signal.                                                                               |

| BI                                                                                              | EBI    | Input                                                        | Burst inhibit. When asserted, indicates the slave does not support burst mode.                                                                                                                         |

| BR                                                                                              | EBI    | Output                                                       | Bus request. When asserted, indicates the potential bus master is re-<br>questing the bus. Each master has its own bus request signal.                                                                 |

| BURST                                                                                           | EBI    | Output                                                       | If asserted, indicates cycle is a burst cycle.                                                                                                                                                         |

| CLKOUT                                                                                          | EBI    | Output                                                       | Continuously-running clock. All signals driven on the E-bus must be syn-<br>chronized to the rising edge of this clock.                                                                                |

| CR                                                                                              | EBI    | Input                                                        | Cancel reservation. Each RCPU has its own $\overline{CR}$ signal. When asserted, instructs the bus master to clear its reservation.                                                                    |

| <b>Table 4 Signal Descriptions</b> | (Continued) |

|------------------------------------|-------------|

|------------------------------------|-------------|

| Mnemonic   | Module          | Direction    | Description                                                                                                                                                                                                                                                                                                |  |

|------------|-----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CSBOOT     | Chip<br>Selects | Output       | Chip select of system boot memory.                                                                                                                                                                                                                                                                         |  |

| CS[0:11]   | Chip<br>Selects | Output       | Chip-select signals for external memory devices.                                                                                                                                                                                                                                                           |  |

| CT[0:3]    | EBI             | Output       | Cycle type signals. Indicate what type of bus cycle the bus master is initiating.                                                                                                                                                                                                                          |  |

| DATA[0:31] | EBI             | Input/Output | 32-bit data bus.                                                                                                                                                                                                                                                                                           |  |

| DS         | EBI             | Output       | Data strobe. Asserted by EBI at the end of a chip-select-controlled bus cycle after the chip-select unit asserts the internal $\overline{TA}$ signal or the bus monitor timer asserts the internal $\overline{TEA}$ signal. Also asserted at the end of a show cycle. Used primarily by development tools. |  |

| DSCK       | Dev.<br>Support | Input        | Development serial clock. Used to clock data shifted into or out of development serial port.                                                                                                                                                                                                               |  |

| DSDI       | Dev.<br>Support | Input        | Development serial data in. Used to shift development serial data into the development port shift register.                                                                                                                                                                                                |  |

| DSDO       | Dev.<br>Support | Output       | Development serial data out. Used to shift development serial data out of the development port shift register.                                                                                                                                                                                             |  |

| ECROUT     | Clocks          | Output       | Provides a clock reference output with a frequency equal to the crystal oscillator frequency, taken from the PLL feedback signal.                                                                                                                                                                          |  |

| EXTAL      | Clocks          | Input        | Connection for external crystal to the internal oscillator circuit, or clock input.                                                                                                                                                                                                                        |  |

| IRQ[0:6]   | PCU             | Input        | Interrupt request inputs.                                                                                                                                                                                                                                                                                  |  |

| MODCLK     | Clocks          | Input        | Clock mode. The state of this signal and that of $V_{DDSN}$ during reset determine the source of the system clock (normal operation, 1:1 mode, PLL bypass mode, or special test mode). Refer to <b>Table 55</b> in <b>5 System Interface Unit</b> for details.                                             |  |

| PA[0:7]    | Ports           | Output       | Port A discrete output signals.                                                                                                                                                                                                                                                                            |  |

| PB[0:7]    | Ports           | Output       | Port B discrete output signals.                                                                                                                                                                                                                                                                            |  |

| PDWU       | Clocks          | Output       | Power-down wakeup to external power-on reset circuit.                                                                                                                                                                                                                                                      |  |

| PI[0:7]    | Ports           | Input/Output | Port I discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PJ[0:7]    | Ports           | Input/Output | Port J discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PK[0:7]    | Ports           | Input/Output | Port K discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PL[2:7]    | Ports           | Input/Output | Port L discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PM[3:7]    | Ports           | Input/Output | Port M discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PQ[0:6]    | PCU             | Input/Output | Port Q discrete input/output signals.                                                                                                                                                                                                                                                                      |  |

| PLLL       | Clock           | Output       | Indicates whether phase-locked loop is locked.                                                                                                                                                                                                                                                             |  |

| RESET      | EBI             | Input        | Hard reset. When asserted, devices on the bus must reset.                                                                                                                                                                                                                                                  |  |

| RESETOUT   | EBI             | Output       | Reset output signal. Asserted by MCU during reset. When asserted, in-<br>structs all devices monitoring this signal to reset all parts within them-<br>selves that can be reset by software.                                                                                                               |  |

| TA         | EBI             | Input        | Transfer acknowledge. When asserted, indicates the slave has received the data during a write cycle or returned the data during a read cycle.                                                                                                                                                              |  |

| TCK        | Test            | Input        | Test clock input with a pulldown resistor to synchronize the test logic.                                                                                                                                                                                                                                   |  |

| TDI        | Test            | Input        | Test data input with a pullup resistor sampled on the rising edge of TCK.                                                                                                                                                                                                                                  |  |

| TDO        | Test            | Output       | Three-statable test data output that changes on the falling edge of TCK.                                                                                                                                                                                                                                   |  |

| TEA        | EBI             | Input        | Transfer error acknowledge. Asserted by an external device to signal a bus error condition.                                                                                                                                                                                                                |  |

| Mnemonic          | Module          | Direction | Description                                                                                                                                                                                                                                                                                |

|-------------------|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS               | Test            | Input     | Test mode select input with a pullup resistor. Sampled on the rising edge of TCK to sequence the test controller's state machine.                                                                                                                                                          |

| TRST              | Test            | Input     | Asynchronous active-low test reset with a pullup resistor that provides initialization of the TAP controller and other logic as required by the standard.                                                                                                                                  |

| TS                | EBI             | Output    | Transfer start. When asserted, indicates the start of a bus cycle.                                                                                                                                                                                                                         |

| V <sub>DDSN</sub> | Clocks          | Input     | Power supply input to the VCO. In addition, the state of this signal and that of MODCLK during reset determine the source of the system clock (normal operation, 1:1 mode, PLL bypass mode, or special test mode). Refer to <b>Table 55</b> in <b>5 System Interface Unit</b> for details. |

| VF[0:2]           | Dev.<br>Support | Output    | Denotes the last fetched instruction or how many instructions were flushed from the instruction queue.                                                                                                                                                                                     |

| VFLS[0:1]         | Dev.<br>Support | Output    | Denotes how many instructions are flushed from the history buffer dur-<br>ing the current clock cycle. Also indicates freeze state.                                                                                                                                                        |

| V <sub>SSSN</sub> | Clocks          | Input     | Power ground input to the VCO.                                                                                                                                                                                                                                                             |

| WP[0:5]           | Dev.<br>Support | Output    | Output signals for I-bus watchpoints (WP[0:3]) and L-bus watchpoints (WP[4:5]).                                                                                                                                                                                                            |

| XTAL              | Clocks          | Output    | Connection for external crystal to the internal oscillator circuit.                                                                                                                                                                                                                        |

| WR                | EBI             | Output    | Asserted: write cycle. Negated: read cycle.                                                                                                                                                                                                                                                |

| XFCN,<br>XFCP     | Clocks          | Input     | Used to add an external filter circuit for the phase-locked loop. Refer to AN1282/D, "Board Strategies for Insuring Optimum Frequency Synthesizer Performance."                                                                                                                            |

# Table 4 Signal Descriptions (Continued)

# **3 Central Processing Unit**

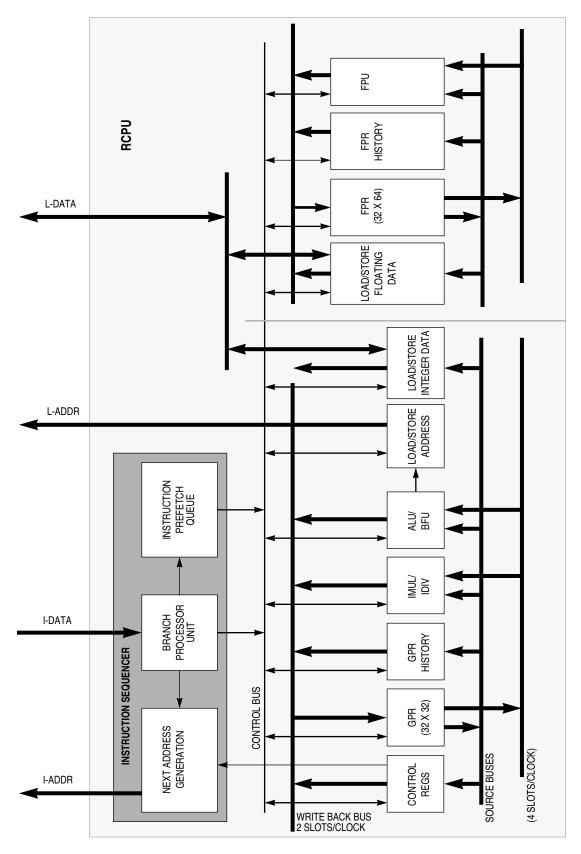

The PowerPC-based RISC processor (RCPU) used in the MPC500 family of microcontrollers integrates four execution units: an integer unit (IU), a load/store unit (LSU), a branch processing unit (BPU), and a floating-point unit (FPU). The use of simple instructions with rapid execution times yields high efficiency and throughput for MPC509-based systems.

Most integer instructions execute in one clock cycle. The FPU is designed to provide cost-effective solutions to most mathematical problems. It includes single- and double-precision multiply-add instructions. Instructions can complete out of order for increased performance; however, the processor makes execution appear sequential.

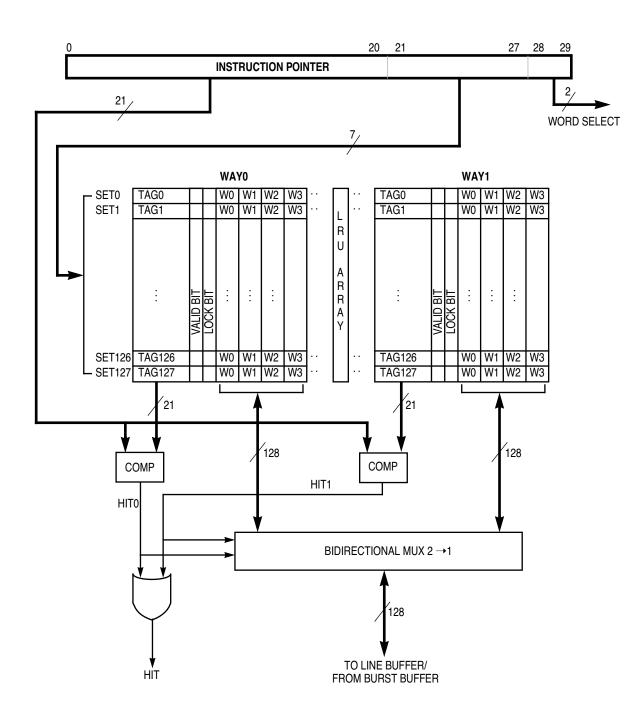

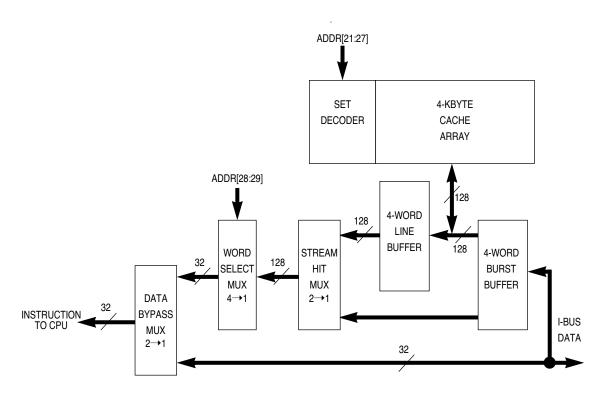

The MPC509 includes an on-chip, 4-Kbyte, two-way set-associative instruction cache. The cache uses a least recently used (LRU) replacement algorithm.

#### 3.1 RCPU Features

Major features of the RCPU include the following:

- High-performance microprocessor

- Single clock-cycle execution for many instructions

- Four independent execution units and two register files

- Independent LSU for load and store operations

- BPU featuring static branch prediction

- A 32-bit IU

- Fully IEEE 754-compliant FPU for both single- and double-precision operations

- Thirty-two general-purpose registers (GPRs) for integer operands

- Thirty-two floating-point registers (FPRs) for single- or double-precision operands

- Facilities for enhanced system performance

- Programmable big- and little-endian byte ordering

- Atomic memory references

- In-system testability and debugging features through boundary-scan capability

- High instruction and data throughput

- Condition register (CR) look-ahead operations performed by BPU

- Branch-folding capability during execution (zero-cycle branch execution time)

- Programmable static branch prediction on unresolved conditional branches

- A prefetch queue that can hold up to four instructions, providing look-ahead capability

- Interlocked pipelines with feed-forwarding that control data dependencies in hardware

- 4-Kbyte instruction cache: two-way set-associative, LRU replacement algorithm

# 3.2 RCPU Block Diagram

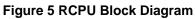

Figure 5 provides a block diagram of the RCPU.

#### **3.3 Instruction Sequencer**

The instruction sequencer provides centralized control over data flow between execution units and register files. The sequencer implements the basic instruction pipeline, fetches instructions from the memory system, issues them to available execution units, and maintains a state history so it can back the machine up in the event of an exception.

The instruction sequencer fetches the instructions from the instruction cache into the instruction prefetch queue. The BPU extracts branch instructions from the pre-fetch queue and uses static branch prediction on unresolved conditional branches to allow the instruction unit to fetch instructions from a predicted target instruction stream while a conditional branch is evaluated. The BPU folds out branch instructions for unconditional branches or conditional branches unaffected by instructions in the execution stage.

Instructions issued beyond a predicted branch do not complete execution until the branch is resolved, preserving the programming model of sequential execution. If branch prediction is incorrect, the instruction unit flushes all predicted path instructions, and instructions are issued from the correct path.

Figure 6 Sequencer Data Path

#### **3.4 Independent Execution Units**

The PowerPC architecture supports independent floating-point, integer, load-store, and branch processing execution units, making it possible to implement advanced features such as look-ahead operations. For example, since branch instructions do not depend on GPRs or FPRs, branches can often be resolved early, eliminating stalls caused by taken branches.

**Table 5** summarizes the RCPU execution units.

| Unit                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Branch processing<br>unit (BPU) | Includes the implementation of all branch instructions.                                                                                                                                                                                                                                                                                                                                                                    |

| Load/store unit (LSU)           | Includes implementation of all load and store instructions, whether defined as part of the integer processor or the floating-point processor.                                                                                                                                                                                                                                                                              |

| Integer unit (IU)               | Includes implementation of all integer instructions except load-store instructions.<br>This module includes the GPRs (including GPR history and scoreboard) and the<br>following subunits:<br>The IMUL-IDIV includes the implementation of the integer multiply and divide in-<br>structions.<br>The ALU-BFU includes implementation of all integer logic, add and subtract in-<br>structions, and bit field instructions. |

| Floating-point unit<br>(FPU)    | Includes the FPRs (including FPR history and scoreboard) and the implementa-<br>tion of all floating-point instructions except load and store floating-point instruc-<br>tions.                                                                                                                                                                                                                                            |

#### Table 5 RCPU Execution Units

The following sections describe the execution units in greater detail.

#### 3.4.1 Branch Processing Unit (BPU)

The BPU, located within the instruction sequencer, performs condition register look-ahead operations on conditional branches. The BPU looks through the instruction queue for a conditional branch instruction and attempts to resolve it early, achieving the effect of a zero-cycle branch in many cases.

The BPU uses a bit in the instruction encoding to predict the direction of the conditional branch. Therefore, when an unresolved conditional branch instruction is encountered, the processor prefetches instructions from the predicted target stream until the conditional branch is resolved.

The BPU contains an adder to compute branch target addresses and three special-purpose, user-accessible registers: the link register (LR), the count register (CTR), and the condition register (CR). The BPU calculates the return pointer for subroutine calls and saves it into the LR. The LR also contains the branch target address for the branch conditional to link register (**bctr***x*) instruction. The CTR contains the branch target address for the branch conditional to count register (**bctr***x*) instruction. The contents of the LR and CTR can be copied to or from any GPR. Because the BPU uses dedicated registers rather than general-purpose or floating-point registers, execution of branch instructions is independent from execution of integer and floating-point instructions.

#### 3.4.2 Integer Unit (IU)

The IU executes all integer processor instructions, except the integer storage access instructions, which are implemented by the load/store unit. The IU contains the following subunits:

- The IMUL–IDIV unit includes the implementation of the integer multiply and divide instructions.

- The ALU–BFU unit includes the implementation of all integer logic, add and subtract, and bit field instructions.

The IU also includes the integer exception register (XER) and the general-purpose register file.

IMUL–IDIV and ALU–BFU are implemented as separate execution units. The ALU–BFU unit can execute one instruction per clock cycle. IMUL–IDIV instructions require multiple clock cycles to execute. IMUL–IDIV is pipelined for multiply instructions, so that consecutive multiply instructions can be issued on consecutive clock cycles. Divide instructions are not pipelined; an integer divide instruction preceded or followed by an integer divide or multiply instruction results in a stall in the processor pipeline. Note that since IMUL–IDIV and ALU–BFU are implemented as separate execution units, an integer divide instruction preceded or followed by an ALU–BFU instruction does not cause a delay in the pipeline.

# 3.4.3 Load/Store Unit (LSU)

The load-store unit handles all data transfer between the general-purpose and floating-point register files and the internal load/store bus (L-bus). The load/store unit is implemented as an independent execution unit so that stalls in the memory pipeline do not cause the master instruction pipeline to stall (unless there is a data dependency). The unit is fully pipelined so that memory instructions of any size may be issued on back-to-back cycles.

There is a 32-bit wide data path between the load/store unit and the general-purpose register file and a 64-bit wide data path between the load/store unit and the floating-point register file. Single-word accesses es to the internal on-chip data RAM require one clock, resulting in two clocks latency. Double-word accesses require two clocks, resulting in three clocks latency. Since the L-bus is 32 bits wide, double-word transfers require two bus accesses. The load/store unit performs zero-fill for byte and half-word transfers and sign extension for half-word transfers.

Addresses are formed by adding the source one register operand specified by the instruction (or zero) to either a source two register operand or to a 16-bit, immediate value embedded in the instruction.

# 3.4.4 Floating-Point Unit (FPU)

The FPU contains a double-precision multiply array, the floating-point status and control register (FPSCR), and the FPRs. The multiply-add array allows the MPC509 to efficiently implement floating-point operations such as multiply, multiply-add, and divide.

The MPC509 depends on a software envelope to fully implement the IEEE floating-point specification. Overflows, underflows, NaNs, and denormalized numbers cause floating-point assist exceptions that invoke a software routine to deliver (with hardware assistance) the correct IEEE result.

To accelerate time-critical operations and make them more deterministic, the MPC509 provides a mode of operation that avoids invoking the software envelope and attempts to deliver results in hardware that are adequate for most applications, if not in strict conformance with IEEE standards. In this mode, denormalized numbers, NaNs, and IEEE invalid operations are treated as legitimate, returning default results rather than causing floating-point assist exceptions.

# 3.5 Levels of the PowerPC Architecture

The PowerPC architecture consists of three layers. Adherence to the PowerPC architecture can be measured in terms of which of the following levels of the architecture are implemented:

- PowerPC user instruction set architecture (UISA) Defines the base user-level instruction set, user-level registers, data types, floating-point exception model, memory models for a uniprocessor environment, and programming model for a uniprocessor environment.

- PowerPC virtual environment architecture (VEA) Describes the memory model for a multiprocessor environment, defines cache control instructions, and describes other aspects of virtual environments. Implementations that conform to the VEA also adhere to the UISA, but may not necessarily adhere to the OEA.

- PowerPC operating environment architecture (OEA) Defines the memory management model, supervisor-level registers, synchronization requirements, and the exception model. Implementations that conform to the OEA also adhere to the UISA and the VEA.

#### 3.6 RCPU Programming Model

The PowerPC architecture defines register-to-register operations for most computational instructions. Source operands for these instructions are accessed from the registers or are provided as immediate values embedded in the instruction opcode. The three-register instruction format allows specification of a target register distinct from the two source operands. Load and store instructions transfer data between memory and on-chip registers.

PowerPC processors have two levels of privilege: supervisor mode of operation (typically used by the operating environment) and user mode of operation (used by the application software). The programming models incorporate 32 GPRs, 32 FPRs, special-purpose registers (SPRs), and several miscellaneous registers.

Supervisor-level access is provided through the processor's exception mechanism. That is, when an exception is taken (either due to an error or problem that needs to be serviced, or deliberately through the use of a trap instruction), the processor begins operating in supervisor mode. The level of access is indicated by the privilege-level (PR) bit in the machine state register (MSR).

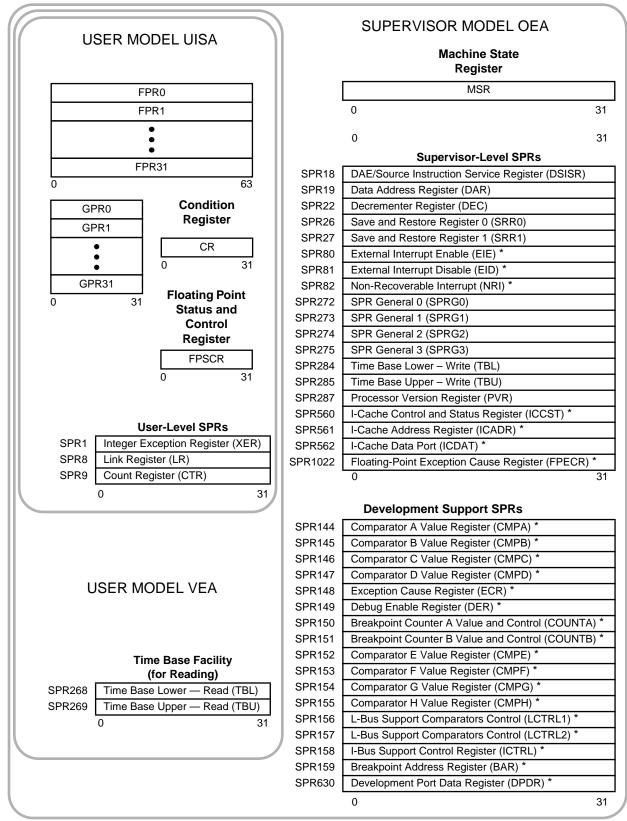

**Figure 7** shows the user-level and supervisor-level RCPU programming models and also illustrates the three levels of the PowerPC architecture. The numbers to the left of the SPRs indicate the decimal number that is used in the syntax of the instruction operands to access the register.

Note that registers such as the general-purpose registers (GPRs) and floating-point registers (FPRs) are accessed through operands that are part of the instructions. Access to registers can be explicit (that is, through the use of specific instructions for that purpose such as Move to Special-Purpose Register (**mtspr**) and Move from Special-Purpose Register (**mtspr**) instructions) or implicitly as the part of the execution of an instruction. Some registers are accessed both explicitly and implicitly.

\* Implementation-specific to the RCPU

# Figure 7 RCPU Programming Model

Where not otherwise noted, reserved fields in registers are ignored when written to and return zero when read. An exception to this rule is XER[16:23]. These bits are set to the value written to them and return that value when read.

#### 3.7 PowerPC UISA Register Set

The PowerPC UISA registers can be accessed by either user- or supervisor-level instructions. The general-purpose registers and floating-point registers are accessed through instruction operands.

#### 3.7.1 General-Purpose Registers (GPRs)

Integer data is manipulated in the integer unit's thirty-two 32-bit GPRs, shown below. These registers are accessed as source and destination registers through operands in the instruction syntax.

#### **GPRs** — General-Purpose Registers

| 0     | 31 |

|-------|----|

| GPR0  |    |

| GPR1  |    |

|       |    |

|       |    |

| GPR31 |    |

RESET: UNCHANGED

#### 3.7.2 Floating-Point Registers (FPRs)

The PowerPC architecture provides thirty-two 64-bit FPRs. These registers are accessed as source and destination registers through operands in floating-point instructions. Each FPR supports the double-precision, floating-point format. Every instruction that interprets the contents of an FPR as a floating-point value uses the double-precision floating-point format for this interpretation. That is, all floating-point numbers are stored in double-precision format.

All floating-point arithmetic instructions operate on data located in FPRs and, with the exception of the compare instructions (which update the CR), place the result into an FPR. Information about the status of floating-point operations is placed into the floating-point status and control register (FPSCR) and in some cases, into the CR, after the completion of the operation's writeback stage. For information on how the CR is affected by floating-point operations, see **3.7.4 Condition Register (CR)**.

#### **FPRs** — Floating-Point Registers

| 0 |       | 63 |

|---|-------|----|

|   | FPR0  |    |

|   | FPR1  |    |

|   |       |    |

|   |       |    |

|   | FPR31 |    |

RESET: UNCHANGED

#### 3.7.3 Floating-Point Status and Control Register (FPSCR)

The FPSCR controls the handling of floating-point exceptions and records status resulting from the floating-point operations. FPSCR[0:23] are status bits. FPSCR[24:31] are control bits.

FPSCR[0:12] and FPSCR[21:23] are floating-point exception condition bits. These bits are sticky, except for the floating-point enabled exception summary (FEX) and floating-point invalid operation exception summary (VX). Once set, sticky bits remain set until they are cleared by an **mcrfs**, **mtfsfi**, **mtfsf**, or **mtfsb0** instruction.

**Table 6** summarizes which bits in the FPSCR are sticky status bits, which are normal status bits, and which are control bits.

| Bits           | Туре               |

|----------------|--------------------|

| 0, 3:12, 21:23 | Status, sticky     |

| 1:2, 13:20     | Status, not sticky |

| 24:31          | Control            |

#### Table 6 FPSCR Bit Categories

FEX and VX are the logical ORs of other FPSCR bits. Therefore these two bits are not listed among the FPSCR bits directly affected by the various instructions.

#### **FPSCR** — Floating-Point Status and Control Register

| 0  | 1   | 2  | 3  | 4  | 5  | 6  | 7           | 8     | 9     | 10    | 11    | 12   | 13 | 14 | 15      |

|----|-----|----|----|----|----|----|-------------|-------|-------|-------|-------|------|----|----|---------|

| FX | FEX | VX | ох | UX | ZX | ХХ | VXS-<br>NAN | VXISI | VXIDI | VXZDZ | VXIMZ | VXVC | FR | FI | FPRF[0] |

RESET: UNCHANGED

| 16 | 17     | 18  | 19 | 20 | 21          | 22          | 23    | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|----|--------|-----|----|----|-------------|-------------|-------|----|----|----|----|----|----|----|----|

|    | FPRF[1 | :4] |    | 0  | VX-<br>SOFT | VX-<br>SQRT | VXCVI | VE | OE | UE | ZE | XE | NI | R  | N  |

RESET: UNCHANGED

A listing of FPSCR bit settings is shown in Table 7.

#### Table 7 FPSCR Bit Settings

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | FX   | Floating-point exception summary. Every floating-point instruction implicitly sets FPSCR[FX] if that instruction causes any of the floating-point exception bits in the FPSCR to change from zero to one. The <b>mcrfs</b> instruction implicitly clears FPSCR[FX] if the FPSCR field containing FP-SCR[FX] is copied. The <b>mtfsf</b> , <b>mtfsfi</b> , <b>mtfsb0</b> , and <b>mtfsb1</b> instructions can set or clear FP-SCR[FX] explicitly. This is a sticky bit.                                      |

| 1      | FEX  | Floating-point enabled exception summary. This bit signals the occurrence of any of the enabled exception conditions. It is the logical OR of all the floating-point exception bits masked with their respective enable bits. The <b>mcrfs</b> instruction implicitly clears FPSCR[FEX] if the result of the logical OR described above becomes zero. The <b>mtfsf</b> , <b>mtfsf</b> , <b>mtfsb0</b> , and <b>mtfsb1</b> instructions cannot set or clear FPSCR[FEX] explicitly. This is not a sticky bit. |

| Table 7 | FPSCR | <b>Bit Settings</b> | (Continued) |

|---------|-------|---------------------|-------------|

|---------|-------|---------------------|-------------|

| Bit(s) | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2      | vx     | Floating-point invalid operation exception summary. This bit signals the occurrence of any invalid operation exception. It is the logical OR of all of the invalid operation exceptions. The <b>mcrfs</b> instruction implicitly clears FPSCR[VX] if the result of the logical OR described above becomes zero. The <b>mtfsf</b> , <b>mtfsb0</b> , and <b>mtfsb1</b> instructions cannot set or clear FPSCR[VX] explicitly. This is not a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3      | OX     | Floating-point overflow exception. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4      | UX     | Floating-point underflow exception. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5      | ZX     | Floating-point zero divide exception. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6      | XX     | Floating-point inexact exception. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7      | VXSNAN | Floating-point invalid operation exception for SNaN. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8      | VXISI  | Floating-point invalid operation exception for ∞-∞. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9      | VXIDI  | Floating-point invalid operation exception for $\infty/\infty$ . This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10     | VXZDZ  | Floating-point invalid operation exception for 0/0. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11     | VXIMZ  | Floating-point invalid operation exception for $\infty^*0$ . This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12     | VXVC   | Floating-point invalid operation exception for invalid compare. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13     | FR     | Floating-point fraction rounded. The last floating-point instruction that potentially rounded the in-<br>termediate result incremented the fraction. This bit is not sticky.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14     | FI     | Floating-point fraction inexact. The last floating-point instruction that potentially rounded the in-<br>termediate result produced an inexact fraction or a disabled exponent overflow. This bit is not<br>sticky.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15:19  | FPRF   | <ul> <li>Floating-point result flags. This field is based on the value placed into the target register even if that value is undefined. Refer to Table 8 for specific bit settings.</li> <li>15 Floating-point result class descriptor (C). Floating-point instructions other than the compare instructions may set this bit with the FPCC bits, to indicate the class of the result.</li> <li>16:19 Floating-point condition code (FPCC). Floating-point compare instructions always set one of the FPCC bits to one and the other three FPCC bits to zero. Other floating-point instructions may set the FPCC bits with the C bit, to indicate the class of the result. Note that in this case the high-order three bits of the FPCC retain their relational significance indicating that the value is less than, greater than, or equal to zero.</li> <li>16 Floating-point greater than or positive (FL or &lt;)</li> <li>17 Floating-point equal or zero (FE or =)</li> <li>19 Floating-point unordered or NaN (FU or ?)</li> </ul> |

| 20     | _      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21     | VXSOFT | Floating-point invalid operation exception for software request. This bit can be altered only by the <b>mcrfs</b> , <b>mtfsf</b> , <b>mtfsf</b> , <b>mtfsb0</b> , or <b>mtfsb1</b> instructions. The purpose of VXSOFT is to allow software to cause an invalid operation condition for a condition that is not necessarily associated with the execution of a floating-point instruction. For example, it might be set by a program that computes a square root if the source operand is negative. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 22     | VXSQRT | Floating-point invalid operation exception for invalid square root. This is a sticky bit. This guar-<br>antees that software can simulate <b>fsqrt</b> and <b>frsqrte</b> , and to provide a consistent interface to han-<br>dle exceptions caused by square-root operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23     | VXCVI  | Floating-point invalid operation exception for invalid integer convert. This is a sticky bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 24     | VE     | Floating-point invalid operation exception enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 25     | OE     | Floating-point overflow exception enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 26     | UE     | Floating-point underflow exception enable. This bit should not be used to determine whether de-<br>normalization should be performed on floating-point stores.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit(s) | Name | Description                                                                                                           |  |

|--------|------|-----------------------------------------------------------------------------------------------------------------------|--|

| 27     | ZE   | Floating-point zero divide exception enable.                                                                          |  |

| 28     | XE   | loating-point inexact exception enable.                                                                               |  |

| 29     | NI   | Non-IEEE mode bit.                                                                                                    |  |

| 30:31  | RN   | Floating-point rounding control.00Round to nearest01Round toward zero10Round toward +infinity11Round toward –infinity |  |

# Table 7 FPSCR Bit Settings (Continued)

Table 8 illustrates the floating-point result flags that correspond to FPSCR[15:19].

| Result Flags<br>(Bits 15:19)<br>C<>=? | Result Value Class                      |

|---------------------------------------|-----------------------------------------|