# **XPEXAR**

30 MSPS, 8-Bit High Speed, Low Power Analog-to-Digital Converter with Power Down

#### FEATURES

- 8-Bit Resolution

- Sampling Rate to 30 MHz

- Low Power: 110 mW typ. (excluding reference)

- Power Down Mode: 100µA (typ)

- DNL = <u>+</u>1/4 LSB, INL = <u>+</u>1/2 LSB (typ)

- Internal S/H Function

- Single Supply: 5 V

- V<sub>IN</sub> Range: 0 V to V<sub>DD</sub>

- V<sub>REF</sub> Range: 1 V to V<sub>DD</sub>

- Latch-Up Free

- ESD Protection: 2000 V Minimum

- 3 State Digital Outputs

# **GENERAL DESCRIPTION**

The MP8786 is an 8-bit Analog-to-Digital Converter designed for high speed digitizing applications requiring low power. The MP8786 offers exceptional performance, flexible input architecture, low power consumption, power down capability, latch-up tolerant operation and is manufactured using an advanced 5 volt CMOS process.

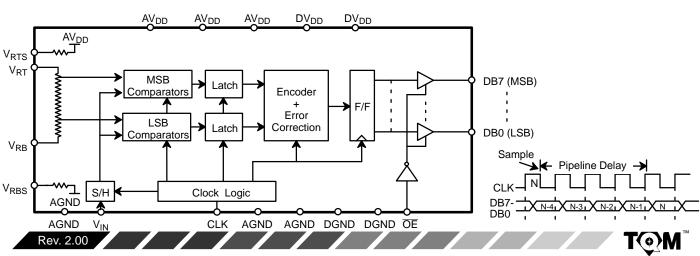

This device uses a two-step flash architecture to maintain low power consumption at high conversion rates. The input circuitry of the MP8786 includes an on-chip S/H function which allows the user to digitize analog input signals between GND and  $V_{DD}$ . Careful design and chip layout have achieved a low analog input capacitance. This reduces "kickback" and eases the requirements of the buffer/amplifier used to drive the MP8786.

The designer can choose the internally generated reference voltages by connecting V\_{RB} to V\_{RBS} and V\_{RT} to V\_{RTS}, or provide

• 20 Pin Package Available: MP8776

**MP8786**

CMOS

- 3 V Version: MP87L86

- Improved Version of MP8785

#### **APPLICATIONS**

- Wireless Communications

- Digital Cellular Telephones

- Telecommunications

- CCDs and Scanners

- Video Boards

- Digital Color Copiers

- Battery Powered Devices

external reference voltages to the V<sub>RB</sub> and V<sub>RT</sub> pins. The internal reference generates 0.6 V at V<sub>RB</sub> and 2.6 V at V<sub>RT</sub>. Providing external reference voltages allows easy interface to any input signal range between GND and V<sub>DD</sub>. This also allows the system to adjust these voltages to cancel zero scale and full scale errors, or to change the input range as needed.

When board space is at a premium, designers may prefer to use the MP8776 which is available in a 20 pin package.

The device operates from a single +5 volt supply. Power consumption is 110 mW (typ) at FS = 20 MHz. Power down is accomplished by dropping  $V_{RT}$  below 0.55 V.

Specified for operation over the commercial / industrial (-40 to +85°C) temperature range, the MP8786 is available in surface mount (SOIC) in Jedec and EIAJ, shrink small outline (SSOP) and plastic dual-in-line (PDIP) packages.

## SIMPLIFIED BLOCK AND TIMING DIAGRAM

# **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No. |

|-----------------|----------------------|----------|

| SOIC (EIAJ)     | –40 to +85°C         | MP8786AR |

| SOIC (Jedec)    | –40 to +85°C         | MP8786AS |

| Plastic Dip     | –40 to +85°C         | MP8786AN |

| SSOP            | –40 to +85°C         | MP8786AQ |

## **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

## **PIN OUT DEFINITIONS**

| PIN NO. | NAME | DESCRIPTION             |  |  |  |

|---------|------|-------------------------|--|--|--|

| 1       | ŌĒ   | Output Enable           |  |  |  |

| 2       | DGND | Ground (outputs)        |  |  |  |

| 3       | DB0  | Data Output Bit 0 (LSB) |  |  |  |

| 4       | DB1  | Data Output Bit 1       |  |  |  |

| 5       | DB2  | Data Output Bit 2       |  |  |  |

| 6       | DB3  | Data Output Bit 3       |  |  |  |

| 7       | DB4  | Data Output Bit 4       |  |  |  |

| 8       | DB5  | Data Output Bit 5       |  |  |  |

| 9       | DB6  | Data Output Bit 6       |  |  |  |

| 10      | DB7  | Data Output Bit 7 (MSB) |  |  |  |

| 11      | DVdd | Power Supply (outputs)  |  |  |  |

| 12      | CLK  | Sampling Clock Input    |  |  |  |

| PIN NO. | NAME | DESCRIPTION                         |

|---------|------|-------------------------------------|

| 13      | DVdd | Digital Power Supply                |

| 14      | AVdd | Power Supply                        |

| 15      | AVdd | Power Supply                        |

| 16      | Vrts | Generates 2.6 V if tied to $V_{RT}$ |

| 17      | Vrt  | Top Reference                       |

| 18      | AVdd | Power Supply                        |

| 19      | Vin  | Analog Input                        |

| 20      | AGND | Ground                              |

| 21      | AGND | Ground                              |

| 22      | VRBS | Generates 0.6 V if tied to $V_{RB}$ |

| 23      | Vrb  | Bottom Reference                    |

| 24      | DGND | Ground                              |

T@M

Rev. 2.00

# ELECTRICAL CHARACTERISTICS TABLE

Unless Otherwise Specified:  $AV_{DD} = DV_{DD} = 5 V$ , FS = 20 MHz (50% Duty Cycle),

/ / / / /

$V_{RT}$  = 2.6 V,  $V_{RB}$  = 0.6 V,  $T_A$  = 25°C

|                                           |                  |          | 25°C      |                  |          |                                                        |

|-------------------------------------------|------------------|----------|-----------|------------------|----------|--------------------------------------------------------|

| Parameter                                 | Symbol           | Min      | Тур       | Max              | Units    | Test Conditions/Comments                               |

| KEY FEATURES                              |                  |          |           |                  |          |                                                        |

| Resolution                                |                  | 8        |           |                  | Bits     |                                                        |

| Sampling Rate                             | FS               | 0.01     |           | 20               | MHz      | For specified performance                              |

|                                           | FS               |          |           | 30               | MHz      |                                                        |

| ACCURACY <sup>1</sup>                     |                  |          |           |                  |          |                                                        |

| Differential Non-Linearity                | DNL              |          | $\pm 1/4$ | ±1/2             | LSB      |                                                        |

| Integral Non-Linearity                    | INL              |          | $\pm 1/2$ | 1                | LSB      | Best Fit Line                                          |

| Zero Scale Error                          | EZS              |          | $\pm 35$  |                  | mV       | (Max INL – Min INL)/2                                  |

| Full Scale Error                          | EFS              |          | $\pm$ 35  |                  | mV       |                                                        |

| REFERENCE VOLTAGES                        |                  |          |           |                  |          |                                                        |

| Positive Ref. Voltage                     | V <sub>RT</sub>  |          | 2.6       | AV <sub>DD</sub> | v        |                                                        |

| Negative Ref. Voltage                     | V <sub>RB</sub>  | AGND     | 0.6       | 66               | V        |                                                        |

| Differential Ref. Voltage <sup>3</sup>    | V <sub>REF</sub> | 1.0      |           | AV <sub>DD</sub> | V        | $V_{REF} = V_{RT} - V_{RB}$                            |

| Ladder Resistance                         | RL               | 245      | 350       | 455              | Ω        |                                                        |

| Ladder Temp. Coefficient                  | R <sub>TCO</sub> |          | 2000      |                  | ppm/°C   |                                                        |

| Self Bias 1                               | V <sub>RB</sub>  |          | 0.6       |                  | V        | Short V <sub>RB</sub> to V <sub>RBS</sub>              |

|                                           |                  |          |           |                  |          | and V <sub>RT</sub> to V <sub>RTS</sub>                |

|                                           | $V_{REF}$        |          | 2         |                  | V        | Short V <sub>RB</sub> to V <sub>RBS</sub>              |

|                                           |                  |          |           |                  |          | and $V_{RT}$ to $V_{RTS}$                              |

| Self Bias 2                               | V <sub>RT</sub>  |          | 2.3       |                  | V        | $V_{RB}$ = AGND, Short $V_{RT}$ and $V_{RTS}$          |

| ANALOG INPUT <sup>2</sup>                 |                  |          |           |                  |          |                                                        |

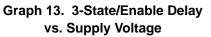

| Bandwidth (–1 dB) <sup>4</sup>            | BW               |          | 14        |                  | MHz      |                                                        |

| Input Voltage Range                       | V <sub>IN</sub>  | 0        |           | AV <sub>DD</sub> | V        |                                                        |

| Input Capacitance Sample <sup>5</sup>     | C <sub>IN</sub>  |          | 22        |                  | pF       | Clock High                                             |

| Input Capacitance Convert <sup>5</sup>    | C <sub>IN</sub>  |          | 7         |                  | pF       | Clock Low                                              |

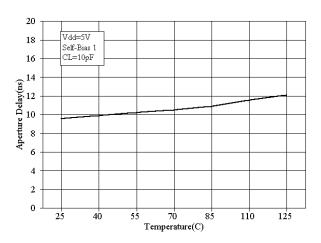

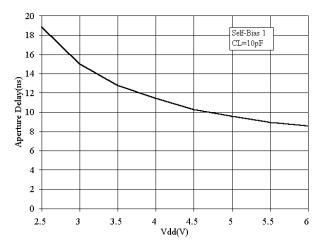

| Aperture Delay                            | t <sub>AP</sub>  |          | 10        |                  | ns       |                                                        |

| Aperture Jitter                           | t <sub>AJ</sub>  |          | 30        |                  | ps       |                                                        |

| DYNAMIC PERFORMANCE <sup>2</sup>          |                  |          |           |                  |          | F <sub>IN</sub> = 1 MHz                                |

| Signal to Noise Ratio                     | SNR              |          | 46        |                  | dB       |                                                        |

| Signal to Noise plus Distortion           | SINAD            |          | 42        |                  | dB       |                                                        |

| Harmonic Distortion                       | THD              |          | -46       |                  | dB       |                                                        |

| Effective No. of Bits                     | ENOB             |          | 6.8       |                  | Bits     |                                                        |

| DIGITAL INPUTS                            |                  |          |           |                  |          |                                                        |

| Logical "1" Voltage                       | V <sub>IH</sub>  | 3.5      |           |                  | V        |                                                        |

| Logical "0" Voltage                       | V <sub>IL</sub>  |          |           | 1.5              | V        |                                                        |

| DC Leakage Currents <sup>6</sup>          | I <sub>IN</sub>  |          |           |                  |          | V <sub>IN</sub> =DGND to DV <sub>DD</sub>              |

| CLK                                       |                  |          | 5         |                  | μΑ       |                                                        |

| OE                                        |                  |          | 5         |                  | μA       |                                                        |

| Input Capacitance                         |                  |          | 5         |                  | pF       |                                                        |

| Clock Timing (See Figure 6.) <sup>7</sup> |                  | 50       |           |                  |          |                                                        |

| Clock Period                              | 1/FS             | 50<br>25 |           |                  | ns       | For Specified Performance<br>For Specified Performance |

| High Pulse Width<br>Low Pulse Width       | t <sub>PWH</sub> | 25<br>25 |           |                  | ns<br>ns | For Specified Performance                              |

|                                           | t <sub>PWL</sub> | 20       |           |                  | 115      |                                                        |

# ELECTRICAL CHARACTERISTICS TABLE (CONT'D)

|                                                                                                                                                                                                |                                                           |     | 25°C                 |                        | Tmin to | Tmax |                                             |                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|----------------------|------------------------|---------|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                                                      | Symbol                                                    | Min | Тур                  | Max                    | Min     | Max  | Units                                       | Test Conditions/Comments                                                                                                                         |

| DIGITAL OUTPUTS                                                                                                                                                                                |                                                           |     |                      |                        |         |      |                                             | C <sub>OUT</sub> =15 pF                                                                                                                          |

| Logical "1" Voltage<br>Logical "0" Voltage<br>3-state Leakage<br>Data Valid Delay <sup>2, 8</sup><br>Data Enable Delay <sup>2, 8</sup><br>Data 3-state Delay <sup>2, 8</sup><br>Pipeline Delay | Voh<br>Vol<br>Ioz<br>t <sub>den</sub><br>t <sub>den</sub> | 4.5 | 10<br>20<br>20<br>12 | 0.4<br>25<br>15<br>3.5 |         |      | V<br>V<br>μA<br>ns<br>ns<br>clock<br>cycles | $I_{LOAD} = 4 \text{ mA}$<br>$I_{LOAD} = 4 \text{ mA}$<br>$V_{OUT}=GND \text{ to } DV_{DD}$<br>Constant relationship between<br>clock and output |

| POWER SUPPLIES                                                                                                                                                                                 |                                                           |     |                      |                        |         |      |                                             |                                                                                                                                                  |

| Operating Voltage (AV <sub>DD</sub> , DV <sub>DD</sub> ) <sup>9</sup><br>Current (AV <sub>DD</sub> + DV <sub>DD</sub> )                                                                        | V <sub>DD</sub><br>I <sub>DD</sub>                        |     | 5<br>22              | 35                     |         |      | V<br>mA                                     | Does not include ref. current                                                                                                                    |

| POWER DOWN                                                                                                                                                                                     |                                                           |     |                      |                        |         |      |                                             |                                                                                                                                                  |

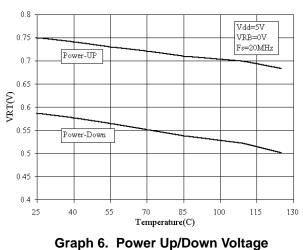

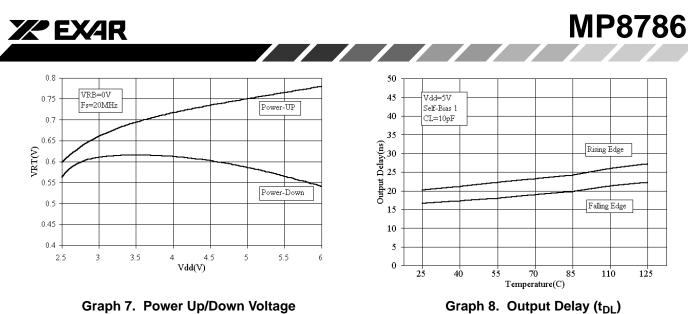

| Power Down Point<br>Power Up Point<br>Power Down Current<br>Power Control Delay                                                                                                                | V <sub>RTPD</sub><br>I <sub>DDPD</sub><br>PDD             | 0.4 | 0.55                 | 0.9<br>100<br>200      |         |      | V<br>V<br>μA<br>ns                          | Chip goes to power down mode when $V_{RT} < 0.55 \text{ V}$<br>Does not include ref. current $V_{RT} @ 0.4 \rightarrow 0.9 \text{ V}$            |

#### NOTES

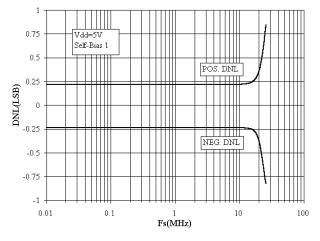

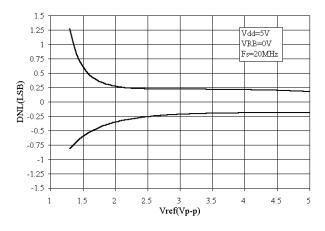

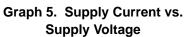

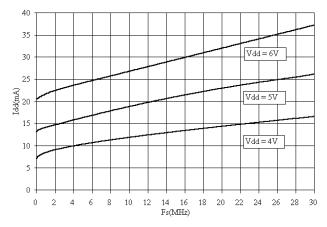

Tester measures code transitions by dithering the voltage of the analog input (V<sub>IN</sub>). The difference between the measured and the ideal code width ( $V_{REF}/256$ ) is the DNL error (*Figure 10*.). The INL error is the maximum distance (in LSBs) from the best fit line to any transition voltage (*Figure 11*.) Accuracy is a function of the sampling rate (FS).

2 Guaranteed. Not tested.

3 Specified values guarantee functionality. Refer to other parameters for accuracy.

4 The bandwidth represents the gain of the ADC and does not imply accuracy

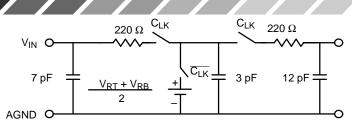

5 See V<sub>IN</sub> input equivalent circuit (Figure 2.). Switched capacitor analog input requires driver with low output resistance.

6 All inputs have diodes to V<sub>DD</sub> and GND. Input DC currents will not exceed specified limits for any input voltage between GND and V<sub>DD</sub>.

- 7 t<sub>R</sub>, t<sub>F</sub> should be limited to >5 ns for best results.

- 8 Depends on the RC load connected to the output pin.

- 9 AGND and DGND pins are connected through the silicon substrate. Connect together at the package and to the analog ground plane.

Specifications are subject to change without notice

## ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted) <sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND            |                                    |

|-----------------------------------|------------------------------------|

| V <sub>RT</sub> & V <sub>RB</sub> | V <sub>DD</sub> +0.5 to GND -0.5 V |

| V <sub>IN</sub>                   | V <sub>DD</sub> +0.5 to GND -0.5 V |

| All Inputs                        | $V_{DD}$ +0.5 to GND –0.5 V        |

| All Outputs                       | V <sub>DD</sub> +0.5 to GND -0.5 V |

| Storage Temperature               | –65 to +150°C                      |

| Lead Temperature (Soldering 10 seconds) $\ldots \ldots 300^{\circ}C$ |

|----------------------------------------------------------------------|

| Maximum Junction Temperature $\ldots \ldots \ldots 150^{\circ}C$     |

| Package Power Dissipation Rating @ 75°C<br>SOIC, PDIP, SSOP          |

#### NOTES:

- Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2 Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100 $\mu$ s. V<sub>DD</sub> refers to AV<sub>DD</sub> and DV<sub>DD</sub>. GND refers to AGND and DGND. 3

# THEORY OF OPERATION

## Analog to Digital Conversion

The MP8786 uses a two step, subranging architecture to convert analog voltages into 256 digital codes.

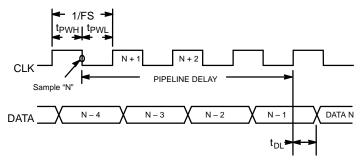

A full conversion (sampling V<sub>IN</sub>, converting MSB & LSB, and performing any error correction) requires four clock cycles to complete (*see Figure 6.*) The pipelined architecture allows the chip to maintain a one conversion per cycle sample rate. Digital logic combines the MSB and LSB data and performs error correction to produce 8-bit output codes.

#### **Internal Reference Bias**

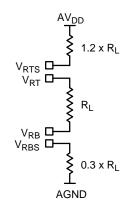

The MP8786 includes two on-chip resistors that can be used to bias the reference ladder without external circuitry. These two resistors are designed to track the reference ladder and are used to create a voltage divider between the supplies (AV<sub>DD</sub> and AGND).

To use this feature simply connect  $V_{RT}$  to  $V_{RTS}$  and connect  $V_{RB}$  to  $V_{RBS}.$  This will nominally generate:

$AV_{DD} \times (0.3/2.5)$  at  $V_{RB}$ , and

$AV_{DD} x (1.3/2.5)$  at  $V_{RT}$

This will generate 0.6 V at V<sub>RB</sub> and 2.6 V at V<sub>RT</sub> (*Figure 1.*) Bypass capacitors on V<sub>RT</sub> and V<sub>RB</sub> are suggested to stabilize the ladder.

If the internal reference pins  $V_{RTS}$  and/or  $V_{RBS}$  are not used they should be left unconnected.

Figure 1. Internal Reference Bias

#### **Transfer Characteristics**

Rev. 2.00

The ideal ADC is a linear building block that has infinite bandwidth and no phase distortion. A real ADC, however, exhibits finite bandwidth and non-constant group delay characteristics as well as non-linear behavior due to the non-zero INL characteristic. When modeling the ADC as a linear element and a quantizer, the circuit shown in *Figure 2*. can be used in order to represent the ADC's bandwidth.

**MP8786**

#### Figure 2. Input Equivalent Circuit

## Sample and Hold Timing

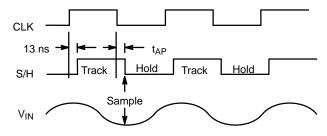

The ADC's internal sample and hold tracks the input signal when CLK is high. After a delay of  $t_{AP}$  from the falling clock edge, the analog signal is sampled and held for conversion as seen in *Figure 3.*

Figure 3. Sample and Hold Timing

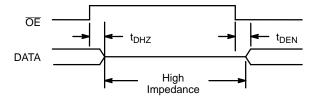

## Output Enable (OE)

The  $\overline{OE}$  pin controls the state of the digital output drivers. When forced low, the drivers are active. When pulled high the drivers are 3-stated. Please note that the  $\overline{OE}$  pin only controls the output drivers, the rest of the chip is still active. Therefore if the clock is running, the internal registers are updated even if the digital outputs are 3-stated (*Figure 4.*).

#### **Power Down Mode**

For systems that are battery powered, the MP8786 has a power down feature to help extend battery life. When the voltage at the V<sub>RT</sub> pin drops below 0.4 V, the chip goes into power down mode. In this state, conversions are halted, the outputs are 3-stated and I<sub>DD</sub> drops to less than 100  $\mu$ A. Then, when the voltage at the V<sub>RT</sub> pin rises above 0.9 V, the chip will power up. Note that after power up, four clock cycles are required to get valid data at the digital outputs (see *Figure 6.*) One way to achieve power down is to disconnect or disable the buffer/amp driving V<sub>RT</sub>, and let the internal reference resistance pull V<sub>RT</sub> down. Remember, any bypass capacitors at V<sub>RT</sub> will increase the time for V<sub>RT</sub> to drop below 0.4 V.

# APPLICATION NOTES

**MP8786**

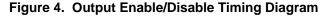

#### **Power Supplies and Grounding**

$AV_{DD}$  and  $DV_{DD}$  should be connected to the sample power supply source (*Figure 5.*). The power supply (AV\_{DD} and DV\_{DD}) and reference voltage (V<sub>RT</sub> & V<sub>RB</sub>) pins should be decoupled with 0.1µF and 10µF capacitors to GND, placed as close to the chip as possible.

AGND and DGND pins are connected internally through the P-substrate. AGND and DGND pins should be connected together as close to the chip as possible.

**Figure 5. Typical Circuit Connections**

#### The Analog Input

Rev. 2.00

When designing with the MP8786, the following points can help optimize performance.

- Driving the analog input The input impedance can be represented as a switched capacitor type input circuit, ie. the input impedance changes with the phase of the input clock. *Figure 2.* shows an equivalent input circuit. In many applications, the input impedance can be treated as capacitive. For fast signals and a high driving impedance, a wide bandwidth op amp is recommended.

- It is important to note that op amps have inductive output impedances at high frequencies which is a consequence of the emitter impedance of the typical push-pull output stage. The resulting transient ringing should be damped by inserting a resistor in series with the ADC input – typically about 50Ω. See *Figure 5*. The exact value may be obtained from the op amp manufacturer's data sheet.

- Signals should not exceed V<sub>DD</sub> +0.5V or go below GND -0.5V. All pins have internal protection diodes that will protect them from short transients (*See Note 2, Absolute Maximum Ratings*) outside the supply range.

#### **Digital Outputs**

Refer to *Figure 6.* for details on the data availability timing. The digital outputs should not drive long wires or buses. The capacitive coupling and reflections will contribute noise to the conversion. The output enable pin ( $\overline{OE}$ ) should not be left unconnected. If it is not controlled by an active signal, it must be tied to ground.

**Z** EXAR

Figure 6. Data Available Timing

#### **Dynamic Reference Control**

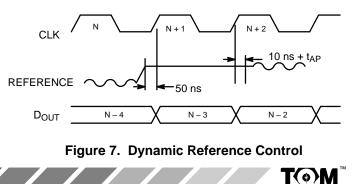

The MP8786 allows for dynamically adjusted  $V_{RT}$  and  $V_{RB}$ . When this is done,  $V_{RT}$  and  $V_{RB}$  have to be kept static during a certain period.

The A/D conversion is done in a two-step method. During the first clock period, the MSB comparator bank compares the V<sub>IN</sub> with the reference voltage string in order to determine in which subrange the exact V<sub>IN</sub> lies. During the subsequent clock period, an LSB comparator bank compares a subrange of the V<sub>REF</sub> to the V<sub>IN</sub>. Thus, the reference inputs have to be stable during two compare cycles. This implies that while the ADC is clocked with FS, the conversion only occurs at a rate of FS/2. Every second sample and resulting data must be discarded because the reference changes during its conversion.

The reference inputs V<sub>RT</sub> and V<sub>RB</sub> have to have settled to within 1 LSB, at least 50 ns before the rising edge which occurs after the sampling instant. The reference has to be kept constant until ( $t_{AP}$  + 10 ns) after the second rising edge. See *Figure 7.* for timing details. The digital data of the N + 1, N + 3, N + 5 etc. samples are invalid if the reference is changed every second clock cycle. The data for the N, N + 2, N + 4 etc. samples are valid.

# LINEARITY DEFINITION

#### The Ideal ADC

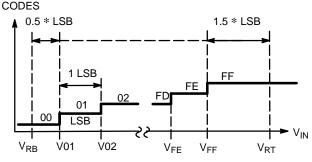

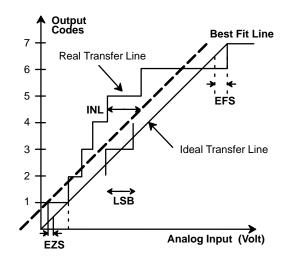

The transfer function for an ideal A/D converter is shown in Figure 8.

#### Figure 8. Ideal A/D Transfer Function

The first transition for the data bits takes place when:

$V_{IN} = V01 = V_{RB} + 0.5 * LSB$

The last transition of the data bits takes place when:

$V_{IN} = V_{FF} = V_{RT} - 1.5 * LSB$ where: LSB =  $V_{REF}$  / 256 = (V<sub>FF</sub> - V01) / 254  $V_{RFF} = (V_{RT} - V_{RB})$ and

# The Real ADC

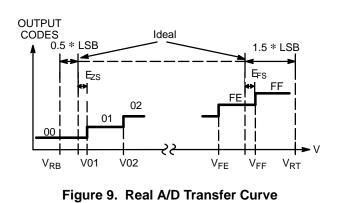

In a "real" converter, the code-to-code transitions do not fall exactly every V<sub>REF</sub>/256 volts.

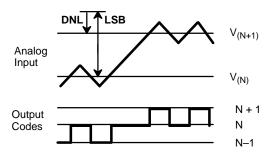

A positive DNL (Differential Non Linearity) error means that the real width of a particular code is larger than 1 LSB. This error is measured in fractions of LSBs.

A specification of Max DNL = +0.5 LSB means that all codes are within 0.5 LSB and 1.5 LSB. For example, if  $V_{REF} = 4.096 V$ then 1 LSB = 16mV and every code width is between 8 and 24 mV.

#### Figure 10. DNL Measurement

The formulas for Differential Non-linearity (DNL), Integral Non-Linearity (INL) are:

DNL (01) = V02 - V01 - LSB

: : :

$DNL (FE) = V_{FF} - V_{FE} - LSB$ Thus  $DNL_{(N)} = [V_{(N+1)} - V_{(N)}] - LSB$

Code Width (N) =  $V_{(N+1)} - V_{(N)}$

Similarly, the zero scale and full scale errors are defined as:

EFS (full scale error) =  $V_{FF} - (V_{RT} - 1.5 * LSB)$ EZS (zero scale error) =  $V01 - (V_{RB} + 0.5 * LSB)$

where:  $LSB = [V_{RT} - V_{RB}] / 256$

Figure 9. shows the zero scale and full scale error terms while Figure 10. shows the definition of DNL.

Figure 11. INL Error Calculation (3-Bit)

Figure 11. gives a visual definition of the INL error. The graph shows a 3-bit converter transfer curve with greatly exaggerated DNL errors to show the deviation of the real transfer curve from the ideal one.

After a tester has measured all the transition voltages, a line is drawn parallel to the ideal transfer line. By definition the best fit line makes equal the positive and and the negative INL errors. This may change an INL of -1 to +2 LSBs relative to the ideal line into a ±1.5 relative to the best fit line.

# PERFORMANCE CHARACTERISTICS

Graph 1. DNL vs. Sampling Frequency

Graph 3. DNL vs. Reference Voltage

Graph 2. INL vs. Sampling Frequency

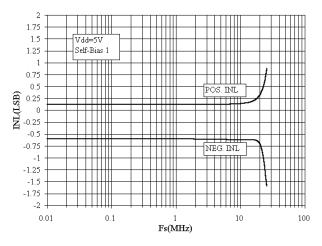

Graph 4. Supply Current vs. Sampling Frequency

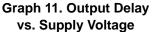

vs. Temperature

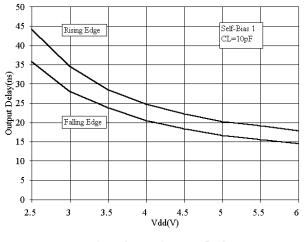

vs. Supply Voltage

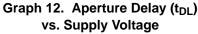

Graph 10. 3-State/Enable Delay vs. Temperature

Graph 14. Gain vs. Input Frequency

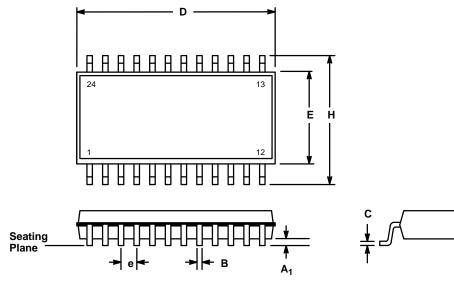

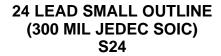

# 24 LEAD SMALL OUTLINE PACKAGE (300 MIL EIAJ SOIC) RN24

|                | MILLIN | METERS | INC   | CHES  |

|----------------|--------|--------|-------|-------|

| SYMBOL         | MIN    | МАХ    | MIN   | MAX   |

| A <sub>2</sub> | 1.7    | 1.9    | 0.067 | 0.075 |

| A <sub>1</sub> | 0.0    | 0.1    | 0.000 | 0.004 |

| В              | 0.3    | 0.5    | 0.012 | 0.02  |

| С              | 0.1    | 0.25   | 0.004 | 0.01  |

| D              | 14.9   | 15.5   | 0.588 | 0.608 |

| E              | 5.2    | 5.6    | 0.205 | 0.221 |

| е              | 1.2    | 7 BSC  | 0.0   | 5 BSC |

| н              | 7.5    | 8.1    | 0.297 | 0.317 |

| L              | 0.3    | 0.7    | 0.012 | 0.028 |

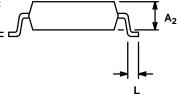

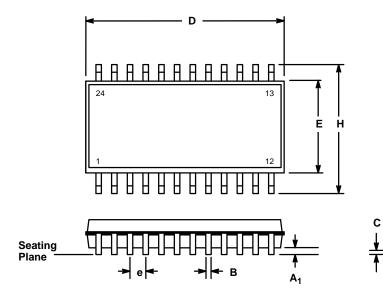

# 24 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP) NN24

|                    | INC       | HES   | MILLIN | <b>IETERS</b> |

|--------------------|-----------|-------|--------|---------------|

| SYMBOL             | MIN       | MAX   | MIN    | МАХ           |

| А                  |           | 0.200 |        | 5.08          |

| A <sub>1</sub>     | 0.015     |       | 0.38   | _             |

| В                  | 0.014     | 0.023 | 0.356  | 0.584         |

| B <sub>1</sub> (1) | 0.038     | 0.065 | 0.965  | 1.65          |

| С                  | 0.008     | 0.015 | 0.203  | 0.381         |

| D                  | 1.16      | 1.280 | 29.46  | 32.51         |

| Е                  | 0.295     | 0.325 | 7.49   | 8.26          |

| E <sub>1</sub>     | 0.220     | 0.310 | 5.59   | 7.87          |

| е                  | 0.100 BSC |       | 2.5    | 4 BSC         |

| L                  | 0.115     | 0.150 | 2.92   | 3.81          |

| α                  | 0°        | 15°   | 0°     | 15°           |

| Q <sub>1</sub>     | 0.055     | 0.070 | 1.40   | 1.78          |

| S                  | 0.028     | 0.098 | 0.711  | 2.49          |

Note: (1) The minimum limit for dimensions B1 may be 0.023" (0.58 mm) for all four corner leads only.

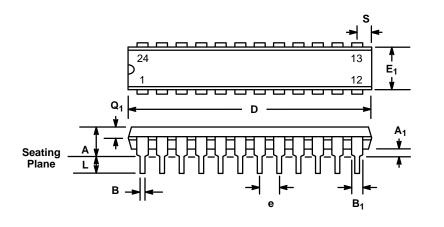

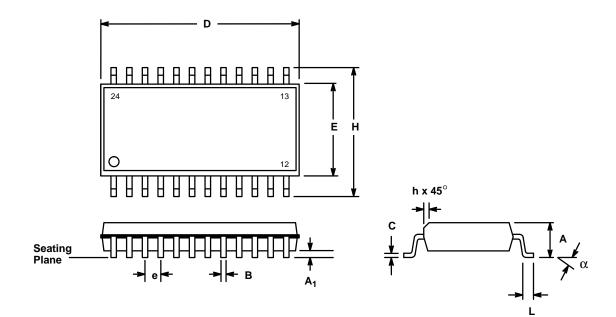

|        | INC    | CHES   | MILLIN | <b>IETERS</b> |

|--------|--------|--------|--------|---------------|

| SYMBOL | MIN    | МАХ    | MIN    | MAX           |

| А      | 0.097  | 0.104  | 2.464  | 2.642         |

| A1     | 0.0050 | 0.0115 | 0.127  | 0.292         |

| В      | 0.014  | 0.019  | 0.356  | 0.483         |

| С      | 0.0091 | 0.0125 | 0.231  | 0.318         |

| D      | 0.602  | 0.612  | 15.29  | 15.54         |

| E      | 0.292  | 0.299  | 7.42   | 7.59          |

| е      | 0.0    | 50 BSC | 1.2    | 7 BSC         |

| Н      | 0.400  | 0.410  | 10.16  | 10.41         |

| h      | 0.010  | 0.016  | 0.254  | 0.406         |

| L      | 0.016  | 0.035  | 0.406  | 0.889         |

| α      | 0°     | 8°     | 0°     | 8°            |

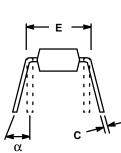

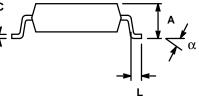

# 24 LEAD SHRINK SMALL OUTLINE PACKAGE (SSOP) A24

|                | MILLIN | <b>IETERS</b> | INC   | CHES   |

|----------------|--------|---------------|-------|--------|

| SYMBOL         | MIN    | МАХ           | MIN   | MAX    |

| А              | 1.73   | 2.05          | 0.068 | 0.081  |

| A <sub>1</sub> | 0.05   | 0.21          | 0.002 | 0.008  |

| В              | 0.20   | 0.40          | 0.008 | 0.016  |

| С              | 0.13   | 0.25          | 0.005 | 0.010  |

| D              | 8.07   | 8.40          | 0.318 | 0.331  |

| Е              | 5.20   | 5.38          | 0.205 | 0.212  |

| е              | 0.65 I | BSC           | 0.02  | 56 BSC |

| н              | 7.65   | 8.1           | 0.301 | 0.319  |

| L              | 0.45   | 0.95          | 0.018 | 0.037  |

| α              | 0°     | 8°            | 0°    | 8°     |

**Notes**

## NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1994 EXAR Corporation Datasheet April 1995 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.