## Designer's™ Data Sheet

# NPN Silicon Power Transistor 1 kV SWITCHMODE Series

These transistors are designed for high–voltage, high–speed, power switching in inductive circuits where fall time is critical. They are particularly suited for line–operated switchmode applications.

Typical Applications:

- Switching Regulators

- Inverters

- Solenoids

- Relay Drivers

- Motor Controls

- Deflection Circuits

Features:

- Collector–Emitter Voltage V<sub>CEV</sub> = 1000 Vdc

- Fast Turn-Off Times

80 ns Inductive Fall Time — 100°C (Typ) 120 ns Inductive Crossover Time — 100°C (Typ) 800 ns Inductive Storage Time — 100°C (Typ)

• 100°C Performance Specified for:

Reverse–Biased SOA with Inductive Load Switching Times with Inductive Loads Saturation Voltages

Leakage Currents

- Extended FBSOA Rating Using Ultra–fast Rectifiers

- · Extremely High RBSOA Capability

#### **MAXIMUM RATINGS**

| Rating                                                                                                            | Symbol                            | Value          | Unit          |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|---------------|

| Collector–Emitter Voltage                                                                                         | VCEO                              | 500            | Vdc           |

| Collector–Emitter Voltage                                                                                         | VCEV                              | 1000           | Vdc           |

| Emitter-Base Voltage                                                                                              | V <sub>EB</sub>                   | 6              | Vdc           |

| Collector Current — Continuous<br>— Peak <sup>(1)</sup>                                                           | I <sub>C</sub>                    | 8<br>16        | Adc           |

| Base Current — Continuous<br>— Peak <sup>(1)</sup>                                                                | I <sub>B</sub>                    | 6<br>12        | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C<br>@ T <sub>C</sub> = 100°C<br>Derate above T <sub>C</sub> = 25°C | P <sub>D</sub>                    | 125<br>50<br>1 | Watts<br>W/°C |

| Operating and Storage Junction<br>Temperature Range                                                               | T <sub>J</sub> , T <sub>stg</sub> | -55 to 150     | °C            |

#### THERMAL CHARACTERISTICS

| Characteristic                                                        | Symbol          | Max | Unit |

|-----------------------------------------------------------------------|-----------------|-----|------|

| Thermal Resistance, Junction to Case                                  | $R_{\theta JC}$ | 1   | °C/W |

| Lead Temperature for Soldering Purposes: 1/8" from Case for 5 Seconds | TL              | 275 | °C   |

(1) Pulse Test: Pulse Width = 5 ms, Duty Cycle  $\leq$  10%.

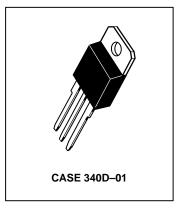

## **MJH16006A**

POWER TRANSISTORS

8 AMPERES

500 VOLTS

150 WATTS

**Designer's Data for "Worst Case" Conditions** — The Designer's Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit curves — representing boundaries on device characteristics — are given to facilitate "worst case" design.

Preferred devices are Motorola recommended choices for future use and best overall value.

Designer's and SWITCHMODE are trademarks of Motorola, Inc.

#### REV<sub>3</sub>

## MJH16006A

## **ELECTRICAL CHARACTERISTICS** ( $T_C = 25^{\circ}C$ unless otherwise noted)

|                                                               | Characteristic                                                                                                                                                     |                                 |                  | Min                   | Тур                  | Max             | Unit        |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|-----------------------|----------------------|-----------------|-------------|

| OFF CHARACTER                                                 | ISTICS(1)                                                                                                                                                          |                                 | •                | •                     | •                    |                 | •           |

| Collector–Emitter<br>(I <sub>C</sub> = 100 mA, I <sub>E</sub> | Sustaining Voltage (Table 1)<br>3 = 0)                                                                                                                             | VCEO(sus)                       | 500              | _                     | _                    | Vdc             |             |

|                                                               | r Cutoff Current<br><sub>V</sub> = 1000 Vdc, V <sub>BE</sub> (off) = 1.5 Vdc)<br><sub>V</sub> = 1000 Vdc, V <sub>BE</sub> (off) = 1.5 Vdc, T <sub>C</sub> = 100°C) |                                 |                  | _                     | 0.003<br>0.020       | 0.15<br>1.0     | mAdc        |

|                                                               | Collector Cutoff Current (V <sub>CE</sub> = 1000 Vdc, R <sub>BE</sub> = 50 Ω, T <sub>C</sub> = 100°C)                                                              |                                 |                  | _                     | 0.020                | 1.0             | mAdc        |

| Emitter Cutoff Cur<br>(VEB = 6 Vdc, Id                        |                                                                                                                                                                    |                                 |                  | _                     | 0.005                | 0.15            | mAdc        |

| SECOND BREAKD                                                 | OWN                                                                                                                                                                |                                 | •                | •                     | •                    |                 | •           |

| Second Breakdow                                               | n Collector Current with Bas                                                                                                                                       | se Forward Biased               | I <sub>S/b</sub> | See Figure 14a or 14b |                      |                 |             |

| Clamped Inductive SOA with Base Reverse Biased                |                                                                                                                                                                    |                                 | RBSOA            |                       | See Figure 15        |                 |             |

| ON CHARACTERIS                                                | STICS <sup>(1)</sup>                                                                                                                                               |                                 | •                | •                     |                      |                 |             |

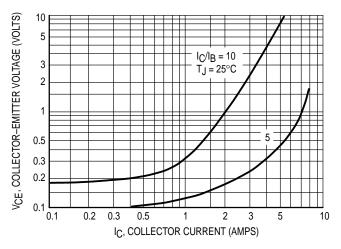

| (IC = 3 Adc, IB = 0)                                          |                                                                                                                                                                    |                                 | VCE(sat)         | _<br>_<br>_           | 0.35<br>0.50<br>0.60 | 0.7<br>1<br>1.5 | Vdc         |

| (I <sub>C</sub> = 5 Adc, I <sub>B</sub> =                     | Base–Emitter Saturation Voltage (I <sub>C</sub> = 5 Adc, I <sub>B</sub> = 1 Adc) (I <sub>C</sub> = 5 Adc, I <sub>B</sub> = 1 Adc, T <sub>C</sub> = 100°C)          |                                 | VBE(sat)         | <u> </u>              | 1<br>1               | 1.5<br>1.5      | Vdc         |

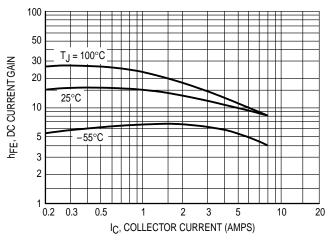

| DC Current Gain<br>(I <sub>C</sub> = 8 Adc, V <sub>C</sub>    |                                                                                                                                                                    |                                 | hFE              | 5                     | 8                    | _               | _           |

| DYNAMIC CHARA                                                 | CTERISTICS                                                                                                                                                         |                                 |                  |                       |                      |                 |             |

|                                                               | Output Capacitance<br>(V <sub>CB</sub> = 10 Vdc, I <sub>E</sub> = 0, f <sub>test</sub> = 1 kHz)                                                                    |                                 |                  | _                     | _                    | 350             | pF          |

| SWITCHING CHAR                                                | ACTERISTICS                                                                                                                                                        |                                 | -                |                       |                      |                 |             |

| Inductive Load (Ta                                            | able 1)                                                                                                                                                            |                                 |                  |                       |                      |                 |             |

| Storage Time                                                  |                                                                                                                                                                    |                                 | t <sub>SV</sub>  | _                     | 800                  | 2000            | ns          |

| Fall Time                                                     | 1                                                                                                                                                                  | (T <sub>J</sub> = 100°C)        | t <sub>fi</sub>  | _                     | 80                   | 200             | ]           |

| Crossover Time                                                | I <sub>C</sub> = 5 Adc,<br>I <sub>B1</sub> = 0.66 Adc,                                                                                                             |                                 | t <sub>C</sub>   | _                     | 120                  | 300             |             |

| Storage Time                                                  | VBE(off) = 5 Vdc,<br>VCE(pk) = 400 Vdc)                                                                                                                            | (T <sub>J</sub> = 150°C)        | t <sub>sv</sub>  | _                     | 1000                 | _               |             |

| Fall Time                                                     |                                                                                                                                                                    |                                 | t <sub>fi</sub>  | _                     | 90                   | _               |             |

| Crossover Time                                                |                                                                                                                                                                    |                                 | t <sub>C</sub>   | _                     | 150                  | _               |             |

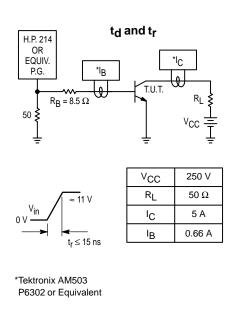

| Resistive Load (Ta                                            | able 2)                                                                                                                                                            | •                               | •                |                       | •                    |                 | •           |

| Delay Time                                                    | $(I_{C} = 5 \text{ Adc}, \\ V_{CC} = 250 \text{ Vdc}, \\ I_{B1} = 0.66 \text{ Adc}, \\ PW = 30 \mu\text{s}, \\ Duty \text{ Cycle} \leq 2\%)$                       |                                 | t <sub>d</sub>   | _                     | 25                   | 100             | ns          |

| Rise Time                                                     |                                                                                                                                                                    | (I <sub>B2</sub> = 1.3 Adc,     | t <sub>r</sub>   | _                     | 400                  | 700             | -<br>-<br>- |

| Storage Time                                                  |                                                                                                                                                                    | $R_{B1} = R_{B2} = 4 \Omega$    | t <sub>S</sub>   | _                     | 1400                 | 3000            |             |

| Fall Time                                                     |                                                                                                                                                                    |                                 | t <sub>f</sub>   | _                     | 175                  | 400             |             |

| Storage Time                                                  |                                                                                                                                                                    | (\\n=\(\mu_0 = 5\\do\)          | t <sub>S</sub>   | _                     | 475                  | _               | 1           |

| Fall Time                                                     | 1                                                                                                                                                                  | $(V_{BE(off)} = 5 \text{ Vdc})$ | t <sub>f</sub>   | _                     | 100                  | _               | ]           |

<sup>(1)</sup> Pulse Test: PW = 300  $\mu$ s, Duty Cycle  $\leq$  2%.

#### TYPICAL STATIC CHARACTERISTICS

Figure 1. DC Current Gain

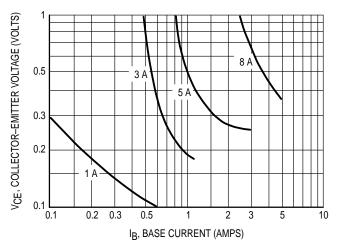

Figure 2. Collector-Emitter Saturation Region

Figure 3. Collector-Emitter Saturation Region

Figure 4. Base-Emitter Saturation Region

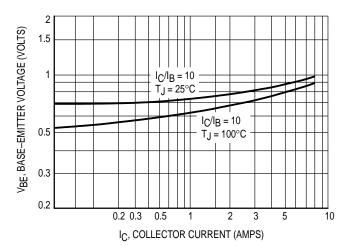

Figure 5. Capacitance

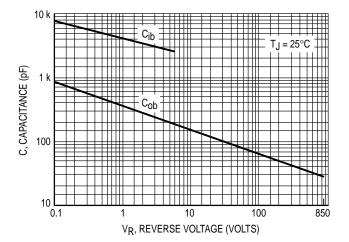

#### TYPICAL INDUCTIVE SWITCHING CHARACTERISTICS

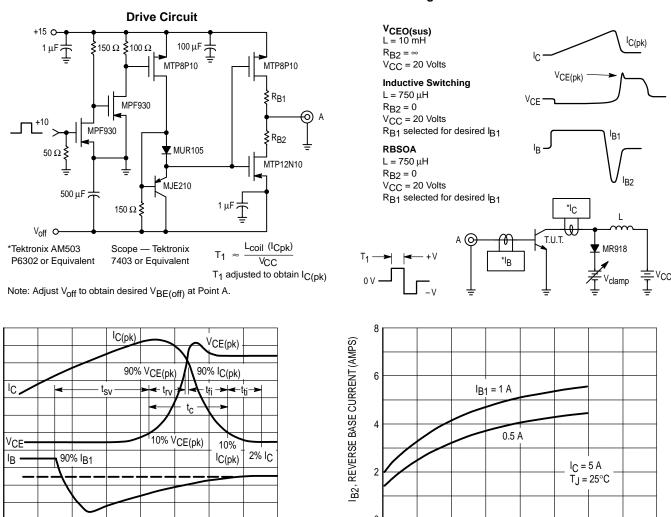

#### **Table 1. Inductive Load Switching**

Figure 12. Inductive Switching Measurements

t, TIME

Figure 13. Peak Reverse Base Current

VBE(off), REVERSE BASE VOLTAGE (VOLTS)

0

5

#### **GUARANTEED SAFE OPERATING AREA LIMITS**

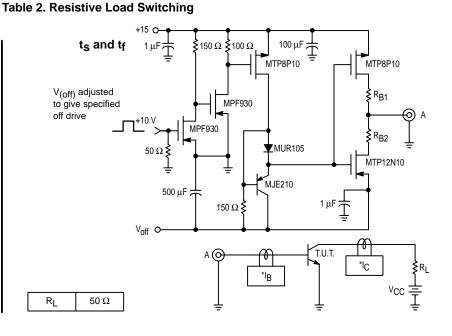

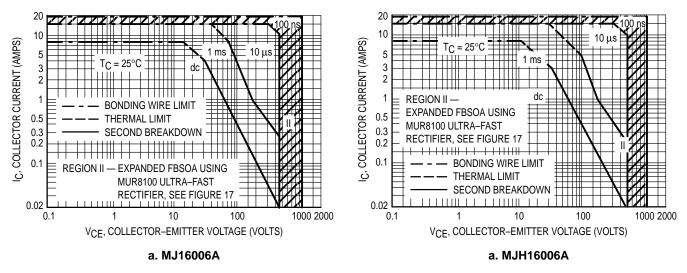

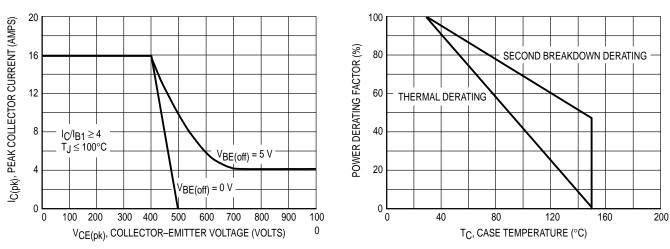

Figure 14. Maximum Rated Forward Biased Safe Operating Area

Figure 15. Maximum Reverse Biased Safe Operating Area

Figure 16. Power Derating

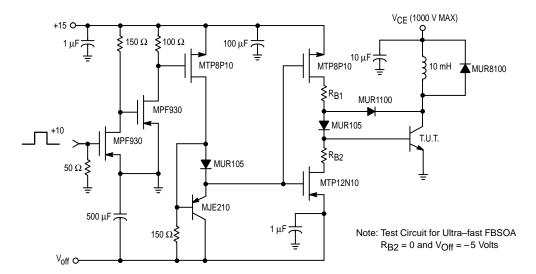

Figure 17. Switching Safe Operating Area

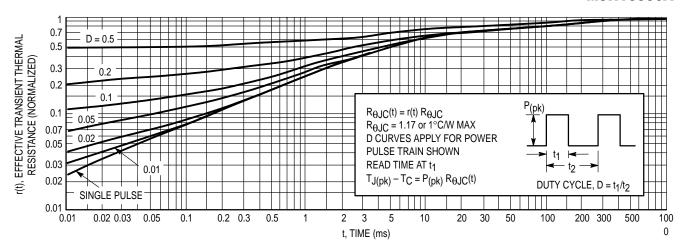

Figure 18. Thermal Response

#### SAFE OPERATING AREA INFORMATION

#### **FORWARD BIAS**

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate  $I_C - V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

The data of Figures 14a and 14b is based on  $T_C = 25\,^{\circ}C$ ;  $T_{J(pk)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \geq 25\,^{\circ}C$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Figures 14a and 14b may be found at any case temperature by using the appropriate curve on Figure 16.

$T_{J(pk)}$  may be calculated from the data in Figure 18. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

#### **REVERSE BIAS**

For inductive loads, high voltage and high current must be sustained simultaneously during turn–off, in most cases, with the base–to–emitter junction reverse biased. Under these conditions the collector voltage must be held to a safe level at or below a specific value of collector current. This can be accomplished by several means such as active clamping, RC snubbing, load line shaping, etc. The safe level for these devices is specified as Reverse Biased Safe Operating Area and represents the voltage current condition allowable during reverse biased turnoff. This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode. Figure 15 gives the RBSOA characteristics.

#### **SWITCHMODE III DESIGN CONSIDERATIONS**

#### 1. FBSOA —

Allowable dc power dissipation in bipolar power transistors decreases dramatically with increasing collector emitter

voltage. A transistor which safely dissipates 100 watts at 10 volts will typically dissipate less than 10 watts at its rated VCEO(sus). From a power handling point of view, current and voltage are not interchangeable (see Application Note AN875).

#### 2. TURN-ON -

Safe turn–on load line excursions are bounded by pulsed FBSOA curves. The 10 µs curve applies for resistive loads, most capacitive loads, and inductive loads that are clamped by standard or fast recovery rectifiers. Similarly, the 100 ns curve applies to inductive loads which are clamped by ultra–fast recovery rectifiers, and are valid for turn–on crossover times less than 100 ns (see Application Note AN952).

At voltages above 75% of VCEO(sus), it is essential to provide the transistor with an adequate amount of base drive VERY RAPIDLY at turn—on. More specifically, safe operation according to the curves is dependent upon base current rise time being less than collector current rise time. As a general rule, a base drive compliance voltage in excess of 10 volts is required to meet this condition (see Application Note AN875).

#### 3. TURN-OFF -

A bipolar transistor's ability to withstand turn-off stress is dependent upon its forward base drive. Gross overdrive violates the RBSOA curve and risks transistor failure. For this reason, circuits which use fixed base drive are often more likely to fail at light loads due to heavy overdrive (see Application Note AN875).

### 4. OPERATION ABOVE VCEO(sus) -

When bipolars are operated above collector-emitter breakdown, base drive is crucial. A rapid application of adequate forward base current is needed for safe turn-on, as is a stiff negative bias needed for safe turn-off. Any hiccup in the base-drive circuitry that even momentarily violates either of these conditions will likely cause the transistor to fail. Therefore, it is important to design the driver so that its output is negative in the absence of anything but a clean crisp input signal (see Application Note AN952).

#### **SWITCHMODE DESIGN CONSIDERATIONS (Cont.)**

#### 5. RBSOA —

Reverse Biased Safe Operating Area has a first order dependency on circuit configuration and drive parameters. The RBSOA curves in this data sheet are valid only for the conditions specified. For a comparison of RBSOA results in several types of circuits (see Application Note AN951).

#### 6. DESIGN SAMPLES —

Transistor parameters tend to vary much more from wafer lot to wafer lot, over long periods of time, than from one de-

vice to the next in the same wafer lot. For design evaluation it is advisable to use transistors from several different date codes.

#### 7. BAKER CLAMPS —

Many unanticipated pitfalls can be avoided by using Baker Clamps. MUR105 and MUR1100 diodes are recommended for base drives less than 1 amp. Similarly, MUR405 and MUR4100 types are well–suited for higher drive requirements (see Article Reprint AR131).

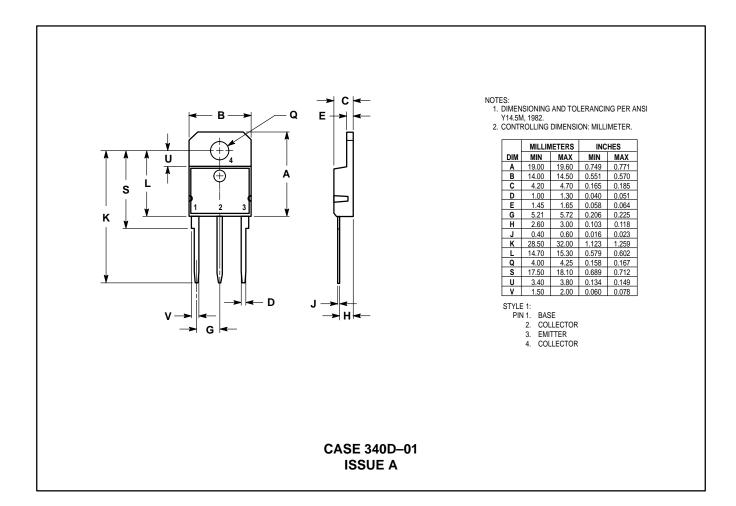

#### **PACKAGE DIMENSIONS**

#### MJH16006A

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and Employer.

How to reach us:

**USA/EUROPE**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design\_NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, Toshikatsu Otsuki, 6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 03-3521-8315

**HONG KONG:** Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298