# Designer's™ Data Sheet

# **NPN Silicon Power Transistors SWITCHMODE Bridge Series**

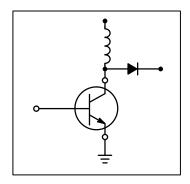

- . . . specifically designed for use in half bridge and full bridge off line converters.

- Excellent Dynamic Saturation Characteristics

- Rugged RBSOA Capability

- Collector–Emitter Sustaining Voltage V<sub>CEO(sus)</sub> 400 V

- Collector–Emitter Breakdown V<sub>(BR)</sub>CES 650 V

- State-of-Art Bipolar Power Transistor Design

- · Fast Inductive Switching:

$t_{fi} = 25 \text{ ns (Typ)} @ 100^{\circ}\text{C}$

$t_C = 50 \text{ ns (Typ)} @ 100^{\circ}C$

$t_{SV} = 1 \mu s (Typ) @ 100^{\circ}C$

- Ultrafast FBSOA Specified

- 100°C Performance Specified for:

**RBSOA**

Inductive Load Switching

Saturation Voltages

Leakages

#### **MAXIMUM RATINGS**

| Rating                                                                                         | Symbol                            | MJ16110         | MJW16110          | Unit          |

|------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-------------------|---------------|

| Collector–Emitter Sustaining Voltage                                                           | VCEO(sus)                         | 400             |                   | Vdc           |

| Collector–Emitter Breakdown Voltage                                                            | VCES                              | 65              | 650               |               |

| Emitter–Base Voltage                                                                           | VEBO                              | 6               |                   | Vdc           |

| Collector Current — Continuous<br>— Pulsed (1)                                                 | I <sub>CM</sub>                   | 15<br>20        |                   | Adc           |

| Base Current — Continuous<br>— Pulsed (1)                                                      | I <sub>B</sub>                    | 10<br>15        |                   | Adc           |

| Total Power Dissipation  @ T <sub>C</sub> = 25°C  @ T <sub>C</sub> = 100°C  Derated above 25°C | PD                                | 175<br>100<br>1 | 135<br>54<br>1.09 | Watts<br>W/°C |

| Operating and Storage Temperature                                                              | T <sub>J</sub> , T <sub>stg</sub> | -65 to 200      | -55 to 150        | °C            |

#### THERMAL CHARACTERISTICS

| Thermal Resistance — Junction to Case                                        | R <sub>θ</sub> JC | 1  | 0.92 | °C/W |

|------------------------------------------------------------------------------|-------------------|----|------|------|

| Maximum Lead Temperature for Soldering Purposes 1/8" from Case for 5 Seconds | TL                | 27 | 75   | °C   |

(1) Pulse Test: Pulse Width = 5 ms, Duty Cycle ≤ 10%.

# **MJ16110\*** MJW16110\*

\*Motorola Preferred Device

**POWER TRANSISTORS 15 AMPERES 400 VOLTS** 175 AND 135 WATTS

Designer's Data for "Worst Case" Conditions — The Designer's Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit curves — representing boundaries on device characteristics — are given to facilitate "worst case" design.

Preferred devices are Motorola recommended choices for future use and best overall value.

Designer's and SWITCHMODE are trademarks of Motorola Inc.

#### REV<sub>1</sub>

### MJ16110 MJW16110

## **ELECTRICAL CHARACTERISTICS** (T $_{C}$ = 25 $^{\circ}$ C unless otherwise noted)

| Characteristic                                                                                                                                                                        |                                                                                              | Symbol                          | Min              | Тур                      | Max                      | Unit |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------|------------------|--------------------------|--------------------------|------|------|

| OFF CHARACTERIS                                                                                                                                                                       | STICS (1)                                                                                    |                                 |                  |                          |                          |      |      |

| Collector–Emitter Sustaining Voltage (Table 1) (I <sub>C</sub> = 20 mAdc, I <sub>B</sub> = 0)                                                                                         |                                                                                              |                                 | VCEO(sus)        | 400                      | _                        | _    | Vdc  |

| Collector Cutoff Current (VCE = 650 Vdc, VBE(off) = 1.5 V) (VCE = 650 Vdc, VBE(off) = 1.5 V, T <sub>C</sub> = 100°C)                                                                  |                                                                                              | ICEV                            | _<br>_           |                          | 100<br>1000              | μAdc |      |

| Collector Cutoff Cui                                                                                                                                                                  | rrent (V <sub>CE</sub> = 650 Vdc, R <sub>BE</sub> =                                          | = 50 Ω, T <sub>C</sub> = 100°C) | ICER             |                          | _                        | 1000 | μAdc |

| Emitter-Base Leak                                                                                                                                                                     | age (V <sub>EB</sub> = 6 Vdc, I <sub>C</sub> = 0)                                            |                                 | I <sub>EBO</sub> |                          | _                        | 10   | μAdc |

| ON CHARACTERIST                                                                                                                                                                       | TICS (1)                                                                                     |                                 | •                |                          |                          |      |      |

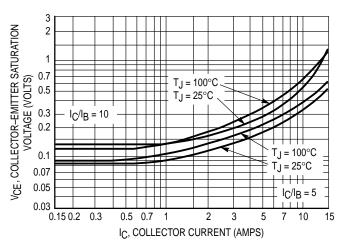

| Collector–Emitter Saturation Voltage (IC = 5 Adc, IB = 0.5 Adc) (IC = 10 Adc, IB = 1.2 Adc) (IC = 10 Adc, IB = 2 Adc) (IC = 10 Adc, IB = 2 Adc) (IC = 10 Adc, IB = 2 Adc, IC = 100°C) |                                                                                              | VCE(sat)                        | _<br>_<br>_<br>_ | 0.3<br>0.7<br>0.3<br>0.4 | 0.9<br>2.0<br>1.0<br>1.5 | Vdc  |      |

| Base–Emitter Saturation Voltage (I <sub>C</sub> = 10 Adc, I <sub>B</sub> = 2 Adc) (I <sub>C</sub> = 10 Adc, I <sub>B</sub> = 2 Adc, T <sub>C</sub> = 100°C)                           |                                                                                              | V <sub>BE</sub> (sat)           |                  | 1.2<br>1.2               | 1.5<br>1.5               | Vdc  |      |

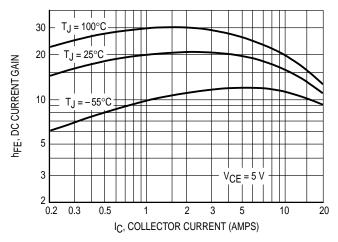

| DC Current Gain (Id                                                                                                                                                                   | C = 15 Adc, V <sub>CE</sub> = 5 Vdc)                                                         |                                 | hFE              | 6                        | 12                       | 20   | _    |

| DYNAMIC CHARAC                                                                                                                                                                        | TERISTICS                                                                                    |                                 |                  |                          |                          |      |      |

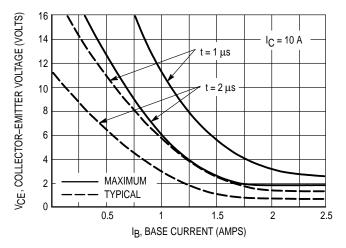

| Dynamic Saturation                                                                                                                                                                    |                                                                                              | VCE(dsat)                       | See Fig          | Figures 11, 12, and 13   |                          | V    |      |

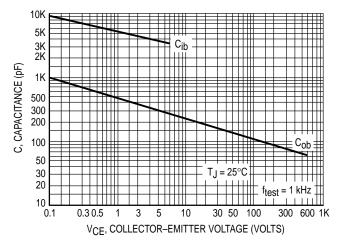

| Output Capacitance                                                                                                                                                                    | Output Capacitance (V <sub>CE</sub> = 10 Vdc, I <sub>E</sub> = 0, f <sub>test</sub> = 1 kHz) |                                 | C <sub>ob</sub>  | _                        | _                        | 400  | pF   |

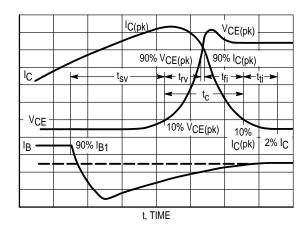

| SWITCHING CHARA                                                                                                                                                                       | ACTERISTICS                                                                                  |                                 |                  |                          |                          |      |      |

| Inductive Load (Ta                                                                                                                                                                    | able 1)                                                                                      |                                 |                  |                          |                          |      |      |

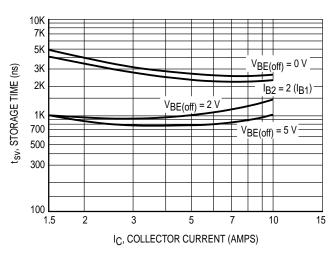

| Storage                                                                                                                                                                               |                                                                                              |                                 | t <sub>SV</sub>  | _                        | 700                      | 1500 | ns   |

| Crossover                                                                                                                                                                             |                                                                                              | T <sub>J</sub> = 25°C           | t <sub>C</sub>   | _                        | 45                       | 150  |      |

| Fall Time                                                                                                                                                                             | $I_C = 10 \text{ A}, I_{B1} = 1 \text{ A},$                                                  |                                 | tfi              | _                        | 20                       | 75   |      |

| Storage                                                                                                                                                                               | $V_{BE(off)} = 5 \text{ V},$<br>$V_{CE(pk)} = 250 \text{ V}$                                 |                                 | t <sub>sv</sub>  | _                        | 1000                     | 2000 |      |

| Crossover                                                                                                                                                                             | - 02(βιί)                                                                                    | $T_J = 100^{\circ}C$            | t <sub>C</sub>   | _                        | 50                       | 200  |      |

| Fall Time                                                                                                                                                                             |                                                                                              |                                 | t <sub>fi</sub>  |                          | 25                       | 125  |      |

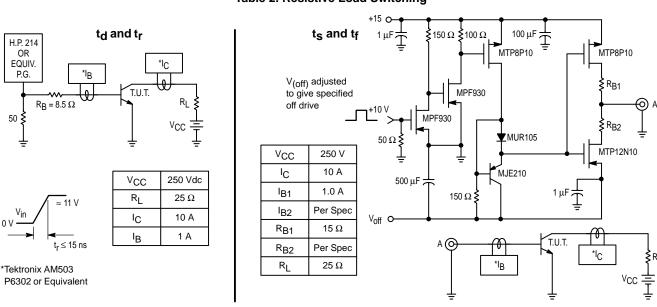

| Resistive Load (Ta                                                                                                                                                                    | able 2)                                                                                      |                                 | •                |                          | -                        |      | -    |

| Delay Time                                                                                                                                                                            |                                                                                              |                                 | t <sub>d</sub>   | _                        | 15                       | _    | ns   |

| Rise Time                                                                                                                                                                             |                                                                                              | I <sub>B2</sub> = 2 A,          | t <sub>r</sub>   | _                        | 330                      | _    | 1    |

| Storage Time                                                                                                                                                                          |                                                                                              | t <sub>S</sub>                  | _                | 800                      | _                        | 1    |      |

| Fall Time                                                                                                                                                                             |                                                                                              |                                 | t <sub>f</sub>   | _                        | 110                      | _    | 1    |

| Storage Time                                                                                                                                                                          |                                                                                              | Vp=( m = 5 \/                   | t <sub>S</sub>   | _                        | 500                      | _    |      |

| Fall Time                                                                                                                                                                             |                                                                                              | t <sub>f</sub>                  | _                | 250                      | _                        |      |      |

<sup>(1)</sup> Pulse Test: Pulse Width = 300  $\mu$ s, Duty Cycle  $\leq$  2%.

### TYPICAL STATIC CHARACTERISTICS

Figure 1. DC Current Gain

Figure 2. Collector-Emitter Saturation Voltage

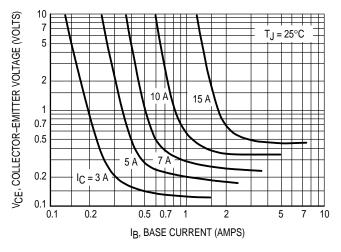

Figure 3. Collector-Emitter Saturation Region

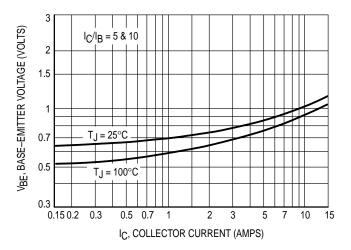

Figure 4. Base-Emitter Saturation Region

Figure 5. Capacitance

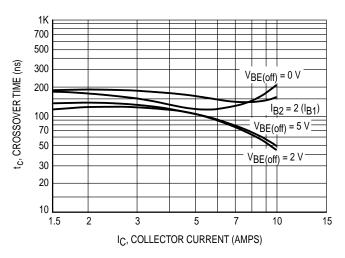

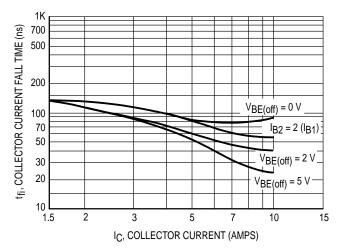

### TYPICAL INDUCTIVE SWITCHING CHARACTERISTICS

$$I_{C}/I_{B} = 10$$

,  $T_{C} = 100^{\circ}C$ ,  $V_{CE(pk)} = 250 \text{ V}$

Figure 6. Storage Time

Figure 7. Crossover Time

Figure 8. Fall Time

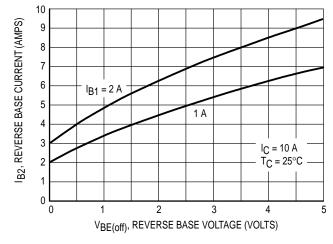

Figure 10. Peak Reverse Base Current

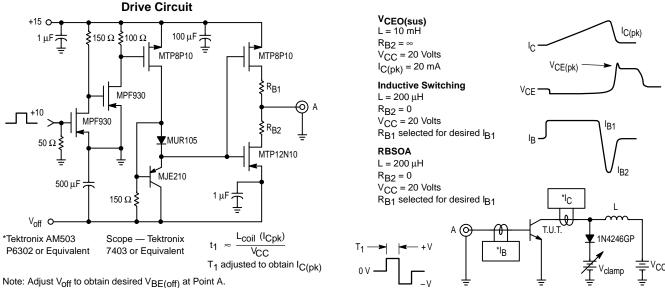

#### **Table 1. Inductive Load Switching**

**Table 2. Resistive Load Switching**

Figure 12. Dynamic Saturation Voltage

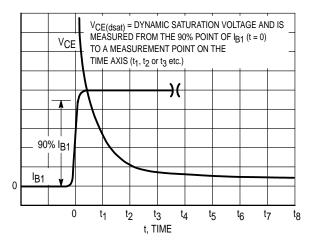

#### DYNAMIC SATURATION VOLTAGE

For bipolar power transistors low DC saturation voltages are achieved by conductivity modulating the collector region. Since conductivity modulation takes a finite amount of time, DC saturation voltages are not achieved instantly at turn–on. In bridge circuits, two transistor forward converters, and two transistor flyback converters dynamic saturation characteristics are responsible for the bulk of dynamic losses. The MJ16110 has been designed specifically to minimize these losses. Performance is roughly four times better than the original version of MJ16010.

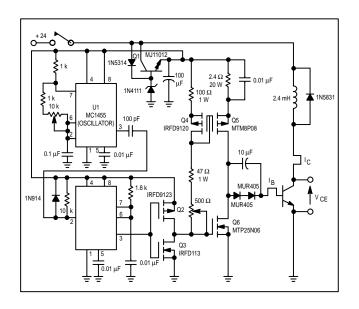

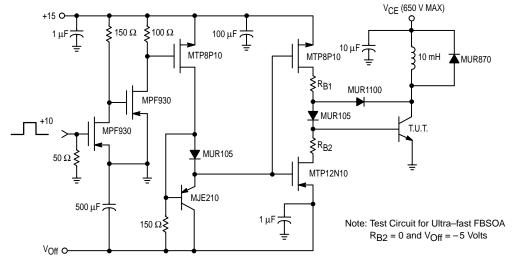

From a measurement point of view, dynamic saturation voltage is defined as collector—emitter voltage at a specific point in time after  $I_{B1}$  has been applied, where t=0 is the 90% point on the  $I_{B1}$  rise time waveform, This definition is illustrated in Figure 11. Performance data was taken in the circuit that is shown in Figure 13. The 24 volt rail allows a Tektronix 2445 or equivalent scope to operate at 1 volt per division without input amplifier saturation.

Dynamic saturation performance is illustrated in Figure 12. The MJ16110 reaches DC saturation levels in approximately 2  $\mu$ s, provided that sufficient base drive is provided. The dependence of dynamic saturation voltage upon base drive suggests a spike of IB1 at turn—on to minimize dynamic saturation losses, and also avoid overdrive at turn—off. However, in order to simulate worst case conditions the guaranteed dynamic saturation limits in this data sheet are specified with a constant level of IB1.

Figure 13. Dynamic Saturation Test Circuit

#### **GUARANTEED SAFE OPERATING AREA INFORMATION**

Figure 14. Forward Bias Safe Operating Area

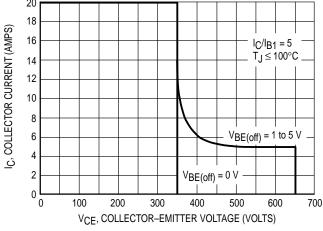

Figure 15. Reverse Bias Safe Operating Area

Figure 16. Switching Safe Operating Area

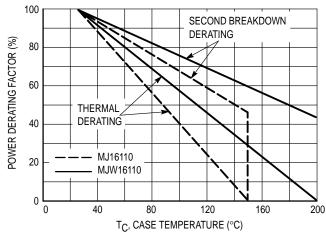

Figure 17. Power Derating

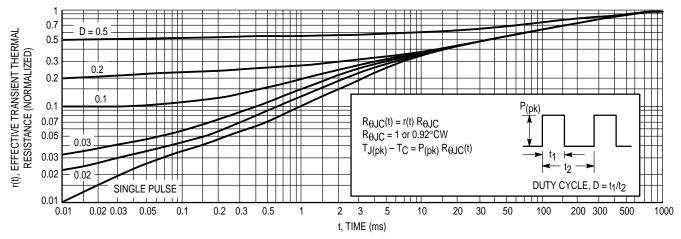

Figure 18. Thermal Response

### SAFE OPERATING AREA INFORMATION

#### **FORWARD BIAS**

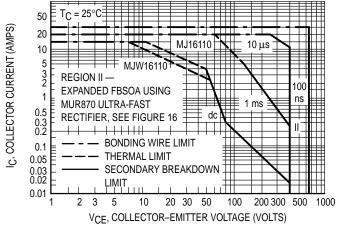

There are two limitations on the power handling ability of a transistor: average junction temperature and second breakdown. Safe operating area curves indicate  $I_C - V_{CE}$  limits of the transistor that must be observed for reliable operation; i.e., the transistor must not be subjected to greater dissipation than the curves indicate.

The data in Figure 14 is based on  $T_C = 25^{\circ}C$ ;  $T_{J(pk)}$  is variable depending on power level. Second breakdown pulse limits are valid for duty cycles to 10% but must be derated when  $T_C \ge 25^{\circ}C$ . Second breakdown limitations do not derate the same as thermal limitations. Allowable current at the voltages shown on Figure 14 may be found at any case temperature by using the appropriate curve on Figure 17.

$T_{J(pk)}$  may be calculated from the data in Figure 18. At high case temperatures, thermal limitations will reduce the power that can be handled to values less than the limitations imposed by second breakdown.

#### **REVERSE BIAS**

For inductive loads, high voltage and high current must be sustained simultaneously during turn-off, in most cases, with the base-to-emitter junction reverse biased. Under these conditions the collector voltage must be held to a safe level at or below a specific value of collector current. This can be

accomplished by several means such as active clamping, RC snubbing, load line shaping, etc. The safe level for these devices is specified as Reverse Biased Safe Operating Area and represents the voltage–current condition allowable during reverse biased turn–off. This rating is verified under clamped conditions so that the device is never subjected to an avalanche mode. Figure 15 gives the RBSOA characteristics.

#### SWITCHMODE DESIGN CONSIDERATIONS

#### **FBSOA**

Allowable dc power dissipation in bipolar power transistors decreases dramatically with increasing collector–emitter voltage. A transistor which safely dissipates 100 watts at 10 volts will typically dissipate less than 10 watts at its rated V(BR)CEO(sus). From a power handling point of view, current and voltage are not interchangeable (see Application Note AN875).

#### TURN-ON

Safe turn–on load line excursions are bounded by pulsed FBSOA curves. The 10 µs curve applies for resistive loads, most capacitive loads, and inductive loads that are clamped by standard or fast recovery rectifiers. Similarly, the 100 ns curve applies to inductive loads which are clamped by ultra–fast recovery rectifiers, and are valid for turn–on crossover times less than 100 ns (AN952).

### **SWITCHMODE DESIGN CONSIDERATIONS (Cont.)**

At voltages above 75% of V(BR)CEO(sus), it is essential to provide the transistor with an adequate amount of base drive VERY RAPIDLY at turn–on. More specifically, safe operation according to the curves is dependent upon base current rise time being less than collector current rise time. As a general rule, a base drive compliance voltage in excess of 10 volts is required to meet this condition (see Application Note AN875).

#### TURN-OFF

A bipolar transistor's ability to withstand turn-off stress is dependent upon its forward base drive. Gross overdrive violates the RBSOA curve and risks transistor failure. For this reason, circuits which use fixed base drive are more likely to fail at light loads due to heavy overdrive (see Application Note AN875).

## OPERATION ABOVE V(BR)CEO(sus)

When bipolars are operated above collector—emitter breakdown, base drive is crucial. A rapid application of adequate forward base current is needed for safe turn—on, as is a stiff negative bias needed for safe turn—off. Any hiccup in the base—drive circuitry that even momentarily violates either of these conditions will likely cause the transistor to fail.

Therefore, it is important to design the driver so that its output is negative in the absence of anything but a clean crisp input signal (see Application Note AN952).

#### **RBSOA**

Reversed Biased Safe Operating Area has a first order dependency on circuit configuration and drive parameters. The RBSOA curves in this data sheet are valid only for the conditions specified. For a comparison of RBSOA results in several types of circuits (see Application Note AN951).

#### **DESIGN SAMPLES**

Transistor parameters tend to vary much more from wafer lot to wafer lot, over long periods of time, than from one device to the next in the same wafer lot. For design evaluation it is advisable to use transistors from several different date codes.

#### **BAKER CLAMPS**

Many unanticipated pitfalls can be avoided by using Baker Clamps. MUR105 and MUR170 diodes are recommended for base drives less than 1 amp. Similarly, MUR405 and MUR470 types are well–suited for higher drive requirements (see Article Reprint AR131).

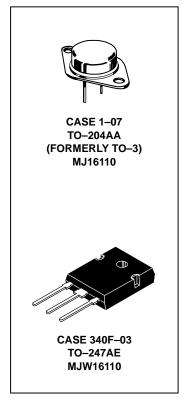

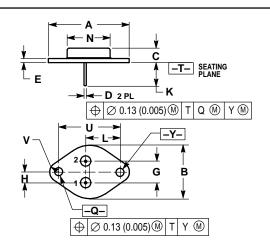

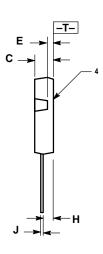

### **PACKAGE DIMENSIONS**

- IOLES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. ALL RULES AND NOTES ASSOCIATED WITH REFERENCED TO-204AA OUTLINE SHALL APPLY.

|     | INCHES    |       | MILLIMETERS |        |  |

|-----|-----------|-------|-------------|--------|--|

| DIM | MIN       | MAX   | MIN         | MAX    |  |

| Α   | 1.550 REF |       | 39.37 REF   |        |  |

| В   |           | 1.050 |             | 26.67  |  |

| U   | 0.250     | 0.335 | 6.35        | 8.51   |  |

| D   | 0.038     | 0.043 | 0.97        | 1.09   |  |

| Е   | 0.055     | 0.070 | 1.40        | 1.77   |  |

| G   | 0.430 BSC |       | 10.92 BSC   |        |  |

| Η   | 0.215 BSC |       | 5.46        | 46 BSC |  |

| K   | 0.440     | 0.480 | 11.18       | 12.19  |  |

| L   | 0.665     | BSC   | 16.89       | BSC    |  |

| N   |           | 0.830 |             | 21.08  |  |

| Q   | 0.151     | 0.165 | 3.84        | 4.19   |  |

| U   | 1.187 BSC |       | 30.15       | BSC    |  |

| l v | 0 131     | 0.188 | 3.33        | 4 77   |  |

STYLE 1:

PIN 1. BASE

2. EMITTER

CASE: COLLECTOR

### **CASE 1-07 TO-204AA** (FORMERLY TO-3) **ISSUE Z**

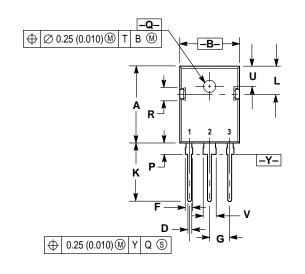

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

|     | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 20.40       | 20.90 | 0.803     | 0.823 |

| В   | 15.44       | 15.95 | 0.608     | 0.628 |

| C   | 4.70        | 5.21  | 0.185     | 0.205 |

| ם   | 1.09        | 1.30  | 0.043     | 0.051 |

| Е   | 1.50        | 1.63  | 0.059     | 0.064 |

| F   | 1.80        | 2.18  | 0.071     | 0.086 |

| G   | 5.45 BSC    |       | 0.215 BSC |       |

| Ξ   | 2.56        | 2.87  | 0.101     | 0.113 |

| ٦   | 0.48        | 0.68  | 0.019     | 0.027 |

| K   | 15.57       | 16.08 | 0.613     | 0.633 |

| L   | 7.26        | 7.50  | 0.286     | 0.295 |

| Р   | 3.10        | 3.38  | 0.122     | 0.133 |

| ø   | 3.50        | 3.70  | 0.138     | 0.145 |

| R   | 3.30        | 3.80  | 0.130     | 0.150 |

| U   | 5.30 BSC    |       | 0.209     | BSC   |

| ٧   | 3.05        | 3.40  | 0.120     | 0.134 |

- STYLE 3:

PIN 1. BASE

2. COLLECTOR

3. EMITTER

4. COLLECTOR

**CASE 340F-03** TO-247AE **ISSUE E**

#### MJ16110 MJW16110

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

**USA/EUROPE**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447

MFAX: RMFAX0@email.sps.mot.com – TOUCHTONE (602) 244–6609 INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, Toshikatsu Otsuki, 6F Seibu-Butsuryu-Center, 3–14–2 Tatsumi Koto-Ku, Tokyo 135, Japan. 03–3521–8315

**HONG KONG:** Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298