MC68HC05F8

## MC68HC05F8 MC68HC705F8

TECHNICAL DATA

| 1  | GENERAL DESCRIPTION          |

|----|------------------------------|

| 2  | PIN DESCRIPTIONS             |

| 3  | MEMORY AND REGISTERS         |

| 4  | RESETS                       |

| 5  | INTERRUPTS                   |

| 6  | TIMERS                       |

| 7  | SERIAL PERIPHERAL INTERFACE  |

| 8  | MANCHESTER ENCODER/DECODER   |

| 9  | DTMF/MELODY GENERATOR        |

| 10 | CPU CORE AND INSTRUCTION SET |

| 11 | LOW POWER MODES              |

| 12 | OPERATING MODES              |

| 13 | ELECTRICAL SPECIFICATIONS    |

| 14 | MECHANICAL SPECIFICATIONS    |

| 1  | GENERAL DESCRIPTION          |

|----|------------------------------|

| 2  | PIN DESCRIPTIONS             |

| 3  | MEMORY AND REGISTERS         |

| 4  | RESETS                       |

| 5  | INTERRUPTS                   |

| 6  | TIMERS                       |

| 7  | SERIAL PERIPHERAL INTERFACE  |

| 8  | MANCHESTER ENCODER/DECODER   |

| 9  | DTMF/MELODY GENERATOR        |

| 10 | CPU CORE AND INSTRUCTION SET |

| 11 | LOW POWER MODES              |

| 12 | OPERATING MODES              |

| 13 | ELECTRICAL SPECIFICATIONS    |

| 14 | MECHANICAL SPECIFICATIONS    |

|    |                              |

### MC68HC05F8 MC68HC705F8

### High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the part was a registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

### Conventions

Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, blank cells in a register diagram indicate that the bit is either unused or reserved; shaded cells indicate that the bit is not described in the following paragraphs; 'u' is used to indicate an undefined state (on reset).

### CUSTOMER FEEDBACK QUESTIONNAIRE (MC68HC05F8D/H)

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

1. How would you rate the quality of the document? Check one box in each category.

|    | -                                                                         | Excellen          | t           | Poor          |            |                                                                     |              | Exceller   | nt      |          | Poor     |             |

|----|---------------------------------------------------------------------------|-------------------|-------------|---------------|------------|---------------------------------------------------------------------|--------------|------------|---------|----------|----------|-------------|

|    | Organization<br>Readability<br>Understandabi<br>Accuracy<br>Illustrations |                   |             |               |            | Tables<br>Table of conto<br>Index<br>Page size/bir<br>Overall impre | nding        |            |         |          |          |             |

|    | Comments: _                                                               |                   |             |               |            |                                                                     |              |            |         |          |          |             |

| 2. | What is your in                                                           | tended use for    | this docu   | ument? If mo  | re than o  | ne option app                                                       | olies, pleas | e rank     | them (1 | , 2, 3). |          |             |

|    | Selection of de                                                           | vice for new ap   | plication   |               |            | Other                                                               | Please sp    | ecify: _   |         |          |          |             |

|    | System design                                                             |                   |             |               |            |                                                                     |              |            |         |          |          |             |

|    | Training purpos                                                           | ses               |             |               |            |                                                                     |              |            |         |          |          |             |

| 3. | How well does                                                             | this manual en    | able you    | to perform th | ne task(s) | outlined in a                                                       | question 2?  | ,          |         |          |          |             |

|    |                                                                           | Complete          | -           | Not at all    |            | Comments:                                                           |              |            |         |          |          |             |

|    |                                                                           |                   |             |               |            |                                                                     |              |            |         |          |          |             |

| 4. | How easy is it                                                            | to find the infor | mation yo   | ou are lookin | g for?     |                                                                     |              |            |         |          |          |             |

|    |                                                                           | Easy              |             | Difficult     |            | Comments:                                                           |              |            |         |          |          |             |

|    |                                                                           |                   |             |               |            |                                                                     |              |            |         |          |          |             |

| 5. | Is the level of te                                                        | achaical dataili  | in the fell |               | aa auffiai | ant to allow w                                                      | ou to undo   | rotond     | now the | dovior   | function | 222         |

| э. |                                                                           |                   |             | owing section | 13 Sumole  | shi to allow y                                                      |              | o little d |         | uevice   |          | much detail |

|    | SECTION 1                                                                 | GENERAL DE        | ESCRIPT     | TION          |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 2                                                                 | PIN DESCRIF       | PTIONS      |               |            |                                                                     |              |            | T.      | П        |          |             |

|    | SECTION 3                                                                 | MEMORY AN         | ID REGIS    | STERS         |            |                                                                     |              |            | T.      | П        | П        | T I         |

|    | SECTION 4                                                                 | RESETS            |             |               |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 5                                                                 | INTERRUPTS        | S           |               |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 6                                                                 | TIMERS            |             |               |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 7                                                                 | SERIAL PER        | IPHERAL     | INTERFAC      | E          |                                                                     |              |            |         |          |          |             |

|    | SECTION 8                                                                 | MANCHESTE         | ER ENCC     | DER/DECO      | DER        |                                                                     |              |            |         |          |          |             |

|    | SECTION 9                                                                 | DTMF/MELO         | DY GENE     | ERATOR        |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 10                                                                | CPU CORE A        | ND INST     | FRUCTION S    | ET         |                                                                     |              |            |         |          |          |             |

|    | SECTION 11                                                                | LOW POWER         | R MODES     | 6             |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 12                                                                | OPERATING         | MODES       |               |            |                                                                     |              |            |         |          |          |             |

|    | SECTION 13                                                                | ELECTRICAL        | SPECIF      | ICATIONS      |            |                                                                     |              |            |         |          |          | Ē           |

|    | SECTION 14                                                                | MECHANICA         | L SPECI     | FICATIONS     |            |                                                                     |              | ū          |         |          |          |             |

|    | Comments:                                                                 |                   |             |               |            |                                                                     |              |            |         |          |          |             |

| 6. | Have you found                                                            |                   |             |               |            |                                                                     |              |            |         |          |          |             |

|    |                                                                           | ,,                |             |               |            |                                                                     |              |            |         |          |          |             |

| 7. | From your poin                                                            | t of view, is any | ything mis  | ssing from th | e docum    | ent? If so, ple                                                     | ease say w   | hat:       |         |          |          |             |

| 8.  | How could we improve this document?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

| 9.  | How would you rate Motorola's documentation?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |

| 11. | Excellent Poor     In general     Against other semiconductor suppliers     Which semiconductor manufacturer provides the best technical documentation?     Which company (in any field) provides the best technical documentation?     How many years have you worked with microprocessors?     How the function of the |                                     |

|     | Less than 1 year 1–3 years 3–5 years More than 5 years                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     |

|     | – Second fold back along this line –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |

|     | By air mail par avion         Image: State of the st                                                    | - First fold back along this line - |

|     | – Third fold back along this line –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |

| 13. | . Currently there is some discussion in the semiconductor industry regarding a move towards providing datas form. If you have any opinion on this subject, please comment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |

| 14. | . We would be grateful if you would supply the following information (at your discretion), or attach your card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                     |

|     | Name:         Phone No:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                     |

|     | Position: FAX No:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                     |

|     | Department:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |

|     | Company:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |

|     | Address:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |

|     | Thank you for helping us improve our documentation,<br>HKG CSIC Technical Publications , Motorola Semiconductors H.K. Ltd., Hong Kong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                     |

X

### TABLE OF CONTENTS

Paragraph Number

#### TITLE

Page Number

### 1 GENERAL DESCRIPTION

| 1.1   | Features1-1          |

|-------|----------------------|

| 1.1.1 | Hardware Features1-1 |

| 1.1.2 | Software Features1-2 |

#### 2 PIN DESCRIPTIONS

| 2.1   | Functional Pin Descriptions | 2-1 |

|-------|-----------------------------|-----|

|       | Pin Assignments             |     |

| 2.3   | Input/Output Programming    | 2-4 |

|       | Parallel Ports              |     |

| 2.3.2 | Serial Port (SPI)           | 2-4 |

#### 3 MEMORY AND REGISTERS

| 3.1 | Memory Map           | 3-1 |  |

|-----|----------------------|-----|--|

| 3.2 | Input/Output Section | 3-1 |  |

| 3.3 | RAM                  | 3-1 |  |

#### 4 RESETS

| 4.1 | Power-On Reset (POR)                    | .4-1 |

|-----|-----------------------------------------|------|

|     | RESET Pin                               |      |

| 4.3 | Illegal Address (ILADR) Reset           | .4-2 |

| 4.4 | Computer Operating Properly (COP) Reset | .4-2 |

Paragraph Number

### 5

### INTERRUPTS

| 5.1   | Hardware Controlled Sequences                         | 5-4  |

|-------|-------------------------------------------------------|------|

| 5.2   | Software Interrupt (SWI)                              | 5-4  |

| 5.3   | External Interrupts (IRQ1 & IRQ2)                     | 5-4  |

| 5.3.1 | External Interrupt Triggering Options (INTN1 & INTN2) | 5-6  |

| 5.3.2 | External Interrupt Enable (INTE1 & INTE2)             | 5-6  |

| 5.3.3 | External Interrupt Flags (INTF1 & INTF2)              | 5-7  |

| 5.4   | Keyboard Interrupt                                    | 5-7  |

| 5.4.1 | Keyboard Control Register                             | 5-8  |

| 5.5   | Programmable Timer (Timer A) Interrupt                | 5-8  |

| 5.6   | Reloadable Timer (Timer B) Interrupt                  | 5-10 |

| 5.7   | SPI Interrupt                                         | 5-10 |

| 5.8   | Manchester Coder (MANCD) Interrupt                    | 5-11 |

#### 6 TIMERS

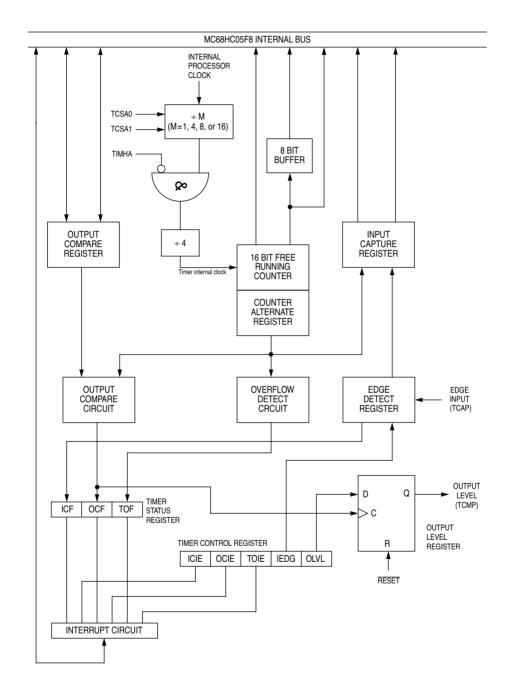

| 6.1   | TIMER A - PROGRAMMABLE TIMER                   | 6-1  |

|-------|------------------------------------------------|------|

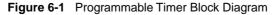

| 6.1.1 | Counter                                        | 6-1  |

| 6.1.2 | Output Compare Registers                       | 6-4  |

| 6.1.3 | Input Capture Registers                        | 6-4  |

| 6.1.4 | Timer Control Register (TCR)                   | 6-5  |

| 6.1.5 | Timer A Status Register (TSR)                  | 6-6  |

| 6.1.6 | Programmable Timer Timing Diagrams             | 6-7  |

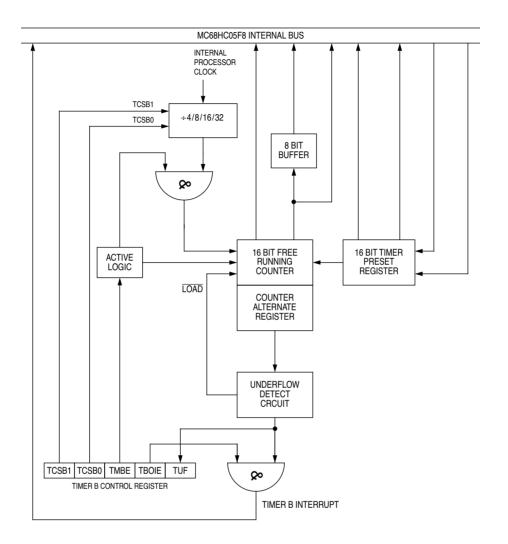

| 6.2   | TIMER B - RELOADABLE TIMER                     | 6-10 |

| 6.2.1 | Functional Description                         | 6-10 |

| 6.2.2 | Resolution and Maximum Period                  | 6-10 |

| 6.2.3 | Timer B Counter                                | 6-11 |

| 6.2.4 | Timer B Preset Register                        | 6-12 |

| 6.2.5 | Timer B Control Status Register                | 6-12 |

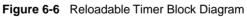

| 6.3   | COP WATCHDOG                                   | 6-13 |

| 6.3.1 | Watchdog Timer Time-Out Flag                   | 6-13 |

| 6.3.2 | COP System Enable and Operation                | 6-14 |

| 6.3.3 | Disable COP Function in Stop or Wait Mode      | 6-14 |

| 6.3.4 | Watchdog Timer Control Status Register (WDCSR) | 6-14 |

|       |                                                |      |

### 7 SERIAL PERIPHERAL INTERFACE

| 7.1 | Features7           | '-1 |

|-----|---------------------|-----|

| 7.2 | Signal Description7 | '-1 |

|     | Serial Clock (SCK)7 |     |

| Paragraph |

|-----------|

| Number    |

| Serial Data Output (SDO)               | 7-3                                          |

|----------------------------------------|----------------------------------------------|

|                                        |                                              |

| General Operation                      | 7-3                                          |

| SPI Registers                          | 7-3                                          |

|                                        |                                              |

|                                        |                                              |

| Serial Peripheral Data Register (SPDR) | 7-6                                          |

|                                        | Serial Data Input (SDI)<br>General Operation |

### 8

### MANCHESTER ENCODER/DECODER

| 8.1     | Features                                                   | 8-1 |

|---------|------------------------------------------------------------|-----|

| 8.2     | General Operation                                          | 8-2 |

| 8.2.1   | Encoder                                                    |     |

| 8.2.1.1 | Idle State of Encoder                                      | 8-3 |

| 8.2.1.2 | Initialization of Encoder                                  | 8-3 |

| 8.2.1.3 | Encode Data Register Empty Flag (NCM) and Encode Interrupt | 8-3 |

| 8.2.1.4 | End Pattern Generation and Next Data Byte Encoding         | 8-3 |

| 8.2.1.5 | Disable Encoder                                            | 8-3 |

| 8.2.2   | Decoder                                                    |     |

| 8.2.2.1 | Decoder Overrun                                            | 8-5 |

| 8.2.2.2 | Data Bit Format Error Detection                            | 8-6 |

| 8.2.2.3 | Bit Rate Error Detection                                   | 8-6 |

| 8.3     | Manchester Encoder/Decoder Registers                       | 8-6 |

| 8.3.1   | MANCD Control Register                                     | 8-6 |

| 8.3.2   | MANCD Status Register                                      | 8-8 |

| 8.3.3   | Encode Data Register (\$2D)                                |     |

| 8.3.4   | Decode Data Register (\$2E)                                | 8-9 |

|         |                                                            |     |

### 9

### DTMF/MELODY GENERATOR

| Features                                | 9-1                                                                                                                                                                                                                                    |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Operation                       | 9-1                                                                                                                                                                                                                                    |

| DMG Registers                           | 9-3                                                                                                                                                                                                                                    |

| Row Frequency Control Register (FCR)    |                                                                                                                                                                                                                                        |

| Column Frequency Control Register (FCC) | 9-3                                                                                                                                                                                                                                    |

| Tone Control Register (TNCR)            | 9-4                                                                                                                                                                                                                                    |

| Programming the DMG                     | 9-6                                                                                                                                                                                                                                    |

| DTMF Dialling                           | 9-6                                                                                                                                                                                                                                    |

| Melody Generation                       | 9-6                                                                                                                                                                                                                                    |

| ToneX Generation                        | 9-6                                                                                                                                                                                                                                    |

| Melody+ToneX Generation                 | 9-6                                                                                                                                                                                                                                    |

|                                         | General Operation<br>DMG Registers<br>Row Frequency Control Register (FCR)<br>Column Frequency Control Register (FCC)<br>Tone Control Register (TNCR)<br>Programming the DMG<br>DTMF Dialling<br>Melody Generation<br>ToneX Generation |

#### TITLE

### 10

### CPU CORE AND INSTRUCTION SET

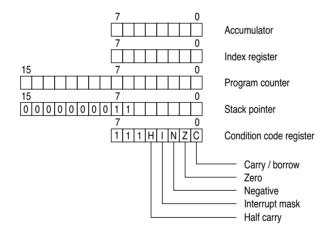

| 10.1    | Registers                      | 10-1  |

|---------|--------------------------------|-------|

| 10.1.1  | Accumulator (A)                | 10-1  |

| 10.1.2  | Index register (X)             | 10-2  |

| 10.1.3  | Program counter (PC)           | 10-2  |

| 10.1.4  | Stack pointer (SP)             | 10-2  |

| 10.1.5  | Condition code register (CCR)  | 10-2  |

| 10.2    | Instruction set                | 10-3  |

| 10.2.1  | Register/memory Instructions   | 10-4  |

| 10.2.2  | Branch instructions            | 10-4  |

| 10.2.3  | Bit manipulation instructions  | 10-4  |

| 10.2.4  | Read/modify/write instructions | 10-4  |

| 10.2.5  | Control instructions           | 10-4  |

| 10.2.6  | Tables                         | 10-4  |

| 10.3    | Addressing modes               | 10-11 |

| 10.3.1  | Inherent                       | 10-11 |

| 10.3.2  | Immediate                      | 10-11 |

| 10.3.3  | Direct                         | 10-11 |

| 10.3.4  | Extended                       | 10-12 |

| 10.3.5  | Indexed, no offset             | 10-12 |

| 10.3.6  | Indexed, 8-bit offset          | 10-12 |

| 10.3.7  | Indexed, 16-bit offset         | 10-12 |

| 10.3.8  | Relative                       | 10-13 |

| 10.3.9  | Bit set/clear                  | 10-13 |

| 10.3.10 | 0 Bit test and branch          | 10-13 |

#### 11

### LOW POWER MODES

| 11.1   | Stop Mode                |      |

|--------|--------------------------|------|

| 11.1.1 | Timer A during Stop Mode | 11-1 |

| 11.1.2 | Timer B during Stop Mode |      |

| 11.1.3 | SPI during Stop Mode     |      |

| 11.1.4 | DMG during Stop Mode     |      |

| 11.1.5 | COP during Stop Mode     |      |

|        | Wait Mode                |      |

### 12

### **OPERATING MODES**

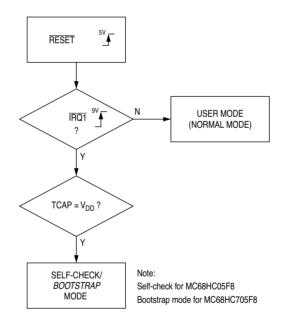

| 12.1 | User Mode (Normal Operation) | 12-2 |

|------|------------------------------|------|

| 12.2 | Self-Check Mode              | 12-2 |

| Paragrap<br>Number | h | т |

|--------------------|---|---|

| 40.0               |   |   |

| 12.3   | Bootstrap Mode                 | 12-4 |

|--------|--------------------------------|------|

|        | EPROM Program Control Register |      |

| 12.3.2 |                                |      |

| 12.3.3 |                                |      |

| 12.3.4 |                                |      |

### 13 ELECTRICAL SPECIFICATIONS

| 13.1 | Maximum Ratings                                  | 13-1 |

|------|--------------------------------------------------|------|

|      | Thermal Characteristics                          |      |

| 13.3 | DC Electrical Characteristics                    |      |

| 13.4 | DTMF/Melody Generator Electrical Characteristics | 13-4 |

| 13.5 | Control Timing                                   | 13-5 |

| 13.6 | Programming Operation Electrical Characteristics |      |

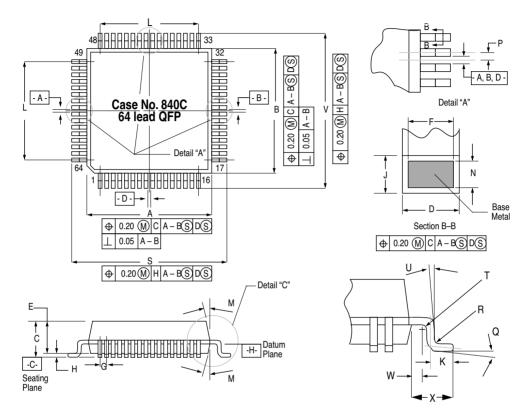

### 14 MECHANICAL SPECIFICATIONS

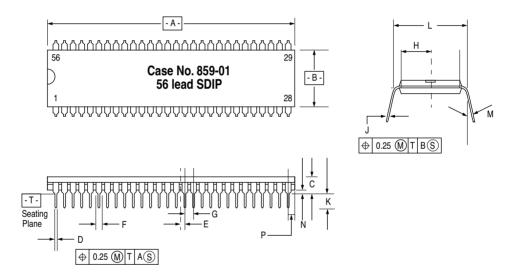

| 14.1 | 56-pin SDIP Package14-1 |

|------|-------------------------|

| 14.2 | 64-pin QFP Package14-2  |

THIS PAGE LEFT BLANK INTENTIONALLY

### LIST OF FIGURES

| Figure<br>Number | TITLE                                         | Page<br>Number |

|------------------|-----------------------------------------------|----------------|

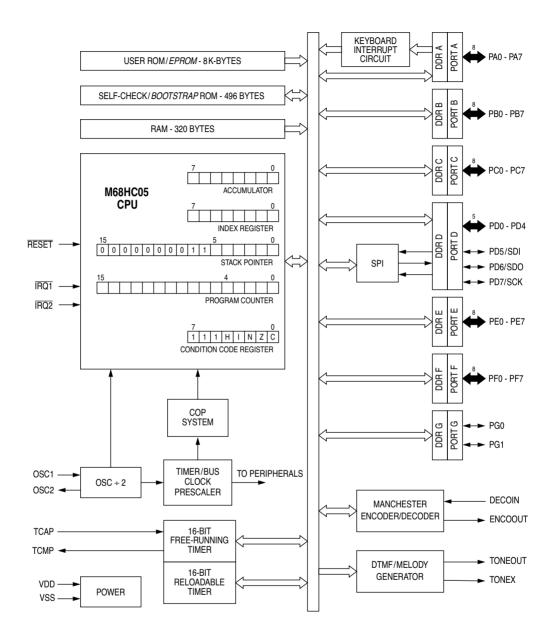

| 1-1              | MC68HC05F8/MC68HC705F8 Block Diagram          | 1-3            |

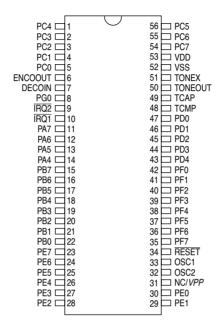

| 2-1              | Pin Assignments for 56-pin SDIP package       | 2-3            |

| 2-2              | Pin Assignments for 64-pin QFP package        | 2-3            |

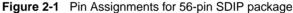

| 2-3              | Parallel Port I/O Circuitry                   | 2-5            |

| 3-1              | MC68HC05F8/MC68HC705F8 Memory Map             | 3-2            |

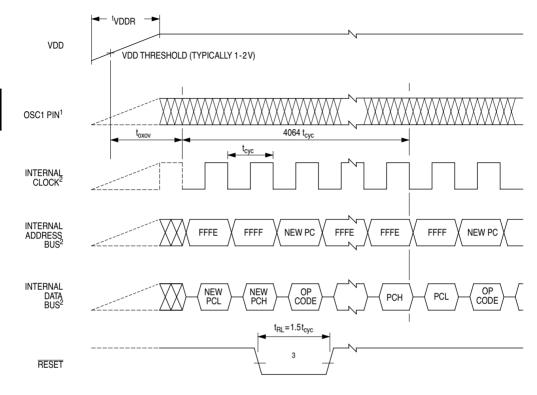

| 4-1              | Power-On Reset and RESET Timing               | 4-4            |

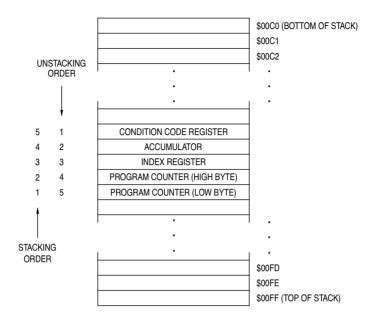

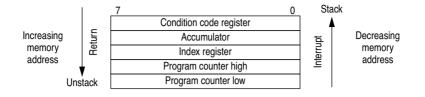

| 5-1              | Interrupt Stacking Order                      | 5-2            |

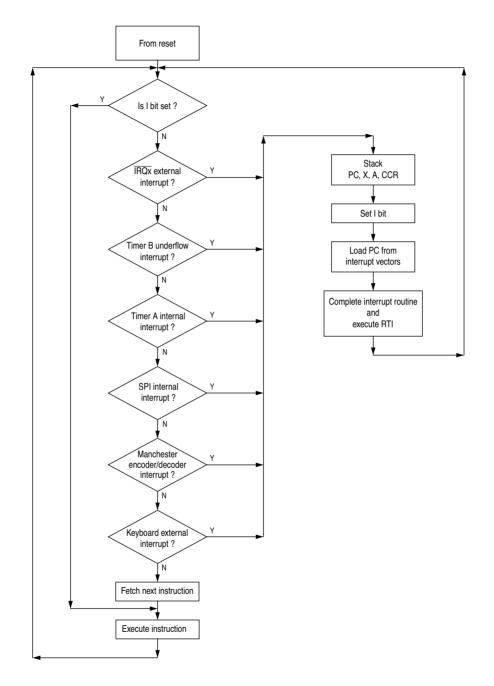

| 5-2              | Hardware Interrupt Flowchart                  | 5-3            |

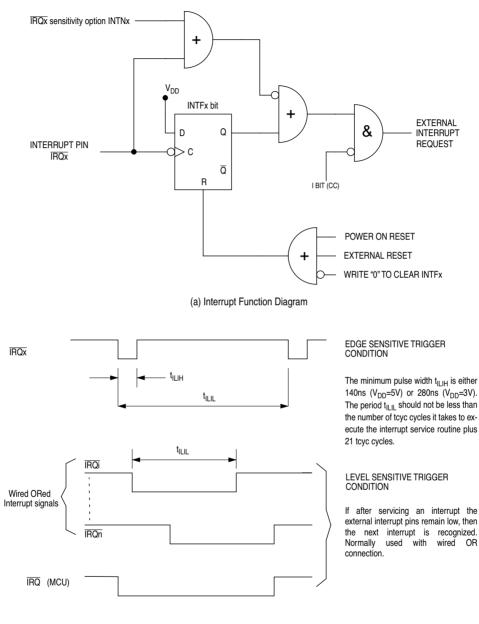

| 5-3              | External Interrupt Circuit and Timing         | 5-5            |

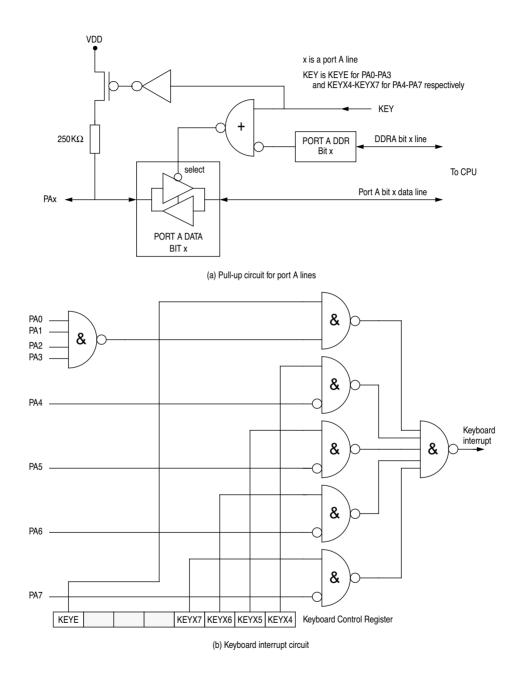

| 5-4              | Keyboard Interrupt Circuit                    |                |

| 6-1              | Programmable Timer Block Diagram              |                |

| 6-2              | Timer State Timing Diagram for Reset          |                |

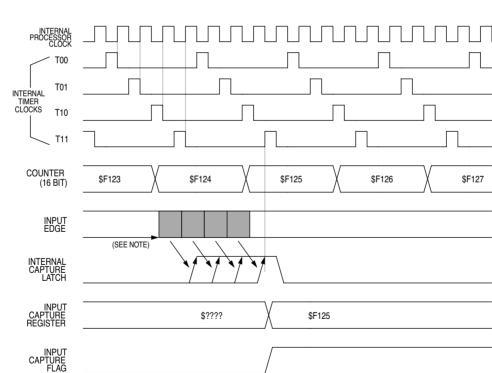

| 6-3              | Timer State Timing Diagram for Input Capture  |                |

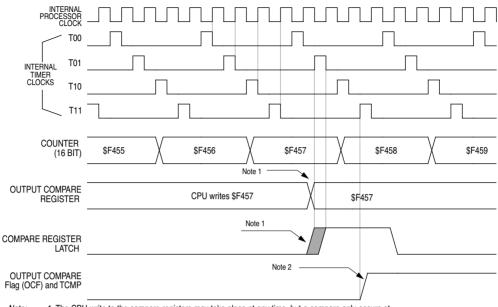

| 6-4              | Timer State Timing Diagram for Output Compare |                |

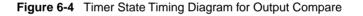

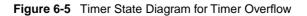

| 6-5              | Timer State Diagram for Timer Overflow        | 6-9            |

| 6-6              | Reloadable Timer Block Diagram                |                |

| 6-7              | Watchdog Timer Block Diagram                  |                |

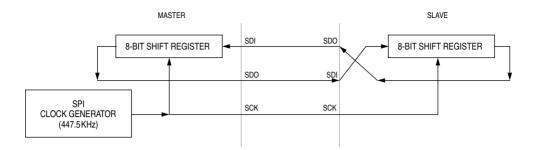

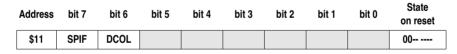

| 7-1              | SPI Master-Slave Interconnection              |                |

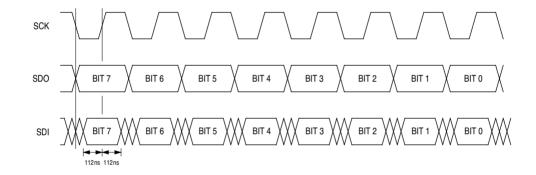

| 7-2              | SPI Port Timing                               |                |

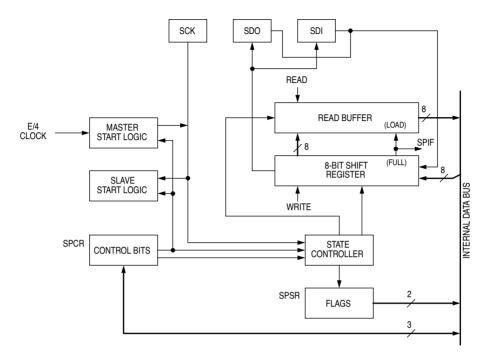

| 7-3              | SPI Block Diagram                             |                |

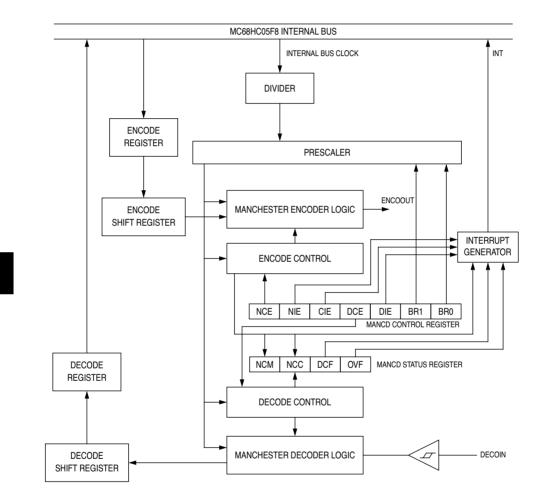

| 8-1              | Manchester Encoder/Decoder Block Diagram      |                |

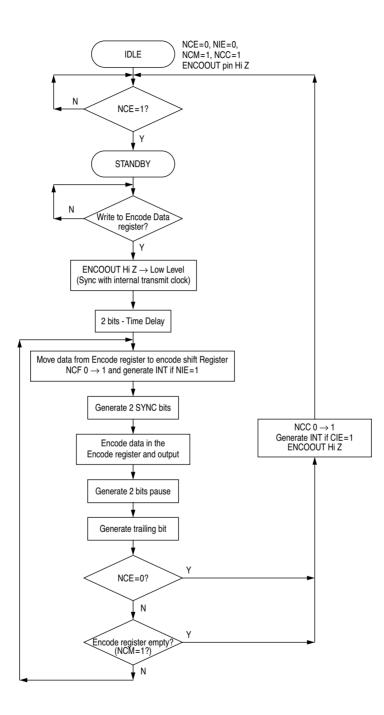

| 8-2              | Logic Flow of Encoder Hardware Operation      |                |

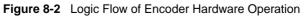

| 8-3              | Encoder Timing Diagram                        |                |

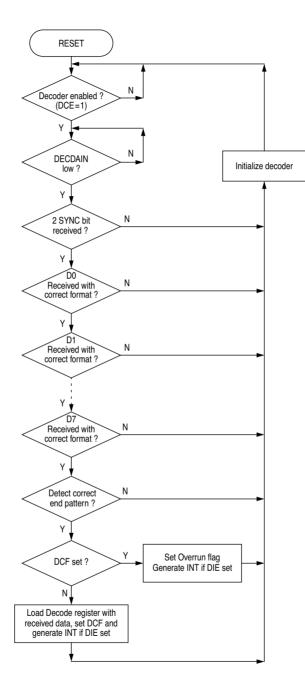

| 8-4              | Logic Flow of Decoder Hardware Operation      |                |

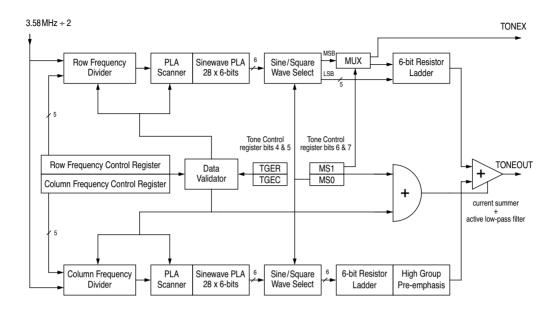

| 9-1              | DTMF/Melody Generator Block Diagram           |                |

| 10-1             | Programming model                             |                |

| 10-2             | Stacking order                                |                |

| 12-1             | Flowchart of Mode Entering                    |                |

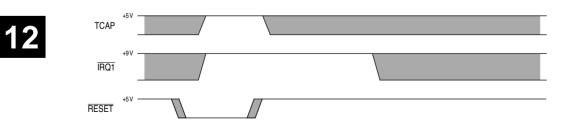

| 12-2             | Self-Check Mode Timing                        |                |

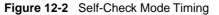

| 12-3             | Self-Test Circuit                             |                |

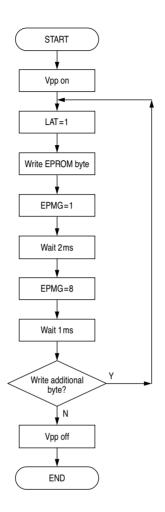

| 12-4             | EPROM Programming Sequence                    |                |

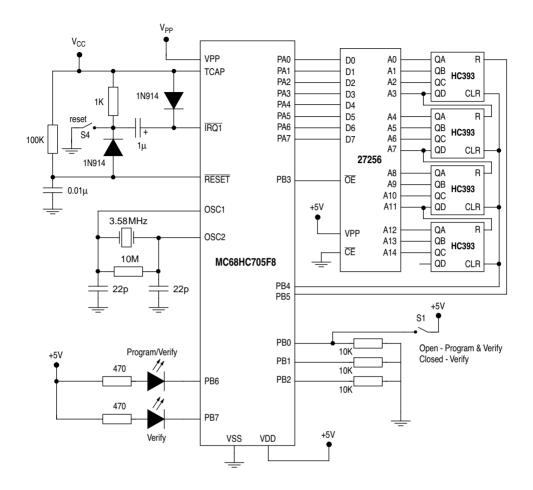

| 12-5             | EPROM Programming Circuit for Bootstrap Mode  |                |

| 14-1             | 56-pin SDIP Mechanical Dimensions             |                |

| 14-2             | 64-pin QFP Mechanical Dimensions              | 14-2           |

THIS PAGE LEFT BLANK INTENTIONALLY

### LIST OF TABLES

| Table<br>Number | TITLE                                                                               | Page<br>Number |

|-----------------|-------------------------------------------------------------------------------------|----------------|

| 2.4             |                                                                                     | 0.4            |

| 2-1<br>3-1      |                                                                                     |                |

| 3-1<br>4-1      | MC68HC05F8/MC68HC705F8 Registers                                                    |                |

| 4-1<br>5-1      | Reset Action on Internal Circuit                                                    | -              |

| 5-1<br>6-1      | Reset/Interrupt Vector Addresses                                                    |                |

| 6-1             | Timer A Clock Frequency Selection<br>Reloadable Timer Resolution and Maximum Period |                |

| 6-2<br>9-1      |                                                                                     |                |

| • •             | Bit Description for DTMF Generation                                                 |                |

| 9-2             | Bit Description for Melody Generation                                               |                |

| 9-3             | DMG Operating Modes<br>Effect of Tone Generation Enable on DMG                      |                |

| 9-4<br>10-1     |                                                                                     |                |

|                 | MUL instruction                                                                     |                |

| 10-2            | Register/memory instructions                                                        |                |

| 10-3            | Branch instructions                                                                 |                |

| 10-4            | Bit manipulation instructions                                                       |                |

| 10-5            | Read/modify/write instructions                                                      |                |

| 10-6            | Control instructions                                                                | -              |

| 10-7            | Instruction set                                                                     |                |

| 10-8            | M68HC05 opcode map                                                                  |                |

| 12-1            | Mode Selection                                                                      |                |

| 12-2            | Self-Check Report                                                                   |                |

| 12-3            | Bootstrap Mode Options                                                              |                |

| 13-1            | DC Electrical Characteristics for 5V Operation                                      |                |

| 13-2            | DC Electrical Characteristics for 2.7V Operation                                    |                |

| 13-3            | Electrical Specification of sine wave tones at TONEOUT output                       |                |

| 13-4            | Electrical Specification of square wave tones at TONEOUT output                     |                |

| 13-5            | Electrical Specification of ToneX at TONEX output                                   |                |

| 13-6            | Control Timing for 5V Operation                                                     |                |

| 13-7            | Control Timing for 2.7V Operation                                                   | 13-6           |

THIS PAGE LEFT BLANK INTENTIONALLY

### **1** GENERAL DESCRIPTION

The MC68HC05F8 HCMOS microcontroller is a member of the M68HC05 family of low-cost single-chip microcontrollers. This 8-bit microcontroller unit (MCU) contains an on-chip oscillator, CPU, RAM, ROM, I/O, timer, serial peripheral interface, Manchester encoder/decoder, DTMF/melody generator, and COP watchdog monitor. This MCU is particularly suitable for cordless telephones with an answering machine.

The MC68HC705F8 is an EPROM version of the MC68HC05F8. All references to the MC68HC05F8 apply equally to the MC68HC705F8, unless otherwise stated. *References specific to the MC68HC705F8 are italicized in the text.*

### 1.1 Features

The following are some of the hardware and software features of the MC68HC05F8 single-chip microcontroller.

### 1.1.1 Hardware Features

- HCMOS technology

- 8-bit architecture

- Power saving Wait and Stop modes

- Full static operation

- 2.5V to 6V operating voltage

- 320 bytes of on-chip RAM (64 bytes for stack)

- 8K-bytes of on-chip ROM; 8K-bytes of on-chip EPROM for MC68HC705F8

- 496-bytes self-check ROM; 496-bytes bootstrap ROM for MC68HC705F8

- 8 keyboard interrupt lines

- Manchester encoder/decoder

- DTMF/melody generator

- Oscillator for 3.579MHz crystal

- 16-bit free-running programmable timer with 4 selectable prescaler frequencies

- 16-bit auto-reload timer with 4 selectable prescaler frequencies

- Computer Operating Properly (COP) watchdog monitor

- Serial peripheral interface

- 10mA high current output pins for LED direct driving

- Available in 56-pin SDIP and 64-pin QFP packages

### 1.1.2 Software Features

- Similar to MC6800

- 8 x 8 unsigned multiply instruction

- Efficient use of program space

- Versatile interrupt handling

- True bit manipulation

- Addressing modes with index addressing for tables

- Efficient instruction set

- Memory mapped I/O

- Two power saving standby modes

- Upward software compatible with the M146805 CMOS family

Figure 1-1 MC68HC05F8/MC68HC705F8 Block Diagram

THIS PAGE LEFT BLANK INTENTIONALLY

# **2** PIN DESCRIPTIONS

This section provides a description of the functional pins and I/O programming of the MC68HC05F8/*MC68HC705F8* microcontroller.

### 2.1 Functional Pin Descriptions

| PIN NAME     | 56-pin SDIP<br>PIN No.  | 64-pin QFP<br>PIN No. | DESCRIPTION                                                                                                                                                                                                                                                                          |

|--------------|-------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD, VSS     | 53, 52                  | 52, 51                | Power is supplied to the MCU using these two pins. VDD is power and VSS is ground.                                                                                                                                                                                                   |

| IRQ1<br>IRQ2 | 10<br>9                 | 2<br>1                | IRQ1 and IRQ2 are software programmable to provide two choices of interrupt triggering sensitivity. These options are:         1) negative edge-sensitive triggering only, or         2) both negative edge-sensitive and level sensitive triggering.                                |

| RESET        | 34                      | 30                    | The active low RESET input is not required for start-up, but can be used to reset the MCU internal state and provide an orderly software start-up procedure.                                                                                                                         |

| ТСАР         | 49                      | 48                    | The TCAP input controls the input capture feature for the on-chip<br>programmable free-running timer.                                                                                                                                                                                |

| ТСМР         | 48                      | 47                    | The TCMP pin provides an output for the output compare feature of the on-chip programmable free-running timer.                                                                                                                                                                       |

| OSC1, OSC2   | 33, 32                  | 29, 28                | These pins provide connections to the on-chip oscillator. The crystal frequency is 3.579545MHz. OSC1 may be driven by an external oscillator if an external crystal circuit is not used.                                                                                             |

| PA0-PA7      | (PA4-PA7 only)<br>14-11 | 10-3                  | These eight I/O lines comprise port A. The state of any pin is software programmable. All port A lines are configured as input during power on or external reset. Port A can also be programmed as keyboard interrupts. PA0 to PA3 are not bonded out on the 56-pin package.         |

| PB0-PB7      | 22-15                   | 18-11                 | These eight I/O lines comprise port B. The state of any pin is software<br>programmable. All port B lines are configured as input during power<br>on or external reset.                                                                                                              |

| PC0-PC7      | 5-1, 56-54              | 60-53                 | These eight I/O lines comprise port C. The state of any pin is software<br>programmable. All port C lines are configured as input during power<br>on or external reset. Each port C pins also has the ability to sink a<br>maximum current of 10mA with a maximum saturation of 1 V. |

| PIN NAME                     | 56-pin SDIP<br>PIN No.                      | 64-pin QFP<br>PIN No.   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------|---------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD0-PD7<br>SDI<br>SDO<br>SCK | (PD0-PD4 only)<br>47-43<br>-<br>-<br>-<br>- | 46-39<br>41<br>40<br>39 | These eight I/O lines comprise port D. The state of any pin is software<br>programmable. All port D lines are configured as input during power<br>on or external reset.<br>When the SPE bit of the SPI Control register (bit 6 of address \$10) is<br>set, PD5, PD6, & PD7 are used for SDI, SDO, & SCK respectively, for<br>the Serial Peripheral Interface. PD5 to PD7 are not bonded out on the<br>56-pin package. Hence, the 56-pin package does not have SPI<br>features. |

| PE0-PE7                      | 30-23                                       | 26-19                   | These eight I/O lines comprise port E. The state of any pin is software<br>programmable. All port E lines are configured as input during power<br>on or external reset.                                                                                                                                                                                                                                                                                                        |

| PF0-PF7                      | 42-35                                       | 38-31                   | These eight I/O lines comprise port F. The state of any pin is software<br>programmable. All port F lines are configured as input during power<br>on or external reset.                                                                                                                                                                                                                                                                                                        |

| PG0, PG1                     | (PG0 only)<br>8                             | 64, 63                  | These two I/O lines comprise port G. The state of any pin is software programmable. All port G lines are configured as input during power on or external reset. PG1 is not bonded out on the 56-pin package.                                                                                                                                                                                                                                                                   |