MC68HC05F12/D

# MC68HC05F12

TECHNICAL DATA

| 1  | INTRODUCTION                          |

|----|---------------------------------------|

| 2  | DES OF OPERATION AND PIN DESCRIPTIONS |

| 3  | MEMORY AND REGISTERS                  |

| 4  | PARALLEL INPUT/OUTPUT PORTS           |

| 5  | CORE TIMER                            |

| 6  | 16-BIT PROGRAMMABLE TIMER             |

| 7  | DTMF/MELODY GENERATOR                 |

| 8  | LIQUID CRYSTAL DISPLAY DRIVER MODULE  |

| 9  | RESETS AND INTERRUPTS                 |

| 10 | <b>CPU CORE AND INSTRUCTION SET</b>   |

| 11 | ELECTRICAL SPECIFICATIONS             |

| 12 | MECHANICAL DATA                       |

| 13 | ORDERING INFORMATION                  |

**MODES OF**

| 1  | INTRODUCTION                            |

|----|-----------------------------------------|

| 2  | MODES OF OPERATION AND PIN DESCRIPTIONS |

| 3  | MEMORY AND REGISTERS                    |

| 4  | PARALLEL INPUT/OUTPUT PORTS             |

| 5  | CORE TIMER                              |

| 6  | 16-BIT PROGRAMMABLE TIMER               |

| 7  | DTMF/MELODY GENERATOR                   |

| 8  | LIQUID CRYSTAL DISPLAY DRIVER MODULE    |

| 9  | RESETS AND INTERRUPTS                   |

| 10 | CPU CORE AND INSTRUCTION SET            |

| 11 | ELECTRICAL SPECIFICATIONS               |

| 12 | MECHANICAL DATA                         |

| 13 | ORDERING INFORMATION                    |

|    |                                         |

## MC68HC05F12

# High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola use negligent regarding the design or manufacture of the part. Motorola and Amages are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

## Conventions

Where abbreviations are used in the text, an explanation can be found in the glossary, at the back of this manual. Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, shaded cells in a register diagram indicate that the bit is either unused or reserved; 'u' is used to indicate an undefined state (on reset).

#### CUSTOMER FEEDBACK QUESTIONNAIRE (MC68HC05F4/D)

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

1. How would you rate the quality of the document? Check one box in each category.

|    |                                                                                                                                                                                 | Excellent                                                                                                                                                                                | Poor                                                                           |                                                                                 | Excellent                               | Poor                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------|

|    | Organization<br>Readability<br>Understandability<br>Accuracy<br>Illustrations<br>Comments:                                                                                      |                                                                                                                                                                                          |                                                                                | Tables<br>Table of contents<br>Index<br>Page size/binding<br>Overall impression |                                         |                                     |

| 2. |                                                                                                                                                                                 |                                                                                                                                                                                          | ment? If more tha                                                              | an one option applies, plea                                                     |                                         | e, 3).                              |

|    |                                                                                                                                                                                 | for new application                                                                                                                                                                      |                                                                                | Other Please s                                                                  | specify:                                |                                     |

|    | System design                                                                                                                                                                   |                                                                                                                                                                                          | ų                                                                              |                                                                                 |                                         |                                     |

|    | Training purposes                                                                                                                                                               |                                                                                                                                                                                          |                                                                                |                                                                                 |                                         |                                     |

| 3. | How well does this                                                                                                                                                              | manual enable you t                                                                                                                                                                      | to perform the tas                                                             | sk(s) outlined in question 2                                                    | 2?                                      |                                     |

|    |                                                                                                                                                                                 | Completely                                                                                                                                                                               | Not at all                                                                     | Comments:                                                                       |                                         |                                     |

|    |                                                                                                                                                                                 |                                                                                                                                                                                          |                                                                                |                                                                                 |                                         |                                     |

| 4. | How easy is it to fir                                                                                                                                                           | nd the information yo                                                                                                                                                                    | u are looking for?                                                             | ·                                                                               |                                         |                                     |

|    |                                                                                                                                                                                 | Easy                                                                                                                                                                                     | Difficult                                                                      | Comments:                                                                       |                                         |                                     |

|    |                                                                                                                                                                                 |                                                                                                                                                                                          |                                                                                |                                                                                 |                                         |                                     |

| 5. | Is the level of techr                                                                                                                                                           | nical detail in the follo                                                                                                                                                                | wing sections su                                                               | fficient to allow you to unc<br>T                                               | derstand how the de<br>oo little detail | evice functions?<br>Too much detail |

|    | SECTION 3 MEM<br>SECTION 4 PARA<br>SECTION 5 COR<br>SECTION 6 16-BI<br>SECTION 7 DTM<br>SECTION 8 LIQUI<br>SECTION 9 RESE<br>SECTION 10 CPU<br>SECTION 11 ELE<br>SECTION 12 MEC | ES OF OPERATION<br>ORY AND REGISTE<br>ALLEL INPUT/OUTPI<br>E TIMER<br>T PROGRAMMABLE<br>F/MELODY GENERA<br>ID CRYSTAL DISPL/<br>ETS AND INTERRUF<br>I CORE AND INSTR<br>CTRICAL SPECIFIC | RS<br>JT PORTS<br>TIMER<br>TOR<br>AY DRIVER MOE<br>PTS<br>UCTION SET<br>ATIONS |                                                                                 |                                         |                                     |

|    | mments:                                                                                                                                                                         |                                                                                                                                                                                          |                                                                                |                                                                                 |                                         |                                     |

| 6. | Have you found any                                                                                                                                                              | / errors? If so, please                                                                                                                                                                  | e comment:                                                                     |                                                                                 |                                         |                                     |

7. From your point of view, is anything missing from the document? If so, please say what:

|      |                                                                                                                                |                                 | X                             |

|------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|

| 8.   | How could we improve this document?                                                                                            |                                 |                               |

|      |                                                                                                                                |                                 |                               |

| 9.   | How would you rate Motorola's documentation?                                                                                   |                                 |                               |

|      | Excellent Poor                                                                                                                 |                                 |                               |

|      | <ul> <li>In general</li> <li>Against other semiconductor suppliers</li> </ul>                                                  |                                 |                               |

|      | Which semiconductor manufacturer provides the best technical documentation?                                                    |                                 |                               |

|      | Which company (in any field) provides the best technical documentation? How many years have you worked with microprocessors?   |                                 |                               |

| . 2. | Less than 1 years 1–3 years 3–5 years More than 5 years                                                                        |                                 |                               |

|      | - Second fold back along this line -                                                                                           |                                 |                               |

|      |                                                                                                                                |                                 |                               |

|      |                                                                                                                                |                                 |                               |

|      | By air mail                                                                                                                    |                                 |                               |

|      | Par avion                                                                                                                      |                                 |                               |

|      | IBRS NUMBER PHQ-B/207/G                                                                                                        |                                 |                               |

|      | CCRI NUMERO PHQ-B/207/G NO STAMP REQUIRED                                                                                      | 1                               | - C                           |

|      | NO STANF REQUIRED                                                                                                              | irst fo                         | ıt alc                        |

|      |                                                                                                                                | old t                           | ong t                         |

|      | REPONSE PAYEE                                                                                                                  | First fold back along this line | Cut along this line to remove |

|      | GRANDE-BRETAGNE                                                                                                                | alon                            | ine t                         |

|      |                                                                                                                                | g thi                           | o rer                         |

|      | Motorola Ltd.,                                                                                                                 | slin                            | поче                          |

|      | Colvilles Road,                                                                                                                | 0                               | I                             |

|      | Kelvin Industrial Estate,<br>EAST KILBRIDE,                                                                                    |                                 |                               |

|      | G75 8BR.                                                                                                                       |                                 |                               |

|      | !MOTOROLA GREAT BRITAIN.                                                                                                       |                                 |                               |

|      | Semiconductor Products Sector F.A.O. Technical Publications Manager                                                            |                                 |                               |

|      | (re: MC68HC05F4/D)                                                                                                             |                                 |                               |

|      |                                                                                                                                |                                 |                               |

|      | – Third fold back along this line –                                                                                            |                                 |                               |

| 13.  | Currently there is some discussion in the semiconductor industry regarding a move towards providing data sheets in el          | ectronic                        |                               |

|      | form. If you have any opinion on this subject, please comment.                                                                 |                                 |                               |

| 14.  | We would be grateful if you would supply the following information (at your discretion), or attach your card.                  |                                 |                               |

|      | Name: Phone No:                                                                                                                |                                 |                               |

|      | Position: FAX No:                                                                                                              |                                 |                               |

|      | Department:                                                                                                                    |                                 |                               |

|      | Company:                                                                                                                       |                                 |                               |

|      | Address:                                                                                                                       | <u> </u>                        |                               |

|      |                                                                                                                                |                                 |                               |

|      | Thank you for helping us improve our documentation,<br>Graham Forbes, Technical Publications Manager, Motorola Ltd., Scotland. |                                 |                               |

|      |                                                                                                                                |                                 |                               |

|      | <ul> <li>Finally, tuck this edge into opposite flap</li> </ul>                                                                 |                                 |                               |

## **TABLE OF CONTENTS**

Paragraph Number

TITLE

Page Number

#### 1 INTRODUCTION

| 1.1 Mask options for the MC68HC05F12 |

|--------------------------------------|

|--------------------------------------|

#### 2 MODES OF OPERATION AND PIN DESCRIPTIONS

| 2.1     | Single-chip mode                   | 2–1 |

|---------|------------------------------------|-----|

| 2.2     | Low power modes                    | 2–1 |

| 2.2.1   | STOP mode                          | 2–1 |

| 2.2.2   | WAIT mode                          | 2–2 |

| 2.2.3   | Data retention mode                | 2–2 |

| 2.3     | System options register            | 2–4 |

| 2.4     | Pin descriptions                   | 2–5 |

| 2.4.1   | VDD and VSS                        | 2–5 |

| 2.4.2   | IRQ                                | 2–5 |

| 2.4.3   | RESET                              | 2–5 |

| 2.4.4   | PA0–PA7/PB0–PB7/Keyboard Interrupt | 2–5 |

| 2.4.5   | PC0–PC7, TCAP3                     | 2–6 |

| 2.4.6   | PD0–PD7                            | 2–6 |

| 2.4.7   | PE0–PE7/TACP1-2, TCMP1-2           | 2–6 |

| 2.4.8   | BP0–BP3, PF0–FP23                  | 2–6 |

| 2.4.9   | PH0-PH1                            |     |

| 2.4.10  | PG0–PG7/FP24–FP31                  | 2–6 |

| 2.4.11  | VLCD                               | 2–7 |

| 2.4.12  | TNO and TNX                        | 2–7 |

| 2.4.13  | OSC1 and OSC2                      | 2–7 |

| 2.4.13. | 1 Crystal                          |     |

| 2.4.13. | 2 External clock                   | 2–7 |

Paragraph Number

#### TITLE

#### 3

## MEMORY AND REGISTERS

| Registers      | 3–1 |

|----------------|-----|

| RAM            | 3–1 |

| ROM            | 3–1 |

| Bootloader ROM | 3–5 |

| EEPROM         | 3–5 |

|                |     |

|                |     |

|                |     |

|                | RAM |

#### 4 PARALLEL INPUT/OUTPUT PORTS

| 4.1     | Input/output programming                                   | 4–1 |

|---------|------------------------------------------------------------|-----|

| 4.2     | Port A                                                     | 4–2 |

| 4.2.1   | Keyboard interrupt                                         | 4–2 |

| 4.2.1.1 |                                                            |     |

| 4.3     | Port B                                                     | 4–4 |

| 4.4     | Port C                                                     | 4–5 |

| 4.5     | Port D                                                     | 4–5 |

| 4.6     | Port E                                                     | 4–5 |

| 4.7     | Port H                                                     | 4–6 |

| 4.8     | Port G                                                     | 4–6 |

| 4.9     | Port registers                                             | 4–7 |

| 4.9.1   | Port data registers (Ports A, B, C, D, E, G and H)         | 4–7 |

| 4.9.2   | Data direction registers (DDRA, DDRB, DDRC, DDRD and DDRE) |     |

| 4.9.3   | Port control registers                                     | 4–8 |

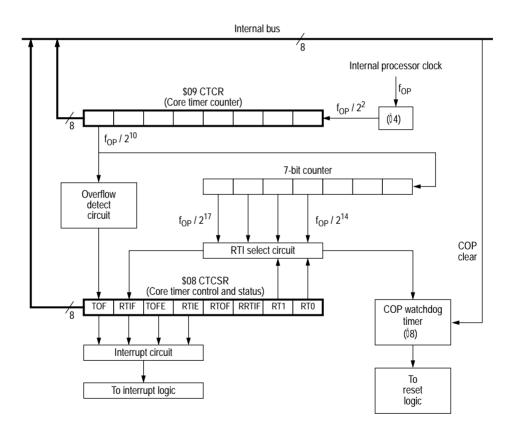

## 5

## **CORE TIMER**

| 5.1   | Real time interrupts (RTI)                       | 5–2 |

|-------|--------------------------------------------------|-----|

|       | Core timer registers                             |     |

| 5.2.1 |                                                  |     |

| 5.2.2 | Core timer counter register (CTCR)               | 5–4 |

| 5.3   | Computer operating properly (COP) watchdog timer | 5–5 |

|       | Core timer during WAIT                           |     |

| 5.5   | Core timer during STOP                           | 5–5 |

#### TITLE

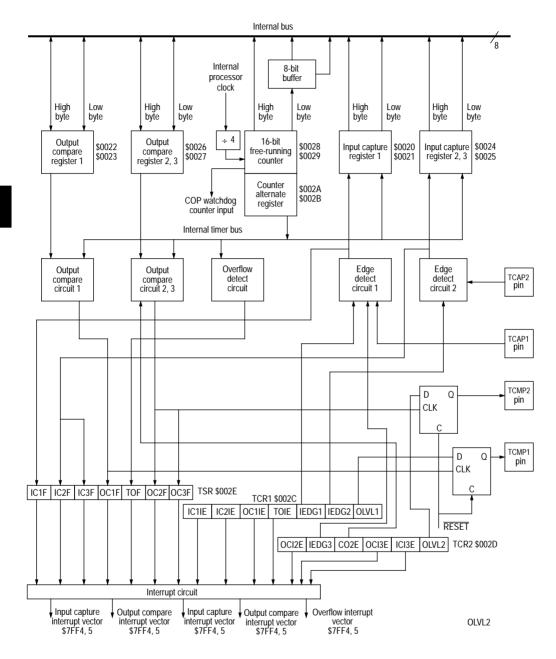

### 6

### **16-BIT PROGRAMMABLE TIMER**

| 6.1   | Counter                                         |      |

|-------|-------------------------------------------------|------|

| 6.1.1 | Counter register and alternate counter register |      |

| 6.2   | Timer control and status                        |      |

| 6.2.1 | Timer control registers 1 and 2 (TCR1 and TCR2) |      |

| 6.2.2 | Timer status register (TSR)                     |      |

| 6.3   | Input capture                                   | 6–10 |

| 6.3.1 | Input capture register 1 (ICR1)                 |      |

| 6.3.2 | Input capture register 2 (ICR2)                 | 6–11 |

| 6.3.3 | Input capture register 3 (ICR3)                 |      |

| 6.4   | Output compare                                  |      |

| 6.4.1 | Output compare register 1 (OCR1)                |      |

| 6.4.2 | Output compare register 2 (OCR2)                | 6–13 |

| 6.4.3 | Output compare register 3 (OCR3)                |      |

| 6.5   | Timer during STOP mode                          |      |

| 6.6   | Timer during WAIT mode                          |      |

| 6.7   | Timer state diagrams                            |      |

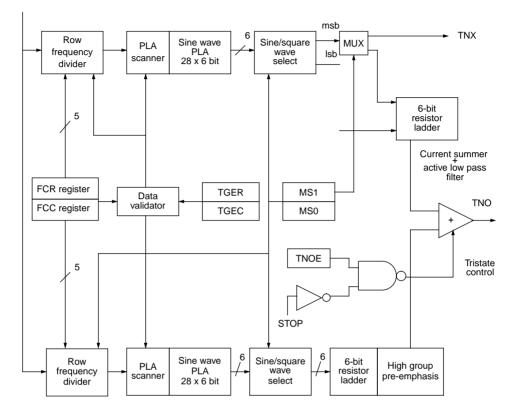

#### 7 DTMF/MELODY GENERATOR

| 7.1   | Introduction                               | 7–1 |

|-------|--------------------------------------------|-----|

| 7.1.1 | Features                                   | 7–1 |

| 7.2   | Functional description                     | 7–2 |

| 7.3   | DMG registers                              | 7–4 |

| 7.3.1 | Row and column frequency control registers | 7–4 |

| 7.3.2 | Tone control register (TNCR)               | 7–4 |

| 7.4   | Operation of the DMG                       | 7–7 |

| 7.5   | DMG during WAIT mode                       | 7–8 |

| 7.6   | DMG during STOP mode                       | 7–8 |

|       |                                            |     |

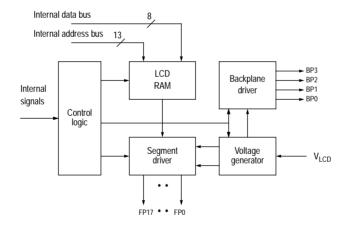

#### 8 LIQUID CRYSTAL DISPLAY DRIVER MODULE

| 8.1 | LCD RAM                                  |  |

|-----|------------------------------------------|--|

|     | LCD operation                            |  |

|     | Timing signals and LCD voltage waveforms |  |

|     | LCD control register                     |  |

|     | LCD during WAIT mode                     |  |

|     | LCD during STOP mode                     |  |

Paragraph Number

#### TITLE

#### 9

### **RESETS AND INTERRUPTS**

| 9.1     | Resets                                       | 9–1 |

|---------|----------------------------------------------|-----|

| 9.1.1   | Power-on reset                               | 9–1 |

| 9.1.2   | RESET pin                                    | 9–1 |

| 9.1.3   | Illegal address reset                        | 9–2 |

| 9.1.4   | Computer operating properly (COP) reset      | 9–2 |

| 9.1.5   | Low voltage reset                            | 9–2 |

| 9.2     | Interrupts                                   | 9–3 |

| 9.2.1   | Interrupt priorities                         |     |

| 9.2.2   | Non-maskable software interrupt (SWI)        | 9–5 |

| 9.2.3   | Maskable hardware interrupts                 | 9–5 |

| 9.2.3.1 | Real time and core timer (CTIMER) interrupts | 9–6 |

| 9.2.3.2 | Programmable 16-bit timer interrupt          | 9–6 |

| 9.2.3.3 |                                              |     |

| 9.2.3.4 |                                              |     |

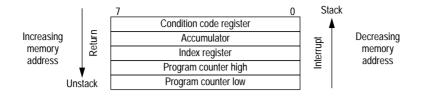

| 9.2.4   | Hardware controlled interrupt sequence       | 9–7 |

|         |                                              |     |

#### 10

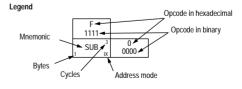

## **CPU CORE AND INSTRUCTION SET**

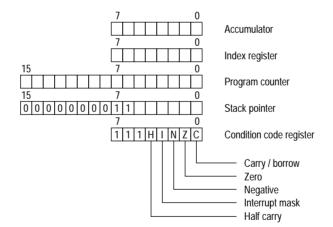

| 10.1   | Registers                              |  |

|--------|----------------------------------------|--|

| 10.1.1 | Accumulator (A)                        |  |

| 10.1.2 | Index register (X)                     |  |

| 10.1.3 | ······································ |  |

| 10.1.4 | Stack pointer (SP)                     |  |

| 10.1.5 | Condition code register (CCR)          |  |

| 10.2   | Instruction set                        |  |

| 10.2.1 | Register/memory Instructions           |  |

| 10.2.2 | Branch instructions                    |  |

| 10.2.3 | Bit manipulation instructions          |  |

| 10.2.4 | Read/modify/write instructions         |  |

| 10.2.5 | Control instructions                   |  |

| 10.2.6 | Tables                                 |  |

| 10.3   | Addressing modes                       |  |

| 10.3.1 | Inherent                               |  |

| 10.3.2 | Immediate                              |  |

| 10.3.3 | Direct                                 |  |

| 10.3.4 | Extended                               |  |

| 10.3.5 | Indexed, no offset                     |  |

| 10.3.6 | Indexed, 8-bit offset                  |  |

| 10.3.7 | Indexed, 16-bit offset                 |  |

| 10.3.8 |                                        |  |

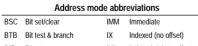

| 10.3.9 | Bit set/clear                          |  |

| Paragraph<br>Number | TITLE               | Page<br>Number |

|---------------------|---------------------|----------------|

| 10.3.10             | Bit test and branch | 10–13          |

#### 11 ELECTRICAL SPECIFICATIONS

| 11.1 | Maximum ratings                                     | 11–1 |

|------|-----------------------------------------------------|------|

|      | Thermal characteristics and power considerations    |      |

| 11.3 | DC electrical characteristics                       | 11–3 |

| 11.4 | Control timing                                      | 11–5 |

|      | DC levels for low voltage RESET and LVI             |      |

| 11.6 | Electrical specifications for DTMF/melody generator | 11–7 |

| 11.7 | EEPROM additional information                       | 11–8 |

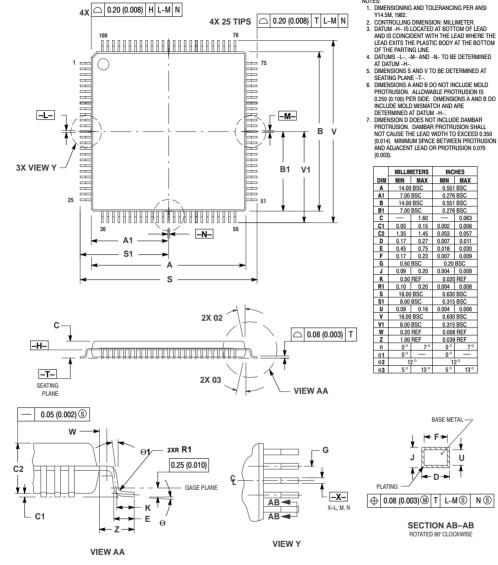

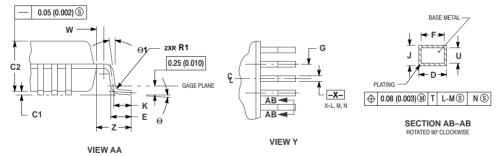

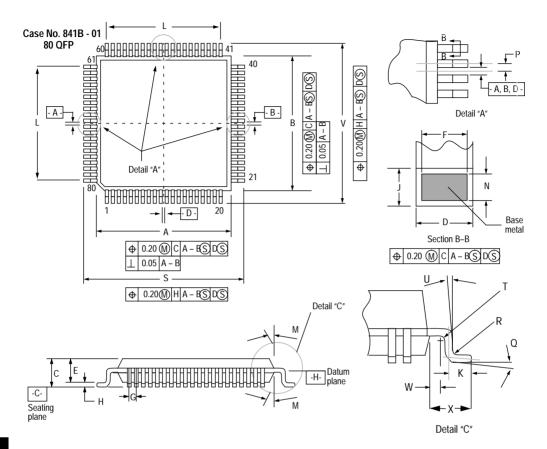

#### 12 MECHANICAL DATA

#### 13 ORDERING INFORMATION

| 13.1 | EPROMs                      | 13–2 |

|------|-----------------------------|------|

| 13.2 | Verification media          | 13–2 |

| 13.3 | ROM verification units(RVU) | 13–2 |

THIS PAGE LEFT BLANK INTENTIONALLY

## LIST OF FIGURES

| Paragrap<br>Number | h <b>TITLE</b>                                | Page<br>Number |

|--------------------|-----------------------------------------------|----------------|

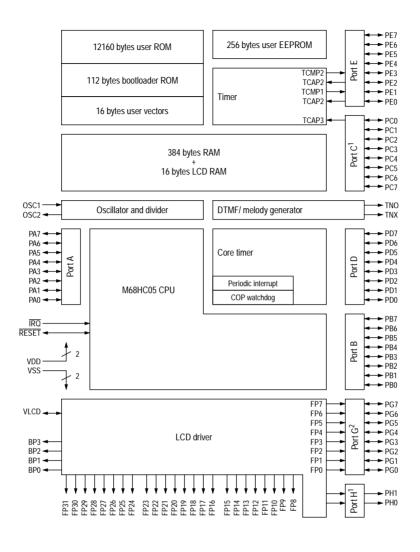

| 1-1                | MC68HC05F12 block diagram                     | 1–3            |

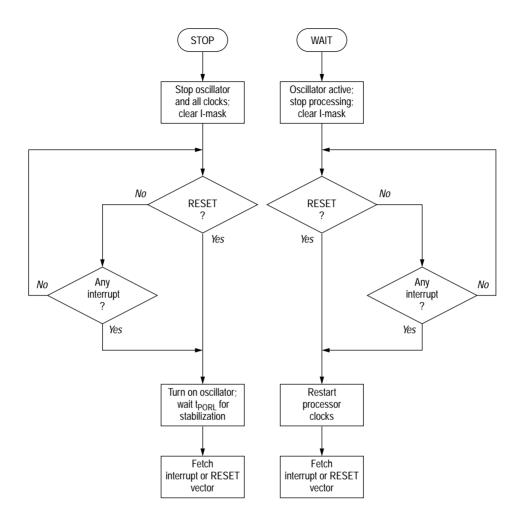

| 2-1                | STOP and WAIT flowcharts                      | 2–3            |

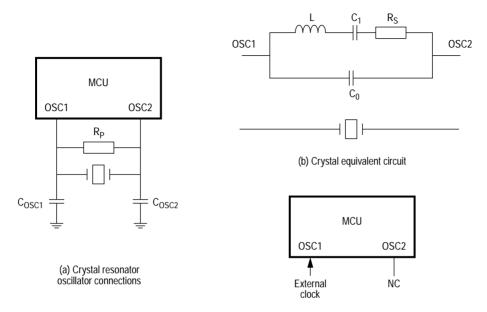

| 2-2                | Oscillator connections                        | 2–8            |

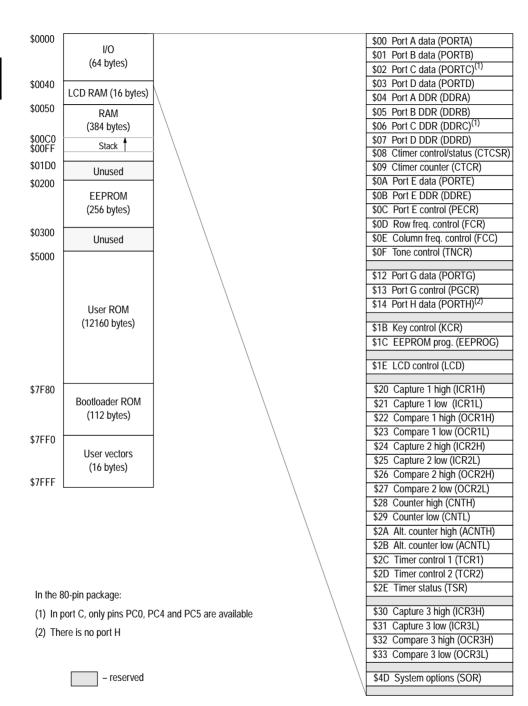

| 3-1                | MC68HC05F12 memory map                        | 3–2            |

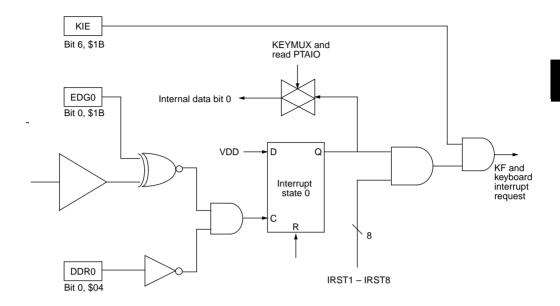

| 4-1                | Structure of port with keyboard interrupt     | 4–3            |

| 4-2                | Standard I/O port structure                   | 4–4            |

| 5-1                | Core timer block diagram                      | 5–1            |

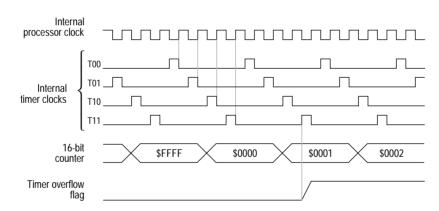

| 0-1                | 16-bit programmable timer block diagram       | 6–3            |

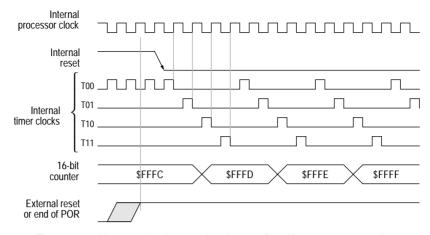

| 6-1                | Timer state timing diagram for reset          | 6–15           |

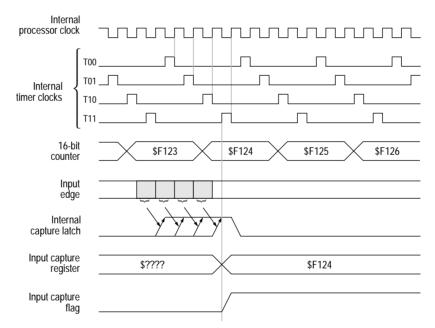

| 6-2                | Timer state timing diagram for input capture  | 6–15           |

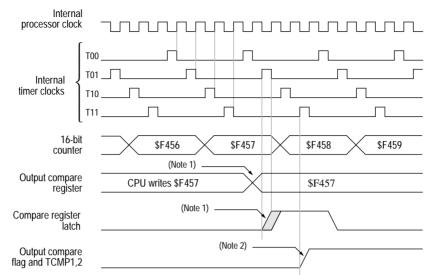

| 6-3                | Timer state timing diagram for output compare | 6–16           |

| 6-4                | Timer state timing diagram for timer overflow |                |

| 7-1                | DTMF/melody generator (DMG) block diagram     | 7–3            |

| 8-1                | LCD system block diagram                      | 8–1            |

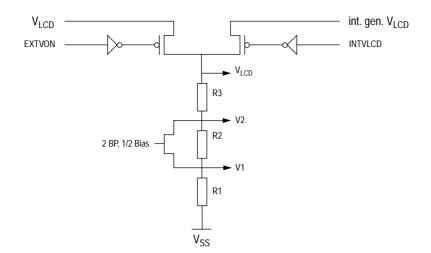

| 8-2                | Voltage level selection                       |                |

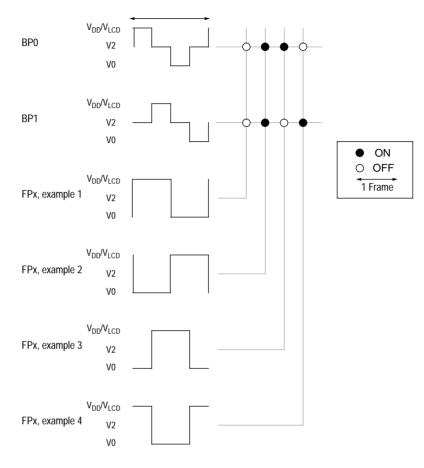

| 8-3                | LCD waveform with 2 backplanes, 1/2 bias      | 8–5            |

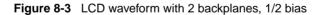

| 8-4                | LCD waveform with 2 backplanes, 1/3 bias      |                |

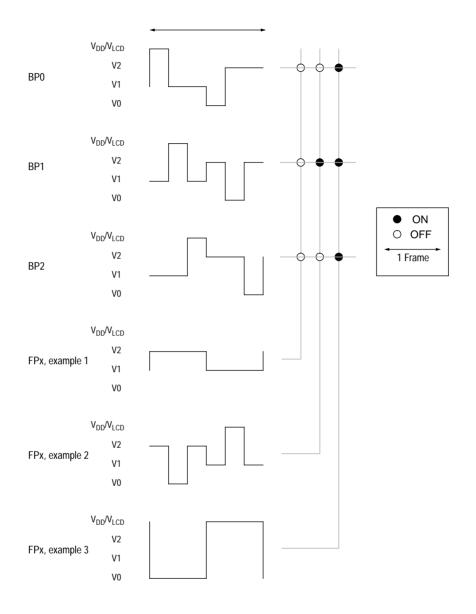

| 8-5                | LCD waveform with 3 backplanes                | 8–7            |

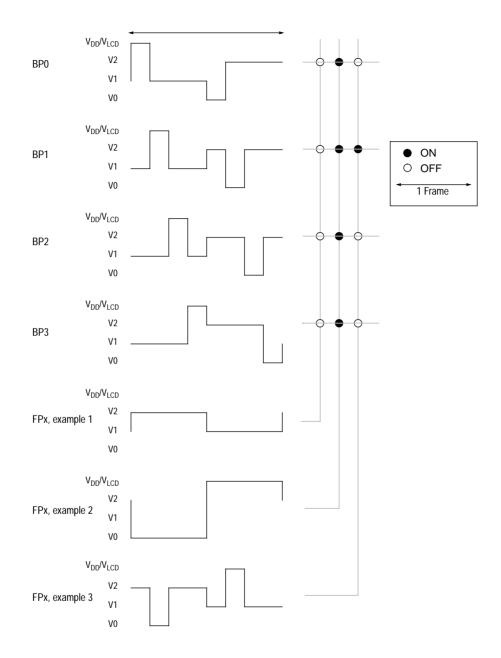

| 8-6                | LCD waveform with 4 backplanes                |                |

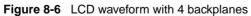

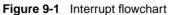

| 9-1                | Interrupt flowchart                           |                |

| 10-1               | Programming model                             |                |

| 10-2               | Stacking order                                |                |

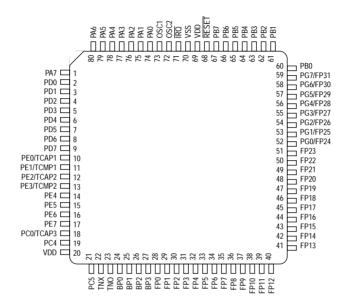

| 12-1               | 100-pin QFP pinout for the MC68HC05F12        |                |

| 12-2               | 100-pin QFP mechanical dimensions             |                |

| 12-3               | 80-pin QFP pinout                             |                |

| 12-4               | 80-pin QFP mechanical dimensions              | 12–4           |

THIS PAGE LEFT BLANK INTENTIONALLY

## **LIST OF TABLES**

| Paragrap<br>Number | h <b>TITLE</b>                                     | Page<br>Number |

|--------------------|----------------------------------------------------|----------------|

| 3-1                | Register outline                                   | 3–3            |

| 3-2                | Erase modes                                        | 3–6            |

| 4-1                | I/O pin states                                     | 4–4            |

| 5-1                | Example RTI periods                                | 5–4            |

| 5-2                | Minimum COP reset times                            | 5–5            |

| 7-1                | Bit description for DTMF generation                | 7–5            |

| 7-2                | Bit description for melody generator               | 7–6            |

| 7-3                | Mode of operation for DMG                          | 7–6            |

| 7-4                | Effect of tone generation on DMG                   | 7–7            |

| 8-1                | LCD RAM organization                               | 8–2            |

| 8-2                | LCD controller operating modes                     | 8–3            |

| 8-3                | Multiplex ratio/backplane selection                | 8–9            |

| 9-1                | Vector address for interrupts and reset            | 9–5            |

| 10-1               | MUL instruction                                    |                |

| 10-2               | Register/memory instructions                       |                |

| 10-3               | Branch instructions                                | 10–7           |

| 10-4               | Bit manipulation instructions                      | 10–7           |

| 10-5               | Read/modify/write instructions                     | 10–8           |

| 10-6               | Control instructions                               | 10–8           |

| 10-7               | Instruction set                                    | 10–9           |

| 10-8               | M68HC05 opcode map                                 | 10–11          |

| 11-1               | Maximum ratings                                    | 11–1           |

| 11-2               | Package thermal characteristics                    | 11–2           |

| 11-3               | DC electrical characteristics (VDD = 5.0 V)        |                |

| 11-4               | DC electrical characteristics ( $V_{DD} = 2.7 V$ ) | 11–4           |

| 11-5               | Control timing ( $V_{DD} = 5V$ )                   |                |

| 11-6               | Control timing ( $V_{DD} = 2.7 V$ )                |                |

| 11-7               | DC levels for low voltage reset and LVI            | 11–7           |

| 11-8               | Sine wave tones at TNO                             |                |

| 11-9               | Square wave tones at TNO                           |                |

| 11-10              | TONEX at TNX output                                |                |

| 11-11              | EEPROM additional information                      |                |

| 13-1               | MC order numbers                                   | 13–1           |

THIS PAGE LEFT BLANK INTENTIONALLY

# 1 INTRODUCTION

The MC68HC05F12 is a member of the M68HC05 family of HCMOS microcomputers. Its memory configuration comprises 12K bytes of ROM, 384 bytes of RAM and 256 bytes of EEPROM. The on-board features of this device make it particularly suitable for use in highly integrated telephone handsets; the timer and DTMF generator allow for both pulse and tone dialling and, in addition to telephone set-up parameters and features such as last number redial, the EEPROM can typically store up to 12 telephone numbers of 20 digits, even after power has been removed from the circuit. Other features of the MC68HC05F12 include the LCD circuit which can drive up to 128 segments of an LCD display. A high level of integration has been achieved on the MC68HC05F12, and careful attention has been paid to its low-power and low-voltage performance, a major consideration in many telecommunications applications.

#### Features

- Fully static design featuring the industry-standard M68HC05 CPU core

- 12144 bytes of user ROM, plus 16 bytes for vectors

- 128 bytes of bootloader ROM

- 384 bytes of RAM plus 16 bytes of LCD RAM

- 256 bytes of user EEPROM

- DTMF/Melody generator

- 16-bit programmable timer with three input captures and three output compares (the output of one of the output compares is used internally and does not have an external connection)

- 15 stage multipurpose core timer with timer overflow, real time interrupt and COP watchdog

- LCD driver with 4 backplanes and 32 frontplanes

- Power saving STOP and WAIT modes

- I/O lines

- 100 QFP configuration total of 50 I/O pins configured as:

37 dedicated bidirectional I/O

13 shared with peripherals

#### INTRODUCTION

- 80 QFP configuration total of 43 I/O pins configured as:

30 dedicated bidirectional I/O

13 shared with peripherals

- Hardware interrupt with edge or edge-and-level sensitive interrupt trigger

- On-chip oscillator

- Power-on and power-off resets; low voltage detection circuitry (EEPROM)

- Available in 100-pin QFP and a reduced I/O 80-pin QFP

- *Note:* In the 80-pin package, there is no port H, and in port C, only pins PC0, PC4 and PC5 are available.

## 1.1 Mask options for the MC68HC05F12

There are three mask options available on the MC68HC05F12: STOP instruction (enable/disable), COP watchdog timer (enable/disable) and low voltage reset (LVR – enable/disable). These options are programmed during fabrication and must be specified by the customer at the time of ordering.

- 1. In the 80-pin package, there is no port H, and in port C only pins PC0, PC4 and PC5 are available.

- 2. When not being used to output eight LCD frontplanes, port G pins are input only

Figure 1-1 MC68HC05F12 block diagram

THIS PAGE LEFT BLANK INTENTIONALLY

# 2 **MODES OF OPERATION AND PIN** DESCRIPTIONS

The normal operating mode of the MC68HC05F12 is single chip mode. There is also a bootloader mode, primarily for factory test purposes. In addition to these modes, there are three low power modes which may be entered and exited at will from user mode: STOP, WAIT and data retention.

#### 2.1 Single-chip mode

This is the normal user operating mode, in which the device functions as a self-contained microcomputer unit, with all on-board peripherals and I/O ports available to the user. All address and data activity occurs within the MCU.

#### 2.2 Low power modes

#### 2.2.1 STOP mode

The STOP instruction places the MCU in its lowest power consumption mode. In STOP mode, the internal oscillator is turned off, halting all internal processing, including timer (and COP watchdog timer) operation.

During STOP mode, the core timer interrupt flags (CTOF and RTIF) and interrupt enable bits (TOFE and RTIE) in the CTCSR as well as the 16-bit timer flags in register TSR and interrupt enable bits in register TCR are cleared by internal hardware. The I-bit in the CCR is cleared to enable external interrupts. All other registers, the remaining bits in the CTCSR, and memory contents remain unaltered. All input/output lines remain unchanged. The processor can be brought out of STOP mode only by an interrupt (IRQ, keyboard, LVI), if enabled or RESET (external reset or low voltage reset - LVR). See Figure 2-1.

The STOP instruction can be disables by a mask option. When disabled, the STOP instruction is executed as a NOP.

## 2.2 WAIT mode

The WAIT instruction places the MCU in a low power consumption mode, though it consumes more power than in STOP mode. All CPU action is suspended, but the Core timer and the 16-bit timer remain active. An interrupt from the core timer, 16-bit timer,  $\overline{IRQ}$ , keyboard, or LVI, if enabled, will cause the MCU to exit the WAIT mode. An external reset, or LVR, causes the MCU to exit the wait mode.

During WAIT mode, the I-bit in CCR is cleared to enable interrupts. All other registers, memory and input/output lines remain in their previous state. The DMG is still active during WAIT mode.

## 2.2.3 Data retention mode

The contents of the RAM and CPU registers are retained at supply voltages as low as 2.0 Vdc. This is called the data retention mode, in which data is maintained but the device is not guaranteed to operate. If the voltage drops below  $V_{ROFF}$  the low voltage reset circuit generates a reset.

For lowest power consumption in data retention mode the device should be put into STOP mode before reducing the supply voltage, to ensure that all the clocks are stopped. If the device is not in STOP mode then it is recommended that RESET be held low whilst the power supply is outwith the normal operating range, to ensure that processing is suspended in an orderly manner.

Recovery from data retention mode, after the power supply has been restored, is by an external interrupt, or by pulling the RESET line high.

Figure 2-1 STOP and WAIT flowcharts

## 2.3 System options register (SOR)

The MC68HC05F12 MCU contains a system option register which is located at address \$4D. This register is used to control the LVI and the clock system.

|                         | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1  | bit 0 | State<br>on reset |

|-------------------------|---------|-------|-------|-------|-------|-------|-------|--------|-------|-------------------|

| System options register | \$003D  | LVIF  | LVIE  | LVION | SC    | IRQ   | 0     | KEYCLR | PUEN  | 0000 0000         |

#### LVIF, LVIE, LVION - Low voltage interrupt bits

The LVIF flag is set by the low voltage detection circuit, if the LVI is enabled and power supply VDD falls below  $V_{lvi}$ .

The low voltage interrupt must be enabled by first setting bit LVION Low Voltage Interrupt On and after that setting bit LVIE Low Voltage Interrupt Enable. After power on reset the LVI circuit is disabled.

#### SC — System clock option

After power on reset the internal bus frequency is f=3.58Mhz/2. If the bit SC System Clock is set the system speed is reduced to f=3.58Mhz/4, with the exception of the DTMF generator (Oscillator Frequency 3.58Mhz).

#### IRQ — Interrupt sensitivity

IRQ edge or level sensitivity

1 (set) - IRQ input edge and level sensitive

0 (clear) - IRQ input edge sensitive

#### KEYCLR — Keyboard interrupt clear

The keyboard wake-up interrupt status flag (Bit 7, \$1B) is cleared by writing a '1' to bit KEYCLR. A read access to this bit always returns '0'.

#### PUEN — PORTC pull-up enable

After power on reset the pull-up resistors in port C are disabled. If bit PUEN is set, the pull-up resistors in port C are enabled. Writing a '0' to PUEN disables the pull-up function.

## 2.4 Pin descriptions

## 2.4.1 VDD and VSS

Power is supplied to the microcomputer via these two pins. VDD is the positive supply pin and VSS is the ground pin.

It is in the nature of CMOS designs that very fast signal transitions occur on the MCU pins. These short rise and fall times place very high short-duration current demands on the power supply. To prevent noise problems, special care must be taken to provide good power supply bypassing at the MCU. Bypass capacitors should have good high-frequency characteristics and be as close to the MCU as possible. Bypassing requirements vary, depending on how heavily the MCU pins are loaded.

## 2.4.2 **IRQ**

This is an input-only pin for external interrupt sources. Interrupt triggering is selected using the IRQ bit in the SOR register, to be one of two options: either edge and level sensitive or edge sensitive only.

The IRQ pin contains an internal Schmitt trigger as part of its input to improve noise immunity.

## 2.4.3 **RESET**

This active low I/O pin is used to reset the MCU. Applying a logic zero to this pin forces the device to a known start-up state. An external RC-circuit can be connected to this pin to generate a power-on reset (POR) if required. In this case, the time constant must be great enough (at least 100ms) to allow the oscillator circuit to stabilise. This input has an internal Schmitt trigger to improve noise immunity. When a low voltage reset condition occurs internally, the RESET pin provides an active-low open drain output signal that may be used to reset external hardware. Other internal reset conditions are not visible at the RESET pin.

## 2.4.4 PA7–PA0/keyboard interrupt, PB7–PB0

These 16 I/O lines comprise the two 8-bit ports A and B. The state of any pin is software programmable, and on reset, the port pins are configured as inputs, with internal pull-up resistors. The eight I/O lines of port A are shared with the keyboard interrupt function.

During reset, these eight lines of port C are configured as inputs and each has an internal pull-up resistor. Port pin PC0 is shared with the timer input capture TCAP3.

## 2.4.6 PD7–PD0

During reset, the eight lines of port D are configured as inputs. As all port D pins are open drain outputs, an external pull-up resistor is needed when a pin is used as an output.

# 2.4.7 PE7–PE4, PE3/TCMP2, PE2/TCMP1, PE1/TCAP2, PE0/TCAP1

The eight pins of port E are general purpose I/O lines. These pins are all open drain, therefore an external pull-up resistor is needed when a pin is used as an output. Four of the pins, PE3–PE0, are shared with the timer system when the corresponding port E control register bits are set. PE0 and PE1 are shared with TCAP1 and TCAP2, PE2 and PE3 are shared with TCMP1 and TCMP2.

## 2.4.8 BP3–BP0, PF23–FP0

The LCD driver subsystem has a maximum of four frontplanes and 32 backplanes configured under software control. The four lines BP3–BP0 provide the backplane drive signals and the output lines FP23–FP0 provide the frontplane drive signals to the LCD unit. The remaining eight frontplanes are shared with port G.

### 2.4.9 PH1–PH0

Port H is a 2-bit output only port.

## 2.4.10 PG7-PG0/FP31-FP24

The eight pins of port G are shared with the frontplanes FP31–FP24. These lines are configured by default as input only, however when the corresponding bits are set in the port G control register, the lines are then connected to the LCD frontplane driver.

## 2.4.11 VLCD

The analogue part of the LCD controller can be supplied with an external voltage,  $V_{LCD}$ , using the VLCD pin. The value of  $V_{LCD}$  may not exceed the positive power supply voltage  $V_{DD}$ . When the INTVLCD bit in the LCD control register is set to 1, an internal voltage generator (approx. 3V, if  $V_{DD}$ >3V) is activated as the source of the analogue LCD supply voltage.

## 2.4.12 TNO and TNX

The TNO output provides dual tone DTMF or melody under program control. TNO is an open-drain output, and therefore requires an external pull-up resistor. The TNX output provides pacifier tones under program control.

## 2.4.13 OSC1 and OSC2

These pins provide control input for an on-chip oscillator circuit. A crystal or external clock signal connected to these pins supplies the oscillator clock. The oscillator frequency of 3.579 MHz provides the time base for the real-time clock and the DTMF/melody generator.

## 2.4.13.1 Crystal

The circuit shown in Figure 2-2(a) is recommended when using either a crystal or a ceramic resonator. Figure 2-2(d) provides the recommended capacitance and feedback resistance values. The internal oscillator is designed to interface with an AT-cut parallel-resonant quartz crystal resonator in the frequency range specified for  $f_{OSC}$  (see Section 11.4). Use of an external CMOS oscillator is recommended when crystals outside the specified ranges are to be used. The crystal and associated components should be mounted as close as possible to the input pins to minimize output distortion and start-up stabilization time. The manufacturer of the particular crystal being considered should be consulted for specific information.

## 2.4.13.2 External clock

An external clock should be applied to the OSC1 input, with the OSC2 pin left unconnected, as shown in Figure 2-2(c). The  $t_{OXOV}$  specification (see Section 11.4) does not apply when using an external clock input. The equivalent specification of the external clock source should be used in lieu of  $t_{OXOV}$ .

(c) External clock source connections

| Crystal              |         |         |      |  |  |  |  |  |  |

|----------------------|---------|---------|------|--|--|--|--|--|--|

|                      | 2MHz    | 4MHz    | Unit |  |  |  |  |  |  |

| R <sub>S</sub> (max) | 400     | 75      | Ω    |  |  |  |  |  |  |

| C <sub>0</sub>       | 5       | 7       | pF   |  |  |  |  |  |  |

| C <sub>1</sub>       | 8       | 12      | fF   |  |  |  |  |  |  |

| C <sub>OSC1</sub>    | 15 – 40 | 15 – 30 | pF   |  |  |  |  |  |  |

| C <sub>OSC2</sub>    | 15 – 30 | 15 – 25 | pF   |  |  |  |  |  |  |

| R <sub>P</sub>       | 10      | 10      | MΩ   |  |  |  |  |  |  |

| Q                    | 30 000  | 40 000  | _    |  |  |  |  |  |  |

(d) Crystal resonator parameters

Figure 2-2 Oscillator connections

# **3** MEMORY AND REGISTERS

The MC68HC05F12 has a 64K byte memory map consisting of registers (for I/O, control and status), user RAM, user ROM, EEPROM, bootloader ROM and reset and interrupt vectors as shown in Figure 3-1.

## 3.1 Registers

All the I/O, control and status registers of the MC68HC05F12 are contained within the first 64 byte block of the memory map, as detailed in Table 3-1.

## 3.2 RAM

The user RAM consists of 384 bytes of memory, from \$0050 to \$01CF. This is shared with a 64 byte stack area. The stack begins at \$00FF, and may extend down to \$00C0.

*Note:* Using the stack area for data storage or temporary work locations requires care to prevent the data from being overwritten due to stacking from an interrupt or subroutine call.

## 3.3 ROM

The user ROM occupies 12160 bytes of memory, from \$5000 to \$7F7F. In addition, there are 16 bytes of user vectors, from \$7FF0 to \$7FFF.

#### MEMORY AND REGISTERS

Table 3-1 Register outline

| Register Name                     | Address | bit 7    | bit 6 | bit 5 | bit 4   | bit 3 | bit 2 | bit 1 | bit 0   | State<br>on reset |

|-----------------------------------|---------|----------|-------|-------|---------|-------|-------|-------|---------|-------------------|

| Port A data (PORTA)               | \$0000  | PA7      | PA6   | PA5   | PA4     | PA3   | PA2   | PA1   | PA0     | undefined         |

| Key interrupt status (KISR)       | \$0000  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port B data (PORTB)               | \$0001  | PB7      | PB6   | PB5   | PB4     | PB3   | PB2   | PB1   | PB0     | undefined         |

| Port C data (PORTC)               | \$0002  | PC7      | PC6   | PC5   | PC4     | PC3   | PC2   | PC1   | PC0     | undefined         |

| Port D data (PORTD)               | \$0003  | PD7      | PD6   | PD5   | PD4     | PD3   | PD2   | PD1   | PD0     | undefined         |

| Port A data direction (DDRA)      | \$0004  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port B data direction (DDRB)      | \$0005  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port C data direction (DDRC)      | \$0006  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port D data direction ((DDRD)     | \$0007  |          |       |       |         |       |       |       |         | 0000 0000         |

| Core timer control/status (CTCSR) | \$0008  | TOF      | RTIF  | TOFE  | RTIE    | RTOF  | RRTIF | RT1   | RT0     | 0000 0011         |

| Core timer counter (CTCR)         | \$0009  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port E data (PORTE)               | \$000A  | PE7      | PE6   | PE5   | PE4     | PE3   | PE2   | PE1   | PE0     | undefined         |

| Port E data direction (DDRE)      | \$000B  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port E control (PECR)             | \$000C  |          |       |       |         |       | 0     |       | 0       | 0000 0000         |

| DTMF row freq. control (FCR)      | \$000D  | 0        | 0     | 0     | FCR4    | FCR3  | FCR2  | FCR1  | FCR0    | undefined         |

| DTMF column freq. control (FCC)   | \$000E  | 0        | 0     | 0     | FCC4    | FCC3  | FCC2  | FCC1  | FCC0    | undefined         |

| DTMF tone control (TNCR)          | \$000F  | MS1      | MS0   | TGER  | TGEC    | TNOE  | 0     | 0     | 0       | 0000 0000         |

|                                   |         |          |       |       |         |       |       |       |         |                   |

|                                   |         |          |       |       |         |       |       |       |         |                   |

| Port G data (PORTG)               | \$0012  | PG7      | PG6   | PG5   | PG4     | PG3   | PG2   | PG1   | PG0     | undefined         |

| Port G control (PGCR)             | \$0013  |          |       |       |         |       |       |       |         | 0000 0000         |

| Port H data (PORTH)               | \$0014  | PH7      | PH6   | PH5   | PH4     | PH3   | PH2   | PH1   | PH0     | 0000 0000         |

|                                   |         |          |       |       |         |       |       |       |         |                   |

| Key control (KCR)                 | \$001B  | KF       | KIE   | EDG5  | EDG4    | EDG3  | EDG2  | EDG1  | EDG0    | 0000 0000         |

| EEPROM prog. (EEPROG)             | \$001C  | 0        | CPEN  | 0     | ER1     | ER0   | LATCH | EERC  | EEPGM   | 0000 0000         |

|                                   |         |          |       |       |         |       |       |       |         |                   |

| LCD control (LCD)                 | \$001E  | WTLCDO   | FSEL1 | FSEL0 | INTVLCD | FDISP | MUX4  | MUX3  | EXTVON  | 0000 0000         |

|                                   |         |          |       |       |         |       |       |       |         |                   |

| Capture 1 high (ICR1H)            | \$0020  | (bit 15) |       |       |         |       |       |       | (bit 8) | undefined         |

| Capture 1 low (ICR1L)             | \$0021  |          |       |       |         |       |       |       |         | undefined         |

| Compare 1 high (OCR1H)            | \$0022  | (bit 15) |       |       |         |       |       |       | (bit 8) | undefined         |

| Compare 1 low (OCR1L)             | \$0023  |          |       |       |         |       |       |       |         | undefined         |

| Capture 2 high (ICR2H)            | \$0024  | (bit 15) |       |       |         |       |       |       | (bit 8) | undefined         |

| Capture 2 low (ICR2L)             | \$0025  |          |       |       |         |       |       |       |         | undefined         |

| Register Name                  | Address | bit 7    | bit 6 | bit 5 | bit 4 | bit 3 | bit 2  | bit 1  | bit 0   | State<br>on reset |

|--------------------------------|---------|----------|-------|-------|-------|-------|--------|--------|---------|-------------------|

| Compare 2 high (OCR2H)         | \$0026  | (bit 15) |       |       |       |       |        |        | (bit 8) | undefind          |

| Compare 2 low (OCR2L)          | \$0027  |          |       |       |       |       |        |        |         | undefined         |

| Counter high (CNTH)            | \$0028  | (bit 15) |       |       |       |       |        |        | (bit 8) | 1111 1111         |

| Counter low (CNTL)             | \$0029  |          |       |       |       |       |        |        |         | 1111 1100         |

| Alternate counter high (ACNTH) | \$002A  | (bit 15) |       |       |       |       |        |        | (bit 8) | 1111 1111         |

| Alternate counter low (ACNT)   | \$002B  |          |       |       |       |       |        |        |         | 1111 1100         |

| Timer control 1 (TCR1)         | \$002C  | ICI1E    | ICI2E | OCI1E | TOIE  | CO1E  | IEDG1  | IEDG2  | OLVL1   | 0000 0uu0         |

| Timer control 2 (TCR2)         | \$002D  | 0        | 0     | OCI2E | 0     | CO2E  | 0      | 0      | OLVL2   | 0000 0000         |

| Timer status (TSR)             | \$002E  | IC1F     | IC2F  | OC1F  | TOF   | TCAP1 | TCAP2  | OC2F   | 0       | uuuu uuu0         |

|                                |         |          |       |       |       |       |        |        |         |                   |

| Capture 3 high (ICR3H)         | \$0030  | (bit 15) |       |       |       |       |        |        | (bit 8) | undefined         |

| Capture 3 low (ICR3L)          | \$0031  |          |       |       |       |       |        |        |         | undefined         |

| Compare 3 high (OCR3H)         | \$0032  | (bit 15) |       |       |       |       |        |        | (bit 8) | undefined         |

| Compare 3 low (OCR3L)          | \$0033  |          |       |       |       |       |        |        |         | undefined         |

|                                |         |          |       |       |       |       |        |        |         |                   |

| System options (SOR)           | \$003D  | LVIF     | LVIE  | LVION | SC    | IRQ   | KEYMUX | KEYCLR | PUEN    | 0000 0000         |

|                                |         |          |       |       |       |       |        |        |         |                   |

|                                |         |          |       |       |       |       |        |        | u = u   | indefined         |

Table 3-1 Register outline

*Note:* For compatibility, unused and reserved bits (shaded) should always be cleared, when writing to them

## 3.4 Bootloader ROM

The MC68HC05F12 has 112 bytes of bootloader ROM, from \$7F80 to \$7FEF. These are included primarily for factory test purposes.

## 3.5 EEPROM

256 bytes of user EEPROM reside at addresses \$0400 to \$04FF.

Programming or erasing the EEPROM can be done by the user on a single byte basis; erasing may also be performed on a block or bulk basis. All programming or erasing is accomplished by manipulating the programming register (EEPROG), located at address \$001C.

*Note:* The erased state of an EEPROM byte is '\$FF'. This means that a write forces zeros to the bits specified, whilst bits defined as ones are unchanged by a write operation.

### 3.5.1 EEPROM programming register

|                             | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|-----------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| EEPROM programming (EEPROG) | \$001C  | 0     | CPEN  | 0     | ER1   | ER0   | LATCH | EERC  | EEPGM | 0000 0000         |

#### **CPEN** — Charge pump enable

- 1 (set) Charge pump enabled.

- 0 (clear) Charge pump disabled.

When set, CPEN enables the charge pump which produces the internal programming voltage. This bit should be set at the same time as the LATCH bit. The programming voltage will not be available until EEPGM is set. The charge pump should be disabled when not in use. CPEN is readable and writable and is cleared by reset.

#### ER1, ER0 — Erase select bits

ER1 and ER0 are used to select either single byte programming or one of three erase modes: byte, block, or bulk. Table 3-2 shows the mode selected for each bit configuration. These bits are readable and writable and are cleared by reset.

- In byte erase mode, only the selected byte is erased.

- In block erase mode, a 32-byte block of EEPROM is erased. The EEPROM memory space is divided into four 64-byte blocks (\$0400 – \$043F, \$0440 –

| ER1 | ER0 | Mode        |

|-----|-----|-------------|

| 0   | 0   | Program     |

| 0   | 1   | Byte erase  |

| 1   | 0   | Block erase |

| 1   | 1   | Bulk erase  |

047F, 0480 - 04BF and 04C0 - 04FF) and performing a block erase on any address within a block will erase the entire block.

- In bulk erase mode, the entire 256 bytes of EEPROM are erased.

#### LATCH — EEPROM latch bit

- 1 (set) EEPROM address and data buses are configured for programming.

- 0 (clear) EEPROM address and data buses are configured for normal operation.

When set, the LATCH bit configures the EEPROM address and data buses for programming. In addition, writes to the EEPROM array cause the address and data buses to be latched. This bit is readable and writable, but reads from the EEPROM array are inhibited if the LATCH bit is set and a write to the EEPROM space has taken place. When this bit is clear, address and data buses are configured for normal operation. Reset clears this bit.

#### EERC — EEPROM RC oscillator control

- 1 (set) Use internal RC oscillator for EEPROM.

- 0 (clear) Use CPU clock for EEPROM.

When this bit is set, the EEPROM memory array uses the internal RC oscillator instead of the CPU clock. After setting the EERC bit, the user should wait a time  $t_{RCON}$  to allow the RC oscillator to stabilize. This bit is readable and writable and should be set by the user when the internal bus frequency falls below 1.5MHz. Reset clears this bit.

#### EEPGM — EEPROM programming power enable

- 1 (set) Programming power connected to the EEPROM array.

- 0 (clear) Programming power switched off.

EEPGM must be set to enable the EEPGM function. When set, EEPGM turns on the charge pump and enables the programming (or erasing) power to the EEPROM array. When clear, this power is switched off. This will enable pulsing of the programming voltage to be controlled internally. This bit can be read at any time, but can only be written to if LATCH = 1, i.e. if LATCH is not set, then EEPGM cannot be set. Reset clears this bit.

# 3.5.2 **Programming and erasing procedures**

To program a byte of EEPROM, set LATCH = CPEN = 1, set ER1 = ER0 = 0, write data to the desired address and then set EEPGM for a time  $t_{EPGM}$ .

There are three possibilities for erasing data from the EEPROM array, depending on how much data is affected.

- To erase a byte of EEPROM, set LATCH = CPEN = 1, set ER1 = 0 and ER0 = 1, write data to the desired address and then set EEPGM for a time t<sub>EBYTE</sub>.

- To erase a block of EEPROM, set LATCH = CPEN = 1, set ER1 = 1 and ER0 = 0, write data to any address in the block and then set EEPGM for a time t<sub>EBLOCK</sub>.

- To bulk erase the EEPROM, set LATCH = CPEN = 1, set ER1 = ER0 = 1, write data to any address in the array and then set EEPGM for a time t<sub>EBULK</sub>.

To terminate the programming or erase sequence, clear EEPGM, wait for a time  $t_{FPV}$  to allow the programming voltage to fall, and then clear LATCH and CPEN to release the buses. Following each erase or programming sequence, clear all programming control bits.

# 3.5.3 Sample EEPROM programming sequence

The following program is an example of the EEPROM programming sequence, using the timer to implement the required delay and assuming a 1 MHz bus frequency.

| TCNT<br>TOF<br>PROG<br>CPEN<br>ER1<br>ER0<br>LATCH<br>EERC<br>EEPGM<br>EESTAF | EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | \$001C<br>6<br>4<br>3<br>2<br>1<br>0<br>\$0400                | TIMER CONTROL AND STATUS REGISTER<br>TIMER COUNTER REGISTER<br>TOF BIT OF TCSR<br>EEPROM PROGRAM REGISTER<br>CHARGE PUMP ENABLE BIT<br>ERASE SELECT BIT 1<br>ERASE SELECT BIT 0<br>LATCH BIT<br>RC/OSC SELECTOR BIT<br>EEPROM PROGRAM BIT<br>START ADDRESS OF EEPROM<br>DUMMY DATA |

|-------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                               | BSET<br>BSET<br>BCLR                                        | EERC, PROG<br>DELAY<br>CPEN, PROG<br>LATCH, PROG<br>ER1, PROG | SELECT RC OSCILLATOR<br>RC OSCILLATOR STABILIZATION<br>TURN ON CHARGE PUMP<br>ENABLE LATCH BIT<br>SELECT PROGRAM (NOT ERASE)<br>SELECT PROGRAM (NOT ERASE)                                                                                                                         |

|                                                                               | STA<br>BSET<br>JSR<br>BCLR<br>JSR                           | DELAY<br>EEPGM, PROG                                          | ENABLE PROGRAMMING POWER<br>WAIT FOR PROGRAMMING TIME<br>CLEAR EEPGM<br>WAIT FOR PROG VOLTAGE TO FALL                                                                                                                                                                              |

|                                                                               | BCLR                                                        | CPEN, PROG<br>EESTART                                         | DISABLE CHARGE PUMP                                                                                                                                                                                                                                                                |

| OUT                                                                           | RTS                                                         |                                                               |                                                                                                                                                                                                                                                                                    |

| OUT1                                                                          | SEC<br>RTS                                                  |                                                               | FLAG AN ERROR                                                                                                                                                                                                                                                                      |

| *титс                                                                         | ROUTIN                                                      | E GIVES & 15MG                                                | (+/-1MS) DELAY AT 1 MHZ BUS THE S                                                                                                                                                                                                                                                  |

\*THIS ROUTINE GIVES A 15MS (+/-1MS) DELAY AT 1 MHZ BUS. THE SAME DELAY \* ROUTINE IS USED IN THIS EXAMPLE FOR SIMPLICITY, USING THE LONGEST DELAY \* TIME. USERS WILL WANT TO WRITE SHORTER DELAY ROUTINES FOR APPLICATIONS \*IN WHICH SPEED IS IMPORTANT.

| DELAY | EQU   | *         |                   |

|-------|-------|-----------|-------------------|

|       | LDX   | #15       | COUNT OF 15       |

| TIMLP | BCLR  | TOF, TCSR | CLEAR TOF         |

|       | BRCLR | TOF, TCSR | WAIT FOR TOF FLAG |

|       | DECX  |           |                   |

|       | BNE   | TIMLP     | COUNT DOWN TO 0   |

|       | RTS   |           |                   |

|       |       |           |                   |

MC68HC05F12

# **4** PARALLEL INPUT/OUTPUT PORTS

The MC68HC05F12 has a total of 50 I/O lines, arranged as six 8-bit ports and one 2-bit port. The I/O lines are individually programmable as either input or output, under the software control of the data direction registers. Port A can also be configured to respond to keyboard interrupts.

To avoid glitches on the output pins, data should be written to the I/O port data register before writing ones to the corresponding data direction register bits to set the pins in output mode.

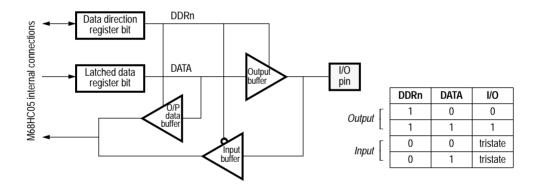

# 4.1 Input/output programming

The bidirectional port lines may be programmed as inputs or outputs under software control. The direction of each pin is determined by the state of the corresponding bit in the port data direction register (DDR). Each I/O port has an associated DDR. Any I/O port pin is configured as an output if its corresponding DDR bit is set to a logic one. A pin is configured as an input if its corresponding DDR bit is cleared.

At power-on or reset, all DDRs are cleared, thus configuring all port pins as inputs. The data direction registers can be written to or read by the MCU. During the programmed output state, a read of the data register actually reads the value of the output data latch and not the I/O pin. The operation of the standard port hardware is shown schematically in Figure 4-2.

This is further summarized in Table 4-1, which shows the effect of reading from, or writing to an I/O pin in various circumstances. Note that the read/write signal shown is internal and not available to the user.

# 4.2 Port A

Port A is an 8-bit bidirectional port which is equipped with a keyboard interrupt. All eight lines have internal pull-up resistors, which are required when the port is in input mode. On reset, this port is configured as a standard I/O port comprising a data register and a data direction register.

Reset does not affect the state of the data register, but clears the data direction register, thereby returning all ports pins to input mode. Writing a 1 to any DDR bit sets the corresponding port pin to output mode. As every pin configured as an input contributes to the keyboard interrupt, it is possible to disable a single pin by configuring it as an output.

# 4.2.1 Keyboard interrupt

Provided that the interrupt mask bit of the condition code register is cleared, the keyboard interrupt facility is enabled by setting the keyboard interrupt bit (KIE) in the Key Control register.

On detection of a high-to-low transition, the interrupt inputs PA6 and PA7 are triggered. The trigger edges of the interrupt lines, PA0–PA5, can be programmed using the EDG0–EDG5 bits in the Key Control register. If one of these bits is cleared, after reset the corresponding interrupt is falling-edge sensitive. If, however, one of them is set, after reset the corresponding interrupt is rising-edge sensitive. The internal pull-up resistors of input lines, PA7–PA0, are disabled, if rising-edge sensitivity is selected.

When a correct transition is detected, on any of this port's pins, a keyboard interrupt request is generated, and the corresponding interrupt status flag of the interrupt status register, IRSTATE, is set. The interrupt status register is an 8-bit register which has the same address as PORTA, \$0000. This register can be read if the KEYMUX bit in the system option register is set. If KIE is set, a keyboard interrupt is generated and the keyboard status flag, KF, is set by generating the logical OR of the eight interrupt state register outputs.

The 8 interrupt state register flags can be reset in three ways:

- 1) Completely, if the chip is reset.

- 2) Completely, if a 1 is written to KEYCLR, in the system option register.

- Individually, if a 1 is written to the corresponding bit position of the interrupt state register (\$00 with KEYMUX = 1, in the system option register).

Figure 4-1 Structure of port with keyboard interrupt

# 4.2.1.1 Key control register (KCR)

This register contains eight bits, two of which are used to control the keyboard interrupt facility, the others determine the keyboard interrupt edges.

|                            | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |