### General Description

The MAX961–MAX964/MAX997/MAX999 are low-power, ultra-high-speed comparators with internal hysteresis. These devices are optimized for single +3V or +5V operation. The input common-mode range extends 100mV Beyond-the-Rails<sup>™</sup>, and the outputs can sink or source 4mA to within 0.52V of GND and V<sub>CC</sub>. Propagation delay is 4.5ns (5mV overdrive), while supply current is 5mA per comparator.

The MAX961/MAX963/MAX964 and MAX997 have a shutdown mode in which they consume only 270µA supply current per comparator. The MAX961/MAX963 provide complementary outputs and a latch-enable feature. Latch enable allows the user to hold a valid comparator output. The MAX999 is available in a tiny SOT23-5 package. The single MAX961/MAX997 and dual MAX962 are available in space-saving 8-pin µMAX packages.

### **Applications**

- Single 3V/5V Systems

- Portable/Battery-Powered Systems

- Threshold Detectors/Discriminators

- GPS Receivers

- Line Receivers

- Zero-Crossing Detectors

- High-Speed Sampling Circuits

| PART   | NO. OF<br>COMPARATORS | COMPLEMENTARY<br>OUTPUT | SHUTDOWN | LATCH<br>ENABLE | PACKAGE    |  |

|--------|-----------------------|-------------------------|----------|-----------------|------------|--|

| MAX961 | 1                     | Yes                     | Yes      | Yes             | 8 SO/µMAX  |  |

| MAX962 | 2                     | No                      | No       | No              | 8 SO/µMAX  |  |

| MAX963 | 2                     | Yes                     | Yes      | Yes             | 14 SO      |  |

| MAX964 | 4                     | No                      | Yes      | No              | 16 SO/QSOP |  |

| MAX997 | 1                     | No                      | Yes      | No              | 8 SO/µMAX  |  |

| MAX999 | 1                     | No                      | No       | No              | 5 SOT23    |  |

Beyond-the-Rails is a trademark of Maxim Integrated Products.

###

Selector Guide

### \_Features

- Ultra-Fast, 4.5ns Propagation Delay

- Ideal for +3V and +5V Single-Supply Applications

- Beyond-the-Rails Input Voltage Range

- Low, 5mA Supply Current (MAX997/MAX999)

- ♦ 3.5mV Internal Hysteresis for Clean Switching

- Output Latch (MAX961/MAX963)

- TTL/CMOS-Compatible Outputs

- 270µA Shutdown Current per Comparator (MAX961/MAX963/MAX964/MAX997)

- Available in Space-Saving Packages: 5-Pin SOT23 (MAX999) 8-Pin µMAX (MAX961/MAX962/MAX997) 16-Pin QSOP (MAX964)

### \_Ordering Information

| PART                | TEMP. RANGE    | PIN-<br>PACKAGE | SOT<br>TOP MARK |  |

|---------------------|----------------|-----------------|-----------------|--|

| MAX961ESA           | -40°C to +85°C | 8 SO            | _               |  |

| MAX961EUA           | -40°C to +85°C | 8 μΜΑΧ          | _               |  |

| MAX962ESA           | -40°C to +85°C | 8 SO            | —               |  |

| MAX962EUA           | -40°C to +85°C | 8 µMAX          | _               |  |

| MAX963ESD           | -40°C to +85°C | 14 SO           | _               |  |

| MAX964ESE           | -40°C to +85°C | 16 Narrow SO    | _               |  |

| MAX964EEE           | -40°C to +85°C | 16 QSOP         | _               |  |

| MAX997ESA           | -40°C to +85°C | 8 SO            | _               |  |

| MAX997EUA           | -40°C to +85°C | 8 μΜΑΧ          | _               |  |

| <b>MAX999</b> EUK-T | -40°C to +85°C | 5 SOT23-5       | ACAB            |  |

|                     |                |                 |                 |  |

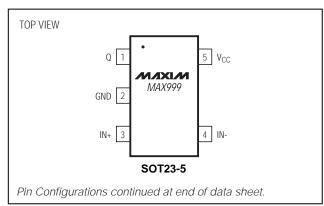

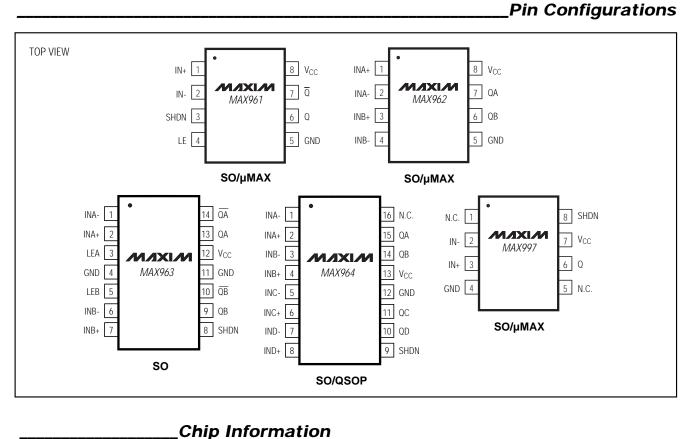

### \_Pin Configurations

\_ Maxim Integrated Products 1

*For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800 For small orders, phone 408-737-7600 ext. 3468.*

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub> to GND0.3V to +6V                     |

|-----------------------------------------------------------------------|

| All Other Pins $0.3V$ to (V <sub>CC</sub> + $0.3V$ )                  |

| Duration of Output Short Circuit to GND or V <sub>CC</sub> Continuous |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                 |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)571mW/°C                     |

| 8-Pin SO (derate 5.88mW/°C above +70°C)471mW/°C                       |

| 8-Pin µMAX (derate 4.10mW/°C above +70°C)330mW/°C                     |

14-Pin SO (derate 8.33mW/°C above +70°C)......667mW/°C 16-Pin SO (derate 8.70mW/°C above +70°C).....696mW/°C 16-Pin QSOP (derate 8.33mW/°C above +70°C)....667mW/°C Operating Temperature Range MAX96\_E/MAX99\_E.....-40°C to +85°C Storage Temperature Range .....-40°C to +160°C Lead Temperature (soldering, 10sec).....+300°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +2.7V to +5.5V, V<sub>CM</sub> = 0V, C<sub>OUT</sub> = 5pF, V<sub>SHDN</sub> = 0V, V<sub>LE</sub> = 0V, unless otherwise noted.) (Note 1)

|                                    | CVMDOI               | CONDITIONS -                                              |                    | TA = +25°C            |      |                       | TMIN to TMAX        |                       | UNITS  |

|------------------------------------|----------------------|-----------------------------------------------------------|--------------------|-----------------------|------|-----------------------|---------------------|-----------------------|--------|

| PARAMETER                          | SYMBOL               |                                                           |                    | MIN                   | TYP  | MAX                   | MIN                 | MAX                   | UNITS  |

| Supply Voltage                     | V <sub>CC</sub>      |                                                           |                    | 2.7                   |      | 5.5                   | 2.7                 | 5.5                   | V      |

| Input Common-Mode Voltage<br>Range | VCMR                 | (Note 2)                                                  |                    | -0.1                  |      | V <sub>CC</sub> + 0.1 | -0.1                | V <sub>CC</sub> + 0.1 | V      |

| Input-Referred Trip Points         | VTRIP                | V <sub>CM</sub> = - 0.1V<br>or 5.1V,                      | µMAX,<br>SOT23     |                       | ±2.0 | ±3.5                  |                     | ±6.0                  | - mV   |

| input-keleneu mp roints            | VIRIP                | V <sub>CC</sub> = 5V<br>(Note 3)                          | All other packages |                       | ±2.0 | ±3.5                  |                     | ±4.0                  |        |

| Input-Referred Hysteresis          |                      |                                                           |                    |                       | 3.5  |                       |                     |                       | mV     |

| Input Offset Voltage               | Vos                  | V <sub>CM</sub> = - 0.1V<br>or 5.1V,                      | µMAX,<br>SOT23     |                       | ±0.5 | ±1.5                  |                     | ±4.5                  | mV     |

| input onset voltage                |                      | V <sub>CC</sub> = 5V<br>(Note 4)                          | All other packages |                       | ±0.5 | ±1.5                  |                     | ±2.0                  |        |

|                                    | IB                   |                                                           | µMAX,<br>SOT23     |                       |      | ±15                   |                     | ±30                   | - μΑ   |

| Input Bias Current                 |                      |                                                           | All other packages |                       |      | ±15                   |                     | ±15                   |        |

| Differential Input Clamp Voltage   |                      | $V_{CC} = 5.5V, V_{IN-} = 0V,$<br>$I_{IN+} = 100\mu A$    |                    |                       | 2.1  |                       |                     |                       | V      |

| Input Capacitance                  |                      |                                                           |                    |                       | 3    |                       |                     |                       | рF     |

| Differential Input Impedance       | Rind                 | $V_{CC} = 5V$                                             |                    |                       | 8    |                       |                     |                       | kΩ     |

| Common-Mode Input Impedance        | RINCM                | $V_{CC} = 5V$                                             |                    |                       | 130  |                       |                     |                       | kΩ     |

| Common Made Dejection Datio        | Rejection Ratio CMRR | $V_{CC} = 5V,$<br>$V_{CM} = -0.1V$<br>to 5.1V<br>(Note 5) | µMAX,<br>SOT23     |                       | 0.1  | 0.3                   |                     | 1.0                   | mV/V   |

| Common-Mode Rejection Ratio        |                      |                                                           | All other packages |                       | 0.1  | 0.3                   |                     | 0.5                   | 111V/V |

| Power-Supply Rejection Ratio       | PSRR                 | V <sub>CM</sub> = 0V (Note 6)                             |                    |                       | 0.05 | 0.3                   |                     | 0.3                   | mV/V   |

| Output High Voltage                | Voh                  | ISOURCE = 4mA                                             |                    | V <sub>CC</sub> - 0.5 | 52   |                       | V <sub>CC</sub> - C | 0.52                  | V      |

| Output Low Voltage                 | Vol                  | I <sub>SINK</sub> = 4mA                                   |                    |                       |      | 0.52                  |                     | 0.52                  | V      |

| Capacitive Slew Current            |                      | V <sub>OUT</sub> = 1.4V, V <sub>CC</sub> = 2.7V           |                    | 30                    | 60   |                       |                     |                       | mA     |

### ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = +2.7V to +5.5V, V<sub>CM</sub> = 0V, C<sub>OUT</sub> = 5pF, V<sub>SHDN</sub> = 0V, V<sub>LE</sub> = 0V, unless otherwise noted.) (Note 1)

|                                        | SYMBOL           |                                                                    | Т                              | A = +25 | °C                             | T <sub>MIN</sub> to            |                                |       |

|----------------------------------------|------------------|--------------------------------------------------------------------|--------------------------------|---------|--------------------------------|--------------------------------|--------------------------------|-------|

| PARAMETER                              | STMBOL           | CONDITIONS                                                         | MIN                            | TYP     | MAX                            | MIN                            | MAX                            | UNITS |

| Output Capacitance                     |                  |                                                                    |                                | 4       |                                |                                |                                | рF    |

|                                        |                  | MAX961/MAX963, $V_{CC} = 5V$                                       |                                | 8.5     | 11                             |                                | 11                             |       |

| Supply Current<br>per Comparator       | Icc              | MAX962/MAX964, $V_{CC} = 5V$                                       |                                | 6.5     | 8                              |                                | 9                              | mA    |

| per comparator                         |                  | MAX997/MAX999, $V_{CC} = 5V$                                       |                                | 5       | 6.5                            |                                | 6.5                            |       |

| Shutdown Supply Current per Comparator | ISHDN            | MAX961/MAX963/MAX964/<br>MAX997, V <sub>CC</sub> = 5V              |                                | 0.27    | 0.5                            |                                | 0.5                            | mA    |

| Shutdown Output<br>Leakage Current     |                  | MAX961/MAX963/MAX964/ MAX997, $V_{OUT} = 0.5V$ and $V_{CC} - 0.5V$ |                                |         | 1                              |                                | 20                             | μA    |

| Rise/Fall Time                         | tR, tF           | $V_{CC} = 5V$                                                      |                                | 2.3     |                                |                                |                                | ns    |

| Logic Input High                       | Vih              |                                                                    | (V <sub>CC</sub> / 2)<br>+ 0.4 |         |                                | (V <sub>CC</sub> / 2)<br>+ 0.4 |                                | V     |

| Logic Input Low                        | VIL              |                                                                    |                                |         | (V <sub>CC</sub> / 2)<br>- 0.4 |                                | (V <sub>CC</sub> / 2)<br>- 0.4 | V     |

| Logic Input Current                    | IIL, IIH         | $V_{LOGIC} = 0V \text{ or } V_{CC}$                                |                                |         | ±15                            |                                | ±30                            | μA    |

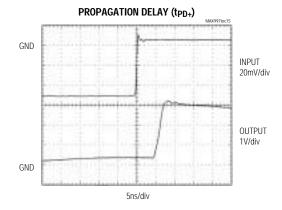

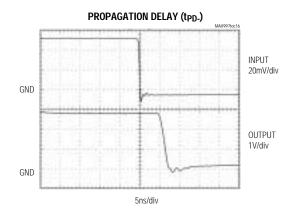

| Propagation Delay                      | t <sub>PD</sub>  | 5mV overdrive (Note 7)                                             |                                | 4.5     | 7                              |                                | 8.5                            | ns    |

| Differential Propagation<br>Delay      | t <sub>PD</sub>  | Between any two channels or outputs $(Q/\overline{Q})$             |                                | 0.3     |                                |                                |                                | ns    |

| Propagation-Delay Skew                 | tskew            | Between tPD- and tPD+                                              |                                | 0.3     |                                |                                |                                | ns    |

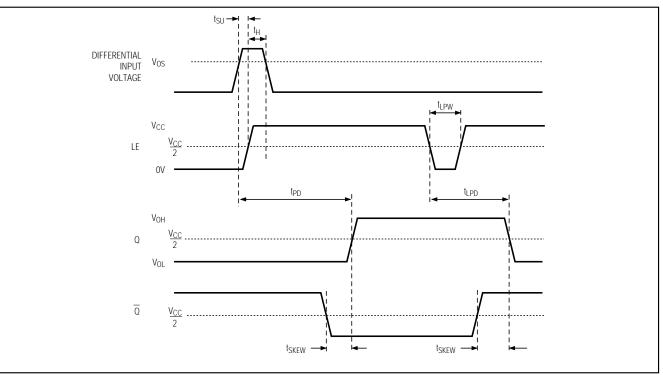

| Data-to-Latch Setup Time               | tsu              | MAX961/MAX963 (Note 8)                                             |                                |         | 5                              |                                | 5                              | ns    |

| Latch-to-Data Hold Time                | tн               | MAX961/MAX963 (Note 8)                                             |                                |         | 5                              |                                | 5                              | ns    |

| Latch Pulse Width                      | t <sub>LPW</sub> | MAX961/MAX963 (Note 8)                                             |                                |         | 5                              |                                | 5                              | ns    |

| Latch Propagation Delay                | t <sub>LPD</sub> | MAX961/MAX963 (Note 8)                                             |                                |         | 10                             |                                | 10                             | ns    |

| Shutdown Time                          | toff             | Delay until output is high-Z (>10k $\Omega$ )                      |                                | 150     |                                |                                |                                | ns    |

| Shutdown Disable Time                  | ton              | Delay until output is valid                                        |                                | 250     |                                |                                |                                | ns    |

Note 1: The MAX961EUA/MAX962EUA/MAX997EUA/MAX999EUK are 100% production tested at  $T_A = +25^{\circ}C$ ; all temperature specifications are guaranteed by design.

Note 2: Inferred by CMRR. Either input can be driven to the absolute maximum limit without false output inversion, provided that the other input is within the input voltage range.

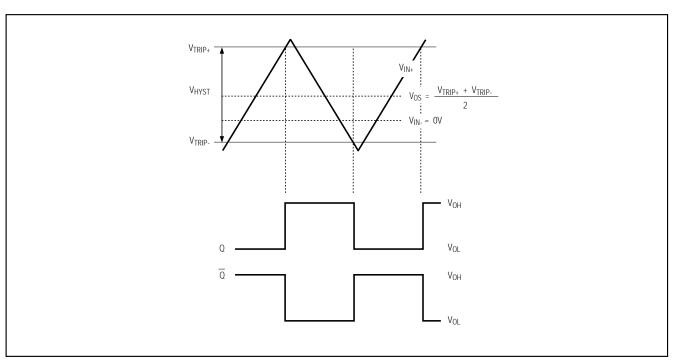

Note 3: The input-referred trip points are the extremities of the differential input voltage required to make the comparator output change state. The difference between the upper and lower trip points is equal to the width of the input-referred hysteresis zone. (See Figure 1.)

Note 4: Input offset voltage is defined as the mean of the trip points.

Note 5: CMRR = ( $V_{OSL} - V_{OSH}$ ) / 5.2V, where  $V_{OSL}$  is the offset at  $V_{CM}$  = -0.1V and  $V_{OSH}$  is the offset at  $V_{CM}$  = 5.1V.

Note 6: PSRR = ( $V_{OS}2.7 - V_{OS}5.5$ ) / 2.8V, where  $V_{OS}2.7$  is the offset voltage at  $V_{CC} = 2.7V$ , and  $V_{OS}5.5$  is the offset voltage at  $V_{CC} = 5.5V$ .

**Note 7:** Propagation delay for these high-speed comparators is guaranteed by design characterization because it cannot be accurately measured using automatic test equipment. A statistically significant sample of devices is characterized with a 200mV step and 100mV overdrive over the full temperature range. Propagation delay can be guaranteed by this characterization, since DC tests ensure that all internal bias conditions are correct. For low overdrive conditions, VTRIP is added to the overdrive.

Note 8: Guaranteed by design.

###

MAX961-MAX964/MAX997/MAX999

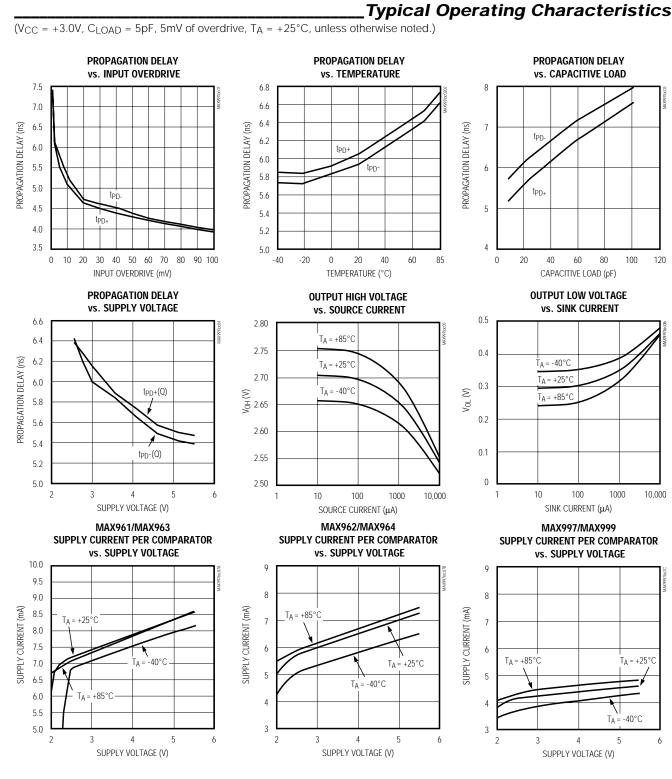

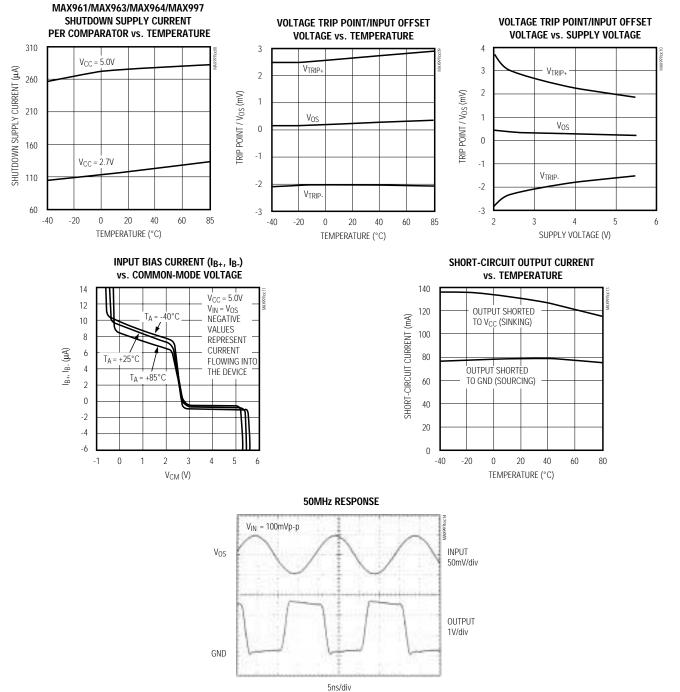

### \_Typical Operating Characteristics (continued)

$(V_{CC} = +3.0V, C_{LOAD} = 5pF, 5mV of overdrive, T_A = +25°C, unless otherwise noted.)$

MAX961-MAX964/MAX997/MAX999

# MAX961-MAX964/MAX997/MAX999

###

(V<sub>CC</sub> = +3.0V, C<sub>LOAD</sub> = 5pF, 5mV of overdrive,  $T_A$  = +25°C, unless otherwise noted.)

### \_Pin Description

| PIN    |        |        |        |        |        |                 | FUNCTION                                                                                              |  |  |  |

|--------|--------|--------|--------|--------|--------|-----------------|-------------------------------------------------------------------------------------------------------|--|--|--|

| MAX997 | MAX999 | MAX961 | MAX962 | MAX963 | MAX964 | NAME            | FUNCTION                                                                                              |  |  |  |

| 1, 5   | —      |        | _      | _      | —      | N.C.            | No Connection                                                                                         |  |  |  |

| 2      | 4      | 2      | 2      | 1      | 1      | IN-, INA-       | Comparator A Inverting Input                                                                          |  |  |  |

| 3      | 3      | 1      | 1      | 2      | 2      | IN+, INA+       | Comparator A Noninverting Input                                                                       |  |  |  |

| _      | _      | 4      | _      | 3, 5   | _      | LE, LEA,<br>LEB | Latch-Enable Input. The output latches when LE_<br>is high. The latch is transparent when LE_ is low. |  |  |  |

| 4      | 2      | 5      | 5      | 4, 11  | 12     | GND             | Ground                                                                                                |  |  |  |

| _      | _      | _      | _      |        | 16     | N.C.            | No Connect. Connect to GND to prevent para-<br>sitic feedback.                                        |  |  |  |

| —      | -      | —      | 4      | 6      | 3      | INB-            | Comparator B Inverting Input                                                                          |  |  |  |

| _      | —      | _      | 3      | 7      | 4      | INB+            | Comparator B Noninverting Input                                                                       |  |  |  |

|        | _      |        | _      | _      | 5      | INC-            | Comparator C Inverting Input                                                                          |  |  |  |

|        | _      |        | _      | —      | 6      | INC+            | Comparator C Noninverting Input                                                                       |  |  |  |

| _      | —      | _      |        | _      | 7      | IND-            | Comparator D Inverting Input                                                                          |  |  |  |

| _      | —      | _      | _      | _      | 8      | IND+            | Comparator D Noninverting Input                                                                       |  |  |  |

| 8      | _      | 3      | _      | 8      | 9      | SHDN            | Shutdown Input. The device shuts down when SHDN is high.                                              |  |  |  |

| _      | _      | —      | 6      | 9      | 14     | QB              | Comparator B Output                                                                                   |  |  |  |

| _      | _      | —      | _      | —      | 11     | QC              | Comparator C Output                                                                                   |  |  |  |

|        | _      | _      | _      |        | 10     | QD              | Comparator D Output                                                                                   |  |  |  |

| _      | _      |        |        | 10     | _      | QB              | Comparator B Complementary Output                                                                     |  |  |  |

| 7      | 5      | 8      | 8      | 12     | 13     | V <sub>CC</sub> | Positive Supply Input (V <sub>CC</sub> to GND must be<br>≤5.5V)                                       |  |  |  |

| 6      | 1      | 6      | 7      | 13     | 15     | Q, QA           | Comparator A TTL Output                                                                               |  |  |  |

| _      | _      | 7      | _      | 14     | —      | Q, QA           | Comparator A Complementary Output                                                                     |  |  |  |

### **Detailed Description**

The MAX961–MAX964/MAX997/MAX999 single-supply comparators feature internal hysteresis, ultra-high-speed operation, and low power consumption. Their outputs are guaranteed to pull within 0.52V of either rail without external pull-up or pull-down circuitry. Beyond-the-Rails<sup>™</sup> input voltage range and low-voltage, single-supply operation make these devices ideal for portable equipment. These comparators all interface directly to CMOS logic.

### Timing

Most high-speed comparators oscillate in the linear region because of noise or undesirable parasitic feedback. This can occur when the voltage on one input is close to or equal to the voltage on the other input. These devices have a small amount of internal hysteresis to counter parasitic effects and noise.

The added hysteresis of the MAX961–MAX964/MAX997/ MAX999 creates two trip points: one for the rising input voltage and one for the falling input voltage (Figure 1). The difference between the trip points is the hysteresis. When the comparator's input voltages are equal, the hysteresis effectively causes one comparator input voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. Standard comparators require hysteresis to be added with external resistors. The fixed internal hysteresis eliminates these resistors.

The MAX961/MAX963 include internal latches that allow storage of comparison results. LE has a high input impedance. If LE is low, the latch is transparent (i.e., the comparator operates as though the latch is not present). The comparator's output state is stored when LE is pulled high. All timing constraints must be met when using the latch function (Figure 2).

### Input Stage Circuitry

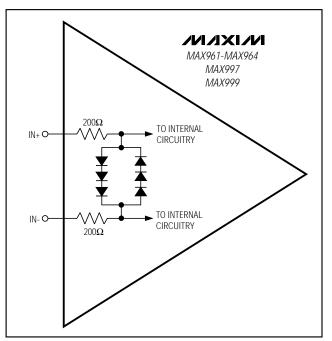

The MAX961–MAX964/MAX997/MAX999 include internal protection circuitry that prevents damage to the precision input stage from large differential input voltages. This protection circuitry consists of two groups of three front-to-back diodes between IN+ and IN-, as well as two  $200\Omega$  resistors (Figure 3). The diodes limit the differential voltage applied to the comparator's internal circuitry to no more than  $3V_F$ , where  $V_F$  is the diode's forward-voltage drop (about 0.7V at +25°C).

Figure 1. Input and Output Waveforms, Noninverting Input Varied

Figure 2. MAX961/MAX963 Timing Diagram

Figure 3. Input Stage Circuitry

For a large differential input voltage (exceeding  $3V_F$ ), this protection circuitry increases the input bias current at IN+ (source) and IN- (sink).

Input current =

$$\frac{(IN + - IN -) - 3V_F}{2 \times 200}$$

Input currents with large differential input voltages should not be confused with input bias currents (I<sub>B</sub>). As long as the differential input voltage is less than  $3V_F$ , this input current is less than  $2I_B$ .

The input circuitry allows the MAX961–MAX964/ MAX997/MAX999's input common-mode range to extend 100mV beyond both power-supply rails. The output remains in the correct logic state if one or both inputs are within the common-mode range. Taking either input outside the common-mode range causes the input to saturate and the propagation delay to increase.

M/IXI/M

Figure 4. Output Stage Circuitry

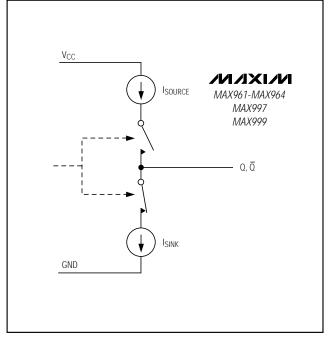

### **Output Stage Circuitry**

The MAX961–MAX964/MAX997/MAX999 contain a current-driven output stage, as shown in Figure 4. During an output transition, ISOURCE or ISINK is pushed or pulled to the output pin. The output source or sink current is high during the transition, creating a rapid slew rate. Once the output voltage reaches VOH or VOL, the source or sink current decreases to a small value, capable of maintaining the VOH or VOL in static condition. This decrease in current conserves power after an output transition has occurred.

One consequence of a current-driven output stage is a linear dependence between the slew rate and the load capacitance. A heavy capacitive load slows down the voltage output transition.

### Shutdown Mode

When SHDN is high, the MAX961/MAX963/MAX964/ MAX997 shut down. When shut down, the supply current drops to 270µA per comparator, and the outputs become high impedance. SHDN has a high input impedance. Connect SHDN to GND for normal operation. Exit shutdown with LE low; otherwise, the output is indeterminate.

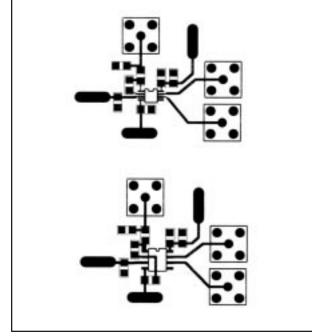

Figure 5. MAX961 PC Board Layout

### Applications Information

### **Circuit Layout and Bypassing**

The MAX961–MAX964/MAX997/MAX999's high bandwidth requires a high-speed layout. Follow these layout guidelines:

- 1) Use a printed circuit board with a good, unbroken, low-inductance ground plane.

- Place a decoupling capacitor (a 0.1µF ceramic surface-mount capacitor is a good choice) as close to V<sub>CC</sub> as possible.

- On the inputs and outputs, keep lead lengths short to avoid unwanted parasitic feedback around the comparators. Keep inputs away from outputs. Keep impedance between the inputs low.

- 4) Solder the device directly to the printed circuit board rather than using a socket.

- 5) Refer to Figure 5 for a recommended circuit layout.

- 6) For slow-moving input signals, take care to prevent parasitic feedback. A small capacitor (1000pF or less) placed between the inputs can help eliminate oscillations in the transition region. This capacitor causes negligible degradation to tpD when the source impedance is low.

###

TRANSISTOR COUNTS:

MAX961/MAX962: 286 MAX963/MAX964: 607 MAX997/MAX999: 142

M/IXI/M

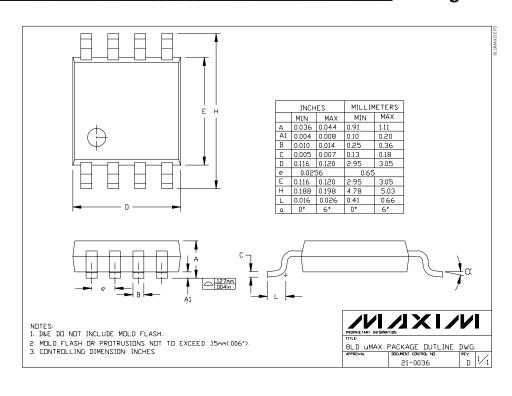

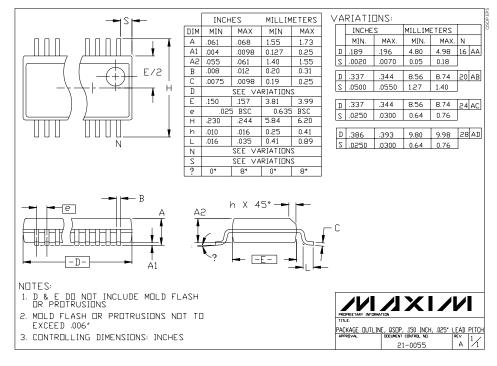

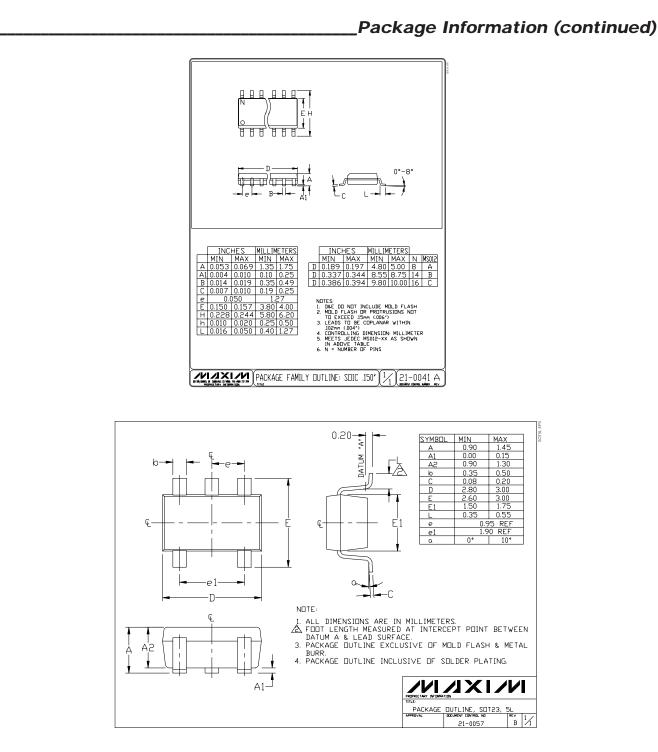

### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1998 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.