##

## 8 x 8 Video Crosspoint Switch

#### General Description

The MAX456 is the first monolithic CMOS 8 x 8 video crosspoint switch that significantly reduces component count, board space, and cost. The crosspoint switch contains a digitally controlled matrix of 64 T-switches that connect eight video input signals to any, or all, output channels. Each matrix output connects to eight internal, high-speed (250V/µs), unity-gain-stable buffers capable of driving 400 $\Omega$  and 20pF to ±1.3V. For applications requiring increased drive capability, the MAX456 outputs can be connected directly to two MAX470 quad, gain-of-two video buffers, which are capable of driving 75 $\Omega$  loads.

Three-state output capability and internal, programmable active loads make it feasible to parallel multiple MAX456s and form larger switch matrices.

In the 40-pin DIP package, crosstalk (70dB at 5MHz) is minimized, and board area and complexity are simplified by using a straight-through pinout. The analog inputs and outputs are on opposite sides, and each channel is separated by a power-supply line or quiet digital logic line.

### \_\_\_\_Applications

Video Test Equipment Video Security Systems Video Editing

#### Typical Application Circuit 8 INPUT CHANNELS MAXAM MAX470 75**Ω** WR I ATCH Ś 75**Ω** MAXIM 1 ΜΔΧΛ5Α OUTPUT SELECT A1 ۵0 8 X 8 T-SWITCH MATRIX INPUT SELECT D2 OR D1/SER OUT SERIAL D0/SER IN I/OMADO. MAX470

#### \_Features

- Routes Any Input Channel to Any Output Channel

- Switches Standard Video Signals

- Serial or Parallel Digital Interface

- Expandable for Larger Switch Matrices

- 80dB All-Channel Off Isolation at 5MHz

- ♦ 8 Internal Buffers with: 250V/µs Slew Rate, Three-State Output Capability, Power-Saving Disable Feature, 35MHz Bandwidth

#### \_Ordering Information

| PART      | TEMP. RANGE  | PIN-PACKAGE    |

|-----------|--------------|----------------|

| MAX456CPL | 0°C to +70°C | 40 Plastic DIP |

| MAX456CQH | 0°C to +70°C | 44 PLCC        |

| MAX456C/D | 0°C to +70°C | Dice*          |

Ordering Information continued on last page.

Dice are specified at  $T_A = +25 \,^{\circ}C$ , DC parameters only.

#### \_Pin Configurations

TOP VIEW D1/SER OUT 1 40 V+ DO/SER IN 2 39 OUTO A2 3 38 D2 **ΜΙΧΙΜ** A1 4 MAX456 37 OUT1 INO 5 36 D3 A0 6 35 OUT2 IN1 7 V-34 LOAD 8 33 OUT3 IN2 9 32 AGND DGND 10 31 OUT4 IN3 1 30 AGND DGND 12 29 OUT5 IN4 1 28 AGND EDGE/LEVEL 1 27 OUT6 IN5 1 V+ 26 V+ 1 25 OUT7 24 CE IN6 1 SER/PAR 18 23 CE IN7 10 22 LATCH WR V- 2 21 DIP PLCC on last page

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

# **MAX456**

#### ABSOLUTE MAXIMUM RATINGS

| Total Supply Voltage (V+ to V-)              |

|----------------------------------------------|

| Digital Input Voltage(V+ + 0.3V) to (V 0.3V) |

| Input Current, Power On or Off               |

| Digital Inputs±20mA                          |

| Analog Inputs±50mA                           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )  |

|--------------------------------------------------------|

| 40-Pin Plastic DIP (derate 11.3mW/°C above +70°C)889mW |

| 40-Pin CERDIP (derate 20.0mW/°C above +70°C)1600mW     |

| 44-Pin PLCC (derate 13.3mW/°C above +70°C)1066mW       |

| Operating Temperature Ranges:                          |

| MAX456C0°C to +70°C                                    |

| MAX456E40°C to +85°C                                   |

| Storage Temperature Range65°C to +160°C                |

| Lead Temperature (soldering, 10 sec)+300°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V+ = 5.0V, V- = -5.0V, -1.3V  $\leq$  V<sub>IN</sub>  $\leq$  +1.3V; LOAD = +5V; internal load resistors on; AGND = DGND = 0V; T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                        | CON                                                            | MIN                          | TYP  | MAX  | UNITS |       |  |

|----------------------------------|----------------------------------------------------------------|------------------------------|------|------|-------|-------|--|

| Input Voltage Range              |                                                                |                              | -1.3 |      | 1.3   | V     |  |

| Voltage Gain                     | Internal load resistors on, no                                 | $T_A = +25^{\circ}C$         | 0.99 | 1.0  | 1.01  | V/V   |  |

|                                  | external load,<br>V <sub>IN</sub> = 0V to 1V                   | $T_A = T_{MIN}$ to $T_{MAX}$ | 0.98 | 1.0  | 1.02  |       |  |

| Buffer Offset Voltage            | $T_A = +25^{\circ}C$                                           |                              |      |      | ±7    | mV    |  |

| Buller Oliset Voltage            | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MA</sub>           | Х                            |      |      | ±12   | IIIV  |  |

| Offset Voltage Drift             | $T_A = T_{MIN}$ to $T_{MA}$                                    | Х                            |      | 20   |       | µV/°C |  |

| Operating Supply Voltage         |                                                                |                              | ±4.5 |      | ±5.5  | V     |  |

| Supply Current, All Buffers On   | $T_A = +25^{\circ}C$                                           |                              |      | 39   | 45    | mA    |  |

| (No External Load)               | $T_A = T_{MIN}$ to $T_{MA}$                                    | X                            |      |      | 60    |       |  |

| Supply Current, All Buffers Off  | $T_A = +25^{\circ}C$                                           |                              |      | 1.5  | 3.0   | mA    |  |

| Supply Current, All Bullers On   | $T_A = T_{MIN}$ to $T_{MAX}$                                   |                              |      |      | 4     |       |  |

| Power-Supply Rejection Ratio     | ±4.5V to ±5.5V,                                                | DC measurement               | 50   | 64   |       | dB    |  |

| Analog Input Current             | $T_A = T_{MIN}$ to $T_{MA}$                                    | x                            |      | ±0.1 | ±10   | nA    |  |

| Output Leakage Current           | Internal load res<br>off, T <sub>A</sub> = T <sub>MIN</sub> to | istors off, all buffers      |      |      | ±100  | nA    |  |

| Internal Amplifier Load Resistor | $T_A = +25^{\circ}C$                                           |                              | 250  | 400  | 600   | Ω     |  |

| (LOAD Pin = 5V)                  | TA = TMIN to TMA                                               | Х                            | 200  |      | 765   | 52    |  |

| Buffer Output Voltage Swing      | Internal load resist                                           | tors on, no external load    | ±1.3 |      |       | V     |  |

| Digital Input Current            | $T_A = T_{MIN}$ to $T_{MA}$                                    | х                            |      |      | ±1    | μΑ    |  |

| Output Impedance at DC           |                                                                |                              |      | 10   |       | Ω     |  |

| Input Logic Low Threshold        |                                                                |                              |      |      | 0.8   | V     |  |

| Input Logic High Threshold       |                                                                |                              | 2.4  |      |       | V     |  |

| SER OUT Output Logic Low         | Serial mode,                                                   | $I_{OL} = 1.6 \text{mA}$     |      |      | 0.4   | V     |  |

| SER OUT Output Logic High        | SER/PAR = 5V                                                   | IOH = -0.4mA                 | 4    |      |       | v     |  |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{+} = 5.0V, V_{-} = -5.0V, -1.3V \le V_{IN} \le +1.3V, LOAD = +5V$ , internal load resistors on, AGND = DGND = 0V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                 | CONDITIONS                                                                    | MIN     | TYP | MAX               | UNITS |

|---------------------------|-------------------------------------------------------------------------------|---------|-----|-------------------|-------|

| DYNAMIC SPECIFICATIONS (N | lote 1)                                                                       |         |     |                   |       |

| Output-Buffer Slew Rate   | Internal load resistors on, 10pF load                                         | 250     |     | V/µs              |       |

| Single-Channel Crosstalk  | 5MHz, $V_{IN} = 2V_{P-P}$ (Note 2)                                            | 60      | 70  |                   | dB    |

| All-Channel Crosstalk     | 5MHz, VIN = 2VP-P (Notes 2, 3)                                                |         | 57  |                   | dB    |

| All-Channel Off Isolation | 5MHz, $V_{IN} = 2V_{P-P}$ (Note 2)                                            | 80      |     |                   | dB    |

| -3dB Bandwidth            | 10pF load, V <sub>IN</sub> = 2V <sub>P-P</sub> (Note 2)                       | 25 35   |     |                   | MHz   |

| Differential Phase Error  | (Note 4)                                                                      | 1.0     |     |                   | deg   |

| Differential Gain Error   | (Note 4)                                                                      | 0.5     |     |                   | %     |

| Input Noise               | DC to 40MHz                                                                   | 0.3 1.0 |     | mV <sub>RMS</sub> |       |

| Input Capacitance         | All buffer inputs grounded                                                    | 6       |     |                   | pF    |

| Buffer Input Capacitance  | Additional capacitance for each out-<br>put buffer connected to channel input | 2       |     | pF                |       |

| Output Capacitance        | Output buffer off                                                             | 7       |     |                   | pF    |

**MAX456**

#### SWITCHING CHARACTERISTICS (Note 1)

(Figure 4, V+ = 5.0V, V- = -5.0V, -1.3V  $\leq$  VIN  $\leq$  +1.3V, LOAD = +5V, internal load resistors on, AGND = DGND = 0V, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                      | SYMBOL          | CONDITIONS         | MIN | TYP | MAX | UNITS |  |

|--------------------------------|-----------------|--------------------|-----|-----|-----|-------|--|

| Chip-Enable to Write Setup     | tCE             |                    | 0   |     |     | ns    |  |

| Write Pulse Width High         | twn             |                    | 80  |     |     | ns    |  |

| Write Pulse Width Low          | t <sub>WL</sub> |                    | 80  |     |     | ns    |  |

| Data Satur                     | +               | Parallel mode      | 240 |     |     |       |  |

| Data Setup                     | t <sub>DS</sub> | 32-bit serial mode | 160 |     |     | ns    |  |

| Data Hold                      | tDH             |                    | 0   |     |     | ns    |  |

| Latch Pulse Width              | t∟              |                    | 80  |     |     | ns    |  |

| Latch Delay                    | tD              |                    | 80  |     |     | ns    |  |

| Switch Break-Before-Make Delay | ton - toff      |                    |     | 15  |     | ns    |  |

| LATCH Edge to Switch Off       | toff            | LATCH on           |     | 35  |     | ns    |  |

| LATCH Edge to Switch On        | ton             |                    |     | 50  |     | ns    |  |

Note 1: Guaranteed by design.

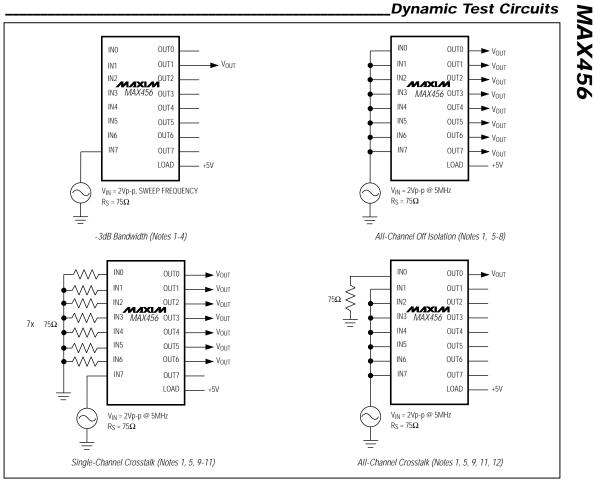

**Note 2:** See *Dynamic Test Circuits* on page 11. **Note 3:** 3dB typical crosstalk improvement when  $R_S = 0\Omega$ .

Note 4: Input lest signal: 3.58MHz sine wave of amplitude 40IRE superimposed on a linear ramp (0 to 100IRE). IRE is a unit of video-signal amplitude developed by the International Radio Engineers. 140IRE = 1.0V.

**MAX456**

| PIN                               |                                   |            |                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|-----------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP                               | PLCC                              | NAME       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                 |

| _                                 | 1, 12, 23, 34                     | N.C.       | No connect. Not internally connected.                                                                                                                                                                                                                                                                                                                                                    |

| 1                                 | 2                                 | D1/SER OUT | Parallel Data Bit D1 when SER/PAR = 0V. Serial Output for cascading multiple parts when SER/PAR = 5V.                                                                                                                                                                                                                                                                                    |

| 2                                 | 3                                 | D0/SER IN  | Parallel Data Bit D0 when SER/ $\overline{PAR}$ = 0V. A Serial Input when SER/ $\overline{PAR}$ = 5V.                                                                                                                                                                                                                                                                                    |

| 3, 4, 6                           | 4, 5, 7                           | A2, A1, A0 | Output Buffer Address Lines                                                                                                                                                                                                                                                                                                                                                              |

| 5, 7, 9, 11,<br>13, 15, 17, 19    | 6, 8, 10, 13,<br>15, 17, 19, 21   | INO-IN7    | Video Input Lines                                                                                                                                                                                                                                                                                                                                                                        |

| 8                                 | 9                                 | LOAD       | Asynchronous control line. When LOAD = 1, all the 400 $\Omega$ internal active loads are on. When LOAD = 0, external 400 $\Omega$ loads must be used. The buffers MUST have a resistive load to maintain stability.                                                                                                                                                                      |

| 10, 12                            | 11, 14                            | DGND       | Digital Ground Pins. Both DGND pins must have the same potential and be bypassed to AGND. DGND should be within $\pm 0.3V$ of AGND.                                                                                                                                                                                                                                                      |

| 14                                | 16                                | EDGE/LEVEL | When this control line is high, the 2nd-rank registers are loaded with the rising edge of the LATCH line. If this control line is low, the 2nd-rank registers are transparant when LATCH is low, passing data directly from the 1st-rank registers to the decoders.                                                                                                                      |

| 16, 26, 40                        | 18, 29, 44                        | V+         | All V+ pins must be tied to each other and bypassed to AGND separately (Figure 2).                                                                                                                                                                                                                                                                                                       |

| 18                                | 20                                | SER/PAR    | 5V = 32-Bit Serial, 0V = 7-Bit Parallel                                                                                                                                                                                                                                                                                                                                                  |

| 20, 34                            | 22, 38                            | V-         | Both V- pins must be tied to each other and bypassed to AGND separately (Figure 2).                                                                                                                                                                                                                                                                                                      |

| 21                                | 24                                | WR         | WRITE in the serial mode, shifts data in. In the parallel mode, WR loads data into the 1st-rank registers. Data is latched on the rising edge.                                                                                                                                                                                                                                           |

| 22                                | 25                                | LATCH      | If $EDGE/LEVEL = 5V$ , data is loaded from the 1st-rank registers to the 2nd-<br>rank registers on the rising edge of LATCH. If $EDGE/LEVEL = 0V$ , data is<br>loaded while LATCH = 0V. In addition, data is loaded during the execution<br>of parallel-mode functions 1011 through 1110, or if LATCH = 5V during the<br>execution of the parallel-mode "software-LATCH" command (1111). |

| 23                                | 26                                | CE         | $\overline{\text{Chip Enable}}$ . When $\overline{\text{CE}} = 0V$ and $\text{CE} = 5V$ , the WR line is enabled.                                                                                                                                                                                                                                                                        |

| 24                                | 27                                | CE         | Chip Enable. When $\overline{CE} = 0V$ and $CE = 5V$ , the WR line is enabled.                                                                                                                                                                                                                                                                                                           |

| 25, 27, 29, 31,<br>33, 35, 37, 39 | 28, 30, 32, 35,<br>37, 39, 41, 43 | OUT7-OUT0  | Output Buffers 7-0 (Note 1)                                                                                                                                                                                                                                                                                                                                                              |

| 28, 30, 32                        | 31, 33, 36                        | AGND       | Analog Ground must be at 0.0V since the gain resistors of the buffers are tied to these 3 pins.                                                                                                                                                                                                                                                                                          |

| 36                                | 40                                | D3         | Parallel Data Bit D3 when SER/ $\overrightarrow{PAR} = 0V$ . When D3 = 0V, D0-D2 specifies the input channel to be connected to buffer. When D3 = 5V, then D0-D2 specify control codes. D3 is not used when SER/ $\overrightarrow{PAR} = 5V$ .                                                                                                                                           |

| 38                                | 42                                | D2         | Parallel Data Bit D2 when SER/ $\overrightarrow{PAR}$ = 0V. Not used when SER/ $\overrightarrow{PAR}$ = 5V.                                                                                                                                                                                                                                                                              |

\_\_\_\_\_Pin Description

D2

D2

SER/ PAR = 5V.

Note 1: Buffer inputs are internally grounded with a 1000 or 1001 command from the D3-D0 lines. AGND must be at 0.0V since the gain setting resistors of the buffers are internally tied to AGND.

\_\_\_\_\_

M/IXI/M

#### \_Digital Interface

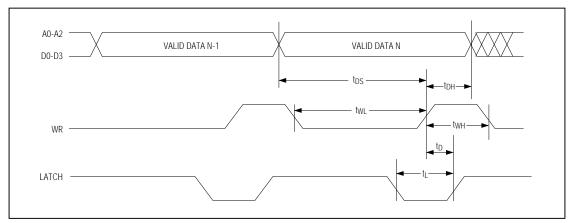

The desired switch state can be loaded in a 7-bit parallel-interface mode or 32-bit serial-interface mode (see Table 3 and Figures 4-6). All action associated with the WR line occurs on its rising edge. The same is true for the LATCH line if EDGE/LEVEL is high. Otherwise, the second-rank registers update while LATCH is low (when EDGE/LEVEL is low). WR is logically ANDed with CE and CE to allow active-high or active-low chip enable.

#### 7-Bit Parallel Mode

In the parallel-interface mode, the 7 data bits A2-A0 and D3-D0 specify an output channel (A2-A0) and the input channel to which it connects (D3-D0). The data is loaded on the rising edge of WR. The 8 input channels are selected by 0000 through 0111 (D3-D0). The remaining 8 codes (1000-1111) control other MAX456 functions, as listed in Table 1.

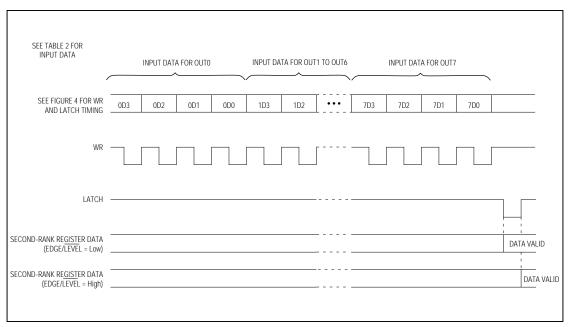

#### 32-Bit Serial-Interface Mode

In serial mode (SER/PAR = high), all first-rank registers are loaded with data, making it unnecessary to specify an output address (A2, A1, A0). The input data format is D3-D0, starting with OUT0 and ending with OUT7 for 32 total bits. Only codes 0000 through 1010 are valid. Code 1010 disables a buffer, while code 1001 enables it. After data is shifted into the 32-bit first-rank register, it is transferred to the second rank by the LATCH line (see Table 2).

#### Detailed Description

#### **Output Buffers**

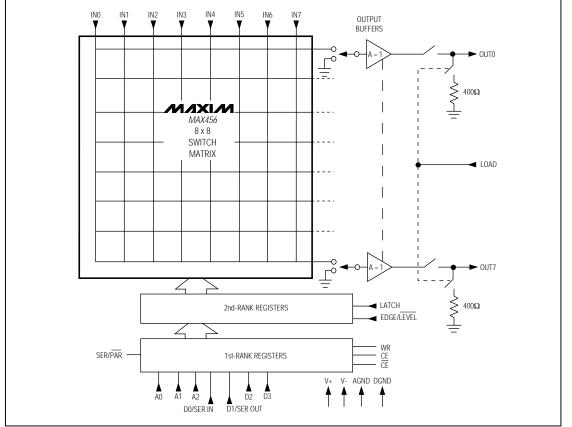

The MAX456 video crosspoint switch consists of 64 T-switches in an 8 x 8 grid (Figure 1). The 8 matrix outputs are followed by 8 wideband buffers optimized for driving 400 $\Omega$  and 20pF loads. Each buffer has an internal active load on the output that can be readily shut off via the LOAD input (off when LOAD = 0V). The shut-off is useful when two or more MAX456 circuits are connected in parallel to create more input channels. With more input channels, only one set of buffers can be active and only one set of loads can be driven. And, when active, the buffer must have either 1) an internal load, 2) the internal load of another buffer in another MAX456, or 3) an external load.

Each MAX456 output can be disabled under logic control. When a buffer is disabled, its output enters a highimpedance state. In multichip parallel applications, the disable function prevents inactive outputs from loading lines driven by other devices. Disabling the inactive buffers reduces power consumption.

The MAX456 outputs connect easily to MAX470 quad, gain-of-two buffers when  $75\Omega$  loads must be driven.

#### **Power-On RESET**

The MAX456 has an internal power-on reset (POR) circuit that remains low for 5µs when power is applied. POR also remains low if the total supply voltage is less than 4V. **The POR disables all buffer outputs at power-up**, but the switch matrix is not preset to any initial condition. The desired switch state should be programmed before the buffer outputs are enabled.

| 9 | Tabl |

|---|------|

| 5 |      |

| X |      |

| 4 |      |

| Ś |      |

|   |      |

#### Table 1. Parallel-Interface Mode Functions

| A2-A0                           | D3-D0         | FUNCTION                                                                                                                                                                                                 |

|---------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | 0000 to 0111  | Connect the buffer selected by A2-A0 to the input channel selected by D3-D0.                                                                                                                             |

|                                 | 1000          | Connect the buffer selected by A2-A0 to DGND. Note, if the buffer output is on, its output is its offset voltage.                                                                                        |

|                                 | 1011          | Shut off the buffer selected by A2-A0, and retain 2nd-rank contents.                                                                                                                                     |

| Selects<br>Output 1'<br>Buffer. | 1100          | Turn on the buffer selected by A2-A0, or restore the previously connected channel.                                                                                                                       |

| OUTO<br>to                      | 1101          | Turn off all buffers, or leave 2nd-rank registers unchanged.                                                                                                                                             |

| OUT7                            | 1110          | Turn on all buffers, or restore the previously connected channels.                                                                                                                                       |

|                                 | 1111          | Send a pulse to the 2nd-rank registers to load them with the contents of the 1st-rank registers. When latch is held high, this "software-LATCH" command performs the same function as pulsing LATCH low. |

|                                 | 1001 and 1010 | Do not use these codes in the parallel-interface mode. These codes are for the serial-<br>interface mode only.                                                                                           |

#### Table 2. Serial-Interface Mode Functions

| D3-D0        | FUNCTION                                                                                                                                                                        |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0000 to 0111 | Connect the selected buffer to the input channel selected by D3-D0.                                                                                                             |  |  |  |

| 1000         | Connect the input of the selected buffer to<br>GND. Note, if the buffer output remains<br>on, its input is its offset voltage.                                                  |  |  |  |

| 1001         | Turn on the selected buffer and connect<br>its input to GND. Use this code to turn on<br>buffers after power is applied. The default<br>power-up state is all buffers disabled. |  |  |  |

| 1010         | Shut off the selected buffer at the speci-<br>fied channel, and erase data stored in the<br>2nd rank of registers. The 2nd rank now<br>holds the command word 1010.             |  |  |  |

| 1011 to 1111 | Do not use these codes in the serial-inter-<br>face mode. They inhibit the latching of the<br>2nd-rank registers, which prevents proper<br>data loading.                        |  |  |  |

N/IXI/N

6 \_

Figure 1. MAX456 Functional Diagram

| Table 3. | Input/Out | put Line | Configurations |

|----------|-----------|----------|----------------|

|----------|-----------|----------|----------------|

| SERIAL/<br>PARALLEL | D3 | D2                | D1                | D0                | A2-A0                       | COMMENT                                 |

|---------------------|----|-------------------|-------------------|-------------------|-----------------------------|-----------------------------------------|

| Н                   | Х  | Х                 | Serial<br>Output  | Serial Input      | Х                           | 32-Bit Serial Mode                      |

| L                   | Н  | Parallel<br>Input | Parallel<br>Input | Parallel<br>Input | Output<br>Buffer<br>Address | Parallel Mode,<br>D0-D2 = Control Code  |

| L                   | L  | Parallel<br>Input | Parallel<br>Input | Parallel<br>Input | Output<br>Buffer<br>Address | Parallel Mode,<br>D0-D2 = Input Address |

Note : X = Don't Care, H = 5V, L = 0V

M/X/W

7

#### **Typical Application**

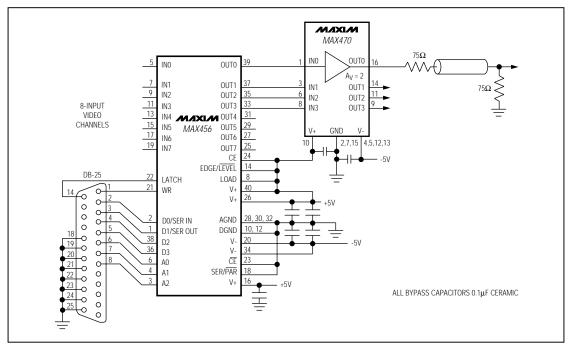

Figure 2 shows a typical application of the MAX456 with MAX470 quad, gain-of-two buffers at the outputs to drive 75 $\Omega$  loads. This application shows the MAX456 digital-switch control interface set up in the 7-bit parallel mode. The MAX456 uses 7 data lines and 2 control lines (WR and LATCH). Two additional lines may be needed to control CE and LOAD when using multiple MAX456s.

The input/output information is presented to the chip at A2-A0 and D3-D0 by a parallel printer port. The data is stored in the 1st-rank registers on the rising edge of WR. When the LATCH line goes high, the switch configuration is loaded into the 2nd-rank registers, and all 8 outputs enter the new configuration at the same time.

Each 7-bit word updates only one output buffer at a time. If several buffers are to be updated, the data is individually loaded into the 1st-rank registers. Then, a single LATCH pulse is used to reconfigure all channels simultaneously.

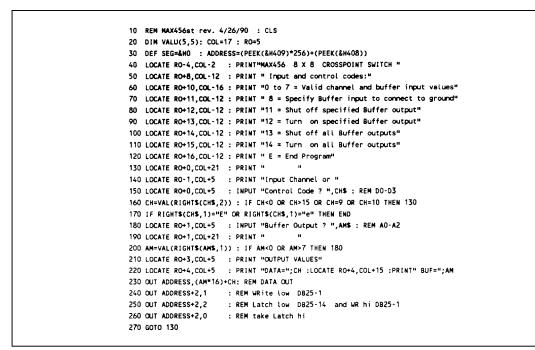

The short Basic program in Figure 3 loads programming data into the MAX456 from any IBM PC or compatible. It uses the computer's "LPT1" output to interface to the circuit, then automatically finds the address for LPT1 and displays a table of valid input values to be used. The program does not keep track of previous commands, but it does display the last data sent to LPT1, which is written and latched with each transmission.

Figure 2. Typical Application Circuit

M/X/W

8

Figure 3. BASIC Program for Loading Data into the MAX456 from a PC Using Figure 2's Circuit

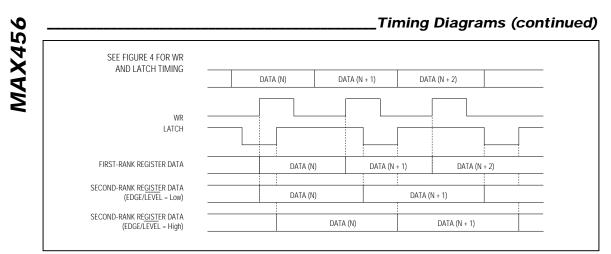

#### \_Timing Diagrams

Figure 4. Write Timing for Serial- and Parallel-Interface Modes

9

Figure 5. Parallel-Interface Mode Format (SER/ $\overline{PAR}$  = Low)

Figure 6. 32-Bit Serial-Mode Interface Format (SER/PAR = High)

M/IXI/M

10

**Note 1:** Connect LOAD (pin 8) to +5V (internal 400 $\Omega$  loads on at all outputs).

Note 2: Program any one input to connect to any one output (see Table 1 or 2 for programming codes).

Note 3: Turn on buffer at the selected output (see Table 1 or 2).

Note 4: Drive the selected input with V<sub>IN</sub>, and measure V<sub>OUT</sub> at the -3dB frequency at the selected output.

- Note 5: Program each numbered input to connect to the same numbered output (IN0 to OUT0, IN1 to OUT1, etc.). See Table 1 or 2 for programming codes.

- Note 6: Turn off all output buffers (see Table 1 or 2).

- Note 7: Drive all inputs with VIN and measure VOUT at any output.

- Note 8: Isolation (in dB) = 20log<sub>10</sub> (V<sub>OUT</sub>/V<sub>IN</sub>).

- Note 9: Turn on all output buffers (see Table 1 or 2).

- Note 10: Drive any one input with  $V_{IN}$  and measure  $V_{OUT}$  at any undriven output.

- **Note 11:** Crosstalk (in dB) = 20log<sub>10</sub> (V<sub>OUT</sub>/V<sub>IN</sub>).

- Note 12: Drive all but one input with VIN and measure VOUT at the undriven output.

M/IXI/N

#### Pin Configurations (continued) **MAX456** ] A1 ] A2 ] D0/SER IN ] D1/SER OUT TOP VIEW 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 I N 0 39 OUT2 A0 7 IN1 8 38 V-37 OUT3 LOAD 9 36 AGND IN2 10 ЛХІМ DGND 11 35 OUT4 MAX456 N.C. 12 34 N.C. 33 AGND IN3 13 DGND 14 32 OUT5 31 AGND IN4 15 EDGE/LEVEL 16 30 OUT6 IN5 17 29 V+ 18 19 20 21 22 23 24 25 26 27 28 IN6 SER/PAR LATCH [ CE [ CE [ 0UT7 \$ LN7 WR Ś N.C. PLCC

## 8 x 8 Video Crosspoint Switch

\_\_Ordering Information (continued)

| PART      | TEMP. RANGE    | PIN-PACKAGE    |

|-----------|----------------|----------------|

| MAX456EPL | -40°C to +85°C | 40 Plastic DIP |

| MAX456EQH | -40°C to +85°C | 44 PLCC        |

| MAX456EJL | -40°C to +85°C | 40 CERDIP      |

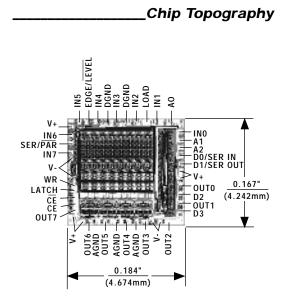

TRANSISTOR COUNT: 3820; SUBSTRATE CONNECTED TO V+.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1994 Maxim Integrated Products

12

Printed USA

is a registered trademark of Maxim Integrated Products.