19-1700; Rev 0; 4/00

## **General Description**

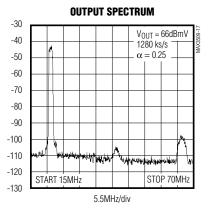

The MAX3509 is a programmable power amplifier for use in CATV upstream applications. The device outputs up to 66dBmV QPSK through a 1:1 transformer. It features variable gain controlled by a 3-wire digital serial bus. Gain control is available in 1dB steps. The device operates over a 5MHz to 65MHz frequency range.

The MAX3509 offers a transmit-disable mode, which places the device in a high-isolation state for use between bursts in TDMA systems. In this mode, all analog functions are shut down, minimizing output noise and power consumption. When entering and leaving transmit-disable mode, transients are kept to 25mV nominal at full gain. In addition, supply current is reduced to 7.8mA.

An additional power-down mode is available. Shutdown mode disables all circuitry and reduces current consumption to less than  $1\mu A$ .

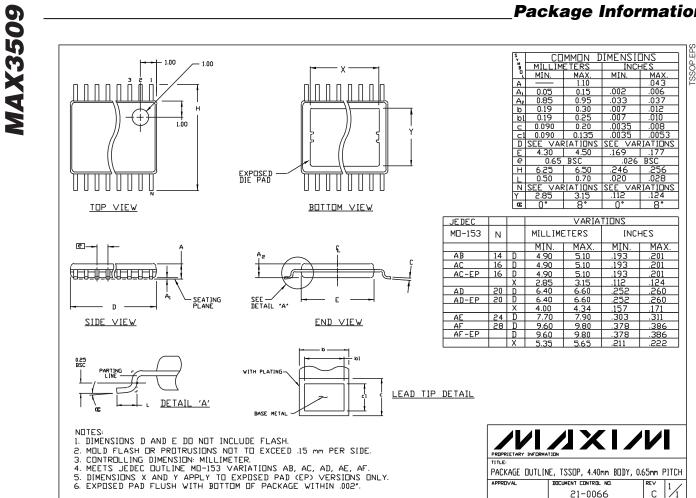

The MAX3509 is available in a 20-pin TSSOP-EP package for the extended-industrial temperature range (-40°C to +85°C).

## **Applications**

Telephony over Cable OPENCATV Set-Top Box Cable Modems

CATV Status Monitor CATV Infrastructure

## **\_Features**

- Ultra-Low Power-Up/Down Transients, 25mV (typ) at 66dBmV Output

- Single-Supply Operation

- Output Level Ranges from <12dBmV to 67dBmV (QPSK)

- Gain Programmable in 1dB Steps

- Low Transmit Output Noise Floor: -41dBmV (160kHz BW)

- Low Transmit-Disable Output Noise: -70dBmV

- Shutdown Mode

## **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE  |  |  |

|------------|----------------|--------------|--|--|

| MAX3509EUP | -40°C to +85°C | 20 TSSOP-EP* |  |  |

\*Exposed paddle

#### TOP VIFW TXEN 20 SCLK 19 SDA SHDN 2 V<sub>CC1</sub> 3 18 CS GND1 4 17 Vcc2 ΜΛΧΙΛ MAX3509 16 OUT+ IN+ 5 15 OUT-IN-6 14 V<sub>CC2</sub> GND1 13 GND V<sub>CC1</sub> 8 12 GND GND 9 GND 10 11 GND EXPOSED PADDLE TSSOP-EP

<sup>†</sup>Covered by U.S. Patent numbers 5,748,027 and 5,994,955.

Maxim Integrated Products 1

*For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.*

## Pin Configuration

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC1</sub> , V <sub>CC2</sub> to GND, GND1 | 0.3V to +10.0V |

|--------------------------------------------------|----------------|

| SCLK, SDA, CS, TXEN, SHDN to GND                 |                |

| and GND1                                         | 0.3V to +5.5V  |

| Continuous Input Voltage (IN+, IN-)              | 2Vp-p          |

| Continuous Current (OUT+, OUT-)                  | 80mA           |

| Continuous Power Dissipation ( $T_A = +70$ |               |

|--------------------------------------------|---------------|

| 20-Pin TSSOP-EP (derate at 27mW/°C         | Cabove        |

| +70°C)                                     | 2200mW        |

| Operating Temperature Range                | 40°C to +85°C |

| Junction Temperature                       | +150°C        |

| Storage Temperature Range                  |               |

| Lead Temperature (soldering, 10s)          | +300°C        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC ELECTRICAL CHARACTERISTICS**

(V<sub>CC1</sub> = V<sub>CC2</sub> = 8.5V to 9.5V, TXEN =  $\overline{SHDN}$  = high, D7 = 1, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. No input signal applied. Typical parameters are at T<sub>A</sub> = +25°C.)

| PARAMETER                            | SYMBOL | CONDITIONS                          | MIN  | ТҮР | MAX | UNITS |

|--------------------------------------|--------|-------------------------------------|------|-----|-----|-------|

| Supply Voltage                       | Vcc    |                                     | 8.5  |     | 9.5 | V     |

| Supply Current Transmit Mode         | Icc    |                                     |      | 84  | 115 | mA    |

| Supply Current Transmit-Disable Mode | ICC    | TXEN = low or D7 = 0                |      | 7.8 | 10  | mA    |

| Supply Current Shutdown Mode         | Icc    | $\overline{SHDN} = Iow, TXEN = Iow$ |      | 1   | 10  | μA    |

| Input High Voltage                   | Vinh   |                                     | 2.0  |     |     | V     |

| Input Low Voltage                    | VINL   |                                     |      |     | 0.8 | V     |

| Input High Current                   | IBIASH |                                     |      |     | 100 | μA    |

| Input Low Current                    | IBIASL |                                     | -100 |     |     | μA    |

## **AC ELECTRICAL CHARACTERISTICS**

(MAX3509 EV kit, V<sub>CC1</sub> = V<sub>CC2</sub> = 8.5V to 9.5V, TXEN =  $\overline{SHDN}$  = high, D7 = 1, V<sub>INPUT</sub> = 34dBmV differential, output impedance = 75 $\Omega$  through a 1:1 transformer, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical parameters are at T<sub>A</sub> = +25°C.)

| PARAMETER      | SYMBOL | CONDITIONS                                                          | MIN  | ΤΥΡ | МАХ  | UNITS |

|----------------|--------|---------------------------------------------------------------------|------|-----|------|-------|

| Voltage Gain   |        | $T_A = +25^{\circ}C$ , $f_{INPUT} = 42MHz$ , gain control word = 63 |      |     | 33   |       |

|                |        | $T_A = +25^{\circ}C$ , $f_{INPUT} = 42MHz$ , gain control word = 0  | -22  |     |      |       |

|                | Av     | $T_A = +25^{\circ}C$ , $f_{INPUT} = 42MHz$ , gain control word = 50 | 22   | 24  | 25.9 | dB    |

|                |        | $f_{INPUT} = 42MHz$ , gain control word = 63                        |      |     | 31   |       |

|                |        | $f_{INPUT} = 42MHz$ , gain control word = 0                         | -21  |     |      |       |

|                |        | $f_{INPUT} = 42MHz$ , gain control word = 50                        | 20.2 | 24  | 25.9 |       |

|                |        | VOUTPUT = 60dBmV, f <sub>INPUT</sub> = 5MHz to 42MHz<br>(Note 1)    |      | 0.1 | 0.4  | dB    |

| Gain Flatness  |        | VOUTPUT = 60dBmV, fINPUT = 5MHz to 65MHz<br>(Note 1)                |      | 0.3 | 0.9  | UD    |

| Gain Step Size |        | $f_{INPUT} = 5MHz$ to 65MHz, A <sub>V</sub> = -20dB to +33dB        | 0.7  | 1   | 1.3  | dB    |

## AC ELECTRICAL CHARACTERISTICS (continued)

(MAX3509 EV kit,  $V_{CC1} = V_{CC2} = 8.5V$  to 9.5V, TXEN =  $\overline{SHDN}$  = high, D7 = 1,  $V_{INPUT}$  = 34dBmV differential, output impedance = 75 $\Omega$  through a 1:1 transformer, TA = -40°C to +85°C, unless otherwise noted. Typical parameters are at TA = +25°C.)

| PARAMETER                                    | SYMBOL  | CON                                                                  | DITIONS                             | MIN | TYP | MAX     | UNITS   |

|----------------------------------------------|---------|----------------------------------------------------------------------|-------------------------------------|-----|-----|---------|---------|

|                                              |         | BW = 160kHz, A <sub>V</sub> = 32                                     |                                     |     | -85 | dBc     |         |

| Transmit Mode Noise                          |         | BW = 160kHz, A <sub>V</sub> = -20dB, T <sub>A</sub> = +25°C (Note 1) |                                     |     | -41 | -39.5   |         |

|                                              |         | BW = 160kHz, A <sub>V</sub> = -20                                    | dB, T <sub>A</sub> = +85°C (Note 1) |     |     | -38.5   | dBmV    |

| Transmit-Disable Mode Noise<br>Floor         |         | TXEN = low, BW = $160$<br>f <sub>INPUT</sub> = 5MHz to 65M           |                                     |     |     | -70     | dBmV    |

| TXEN Enable Transient Duration               |         | TXEN rise time <0.1µs,                                               | T <sub>A</sub> = +25°C (Note 1)     |     | 1.4 | 2       | μs      |

| TXEN Disable Transient Duration              |         | TXEN fall time <0.1µs,                                               | T <sub>A</sub> = +25°C (Note 1)     |     | 1   | 1.5     | μs      |

| TXEN Transient Step Size                     |         | A <sub>V</sub> = 32dB, T <sub>A</sub> = +25°                         | C (Note 1)                          |     | 25  | 100     | mVp-p   |

| TXEN Transient Step Size                     |         | A <sub>V</sub> = 2dB or lower, T <sub>A</sub>                        | = +25°C (Note 1)                    |     | 1.5 | 9       | l mvb-b |

| Input Impedance                              | Zinput  | $f_{INPUT} = 5MHz$ to 65M<br>T <sub>A</sub> = +25°C (Note 1)         | IHz, single ended,                  |     | 1.2 |         | kΩ      |

| Output Impedance in Transmit<br>Mode         | ZOUTPUT | $f_{INPUT} = 5MHz$ to $65N$                                          |                                     | 1.2 |     | Ω       |         |

| Output Impedance in<br>Transmit-Disable Mode | Zoutput | TXEN = low, fINPUT =<br>$T_A = +25^{\circ}C$ (Note 1)                |                                     | 170 |     | Ω       |         |

| Two-Tone Third-Order Distortion              | IM3     | Input tones at 65MHz<br>VINPUT = 31dBmV/ton                          |                                     |     | -53 |         | dBc     |

|                                              |         | f <sub>INPUT</sub> = 33MHz                                           | Voutput = +60dBmV                   |     | -56 | -53     |         |

| 2nd Harmonic Distortion                      | HD2     | NPU   = 33  N  2                                                     | VOUTPUT = +66dBmV                   |     | -56 | -50     | dBc     |

|                                              | TIDZ    | f <sub>INPUT</sub> = 65MHz<br>(Note 1)                               | Voutput = 66dBmV                    |     | -56 | -50     | ubc     |

|                                              |         | (                                                                    | Voutput = +60dBmV                   |     | -56 | -53     |         |

| 3rd Harmonic Distortion                      | HD3     | $f_{INPUT} = 22MHz$                                                  | VOUTPUT = +66dBmV                   |     | -53 | -48.5   | dBc     |

|                                              | 1120    | f <sub>INPUT</sub> = 65MHz<br>(Note 1)                               | V <sub>OUTPUT</sub> = 66dBmV        |     | -43 | -40     |         |

| Output 1dB Compression Point                 | P1dB    | A <sub>V</sub> = 32dB, 65MHz (N                                      |                                     | 26  |     | dBm     |         |

| AM to AM                                     | AM/AM   | A <sub>V</sub> = 32dB, V <sub>INPUT</sub> sw<br>38dBmV (Note 1)      |                                     | 0.1 |     | dB      |         |

| AM to PM                                     | AM/PM   | A <sub>V</sub> = 32dB, V <sub>INPUT</sub> sw<br>38dBmV (Note 1)      |                                     | 1.7 |     | degrees |         |

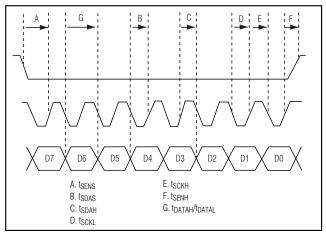

## TIMING CHARACTERISTICS

$(V_{CC1} = V_{CC2} = 8.5V \text{ to } 9.5V, TXEN = \overline{SHDN} = \text{high}, D7 = 1, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                 | SYMBOL         | COMMENT | MIN | TYP | MAX | UNITS |

|---------------------------|----------------|---------|-----|-----|-----|-------|

| CS to SCK Rise Setup Time | <b>t</b> SENS  |         | 10  |     |     | ns    |

| CS to SCK Rise Hold Time  | <b>t</b> SENH  |         | 20  |     |     | ns    |

| SDA to SCK Setup Time     | tsdas          |         | 10  |     |     | ns    |

| SDA to SCK Hold Time      | <b>t</b> SDAH  |         | 20  |     |     | ns    |

| SDA Pulse Width High      | <b>t</b> DATAH |         | 50  |     |     | ns    |

| SDA Pulse Width Low       | <b>t</b> DATAL |         | 50  |     |     | ns    |

| SCK Pulse Width High      | tscкн          |         | 50  |     |     | ns    |

| SCK Pulse Width Low       | <b>t</b> SCKL  |         | 50  |     |     | ns    |

Note 1: Guaranteed by design and characterization.

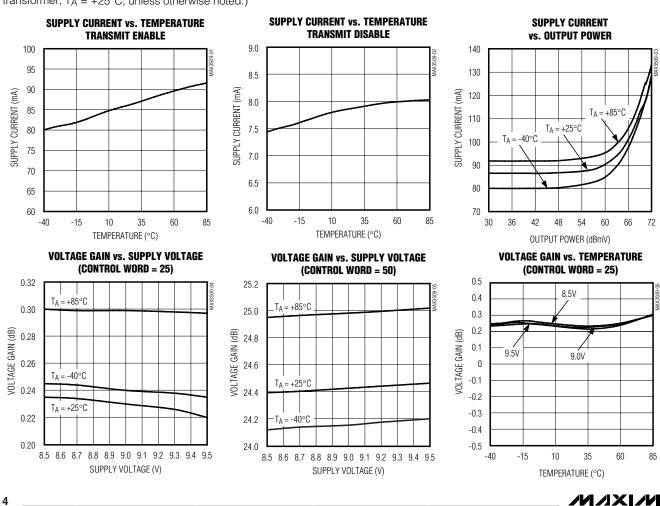

## **Typical Operating Characteristics**

(MAX3509 EV kit, V<sub>CC1</sub> = V<sub>CC2</sub> = +9V, V<sub>IN</sub> = +34dBmV, TXEN =  $\overline{SHDN}$  = high, D7 = 1, f<sub>INPUT</sub> = 10MHz, Z<sub>LOAD</sub> = 75 $\Omega$  through a 1:1 transformer, T<sub>A</sub> = +25°C, unless otherwise noted.)

**MAX3509**

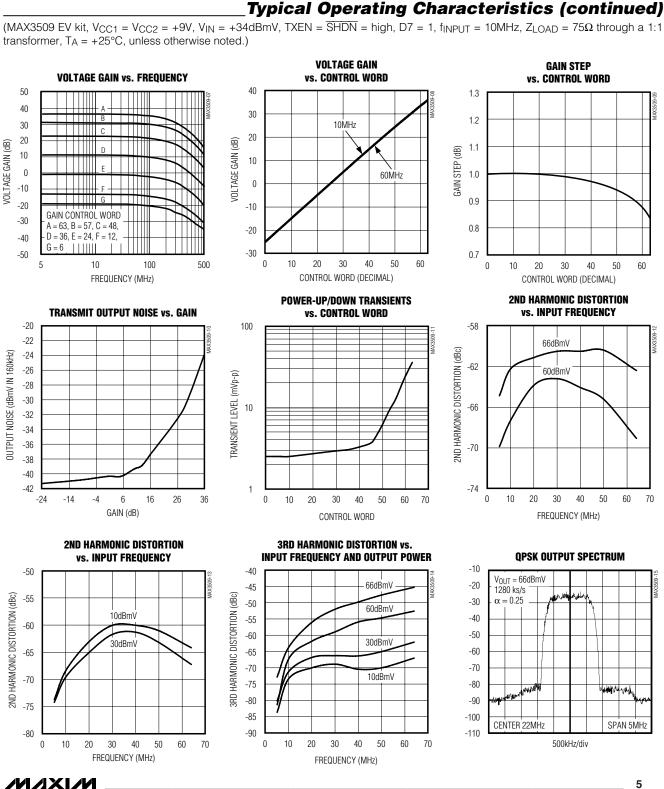

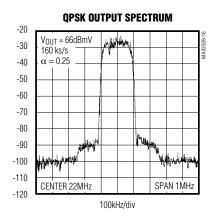

## **Typical Operating Characteristics (continued)**

(MAX3509 EV kit,  $V_{CC1} = V_{CC2} = +9V$ ,  $V_{IN} = +34dBmV$ , TXEN =  $\overline{SHDN}$  = high, D7 = 1,  $f_{INPUT} = 10MHz$ ,  $Z_{LOAD} = 75\Omega$  through a 1:1 transformer,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

## **Pin Description**

| PIN               | NAME             | FUNCTION                                                                                                                                                                                                          |  |  |  |  |  |  |

|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1                 | TXEN             | Transmit Enable. To disable the MAX3509 and provide high input/output isolation, drive TXEN low. Drive TXEN high for normal operation.                                                                            |  |  |  |  |  |  |

| 2                 | SHDN             | Shutdown. To enable low-power shutdown, drive SHDN low. Drive SHDN high for normal operation.                                                                                                                     |  |  |  |  |  |  |

| 3, 8              | V <sub>CC1</sub> | Programmable-Gain Amplifier (PGA) +9V Supply. Bypass to GND1 with a 0.1µF decoupling capacitor as close to the part as possible.                                                                                  |  |  |  |  |  |  |

| 4, 7              | GND1             | PGA Ground. Connect to ground with a low inductance path.                                                                                                                                                         |  |  |  |  |  |  |

| 5                 | IN+              | Noninverting PGA Input. Along with IN-, this port forms a high-impedance differential input to the PGA. Driving this port differentially increases the rejection of second-order distortion at low output levels. |  |  |  |  |  |  |

| 6                 | IN-              | Inverted PGA Input. When not used, AC-coupled to ground. See IN+.                                                                                                                                                 |  |  |  |  |  |  |

| 9–13              | GND              | Ground                                                                                                                                                                                                            |  |  |  |  |  |  |

| 14,17             | V <sub>CC2</sub> | Power Amplifier Bias +9V Supply. Bypass to GND2 (exposed paddle) with a 0.1µF decoupling capacitor as close to the part as possible.                                                                              |  |  |  |  |  |  |

| 15                | OUT-             | Inverted Output. AC-couple to output transformer. Used in conjunction with OUT+.                                                                                                                                  |  |  |  |  |  |  |

| 16                | OUT+             | Noninverted Output. See OUT                                                                                                                                                                                       |  |  |  |  |  |  |

| 18                | CS               | Serial-Interface Enable. TTL-compatible input. See Serial Interface.                                                                                                                                              |  |  |  |  |  |  |

| 19                | SDA              | Serial-Interface Data. TTL-compatible input. See Serial Interface.                                                                                                                                                |  |  |  |  |  |  |

| 20                | SCLK             | Serial-Interface Clock. TTL-compatible input. See Serial Interface.                                                                                                                                               |  |  |  |  |  |  |

| Exposed<br>Paddle | GND2             | Power Amplifier Bias Ground. Connect to ground with a low inductance path. Ensure a low thermal resistive path to PC board. See <i>Layout Issues</i> .                                                            |  |  |  |  |  |  |

M/XI/M

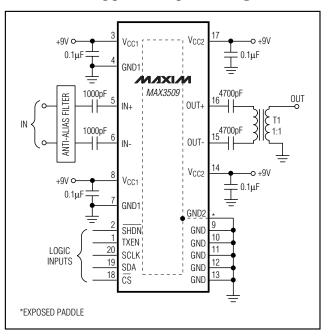

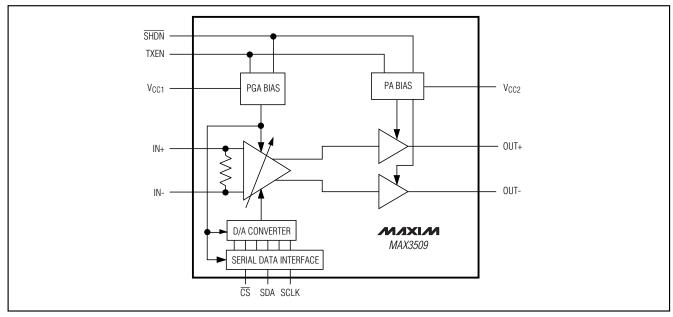

Figure 1. MAX3509 Functional Diagram

### **Detailed Description**

The following sections describe the blocks shown in the functional diagram (Figure 1).

### **Programmable-Gain Amplifier**

The PGA consists of the variable-gain amplifier (VGA) and the digital-to-analog converter (DAC), which provide better than 55dB of output level control in 1dB steps.

The PGA is implemented as a programmable Gilbertcell attenuator. It uses a differential architecture to achieve maximum linearity. The gain of the PGA is determined by a 6-bit word (D5–D0) programmed through the serial data interface (Tables 1 and 2).

Specified performance is achieved when the input is driven differentially. The device may be driven single ended; however, a slight increase in even-order distortion may result at low output levels. To drive the device in this manner, one of the input pins must be capacitively coupled to ground. Use a capacitor value large enough to allow for a low-impedance path to ground at the lowest frequency of operation.

#### **Power Amplifier**

The power amplifier has two current-feedback amplifiers in an instrumentation amplifier configuration. This architecture provides superior even-order distortion performance but requires an external transformer to convert to a single-ended output. In transmit-disable mode, bias to the power amplifier is reduced to a minimal level, which provides high input to output isolation and low output noise.

### **Serial Interface**

The serial interface has an active-low enable  $(\overline{CS})$  to bracket the data, with data clocked in MSB first on the rising edge of SCLK. Data is stored in the storage latch on the rising edge of  $\overline{CS}$ . The serial interface controls the state of the PGA. Tables 1 and 2 show the register format. Serial-interface timing is shown in Figure 2.

### **PGA Bias Cell**

The bias cell in the MAX3509 is controlled by the logic levels present at TXEN and SHDN, as well as the program state of D7, the MSB of the 8-bit program word. Transmit-disable mode is actuated when the TXEN pin is driven to a logic low or when D7 = 0. In this mode, current to the PGA and power amps is reduced significantly while maintaining normal current flow to the serial data interface and DAC. This preserves the program stored in the serial data interface.

A logic low at the SHDN pin overrides the state of the TXEN pin or D7. In shutdown mode, the current to the PGA, power amp, serial data interface, and DAC is cut off, allowing only leakage currents to flow. The stored gain control program is lost in this mode.

### **Power Amp Bias Cell**

The power amp bias cell is used to enable and disable bias to the <u>output</u> power amplifier. This is controlled by TXEN and SHDN.

### **Functional Modes**

The MAX3509 has three functional modes controlled through the serial interface or external pins (Table 2): transmit mode, transmit-disable mode, and shutdown.

#### Transmit Mode

Transmit mode is the normal active mode of the MAX3509. Drive TXEN and  $\overline{SHDN}$  high, and set D7 = 1 to activate transmit mode.

### Transmit-Disable Mode

When in transmit-disable mode, all analog circuitry is shut down. This mode is activated by driving TXEN low or setting D7 = 1 while keeping SHDN high. This mode is typically used between bursts in TDMA systems. Transients are controlled by the transformer balance.

### Shutdown Mode

In normal operation, the shutdown pin  $\overline{(SHDN)}$  is held high. When SHDN is driven low, all circuits within the IC are disabled. Only leakage currents flow in this mode. Data stored within the serial-data interface latches will be lost upon entering this mode. Current draw is reduced to 1µA (typ) in shutdown mode.

Figure 2. Serial-Interface Timing Diagram

### Table 1. Serial-Interface Control Word

| BIT   | MNEMONIC      | DESCRIPTION         |  |  |  |

|-------|---------------|---------------------|--|--|--|

| MSB 7 | D7            | Transmit Disable    |  |  |  |

| 6     | 6 D6 Not used |                     |  |  |  |

| 5     | D5            | Gain Control, Bit 5 |  |  |  |

| 4     | D4            | Gain Control, Bit 4 |  |  |  |

| 3     | D3            | Gain Control, Bit 3 |  |  |  |

| 2     | D2            | Gain Control, Bit 2 |  |  |  |

| 1     | D1            | Gain Control, Bit 1 |  |  |  |

| LSB 0 | D0            | Gain Control, Bit 0 |  |  |  |

| SHDN | TXEN | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | GAIN CONTROL<br>WORD | STATE                 |

|------|------|----|----|----|----|----|----|----|----|----------------------|-----------------------|

| 0    | Х    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х                    | Shutdown Mode         |

| 1    | 0    | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х                    | Transmit-Disable Mode |

| 1    | Х    | 0  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х                    | Transmit-Disable Mode |

| 1    | 1    | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х                    | Transmit Mode         |

| 1    | 1    | 1  | Х  | 0  | 0  | 0  | 0  | 0  | 0  | 0                    | $Gain = -25dB^*$      |

| 1    | 1    | 1  | Х  | 0  | 0  | 0  | 0  | 0  | 1  | 1                    | Gain = -24dB*         |

| 1    | 1    | 1  | Х  | —  | _  | _  | _  | _  |    | _                    | _                     |

| 1    | 1    | 1  | Х  | 0  | 1  | 1  | 0  | 0  | 1  | 25                   | Gain = 0dB*           |

| 1    | 1    | 1  | Х  | _  | _  | _  | _  | _  |    | _                    |                       |

| 1    | 1    | 1  | Х  | 1  | 1  | 1  | 1  | 1  | 0  | 62                   | Gain = 35dB*          |

| 1    | 1    | 1  | Х  | 1  | 1  | 1  | 1  | 1  | 1  | 63                   | Gain = 36dB*          |

\*Typical gain at +25°C and  $V_{CC} = +9V$ .

### **Applications Information**

### **Transformer**

To maintain rated performance into a 75 $\Omega$  load, a 1:1 impedance ratio output transformer with adequate bandwidth is required. A step-up transformer with a 1:1.5 impedance ratio will increase gain and output voltage swing nominally by 1.7dB, but output noise performance will increase by the same amount.

#### **Input Circuit**

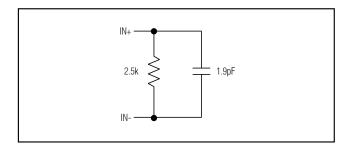

To achieve rated performance, the input of the MAX3509 must be driven differentially with 34dBmV or lower input level. The MAX3509 can be driven from a single-ended source. A slight degradation in evenorder distortion at a 10W output level will result. The differential input impedance is approximately  $1.2k\Omega$ .

Most applications require a differential lowpass filter preceding the MAX3509. The filter design dictates a terminating resistance of a specified value. Place this resistance across the AC-coupled inputs (see *Typical Operating Circuit*).

The MAX3509 has sufficient gain to produce an output level of 66dBmV when driven with a 34dBmV input signal. Rated performance is achieved with this input level. When a lower input level is present, the maximum output level will be reduced proportionally and output linearity will improve. If an input level greater than 34dBmV is used, distortion performance degrades.

If a single-ended source drives the MAX3509, one of the input terminals must be capacitively coupled to ground (IN+ or IN-). The value of this capacitor must be large enough to look like a short circuit at the lowest frequency of interest. For operation at 5MHz with a 50 $\Omega$  source impedance, a value of 0.1µF will suffice.

A typical model for the MAX3509 input impedance is shown in Figure 3.

#### Layout Issues

A well-designed PC board is an essential part of an RF circuit. For best performance, pay attention to powersupply layout issues, as well as the output circuit layout.

**Exposed Paddle Thermal Considerations** The exposed paddle (EP) of the MAX3509's 20-pin TSSOP-EP package provides a low thermal resistance path to the die. It is important that the PC board on which the MAX3509 is mounted be designed to conduct heat from this contact. In addition, the EP should be provided with a low inductance path to electrical ground. It is recommended that the EP be soldered to a ground plane on the PC board, either directly or through an array of plated via holes.

### Output Circuit Layout

The differential implementation of the MAX3509's output has the benefit of reducing even-order distortion, the most significant of which is second-harmonic distortion. The degree of distortion cancellation depends on the amplitude and phase balance of the overall circuit. It is important that the traces that lead from the output pins be the same length.

### Power-Supply Layout

To achieve minimal coupling between different sections of the IC, the ideal power-supply layout is a star configuration. This configuration has a large-value decoupling capacitor at the central power-supply node. The powersupply traces branch out from this node, each going to a separate power-supply node in the MAX3509 circuit. At the end of each of these traces is a decoupling capacitor that provides a very low impedance at the frequency of interest. This arrangement provides local power-supply decoupling at each power-supply pin.

The power-supply traces must be made as thick as practical to keep resistance well below 1  $\!\Omega\!.$

Ground inductance degrades distortion performance. Therefore, ground plane connections to GND, GND1, and GND2 should be made with multiple vias if possible.

Figure 3. Typical Equivalent Input Circuit

Chip Information

TRANSISTOR COUNT: 1085

M/X/M

## **Package Information**

NOTES

NOTES