#

### **MAX1780 Advanced Smart Battery Pack Controller**

## **General Description**

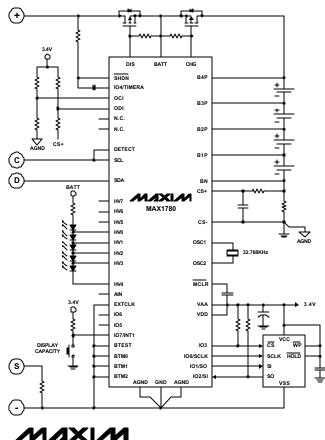

The MAX1780 Advanced Battery Pack Controller is a smart battery pack supervisor that integrates a User programmable Microcontroller Core, Coulomb-Counter-based Fuel Gauge, a multi-channel Data Acquisition Unit, a high-speed SPI Interface, and a Master/Slave SMBus Interface. The 8-bit, RISC, Microcontroller core is user programmable, and provides battery pack designers with complete flexibility in developing fuel gauging and control algorithms. The Data Acquisition Unit can measure individual cell voltages to within 50mV, total battery stack voltage (up to 20.48V), and chip internal/external temperature.

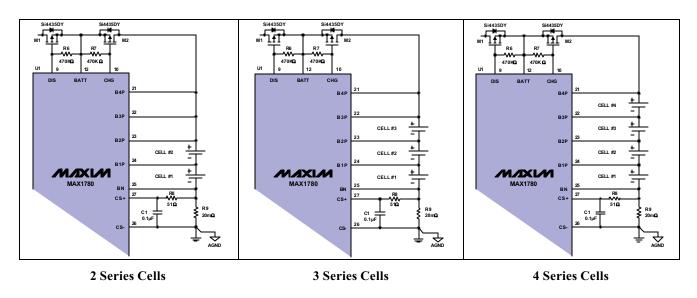

The user adjustable overcurrent comparators, along with individual cell voltage measurements, allow the MAX1780 to eliminate a separate primary pack protection IC. The MAX1780 can be directly connected to 2 to 4 series Lithium Ion cells, and supplies itself through a fully integrated 3.4V low drop out linear regulator.

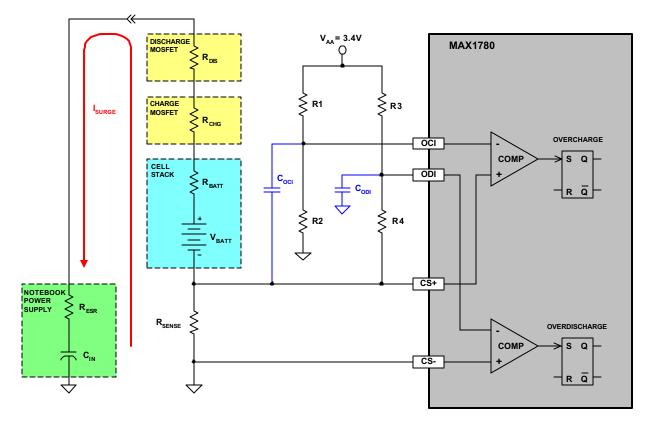

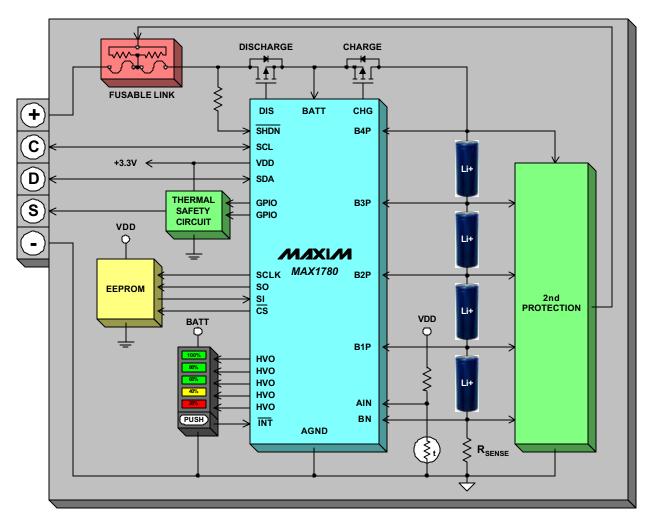

## **Typical Operating Circuit**

### Features

- User Programmable Using an External EEPROM

- Accurate Fuel Gauge Uses V-to-F Method

- $\circ$  < 1µV Input Offset Voltage

- o No External Calibration Required

- Eliminates Separate Primary Protection IC

- 50mV Accurate Individual Cell Voltage Measurements

- o Built in Protection MOSFET Gate Drivers

- Over Charge & Discharge Current Protection

- Fully Integrated LDO ( $V_{IN} = 4V$  to 28V)

- 8-bit RISC Microcontroller Core

- On-board 1.5K ROM & 0.5K Program RAM

- o 144 Bytes Data Memory

- Fast Start-up 3.5MHz Instruction Oscillator

- Watch Dog Timer

- Hardware SMBus with Master Capability

- GPIO Port and High Voltage LED Drivers

- Typical Operating Currents < 200µA Achievable

- Typical Shutdown Current of 1nA

## Applications

SMBus Battery Packs

**Proprietary Battery Packs**

Data Acquisition Systems

Remote Data Logging

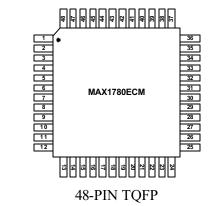

## **Pin Configuration**

### **Ordering Information**

| PART       | TEMP RANGE       | PIN/ PACKAGE |  |  |

|------------|------------------|--------------|--|--|

| MAX1780ECM | -40 °C to +85 °C | 48 TQFP      |  |  |

## **Table Of Contents**

| General Description                                                          |    |

|------------------------------------------------------------------------------|----|

| Typical Operating Circuit                                                    |    |

| Features                                                                     |    |

| Applications                                                                 |    |

| Pin Configuration                                                            |    |

| Ordering Information                                                         |    |

| Table Of Contents                                                            |    |

| Table Of Figures                                                             |    |

| Table Of Tables                                                              |    |

| List Of Applicable Documents                                                 |    |

| Architectural Overview                                                       |    |

| Introduction                                                                 |    |

| Harvard Architecture                                                         |    |

| Detailed Description Of MAX1780                                              |    |

| Instruction Execution                                                        |    |

| Phase Clocks                                                                 |    |

| CPU Architecture                                                             |    |

| Program Counter (PC)                                                         |    |

| Program Stack                                                                |    |

| Arithmetic Logic Unit (ALU)                                                  |    |

| Working Register ("W")                                                       |    |

| Option Register (Write Only, via the "W" Register and OPTION Instruction)    |    |

| Setupint Register (Write Only, via the "W" Register and Of FION Instruction) |    |

| Memory Organization:                                                         |    |

| Page Boundaries                                                              |    |

| Indirect Data Addressing; INDF and FSR Registers                             |    |

| Register File Organization                                                   |    |

| Data RAM                                                                     |    |

| File Select Register (FSR) Read/Write                                        |    |

|                                                                              |    |

| Status Register (Read/Write)<br>Modes Of Operation                           |    |

| Shutdown                                                                     |    |

| Entering Shutdown                                                            |    |

|                                                                              |    |

| Recovering From Shutdown                                                     |    |

| Sleep                                                                        |    |

| Entering Sleep Mode                                                          |    |

| Wake-Up From Sleep Mode                                                      |    |

| Master Clear                                                                 |    |

| Operate (Program Execution)                                                  |    |

| Analog And Mixed Signal Peripheral Interface.                                |    |

| MAX1780 Power Supply Sequencing                                              |    |

| MAX1780 Special Purpose Port Registers.                                      |    |

| PORTA                                                                        |    |

| PORTA Data Latch (Read/Write).                                               |    |

| PORTA TRIS Latch (Write Only)                                                |    |

| PORTB                                                                        |    |

| PORTB Data Latch (Read/Write)                                                |    |

| PORTB TRIS Latch (Write Only)                                                |    |

| Accessing The On-board Peripherals                                           | 27 |

| PORTC (IO0 – IO7)                              | 20 |

|------------------------------------------------|----|

| PORTC (100 – 107)<br>PORTC GPIO Operation      |    |

| I/O Programming Considerations                 |    |

| PORTC Data Latch                               |    |

| PORTC TRIS Latch                               |    |

| Timers And Watchdog                            |    |

| Timer A (TMRA).                                |    |

| Timer B (TMRA)                                 |    |

| Watchdog Timer (WDT)                           |    |

| Interrupts                                     |    |

| Description                                    |    |

| Peripheral Interrupt Control Registers         |    |

| Interrupt Status Register (INTSTAT) Operation  |    |

| Interrupt Enable Register (INTREN) Operation   |    |

| Interrupt Control Register Descriptions        |    |

| Analog Peripherals                             |    |

| 3.5MHz Instruction Oscillator                  |    |

| 32KHz Oscillator                               |    |

| Low Drop Out Linear Regulator                  |    |

| Precision Bandgap Reference.                   |    |

| Mixed Signal Peripherals                       |    |

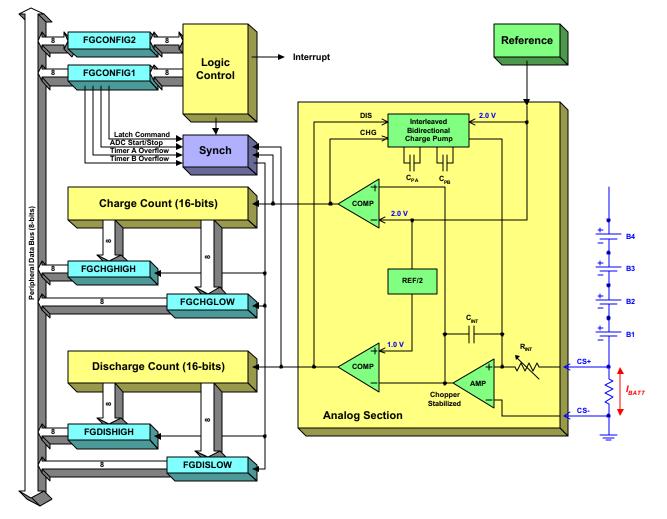

| Fuel Gauge Unit                                |    |

| General Description                            |    |

| Features                                       |    |

| Automatic Cancellation Of Input Offset Voltage |    |

| Coulomb Counting                               |    |

| Charge And Discharge Counters                  |    |

| Current Direction Change Detection Function    |    |

| Counter Latching Source And Arbiter.           |    |

| Direct CPU Control                             |    |

| ADC Conversion Start and Stop                  |    |

| TIMERA Overflow                                |    |

| TIMERB Overflow                                |    |

| Arbitration Logic                              |    |

| Fuel Gauge Register Descriptions               |    |

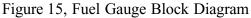

| Data Acquisition Unit                          |    |

| General Description                            |    |

| Features                                       |    |

| Analog Front End/Multiplexer (AFE)             |    |

| Input Bias Cancellation                        |    |

| AFE Register Descriptions                      |    |

| Analog-To-Digital Converter (ADC)              |    |

| Operation                                      |    |

| Dual Voltage-To-Frequency Converter            |    |

| Digital Counter/Adder                          |    |

| Control Logic And Resolution Counter Block     |    |

| Over-Range Status And Limit Bits               |    |

| The OVERFLOW Bit                               |    |

| The SIGN Bit                                   |    |

| The LIMIT Bit                                  |    |

| Understanding ADC Error Sources                |    |

|                                                |    |

| Effective ADC Resolution                                                         |    |

|----------------------------------------------------------------------------------|----|

| ADC Register Descriptions                                                        |    |

| Temperature Sensor                                                               | 51 |

| Description                                                                      | 51 |

| Operation                                                                        | 51 |

| Overcurrent Protection Block                                                     |    |

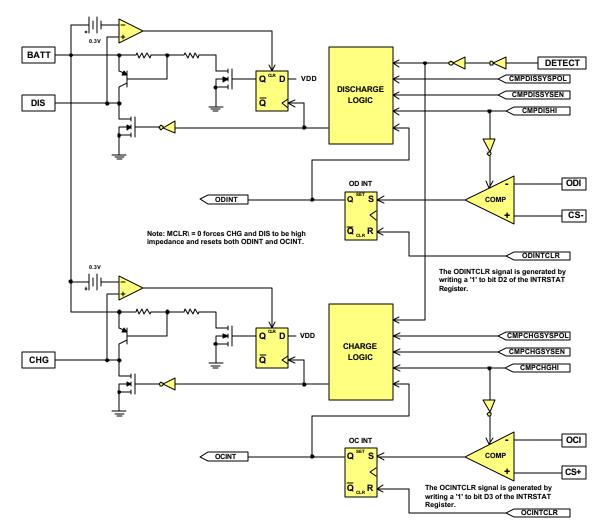

| Description                                                                      |    |

| DISCHARGE LOGIC                                                                  |    |

| CHARGE LOGIC                                                                     |    |

| Using Software To Control The Protection MOSFETs                                 |    |

| Clearing Overcurrent Interrupts                                                  |    |

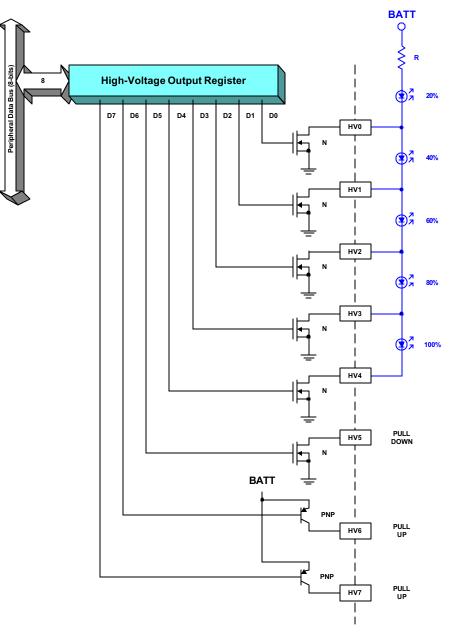

| High-Voltage Output Port                                                         |    |

| Description                                                                      |    |

| Operation                                                                        |    |

| High-Voltage Output Port Register Description                                    |    |

| Digital Peripherals                                                              |    |

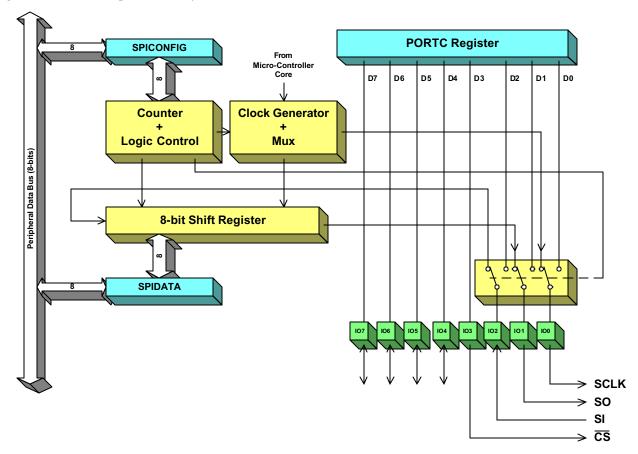

| High-Speed SPI Interface.                                                        |    |

| Description                                                                      |    |

| Operation                                                                        |    |

| SPI Interface Register Descriptions                                              |    |

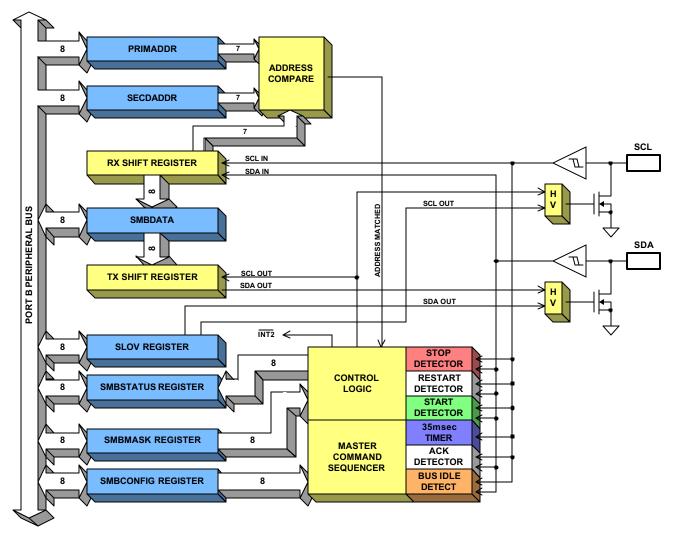

| SMBus Interface.                                                                 |    |

| Introduction                                                                     |    |

| Features                                                                         |    |

| Description                                                                      |    |

| Start Detector                                                                   |    |

| Restart Detector                                                                 |    |

| Stop Detector                                                                    |    |

|                                                                                  |    |

| ACK Detector                                                                     |    |

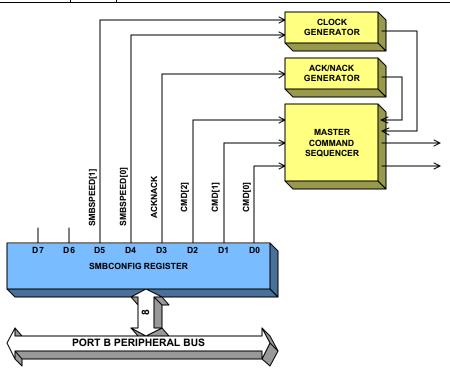

| ACK/NACK Generator                                                               |    |

| Automatic ACK Generation After a Start or Restart Condition:                     |    |

| Conditional ACK Generation In All Other Slave or Master Mode Receive Operations: |    |

| SCL Holding Detector.                                                            |    |

| Automatic SCL Hold Circuit                                                       |    |

| Address Comparator                                                               |    |

| Bus Idle Detector                                                                |    |

| Master Clock Generator                                                           |    |

| 35msec Timer                                                                     |    |

| Slave Mode Operation                                                             |    |

| Initialization                                                                   |    |

| Master Mode Operation                                                            |    |

| Sending a START Signal                                                           |    |

| Sending the Slave Address and Data Direction Bit                                 |    |

| Sending a STOP Signal.                                                           |    |

| Sending a Repeated START Signal                                                  |    |

| SMBus Interface Register Descriptions                                            |    |

| Design And Applications Information                                              | 71 |

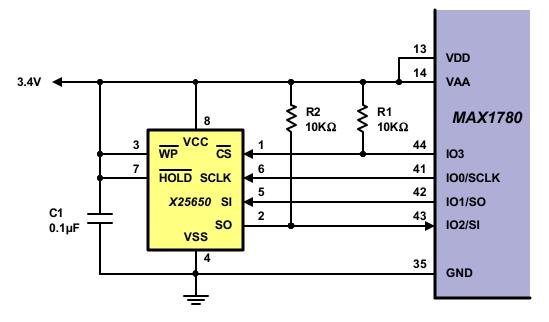

| Interfacing With An External Serial EEPROM                                       |    |

| Chip Select (CS\)                                                                |    |

| Serial Clock (SCLK)                                                              |    |

| Serial Output (SO)                                                               |    |

| Serial Input (SI)                                                                | 71 |

\_\_\_\_\_

| Properly Connecting Lithium Ion Cells                                                 | 72 |

|---------------------------------------------------------------------------------------|----|

| Choosing The Current Sense Resistor (R <sub>cs</sub> )                                |    |

| Setting The Overcurrent Thresholds                                                    |    |

| Handling Battery Insertion Surge Currents                                             |    |

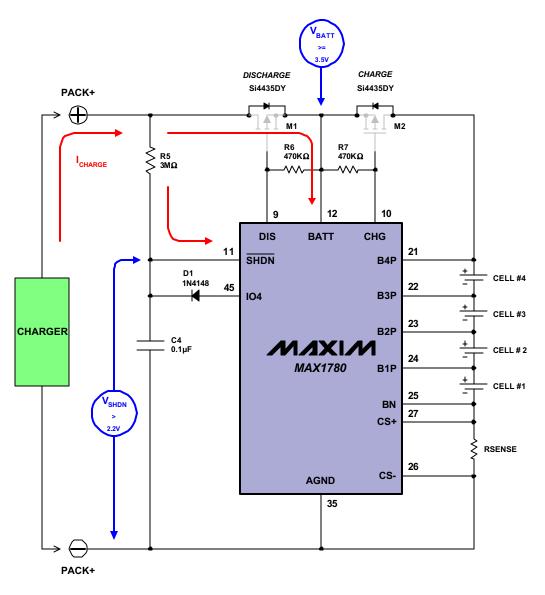

| Handling Charger Connection Surge Currents                                            |    |

| Improving Fuel Gauge Measurement Accuracy                                             |    |

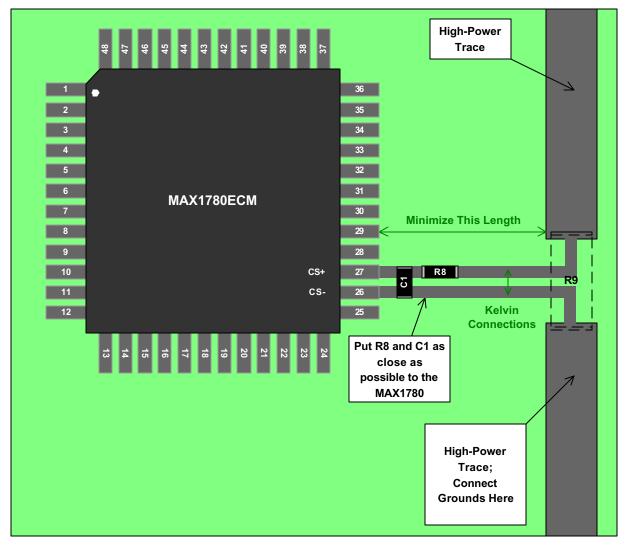

| Use The Correct Ground Layout                                                         |    |

| Filter The Current Sense Inputs                                                       |    |

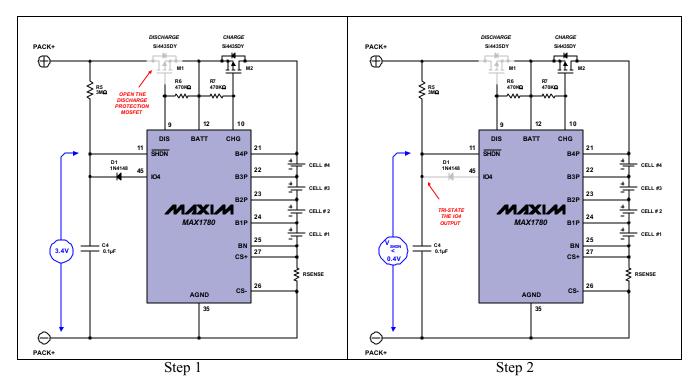

| Connecting The SHDN Pin                                                               | 77 |

| Shutting Down The MAX1780 Under Software Control                                      |    |

| Starting Up The MAX1780 After Being Shutdown                                          |    |

| Implementing An SBS-IF Safety Signal.                                                 |    |

| Circuit Layout And Grounding                                                          |    |

| Pin Descriptions                                                                      |    |

| Detailed Operating Circuit                                                            |    |

| Absolute Maximum Ratings                                                              |    |

| Electrical Characteristics                                                            |    |

| Electrical Characteristics (continued)                                                |    |

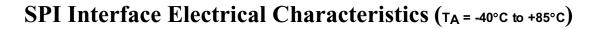

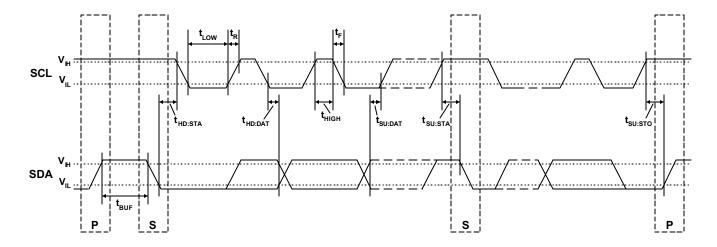

| SPI Interface Electrical Characteristics                                              |    |

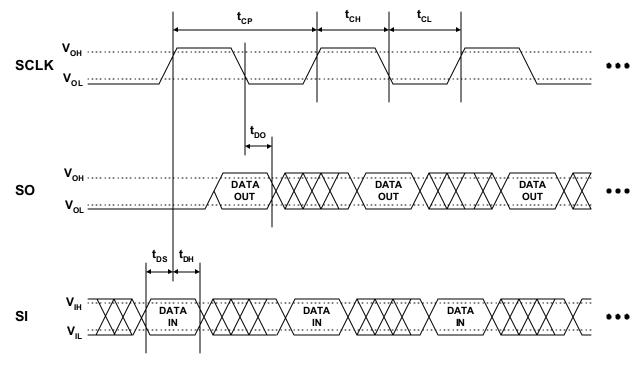

| SMBus Interface Electrical Characteristics                                            |    |

| Electrical Characteristics (continued, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )       |    |

| Electrical Characteristics (continued, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )       |    |

| SPI Interface Electrical Characteristics ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )   |    |

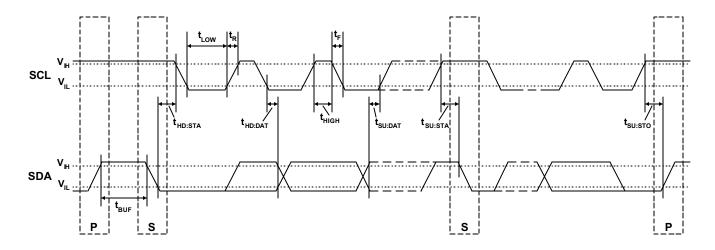

| SMBus Interface Electrical Characteristics ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ) |    |

| Typical Operating Characteristics                                                     |    |

| Typical Operating Characteristics (continued)                                         |    |

| Typical Operating Characteristics (continued)                                         |    |

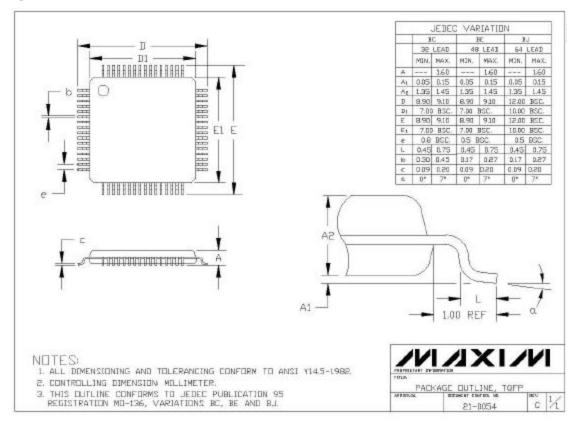

| Package Information                                                                   |    |

| Appendix                                                                              |    |

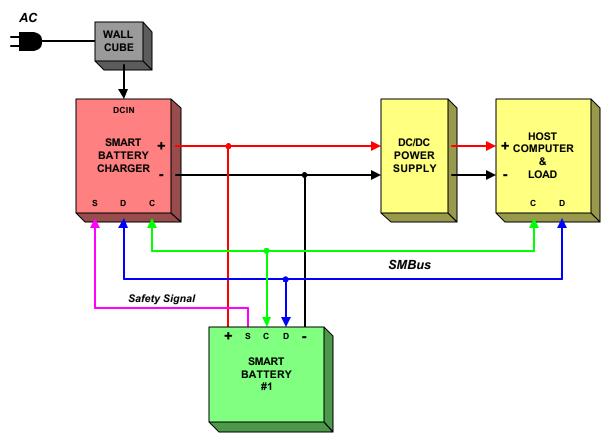

| An Overview Of Smart Batteries                                                        |    |

| The Smart Battery In A Notebook Power Supply System                                   |    |

| What Makes Smart Batteries "Smart"?                                                   |    |

| Lithium Ion Cell Protection                                                           |    |

| Instruction Set Summary                                                               |    |

| Errata                                                                                |    |

| 1. ODO/OCO Section:                                                                   |    |

| Impact:                                                                               |    |

| Solution/Workaround:                                                                  |    |

| 2. ODI/OCI Comparators:                                                               |    |

| Impact:                                                                               |    |

| Solution/Workaround:                                                                  |    |

| 3. SPI Interface:                                                                     |    |

| Impact:                                                                               |    |

| Solution/Workaround:                                                                  |    |

| 4. SMBus Interface:                                                                   |    |

| Impact:                                                                               |    |

| Solution/Workaround:                                                                  |    |

|                                                                                       |    |

## **Table Of Figures**

| Figure 1, MAX1780 Harvard Architecture                                                                        | 9            |

|---------------------------------------------------------------------------------------------------------------|--------------|

| Figure 2, MAX1780 Block Diagram                                                                               | 10           |

| Figure 3, MAX1780 Instruction Pipeline                                                                        | 11           |

| Figure 4, Instruction Cycle Phase Clocks                                                                      | 12           |

| Figure 5, MAX1780 Programming Model                                                                           | 13           |

| Figure 6, MAX1780 Program Memory Organization                                                                 | 17           |

| Figure 7, DRAM Organization                                                                                   |              |

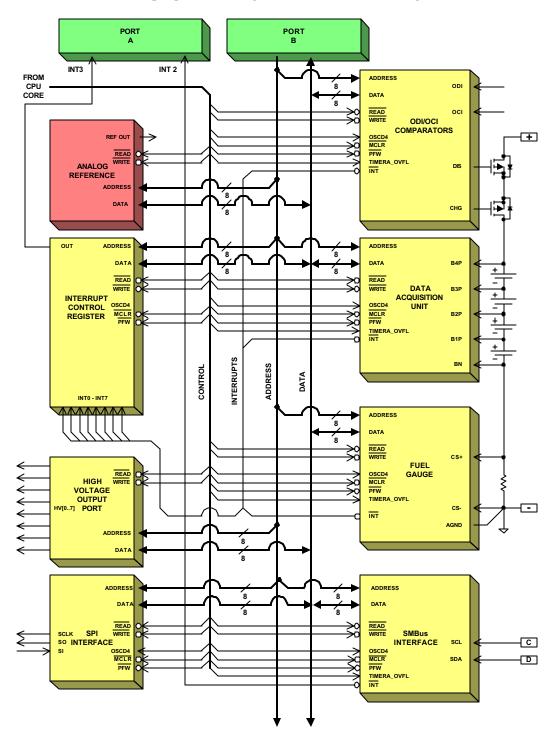

| Figure 8, MAX1780 On-Board Peripherals                                                                        |              |

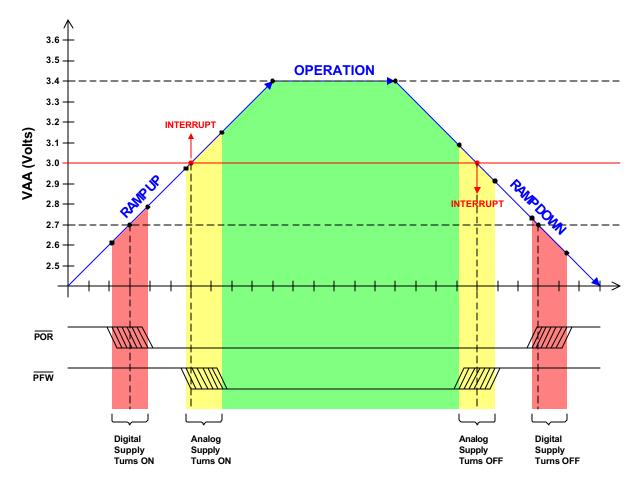

| Figure 9, MAX1780 Power Supply Sequencing                                                                     |              |

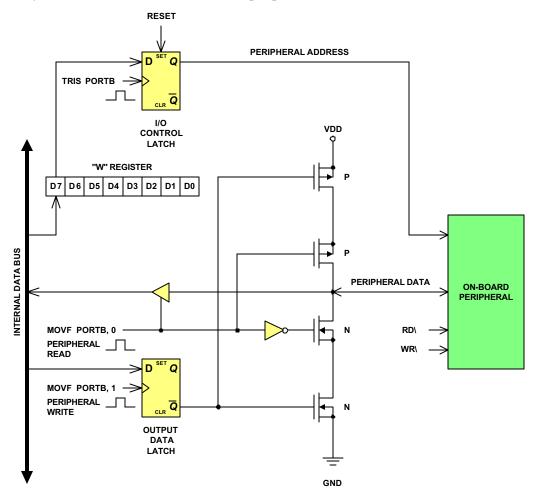

| Figure 10, PORT B Structure (1 Bit)                                                                           |              |

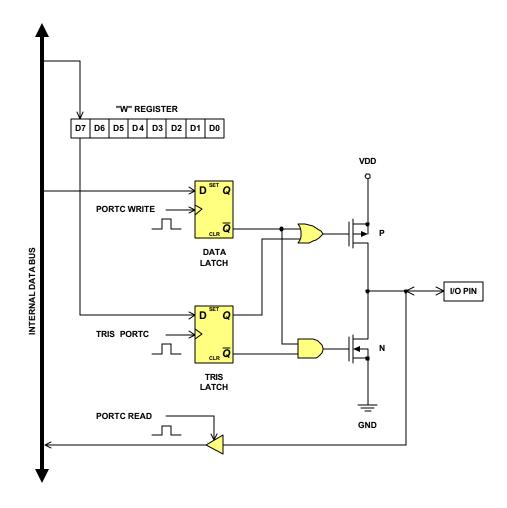

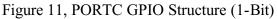

| Figure 11, PORTC GPIO Structure (1-Bit)                                                                       |              |

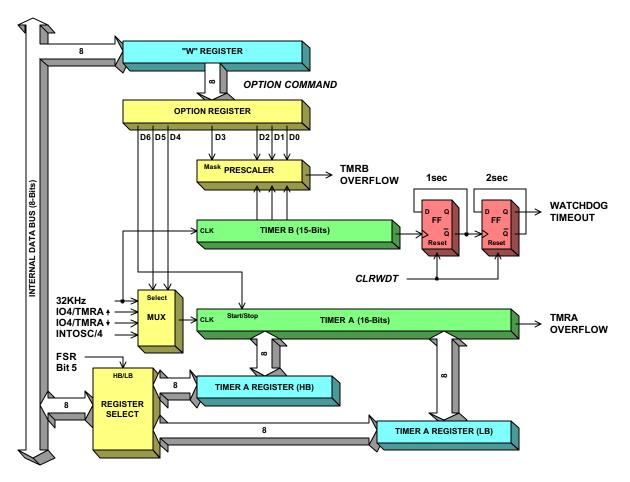

| Figure 12, MAX1780 Timers                                                                                     |              |

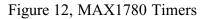

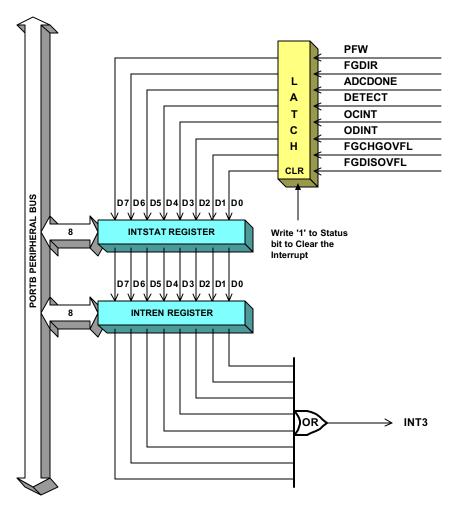

| Figure 13, MAX1780 Interrupt Structure                                                                        |              |

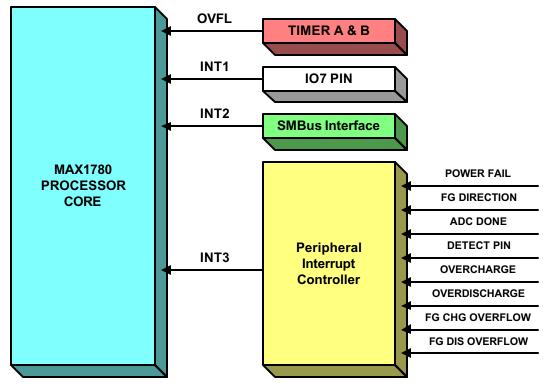

| Figure 14, Peripheral Interrupt Control Registers                                                             |              |

| Figure 15, Fuel Gauge Block Diagram                                                                           |              |

| Figure 16, Data Acquisition Unit Block Diagram.                                                               | 44           |

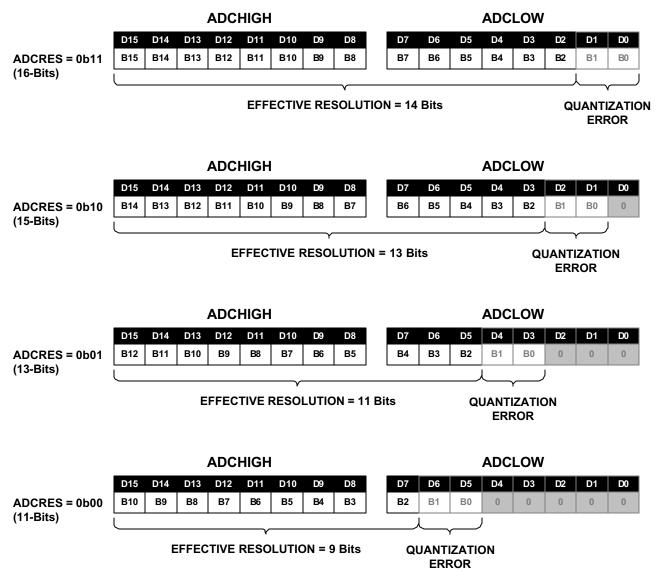

| Figure 17, Effective ADC Resolutions.                                                                         |              |

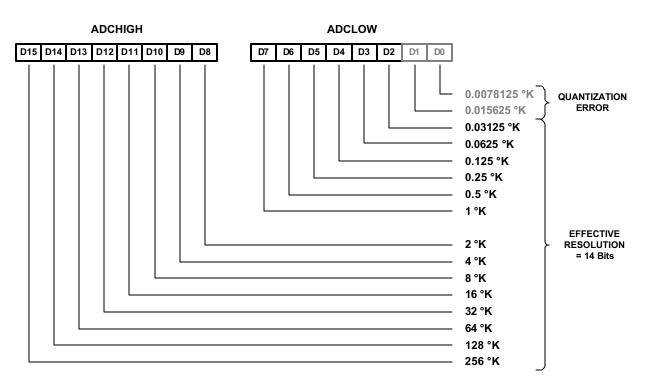

| Figure 18, Temperature Conversion Bit Weights                                                                 |              |

| Figure 19, Overcurrent Comparator Functional Diagram                                                          |              |

| Figure 20, High-Voltage Output Port.                                                                          |              |

| Figure 21, High-Speed SPI Port.                                                                               |              |

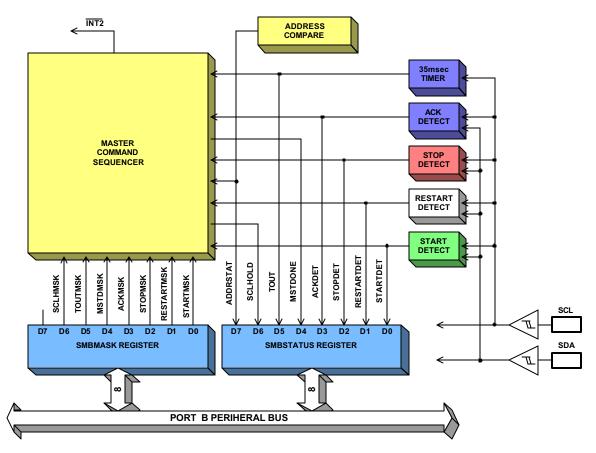

| Figure 22, SMBus Interface Block Dia gram                                                                     |              |

| Figure 23, SMBus Configuration Register                                                                       |              |

| Figure 24, SMBus Status And Mask Registers.                                                                   |              |

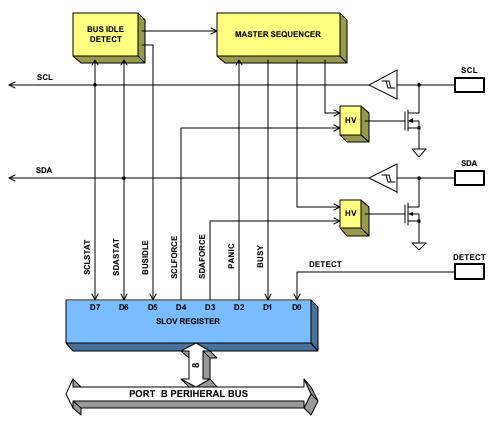

| Figure 25, SMBus SLOV Register                                                                                |              |

| Figure 26, External EEPROM Interface Schematic                                                                |              |

| Figure 27, Proper Series Cell Connections                                                                     |              |

| Figure 28, Overcurrent Comparator System Diagram<br>Figure 30, Layout Recommendation For Current Sense Inputs |              |

| Figure 30, Layout Recommendation For Current Sense inputs<br>Figure 31, MAX1780 Software Shutdown Procedure   | יייייי<br>דד |

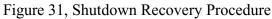

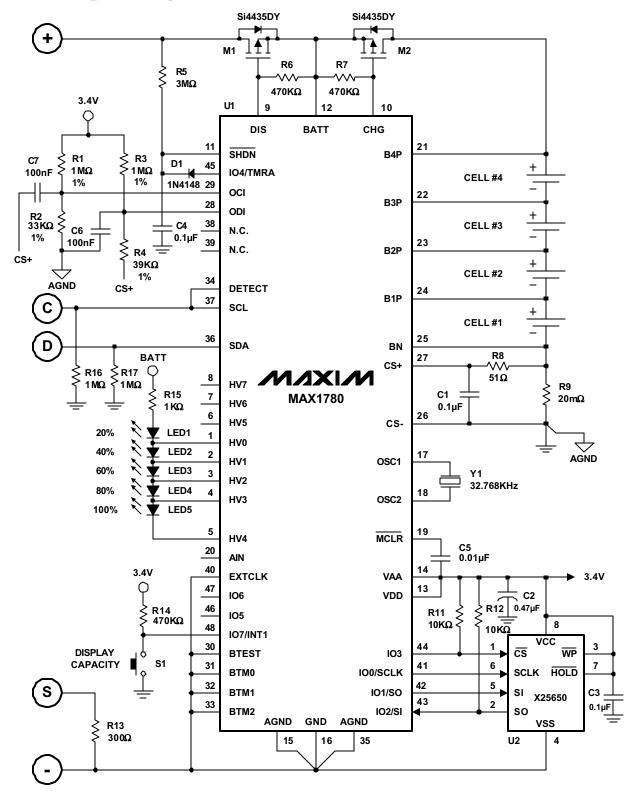

| Figure 31, MAA1780 Software Shuddown Flocedure<br>Figure 32, Shutdown Recovery Procedure                      |              |

| Figure 33, MAX1780 Safety Signal Circuit                                                                      |              |

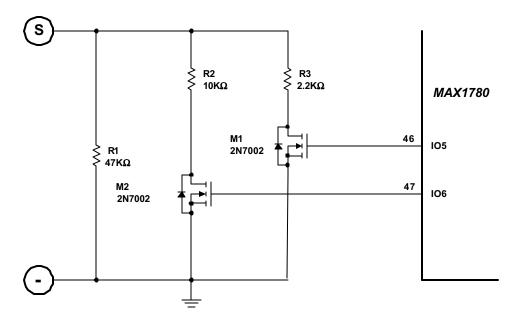

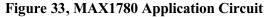

| Figure 34, MAX1780 Application Circuit                                                                        |              |

| Figure 35, SPI Interface Timing                                                                               | 02           |

| Figure 36, SMBus Timing Diagram                                                                               |              |

| Figure 37, SPI Interface Timing $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$                               | 94           |

| Figure 38, SMBus Timing Diagram ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )                                    |              |

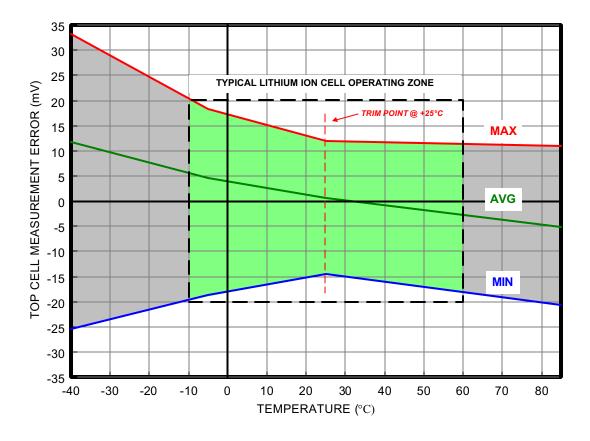

| Figure 39, Typical ADC Voltage Measurement Error.                                                             |              |

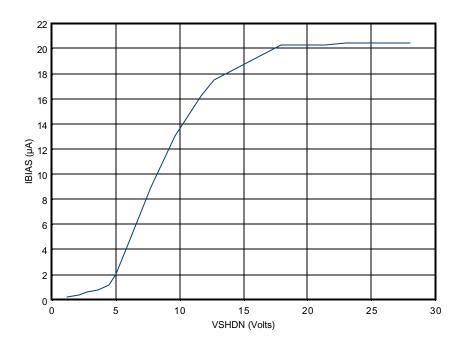

| Figure 40, SHDN Input Bias Current vs. V <sub>SHDN</sub>                                                      |              |

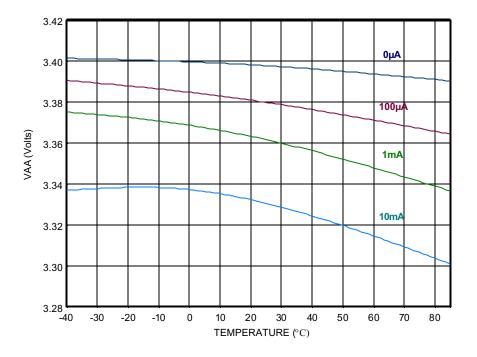

| Figure 41, V <sub>AA</sub> Output Voltage vs. Load Current and Temperature                                    |              |

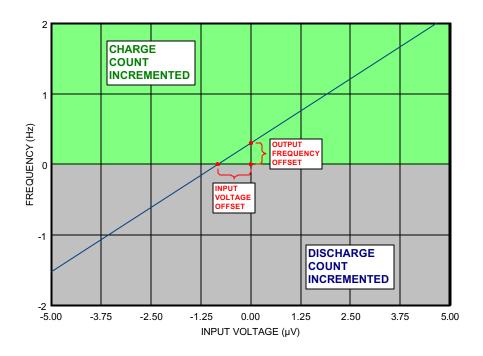

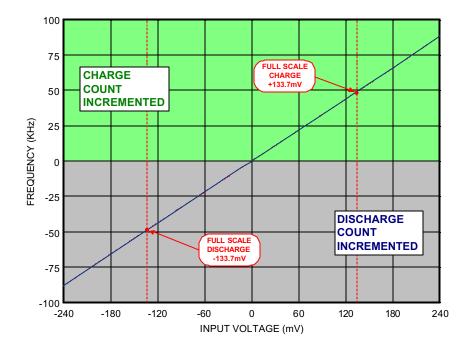

| Figure 42, Fuel Gauge Frequency vs. Input Voltages Near Zero                                                  |              |

| Figure 43, Fuel Gauge Frequency vs. Input Voltage                                                             | .101         |

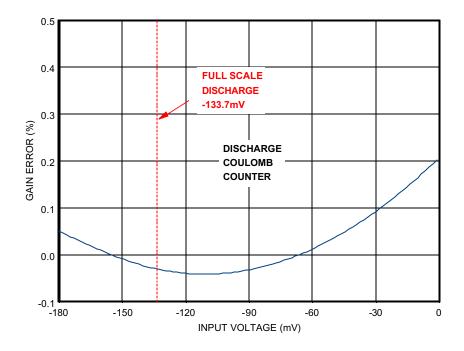

| Figure 44, Discharge Gain Error vs. Fuel Gauge Input Voltage                                                  |              |

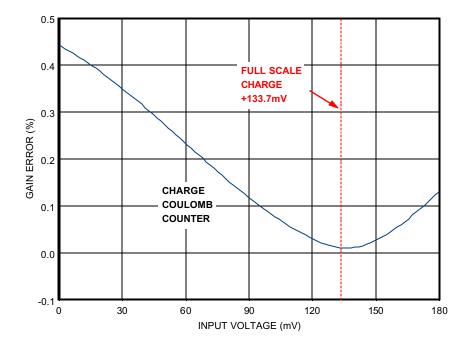

| Figure 45, Charge Gain Error vs. Fuel Gauge Input Voltage                                                     |              |

| Figure 46, Simplified Notebook Computer Power Supply System                                                   |              |

| Figure 47, Typical Smart Battery Pack Implemented With The MAX1780                                            |              |

|                                                                                                               |              |

\_\_\_\_\_

## **Table Of Tables**

| Table 1, Overdischarge Logic Truth Table                                     | 53 |

|------------------------------------------------------------------------------|----|

| Table 2, Overcharge Logic Truth Table                                        |    |

| Table 3, SMBus AC Characteristics                                            |    |

| Table 4, SMBus DC Characteristics                                            | 91 |

| Table 5, SMBus AC Characteristics ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ) | 97 |

| Table 6, SMBus DC Characteristics ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ ) | 97 |

## **List Of Applicable Documents**

"System Management Bus Specification", Revision 1.1, dated December 11, 1998.

"Smart Battery Data Specification", Revision 1.1, dated December 11, 1998.

"MAX1780 ROM Code Supplement", (Contact the Factory for availability)

"MAX1780 Programmers Reference Manual", (Contact the Factory for availability)

## **Architectural Overview**

### Introduction

The MAX1780 Advanced Smart Battery Pack Controller was designed to provide Smart Battery pack designers with a flexible solution that accurately measures individual cell characteristics. I combines an 8bit RISC microprocessor core, program and data memory, with an arsenal of precision analog peripherals. Together with an external serial EEPROM, the MAX1780 provides the most integrated solution for developing battery pack electronics in the industry.

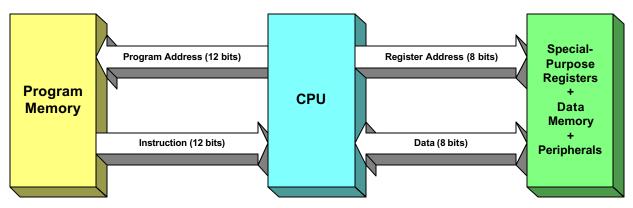

### Harvard Architecture

The MAX1780 uses a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. A 12-bit wide program memory bus fetches a 12-bit instruction in a single cycle. The 12-bit wide instruction opcodes make it possible to have all single word instructions.

Figure 1, MAX1780 Harvard Architecture

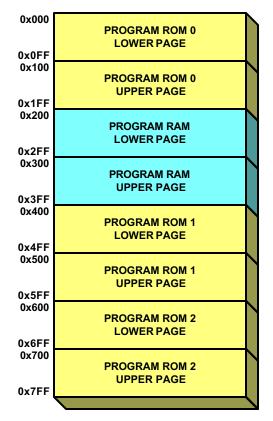

The MAX1780 addresses 2K x 12 of internal program memory, organized as three blocks of ROM, each 512 x 12, and one program RAM block 512 x 12. Using special ROM routines (see MAX1780 ROM Supplement for details), the MAX1780 can access up to  $64K \times 8$  of external serial EEPROM memory. This provides software designers with the ability to load program code residing in external EEPROM into program RAM under program control. This innovative capability can be used to develop self-adapting battery management and control software.

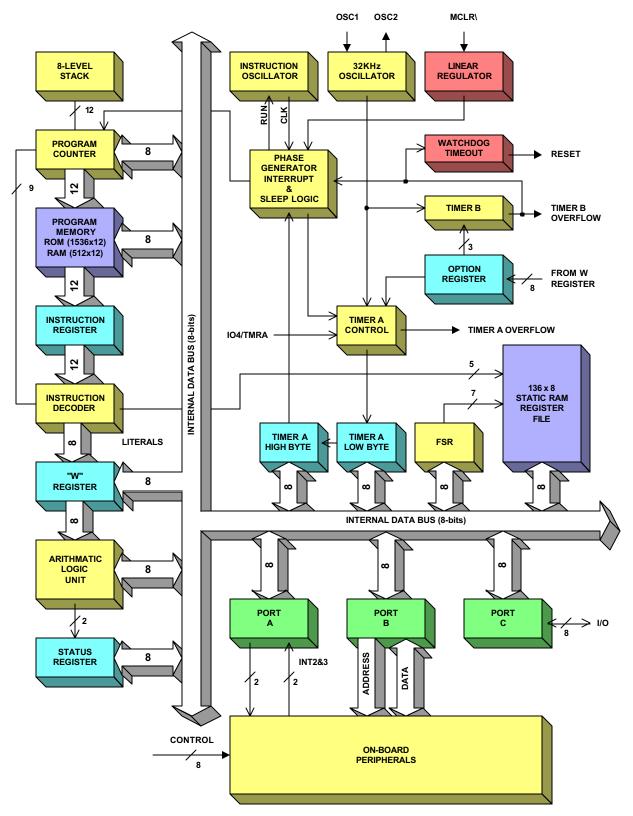

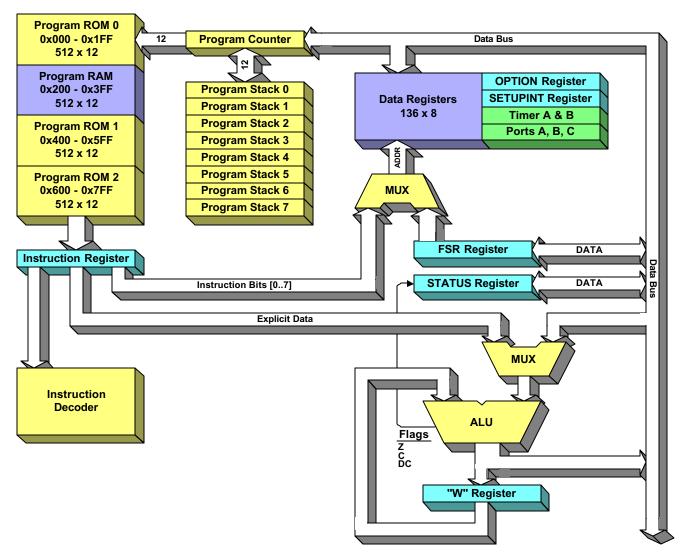

Figure 2 shows a block diagram of the MAX1780 core microcontroller. MAX1780 memory is organized into program memory and data memory. Program memory pages are accessed using one or two STATUS register bits. Data memory is composed of RAM, organized as 8, 16 byte groups or pages. Collectively, all of the DRAM pages are called the Register File. The register file is divided into two functional groups: special function registers and general purpose registers. DRAM is accessed using the File Selection Register (FSR).

The special function registers include the TIMERA Register, the Program Counter (PC), the Status Register, the SETUPINT Register, the I/O registers (ports), and the File Select Register (FSR). In addition, special purpose registers are used to control the I/O port configuration and prescaler options. The General Purpose registers are used for data and control information under command of the instructions.

PORTB is used as a dedicated internal interface between the processor core and all the on-board peripherals. Most of the on-board peripherals function autonomously, generating interrupts to the processor core when service is required.

Figure 2, MAX1780 Block Diagram

### **Detailed Description Of MAX1780**

### **Instruction Execution**

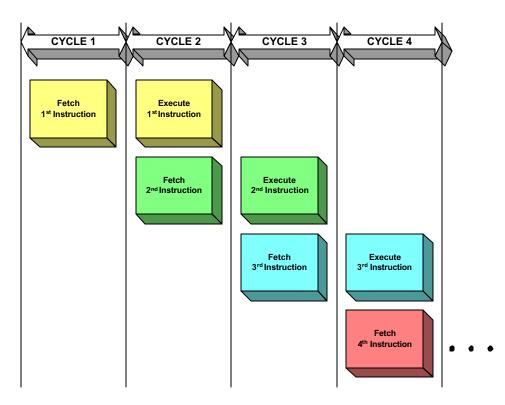

The MAX1780 processor core incorporates a two-stage pipeline. The instruction fetch and execution are pipelined such that an instruction fetch takes one instruction cycle while the instruction decode and execution takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change, for example a GOTO instruction, then two cycles are required to complete the instruction, breaking the pipeline's flow. Figure 3 shows how instruction pipelining increases the processor throughput.

Figure 3, MAX1780 Instruction Pipeline

### **Phase Clocks**

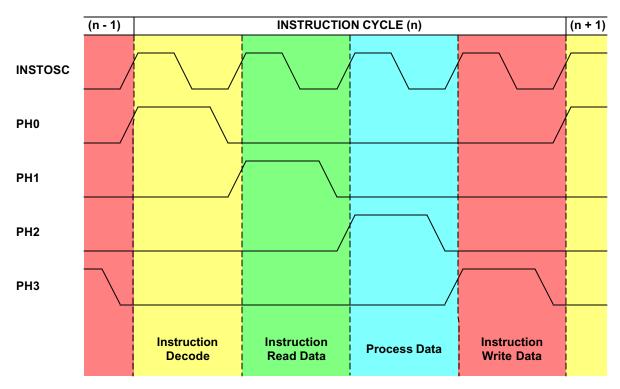

As shown in Figure 4, an Instruction Cycle consists of four phase clocks. The phase clocks do not overlap, and each phase transition occurs on the rising edge of the Instruction Oscillator. Phase 0 (PH0) is called the Decode Phase, where fetched instructions are decoded. Phase 1 (PH1) is known as the Data Read Phase. Any data from Data Memory required to complete the instruction will be read at this time. Phase 2 (PH2) is called the Process Phase, in which any data retrieved in PH1 is processed. The final phase, Phase 3 (PH3), is the Data Write Phase and is used to write data manipulated during PH2 back to Data Memory.

Figure 4, Instruction Cycle Phase Clocks

Figure 5, MAX1780 Programming Model

### **CPU** Architecture

Figure 5 shows the MAX1780's central processing unit (CPU) architecture. As shown, instructions in program memory and variables in data memory are accessed using separate buses

### **Program Counter (PC)**

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC. It should be noted that all subroutine calls are limited to the first 256 locations of any program memory page (512 words long).

### **Program Stack**

The MAX1780 has a 12-bit wide, eight-level hardware stack. This allows program developers to create code with nested subroutine calls. When CALL instructions are executed, pushing the current value onto the stack saves the processor context. A word of caution, the MAX1780 program stack has only 8-levels. Programmers should not create code that has unlimited nesting of subroutine calls, or a stack overflow is possible.

A subroutine call is completed with a RETURN or RETLW instruction, both of which will pop the contents of the stack into the program counter. The RETLW instruction also loads the "W" Register with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

### Arithmetic Logic Unit (ALU)

The MAX1780 CPU contains an 8-bit ALU and working register. The ALU is a general-purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the "W" (working) Register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W Register or a file register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register.

### Working Register ("W")

The "W" Register serves as an accumulator or temporary storage register for many instructions. The "W" Register is not directly accessible. Its contents must be moved to other registers that are directly accessible, in order to be read. The "W" Register is also used in every arithmetic operation.

### Option Register (Write Only, via the "W" Register and OPTION Instruction)

The Option Register is a CPU core register. It is not directly accessible and is not in the Register File address space. To change the contents of the Option Register, use the OPTION instruction, which loads the contents of the "W" Register into the Option Register. Through the Option Register the user has access to the Timer A and Timer B controls. Additionally, whether the Instruction Oscillator runs in SLEEP Mode or not may be selected.

Since the contents of the Option Register cannot be read, it is suggested that programmers "shadow" its contents in a global software variable, and all changes be made to the global variable. The global variable is then moved to the "W" Register and an OPTION Instruction executed to affect changes in the Option Register.

|           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

|           | OSLB  | TMRAD | TAS1  | TAS0  | MSKW  | PS2   | PS1   | PS0   |

| POR STATE | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| OSLB |                                                                                           |

|------|-------------------------------------------------------------------------------------------|

| 0    | The Internal Instruction Execution Oscillator Is Turned off During SLEEP Mode. INTOSC OFF |

|      | in SLEEP. (See note below)                                                                |

| 1    | The Internal Instruction Execution Oscillator Runs During SLEEP Mode. INTOSC ON in SLEEP. |

| TMRAD |                         |

|-------|-------------------------|

| 0     | Timer A (TMRA) Enabled  |

| 1     | Timer A (TMRA) Disabled |

| TAS1 | TAS0 |                                                             |

|------|------|-------------------------------------------------------------|

| 0    | 0    | TMRA increments count on the falling edge of IO4/TMRA pin   |

| 0    | 1    | TMRA increments count on the rising edge of IO4/TMRA pin    |

| 1    | 0    | TMRA increments count on the rising edge of the 32KHz Clock |

| 1    | 1    | TMRA increments count on rising edge of INTOSC/4            |

| MSKB |                                                                                           |

|------|-------------------------------------------------------------------------------------------|

| 0    | TIMER B (TMRB) overflow generates an interrupt if INTOFF = 0 (cleared in STATUS Register) |

| 1    | TIMER B (TMRB) overflow does not generate an interrupt                                    |

| PS2 | PS1 | PS0 |                                               |       |     |

|-----|-----|-----|-----------------------------------------------|-------|-----|

| 0   | 0   | 0   | TMRB period = $(1/32 \text{KHz}) * 256 * 2$   | 15.62 | ms  |

| 0   | 0   | 1   | TMRB period = $(1/32 \text{KHz}) * 256 * 4$   | 31.25 | ms  |

| 0   | 1   | 0   | TMRB period = $(1/32 \text{KHz}) * 256 * 8$   | 62.50 | ms  |

| 0   | 1   | 1   | TMRB period = $(1/32 \text{KHz}) * 256 * 16$  | 125.0 | ms  |

| 1   | 0   | 0   | TMRB period = $(1/32 \text{KHz}) * 256 * 32$  | 250.0 | ms  |

| 1   | 0   | 1   | TMRB period = $(1/32 \text{KHz}) * 256 * 64$  | 500.0 | ms  |

| 1   | 1   | 0   | TMRB period = $(1/32 \text{KHz}) * 256 * 128$ | 1.0   | sec |

| 1   | 1   | 1   | *FACTORY USE ONLY (DO NOT USE)                | -     | -   |

Note: The instruction oscillator will continue to run in SLEEP while an SMBus Slave transmission is in progress.

### Setupint Register (Write Only, via the "W" Register and FREE Instruction)

The Setupint Register is a CPU core register. It is not directly accessible and is not in the Register File address space. To change the contents of the Setupint Register, use the FREE instruction with FSR bits 5 and 6 cleared to '0', which loads the contents of the "W" Register into the Setupint Register. The Setupint Register is used to set-up the triggering characteristics of the MAX1780's three interrupt channels. Additionally, Bit 0 is the global enable bit for addressing the on-board peripherals.

|          | Bit 7  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------|--------|--------|-------|-------|-------|-------|-------|

|          | SENSE3 | SENSE2 | SENSE1 | EN1SN | EDGE3 | EDGE2 | EDGE1 | PADDR |

| OR STATE | 1      | 1      | 1      | 1     | 1     | 1     | 1     | 1     |

POR STATE

#### Interrupt 3

| EDGE3 | SENSE3 |                                                                         |  |

|-------|--------|-------------------------------------------------------------------------|--|

| 0     | 0      | IF3 Flag in the PORTA Register is set to '1' when $INT3 = 0$ '.         |  |

| 0     | 1      | IF3 Flag in the PORTA Register is set to '1' when $INT3 = '1'$ .        |  |

| 1     | 0      | IF3 Flag in the PORTA Register is set to '1' on a Falling Edge of INT3. |  |

| 1     | 1      | IF3 Flag in the PORTA Register is set to '1' on a Rising Edge of INT3.  |  |

|       |        |                                                                         |  |

Note: The Peripheral Interrupt Controller uses INT3 for interrupts. There are total of 8 INT3 interrupt sources: POWER FAILURE, FGCHGSTAT, ADCDONE, DETECT, OCICMP, ODICMP, FGCHGOFL, FGDISOFL.

#### Interrupt 2

| EDGE2 | SENSE2 |                                                                         |

|-------|--------|-------------------------------------------------------------------------|

| 0     | 0      | IF2 Flag in the PORTA Register is set to '1' when $INT2 = '0'$ .        |

| 0     | 1      | IF2 Flag in the PORTA Register is set to '1' when INT2 = '1'.           |

| 1     | 0      | IF2 Flag in the PORTA Register is set to '1' on a Falling Edge of INT2. |

| 1     | 1      | IF2 Flag in the PORTA Register is set to '1' on a Rising Edge of INT2.  |

Note: The SMBus Interface uses INT2 for interrupts. There are a total of 7 INT2 interrupt sources: START, RESTART, STOP, SCLHOLD, TOUT, MSTON, ACK.

#### Interrupt 1

| EN1SN | EDGE1 | SENSE1 |                                                                             |

|-------|-------|--------|-----------------------------------------------------------------------------|

| 0     | 0     | 0      | Do not clear the EN1SN bit to '0'.                                          |

| 0     | 0     | 1      | Do not clear the EN1SN bit to '0'.                                          |

| 0     | 1     | 0      | Do not clear the EN1SN bit to '0'.                                          |

| 0     | 1     | 1      | Do not clear the EN1SN bit to '0'.                                          |

| 1     | 0     | 0      | IF1 Flag in the PORTA Register is set to '1' when the $IO7/INT1$ pin = '0'. |

| 1     | 0     | 1      | IF1 Flag in the PORTA Register is set to '1' when the $IO7/INT1$ pin = '1'. |

| 1     | 1     | 0      | IF1 Flag in the PORTA Register is set to '1' on an IO7/INT1 Falling Edge.   |

| 1     | 1     | 1      | IF1 Flag in the PORTA Register is set to '1' on an IO7/INT1 Rising Edge.    |

Note: Do not clear the EN1SN bit to '0', otherwise this could result in a constant interrupt from INT1.

#### **Peripheral Address Bit**

| PADDR        |                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------|

| D0           | This bit must be set to '1' to enable access to on-board peripherals.                                 |

| Note: This b | bit defaults to '1' on Power-On-Reset. Do not change or the on-board peripherals cannot be addressed. |

### **Memory Organization:**

The MAX1780 program memory is divided into four blocks  $512 \times 12$ -bits in size. Each block is further divided into  $256 \times 12$ -bits upper and lower pages. The first, third, and fourth blocks are Program ROM, which are programmed at the factory. The second memory block is Program RAM, which is loaded with user code at boot, and can be modified during operation.

Figure 6, MAX1780 Program Memory Organization

#### **Page Boundaries**

The Page Preselect bits (PA0 - PA1) of the STATUS Register determine which 512 x 12 page of program memory the MAX1780 CPU fetches instructions from. They are mapped as:

#### Program Memory Selection:

| PA2 | PA1 | PA0 | <b>Address Range</b> | Memory Selected |

|-----|-----|-----|----------------------|-----------------|

| Х   | 0   | 0   | 0x000 - 0x1FF        | ROM (512 WORDS) |

| Х   | 0   | 1   | 0x200 - 0x3FF        | RAM (512 WORDS) |

| Х   | 1   | 0   | 0x400 - 0x5FF        | ROM (512 WORDS) |

| Х   | 1   | 1   | 0x600 - 0x7FF        | ROM (512 WORDS) |

Each instruction cycle causes the Program Counter to increment, which in turn, increments the address in program memory from where instructions are fetched. Program flow within a  $512 \times 12$  page is controlled by GOTO and CALL instructions. GOTO instructions provide 9 bits of address for the Program Counter, so program control can be transferred to any memory address within a page. The CALL instruction on the other

hand, supplies the Program Counter with only 8 bits of address. This limits jumps by the CALL instruction to the lower half of the memory page selected by the Page Preselect Bits (PA0 – PA1).

The Page Preselect Bits have no effect on program flow until a CALL or a GOTO instruction is executed. If the Program Counter is pointing to the last address of a selected memory page, when it increments it will cause the program to continue in the next higher page. However, the Page Preselect bits in the STATUS register will not be updated. Therefore, the next GOTO or CALL instruction will send the program to the page specified by the Page Preselect bits (PA1:PA0).

For example, a NOP at location 1FFh (page 0) increments the PC to 200h (page 1). A GOTO xxx at 200h will return the program to address 0xxh on page 0 (assuming that PA1:PA0 are clear). To prevent this, the page preselect bits must be updated under program control.

#### Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). This is indirect addressing.

The FSR is an 8-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area. The FSR [4:0] bits are used to select data memory addresses 0x00 to 0x1F.

### **Register File Organization**

### Data RAM

The MAX1780 has 144 bytes of read/writable Data Memory. It is organized as follows:

- 8 Special Purpose Register Files (Page Independent)

- 8 General Purpose Registers (Page Independent)

- 128 General Purpose Registers (Page Dependent)

The FSR Register (bits 5 - 7) is used to select the desired data memory block.

As shown in Figure 7 below, the special purpose registers and first 8 general purpose registers (0x00 - 0x0F) are shadowed across all eight Data RAM blocks. For this reason, the contents of these registers are accessible regardless of which memory block is selected by FSR bits 5 – 7. Data stored in this area is referred to as "Page Independent" memory. Selecting the appropriate FSR bits allow access to data residing in the upper 16 bytes of each block. Data stored in this area is referred to as "Page Dependent" memory.

| 000                      | 001                      | 010                      | 011                      | 100                      | 101                      | 110                      | 111                      |

|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 0x00 INDF                | 0x20 INDF                | 0x40 INDF                | 0x60 INDF                | 0x80 INDF                | 0xA0 INDF                | 0xC0 INDF                | 0xE0 INDF                |

| TIMERA (LB)              | TIMERA (HB)              |

| PC                       |

| STATUS                   |

| FSR                      |

| PORTA                    |

| PORTB                    |

| PORTC                    |

| GPR<br>(8 Bytes)<br>0x0F | GPR<br>(8 Bytes)<br>0x2F | GPR<br>(8 Bytes)<br>0x4F | GPR<br>(8 Bytes)<br>0x6F | GPR<br>(8 Bytes)<br>0x8F | GPR<br>(8 Bytes)<br>0xAF | GPR<br>(8 Bytes)<br>0xCF | GPR<br>(8 Bytes)<br>0xEF |

| 0x10                     | 0x30                     | 0x50                     | 0x70                     | 0x90                     | 0xB0                     | 0xD0                     | 0xF0                     |

| GPR<br>(16 Bytes)        |

| 0x1F                     | 0x3F                     | 0x5F                     | 0x7F                     | 0x9F                     | 0xBF                     | 0xDF                     | 0xFF                     |

| BLOCK 0                  | BLOCK 1                  | BLOCK 2                  | BLOCK 3                  | BLOCK 4                  | BLOCK 5                  | BLOCK 6                  | BLOCK 7                  |

FSR [ 7:5 ]

Figure 7, DRAM Organization

### File Select Register (FSR) Read/Write

The File Select Register selects which page of Data Memory can be accessed.

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                               | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 6                                                                                                                                      | Bit 5                                                                                                                                                                                                                               | Bit 4                         | Bit 3                         | Bit 2        | Bit 1        | Bit 0      |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|--------------|--------------|------------|

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |                                                                                                                                                                                                                                     |                               |                               |              |              |            |

| POR STA                                                           | TE                                                                                                                                                                                                                                                                                                                                                                            | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Х                                                                                                                                          | Х                                                                                                                                                                                                                                   | Х                             | Х                             | Х            | X            | Х          |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |                                                                                                                                                                                                                                     |                               |                               |              |              |            |

| Bit7                                                              | Bit6                                                                                                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPR S                                                                                                                                      | ELECTED                                                                                                                                                                                                                             |                               |                               |              |              |            |

| 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 0                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 0                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 0                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 1                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 1                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |                                                                                                                                                                                                                                     | - TIMERA                      |                               |              |              |            |

| 1                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            | •                                                                                                                                                                                                                                   | - TIMERA                      | •                             |              |              |            |

| 1                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPR Pa                                                                                                                                     | ige/Block 7                                                                                                                                                                                                                         | - TIMERA                      | High Byte                     | selected.    |              |            |

| Bit4                                                              | Do ao In                                                                                                                                                                                                                                                                                                                                                                      | don on don t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /Dom on dor                                                                                                                                | of Coloction                                                                                                                                                                                                                        |                               |                               |              |              |            |

| <b>DII</b> 4                                                      |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            | nt Selection                                                                                                                                                                                                                        | 6 bytes of ea                 | ach Page/Bl                   | ock) is acce | ssed The la  | ower 16    |