INITIAL RELEASE Final Electrical Specifications LTC1657

#### Parallel 16-Bit Rail-to-Rail Micropower DAC

November 1999

## FEATURES

- 16-Bit Monotonic Over Temperature

- Deglitched Rail-to-Rail Voltage Output: 8nV•s (Typ)

- 5V Single Supply Operation

- I<sub>CC</sub>: 650μA Typ

- Maximum DNL Error: ±1LSB

- Internal or External Reference

- Internal Power-On Reset

- Output Buffer Configurable for Gain of 1 or 2

- Parallel 16-Bit or 2-Byte Double Buffered Interface

- Narrow 28-Lead SSOP Package

- Multiplying Capability

## **APPLICATIONS**

- Smart Remote Transmitters

- Digital Calibration

- Industrial Process Control

- Automatic Test Equipment

# DESCRIPTION

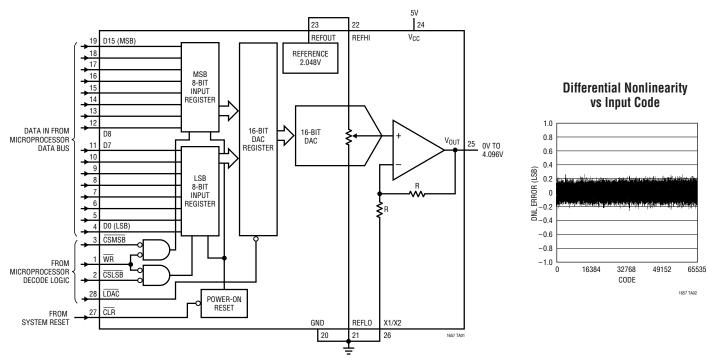

The LTC<sup>®</sup>1657 is a complete single supply, rail-to-rail voltage output, 16-bit digital-to-analog converter (DAC) in a 28-pin SSOP or PDIP package. It includes a rail-to-rail output buffer amplifier, an internal 2.048V reference and a double buffered parallel digital interface.

The LTC1657 operates from a 4.5V to 5.5V supply. It has a separate reference input pin that can be driven by an external reference. The full-scale output can be 1 or 2 times the reference voltage depending on how the X1/X2 pin is connected.

The LTC1657 is similar to Linear Technology Corporation's LTC1450 12-bit  $V_{OUT}$  DAC family allowing an upgrade path. It is the only buffered 16-bit parallel DAC in a 28-lead SSOP package and includes an onboard reference for stand alone performance.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

## **BLOCK DIAGRAM**

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                      |

|-----------------------------------------------|

| $V_{CC}$ to GND0.5V to 7.5V                   |

| TTL Input Voltage, REFHI, REFLO –0.5V to 7.5V |

| $V_{OUT}$ , REFOUT                            |

| Operating Temperature Range                   |

| LTC1657C0°C to 70°C                           |

| LTC1657I –40°C to 85°C                        |

| Maximum Junction Temperature 125°C            |

| Storage Temperature Range –65°C to 150°C      |

| Lead Temperature (Soldering, 10 sec) 300°C    |

|                                               |

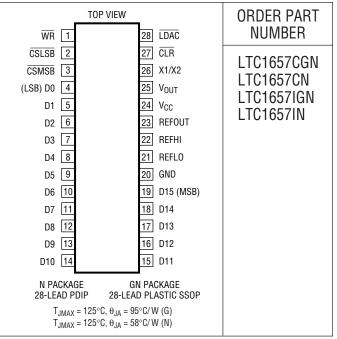

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 4.5V to 5.5V, V<sub>OUT</sub> unloaded, REFOUT tied to REFHI, REFLO tied to GND, X1/X2 tied to GND, unless otherwise noted.

| SYMBOL             | PARAMETER                  | CONDITIONS                                         |   | MIN | ТҮР  | MAX  | UNITS  |

|--------------------|----------------------------|----------------------------------------------------|---|-----|------|------|--------|

| DAC (Note 2)       |                            |                                                    |   |     |      |      |        |

|                    | Resolution                 |                                                    |   | 16  |      |      | Bits   |

|                    | Monotonicity               |                                                    | • | 16  |      |      | Bits   |

| DNL                | Differential Nonlinearity  | Guaranteed Monotonic (Note 3)                      | • |     | ±0.5 | ±1.0 | LSB    |

| INL                | Integral Nonlinearity      | (Note 3)                                           | • |     | ±4   | ±12  | LSB    |

| ZSE                | Zero Scale Error           |                                                    | • | 0   |      | 2    | mV     |

| V <sub>OS</sub>    | Offset Error               | Measured at Code 200                               | • |     | ±0.3 | ±3   | mV     |

| V <sub>OS</sub> TC | Offset Error Tempco        |                                                    |   |     | ±5   |      | μV/°C  |

|                    | Gain Error                 |                                                    | • |     | ±2   | ±16  | LSB    |

|                    | Gain Error Drift           |                                                    |   |     | 0.5  |      | ppm/°C |

| Power Sup          | ply                        |                                                    |   |     |      |      |        |

| V <sub>CC</sub>    | Positive Supply Voltage    | For Specified Performance                          | • | 4.5 |      | 5.5  | V      |

| I <sub>CC</sub>    | Supply Current             | $4.5V \le V_{CC} \le 5.5V$ (Note 4)                | • |     | 650  | 1200 | μA     |

| Op Amp D           | C Performance              |                                                    |   |     |      |      |        |

|                    | Short-Circuit Current Low  | V <sub>OUT</sub> Shorted to GND                    | • |     | 70   | 120  | mA     |

|                    | Short-Circuit Current High | V <sub>OUT</sub> Shorted to V <sub>CC</sub>        | • |     | 80   | 140  | mA     |

|                    | Output Impedance to GND    | Input Code = 0                                     |   |     | 40   | 120  | Ω      |

|                    | Output Line Regulation     | Input Code = 65535, V <sub>CC</sub> = 4.5V to 5.5V | • |     |      | 4    | mV/V   |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 4.5V to 5.5V, V<sub>OUT</sub> unloaded, REFOUT tied to REFHI, REFLO tied to GND, X1/X2 tied to GND, unless otherwise noted.

| SYMBOL            | PARAMETER                    | CONDITIONS                                    |   | MIN          | ТҮР   | MAX                   | UNITS  |

|-------------------|------------------------------|-----------------------------------------------|---|--------------|-------|-----------------------|--------|

| AC Perfor         | mance                        |                                               | I |              |       | I                     |        |

|                   | Voltage Output Slew Rate     | (Note 5)                                      |   | ±0.3         | ±0.7  |                       | V/µs   |

|                   | Voltage Output Settling Time | (Note 5) to 0.0015% (16-Bit Settling Time)    |   |              | 20    |                       | μs     |

|                   |                              | (Note 5) to 0.012% (13-Bit Settling Time)     |   |              | 10    |                       | μs     |

|                   | Digital Feedthrough          |                                               |   |              | 0.3   |                       | nV∙s   |

|                   | Midscale Glitch Impulse      | DAC Switch Between 8000 and 7FFF              |   |              | 8     |                       | nV∙s   |

| Digital I/C       | )                            |                                               |   |              |       |                       |        |

| V <sub>IH</sub>   | Digital Input High Voltage   |                                               | • | 2.4          |       |                       | V      |

| V <sub>IL</sub>   | Digital Input Low Voltage    |                                               | • |              |       | 0.8                   | V      |

| V <sub>OH</sub>   | Digital Output High Voltage  | $I_{OUT} = -1mA$ , $D_{OUT}$ Only             | • | $V_{CC} - 1$ |       |                       | V      |

| V <sub>OL</sub>   | Digital Output Low Voltage   | $I_{OUT} = 1 \text{mA}, D_{OUT} \text{ Only}$ | • |              |       | 0.4                   | V      |

| I <sub>LEAK</sub> | Digital Input Leakage        | $V_{IN} = GND$ to $V_{CC}$                    | • |              |       | ±10                   | μA     |

| CIN               | Digital Input Capacitance    | (Note 6)                                      |   | 10           |       | 10                    | pF     |

| Switching         | ) Characteristics            |                                               |   |              |       |                       |        |

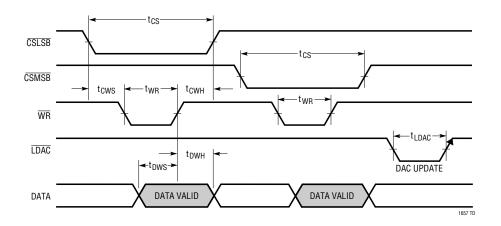

| t <sub>CS</sub>   | CS (MSB or LSB) Pulse Width  |                                               |   | 40           |       |                       | ns     |

| t <sub>WR</sub>   | WR Pulse Width               |                                               | • | 40           |       |                       | ns     |

| t <sub>CWS</sub>  | CS to WR Setup               |                                               |   | 0            |       |                       | ns     |

| t <sub>CWH</sub>  | CS to WR Hold                |                                               | • | 0            |       |                       | ns     |

| t <sub>DWS</sub>  | Data Valid to WR Setup       | V <sub>CC</sub> = 4.5V to 5.5V                | • | 40           | 15    |                       | ns     |

| t <sub>DWH</sub>  | Data Valid to WR Hold        | V <sub>CC</sub> = 4.5V to 5.5V                | • | 0            | -10   |                       | ns     |

| t <sub>LDAC</sub> | LDAC Pulse Width             |                                               | • | 40           |       |                       | ns     |

| t <sub>CLR</sub>  | CLR Pulse Width              |                                               | • | 40           |       |                       | ns     |

|                   | e Output (REFOUT)            |                                               |   |              |       | 1                     |        |

|                   | Reference Output Voltage     |                                               |   | 2.036        | 2.048 | 2.060                 | V      |

|                   | Reference Output             |                                               |   |              | 15    |                       | ppm/°C |

|                   | Temperature Coefficient      |                                               |   |              |       |                       |        |

|                   | Reference Line Regulation    | V <sub>CC</sub> = 4.5V to 5.5V                | • |              |       | ±1.5                  | mV/V   |

|                   | Reference Load Regulation    | I <sub>OUT</sub> = 100μA                      | • |              |       | 0.5                   | mV     |

|                   | Short-Circuit Current        | REFOUT Shorted to GND                         | • |              | 50    | 100                   | mA     |

| Reference         | e Input                      |                                               |   |              |       |                       |        |

|                   | REFHI, REFLO Input Range     | (Note 6) See Applications Information         |   |              |       |                       |        |

|                   |                              | X1/X2 Tie to V <sub>OUT</sub>                 | • | 0            |       | V <sub>CC</sub> – 1.5 | V      |

|                   |                              | X1/X2 Tie to GND                              | • | 0            |       | V <sub>CC</sub> /2    |        |

|                   | REFHI Input Resistance       |                                               |   | 16           | 25    |                       | kΩ     |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** External reference REFHI = 2.2V.

Note 3: Nonlinearity is defined from code 128 to code 65535 (full scale). See Applications Information.

Note 4: Digital inputs at OV or V<sub>CC</sub>.

Note 5: DAC switched between all 1s and code 400.

Note 6: Guaranteed by design. Not subject to test.

## PIN FUNCTIONS

**WR** (Pin 1): Write Input (Active Low). Used with <u>CSMSB</u> and/or <u>CSLSB</u> to control the input registers. While WR and <u>CSMSB</u> and/or <u>CSLSB</u> are held low, data writes into the input register.

**CSLSB** (Pin 2): Chip Select Least Significant Byte (Active Low). Used with WR to control the LSB 8-bit input registers. While WR and CSLSB are held low, the LSB byte writes into the LSB input register. Can be connected to CSMSB for simultaneous loading of both sets of input latches on a 16-bit bus.

**CSMSB (Pin 3):** Chip Select Most Significant Byte (Active Low). Used with WR to control the MSB 8-bit input registers. While WR and CSMSB are held low, the MSB byte writes into the MSB input register. Can be connected to CSLSB for simultaneous loading of both sets of input latches on a 16-bit bus.

**D0 to D7 (Pins 4 to 11):** Input data for the Least Significant Byte. Written into LSB input register when  $\overline{WR} = 0$  and  $\overline{CSLSB} = 0$ .

**D8 to D15 (Pins 12 to 19):** Input data for the Most Significant Byte. Written into MSB input register when  $\overline{WR} = 0$  and  $\overline{CSMSB} = 0$ .

#### GND (Pin 20): Ground.

**REFLO (Pin 21):** Lower input terminal of the DAC's internal resistor ladder. Typically connected to Analog Ground. An input code of  $(0000)_H$  will connect the positive input of

the output buffer to this end of the ladder. Can be used to offset the zero scale above ground.

**REFHI (Pin 22):** Upper input terminal of the DAC's internal resistor ladder. Typically connected to REFOUT. An input code of (FFFF)<sub>H</sub> will connect the positive input of the output buffer to 1LSB below this voltage.

**REFOUT (Pin 23):** Output of the internal 2.048V reference. Typically connected to REFHI to drive internal DAC resistor ladder.

**V<sub>CC</sub> (Pin 24):** Positive Power Supply Input.  $4.5V \le V_{CC} \le 5.5V$ . Requires a bypass capacitor to ground.

Vout (Pin 25): Buffered DAC Output.

**X1/X2 (Pin 26):** Gain Setting Resistor Pin. Connect to GND for G = 2 or to  $V_{OUT}$  for G = 1. This pin should always be tied to a low impedance source, such as ground or  $V_{OUT}$ , to ensure stability of the output buffer when driving capacitive loads.

**CLR (Pin 27):** Clear Input (Asynchronous Active Low). A low on this pin asynchronously resets all input and DAC registers to 0s.

**LDAC** (Pin 28): Load DAC (Asynchronous Active Low). Used to asynchronously transfer the contents of the input registers to the DAC register which updates the output voltage. If held low, the DAC register loads data from the input registers which will immediately update V<sub>OUT</sub>.

## DIGITAL INTERFACE TRUTH TABLE

| CLR | CSMSB | CSLSB | WR | LDAC | FUNCTION                                                  |  |

|-----|-------|-------|----|------|-----------------------------------------------------------|--|

| L   | Х     | Х     | Х  | Х    | Clears input and DAC registers to zero                    |  |

| Н   | Х     | Х     | Х  | L    | Loads DAC register with contents of input registers       |  |

| Н   | Х     | Х     | Х  | Н    | Freezes contents of DAC register                          |  |

| Н   | L     | Н     | L  | Х    | Writes MSB byte into MSB input register                   |  |

| Н   | Н     | L     | L  | Х    | Writes LSB byte into LSB input register                   |  |

| Н   | L     | L     | L  | Х    | Writes MSB and LSB bytes into MSB and LSB input registers |  |

| Н   | Х     | Х     | Н  | Х    | Inhibits write to MSB and LSB input registers             |  |

| Н   | Н     | Х     | Х  | Х    | Inhibits write to MSB input register                      |  |

| Н   | Х     | Н     | Х  | Х    | Inhibits write to LSB input register                      |  |

| Н   | L     | L     | L  | L    | Data bus flows directly through input and DAC registers   |  |

## TIMING DIAGRAM

## DEFINITIONS

**Resolution (n):** Resolution is defined as the number of digital input bits (n). It defines the number of DAC output states  $(2^n)$  that divide the full-scale range. Resolution does not imply linearity.

Full-Scale Voltage ( $V_{FS}$ ): This is the output of the DAC when all bits are set to 1.

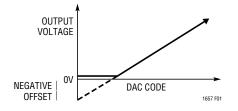

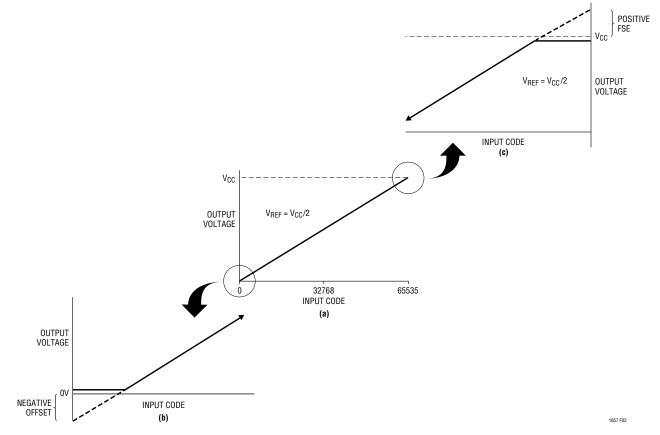

**Voltage Offset Error (V**<sub>OS</sub>): The theoretical voltage at the output when the DAC is loaded with all zeros. The output amplifier can have a true negative offset, but because the part is operated from a single supply, the output cannot go below zero. If the offset is negative, the output will remain near OV resulting in the transfer curve shown in Figure 1.

Figure 1. Effect of Negative Offset

The offset of the part is measured at the code that corresponds to the maximum offset specification:

$V_{OS} = V_{OUT} - [(Code)(V_{FS})/(2^n - 1)]$

**Least Significant Bit (LSB):** One LSB is the ideal voltage difference between two successive codes.

$LSB = (V_{FS} - V_{OS})/(2^n - 1) = (V_{FS} - V_{OS})/65535$

Nominal LSBs:

LTC1657 LSB = 4.096V/65535 = 62.5µV

#### DAC Transfer Characteristic:

$$V_{OUT} = G \bullet \left(\frac{\text{REFHI} - \text{REFLO}}{65536}\right) (\text{CODE}) + \text{REFLO}$$

$\label{eq:G} \begin{array}{l} \mathsf{G} = 1 \mbox{ for X1/X2 connected to } V_{OUT} \\ \mathsf{G} = 2 \mbox{ for X1/X2 connected to } \mathsf{GND} \\ \mathsf{CODE} = \mbox{ Decimal equivalent of digital input} \\ (0 \leq \mbox{ CODE} \leq 65535) \end{array}$

**Zero-Scale Error (ZSE):** The output voltage when the DAC is loaded with all zeros. Since this is a single supply part this value cannot be less than OV.

**Integral Nonlinearity (INL):** End-point INL is the maximum deviation from a straight line passing through the end points of the DAC transfer curve. Because the part operates from a single supply and the output cannot go below zero, the linearity is measured between full scale and the code corresponding to the maximum offset specification. The INL error at a given input code is calculated as follows:

INL (In LSBs) =  $[V_{OUT} - V_{OS} - (V_{FS} - V_{OS}) (code/65535)]$

$V_{OUT}$  = The output voltage of the DAC measured at the given input code

**Differential Nonlinearity (DNL):** DNL is the difference between the measured change and the ideal one LSB change between any two adjacent codes. The DNL error between any two codes is calculated as follows:

$$DNL = (\Delta V_{OUT} - LSB)/LSB$$

$\Delta V_{OUT}$  = The measured voltage difference between two adjacent codes

**Digital Feedthrough:** The glitch that appears at the analog output caused by AC coupling from the digital inputs when they change state. The area of the glitch is specified in  $nV \bullet s$ .

## OPERATION

#### Parallel Interface

The data on the input of the DAC is written into the DAC's input registers when Chip Select (CSLSB and/or CSMSB) and WR are at a logic low. The data that is written into the input registers will depend on which of the Chip Selects are at a logic low (see Digital Interface Truth Table). If WR and CSLSB are both low and CSMSB is high, then only data on the eight LSBs (D0 to D7) is written into the input registers. Similarly, if WR and CSMSB are both low and CSMSB is high, then only data on the eight MSBs (D8 to D15) is written into the input registers. Data is written into the input registers. Data Bits (D0 to D7) and the Most Significant Bits (D8 to D15) at the same time if WR, CSLSB and CSMSB are low. If WR is high or both CSMSB and CSLSB are high, then no data is written into the input registers.

Once data is written into the input registers, it can be written into the DAC register. This will update the analog voltage output of the DAC. The DAC register is written by a logic low on LDAC. The data in the DAC register will be held when LDAC is high.

When  $\overline{WR}$ ,  $\overline{CSLSB}$ ,  $\overline{CSMSB}$  and  $\overline{LDAC}$  are all low, the registers are transparent and data on pins D0 to D15 flows directly into the DAC register.

For an 8-bit data bus connection, tie the MSB byte data pins to their corresponding LSB byte pins (D15 to D7, D14 to D6, etc).

#### Power-On Reset

The LTC1657 has an internal power-on reset that resets all internal registers to 0's on power-up (equivalent to the  $\overline{\text{CLR}}$  pin function).

#### Reference

The LTC1657 includes an internal 2.048V reference, giving the LTC1657 a full-scale range of 4.096V in the gainof-2 configuration. The onboard reference in the LTC1657 is not internally connected to the DAC's reference resistor string but is provided on an adjacent pin for flexibility. Because the internal reference is not internally connected to the DAC resistor ladder, an external reference can be used or the resistor ladder can be driven by an external source in multiplying applications. The external reference or source must be capable of driving the 18k (minimum) DAC ladder resistance.

Internal reference output noise can be reduced with a bypass capacitor to ground. (Note: The reference does not require a bypass capacitor to ground for nominal operation.) When bypassing the reference, a small value resistor in series with the capacitor is recommended to help reduce peaking on the output. A  $10\Omega$  resistor in series with a  $4.7\mu$ F capacitor is optimum for reducing reference generated noise.

#### **DAC Resistor Ladder**

The high and low end of the DAC ladder resistor string (REFHI and REFLO, respectively) are not connected internally on this part. Typically, REFHI will be connected to REFOUT and REFLO will be connected to GND. X1/X2 connected to GND will give the LTC1657 a full-scale output swing of 4.096V.

Either of these pins can be driven up to  $V_{CC} - 1.5V$  when using the buffer in the gain-of-1 configuration. The resistor string pins can be driven to  $V_{CC}/2$  when the buffer is in the gain of 2 configuration. The resistance between these two pins is typically 30k (15k min).

#### Voltage Output

The output buffer for the LTC1657 can be configured for two different gain settings. By tying the X1/X2 pin to GND, the gain is set to 2. By tying the X1/X2 pin to  $V_{OUT}$ , the gain is set to unity.

The LTC1657 rail-to-rail buffered output can source or sink 5mA over the entire operating temperature range to within 300mV of the positive supply voltage or ground. The output stage is equipped with a deglitcher that results in a midscale glitch impulse of  $8nV \cdot s$ . The output swings to within a few millivolts of either supply rail when unloaded and has an equivalent output resistance of  $40\Omega$  when driving a load to the rails.

## **APPLICATIONS INFORMATION**

#### **Rail-to-Rail Output Considerations**

In any rail-to-rail DAC, the output swing is limited to voltages within the supply range.

If the DAC offset is negative, the output for the lowest codes limits at OV as shown in Figure 1b.

Similarly, limiting can occur near full scale when the REF pin is tied to  $V_{CC}/2$ . If  $V_{REF} = V_{CC}/2$  and the DAC full-scale

error (FSE) is positive, the output for the highest codes limits at  $V_{CC}$  as shown in Figure 1c. No full-scale limiting can occur if  $V_{REF}$  is less than ( $V_{CC} - FSE$ )/2.

Offset and linearity are defined and tested over the region of the DAC transfer function where no output limiting can occur.

Figure 2. Effects of Rail-to-Rail Operation On a DAC Transfer Curve. (a) Overall Transfer Function (b) Effect of Negative Offset for Codes Near Zero Scale (c) Effect of Positive Full-Scale Error for Input Codes Near Full Scale When  $V_{REF} = V_{CC}/2$

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                      | COMMENTS                                                                    |

|-------------|------------------------------------------------------------------|-----------------------------------------------------------------------------|

| LTC1446(L)  | Dual 12-Bit V <sub>OUT</sub> DACs in SO-8 Package                | $V_{CC} = 5V (3V), V_{OUT} = 0V \text{ to } 4.095V (0V \text{ to } 2.5V)$   |

| LTC1450(L)  | Single 12-Bit V <sub>OUT</sub> DACs with Parallel Interface      | V <sub>CC</sub> = 5V (3V), V <sub>OUT</sub> = 0V to 4.095V (0V to 2.5V)     |

| LTC1458(L)  | Quad 12-Bit Rail-to-Rail Output DACs with Added Functionality    | V <sub>CC</sub> = 5V (3V), V <sub>OUT</sub> = 0V to 4.095V (0V to 2.5V)     |

| LTC1650     | Single 16-Bit V <sub>OUT</sub> Industrial DAC in 16-Pin SO       | $V_{CC} = \pm 5V$ , Low Power, Deglitched, 4-Quadrant Multiplying $V_{OUT}$ |

| LTC1655(L)  | Single 16-Bit V <sub>OUT</sub> DAC with Serial Interface in SO-8 | $V_{CC}$ = 5V (3V), Low Power, Deglitched, $V_{OUT}$ = 0V to 4.096V         |