# Low Power EIA485 Transceiver with Carrier Detect and Receiver Fail-Safe

September 1998

### **FEATURES**

- No Damage or Latchup to ±15kV (Human Body Model), IEC1000-4-2 Level 4 (±8kV) Contact and Level 3 (±8kV) Air Discharge

- Active Low Carrier Detect Output

- Guaranteed High Receiver Output State for Floating, Shorted or Terminated Inputs with No Signal Present

- Drives Low Cost Residential Telephone Wires

- Low Power: I<sub>CC</sub> = 700µA Max with Driver Disabled

- Icc = 900µA Max in Driver Mode Without Load

- 20µA Max Quiescent Current in Shutdown Mode

- Single 5V Supply

- -7V to 12V Common Mode Range Permits ±7V Ground Difference Between Devices on the Data Line

- Maximum Data Rate of 4Mbps

- Power Up/Down Glitch-Free Driver Outputs

- Up to 32 Transceivers on the Bus

- Available in 8-Lead MSOP, PDIP and SO Packages

### **APPLICATIONS**

- Battery-Powered EIA485/EIA422 Applications

- Low Power EIA485/EIA422 Transceiver

- Level Translator

17, LTC and LT are registered trademarks of Linear Technology Corporation.

### DESCRIPTION

The LTC®1482 is a low power EIA485 compatible transceiver that offers an active low carrier detect output. The open-drain carrier detect pin allows several transceivers to share the same carrier detect line and can be used to detect the insertion or removal of a driven EIA485/EIA422 cable.

Enhanced ESD protection allows the LTC1482 to withstand  $\pm 15$ kV (human body model), IEC-1000-4-2 level 4 ( $\pm 8$ kV) contact and level 3 ( $\pm 8$ kV) air discharge ESD without latchup or damage.

The LTC1482 receiver stays alive at all times except in shutdown. The supply current is a maximum of  $700\mu A$  and  $900\mu A$  when the driver is disabled and enabled respectively. In shutdown, the quiescent current of the LTC1482 drops to a maximum of  $20\mu A$ .

When the driver is disabled or the LTC1482 is in shutdown, the driver outputs are three-stated and remain in a high impedance state over the EIA485 common mode range.

Excessive power dissipation caused by bus contention or faults is prevented by a thermal shutdown circuit, which forces the driver outputs into a high impedance state.

The LTC1482 is fully specified over the commercial and industrial temperature ranges and is available in 8-lead MSOP, PDIP and SO packages.

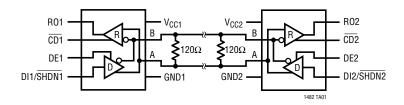

### TYPICAL APPLICATION

#### **EIA485 Interface**

### **ABSOLUTE MAXIMUM RATINGS**

| . 6.5V |

|--------|

| 0.3V)  |

| to 8V  |

| 0.3V)  |

| to 10V |

| to 14V |

|        |

| Junction Temperature                | 125°C                                  |

|-------------------------------------|----------------------------------------|

| Operating Temperature Range         |                                        |

| LTC1482C                            | $0^{\circ}C \le T_A \le 70^{\circ}C$   |

| LTC1482I                            | $-40^{\circ}C \le T_A \le 85^{\circ}C$ |

| Storage Temperature Range           | 65°C to 150°C                          |

| Lead Temperature (Soldering, 10 sec | )300°C                                 |

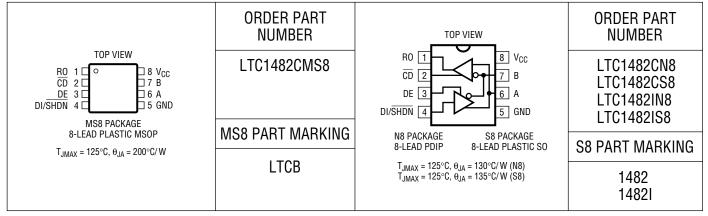

### PACKAGE/ORDER INFORMATION

Receiver Output Voltage ...... -0.3V to  $(V_{CC} + 0.3V)$

Consult factory for Military grade parts.

### **ELECTRICAL CHARACTERISTICS** $v_{CC} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL              | PARAMETER                                                                                    | CONDITIONS                                                                                                           |     | MIN             | TYP | MAX             | UNITS       |

|---------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|-----------------|-------------|

| $V_{\rm OD1}$       | Differential Driver Output Voltage (Unloaded)                                                | I <sub>OUT</sub> = 0                                                                                                 | •   |                 |     | V <sub>CC</sub> | V           |

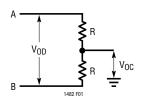

| V <sub>OD2</sub>    | Differential Driver Output Voltage (with Load)                                               | R = $50\Omega$ (EIA422)<br>R = $27\Omega$ (EIA485) Figure 1<br>R = $22\Omega$ , Figure 1                             | • • | 2<br>1.5<br>1.5 |     | 5<br>5          | V<br>V<br>V |

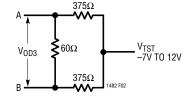

| V <sub>OD3</sub>    | Differential Driver Output Voltage (with Common Mode)                                        | $V_{TST} = -7V$ to 12V, Figure 2                                                                                     | •   | 1.5             |     | 5               | V           |

| $\Delta V_{0D}$     | Change in Magnitude of Driver Differential<br>Output Voltage for Complementary Output States | $R = 22\Omega$ , $27\Omega$ or $R = 50\Omega$ , Figure 1 $V_{TST} = -7V$ to 12V, Figure 2                            | •   |                 |     | 0.2             | V           |

| $V_{OC}$            | Driver Common Mode Output Voltage                                                            | $R = 22\Omega$ , $27\Omega$ or $R = 50\Omega$ , Figure 1                                                             | •   |                 |     | 3               | V           |

| ΔIV <sub>OC</sub> I | Change in Magnitude of Driver Common Mode<br>Output Voltage for Complementary Output States  | $R$ = 22 $\Omega$ , 27 $\Omega$ or R = 50 $\Omega$ , Figure 1                                                        | •   |                 |     | 0.2             | V           |

| $V_{IH}$            | Input High Voltage                                                                           | DE, DI/SHDN                                                                                                          | •   | 2               |     |                 | V           |

| $V_{IL}$            | Input Low Voltage                                                                            | DE, DI/SHDN                                                                                                          | •   |                 |     | 0.8             | V           |

| I <sub>IN1</sub>    | Input Current                                                                                | DE, DI/SHDN                                                                                                          | •   |                 |     | ±2              | μА          |

| I <sub>IN2</sub>    | Input Current (A, B) with Driver Disabled                                                    | DE = 0, V <sub>CC</sub> = 0 or 5V, V <sub>IN</sub> = 12V<br>DE = 0, V <sub>CC</sub> = 0 or 5V, V <sub>IN</sub> = -7V | •   |                 |     | 1.0<br>-0.8     | mA<br>mA    |

| V <sub>THRO</sub>   | Differential Input Threshold Voltage for Receiver                                            | $-7V \le V_{CM} \le 12V$ , DE = 0                                                                                    | •   | -0.20           |     | -0.015          | V           |

### **ELECTRICAL CHARACTERISTICS** $v_{\text{CC}} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL               | PARAMETER                                                        | CONDITIONS                                                                           |   | MIN   | TYP        | MAX        | UNITS    |

|----------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------|---|-------|------------|------------|----------|

| V <sub>THCD</sub>    | Differential Input Threshold Voltage for CD                      | $-7V \le V_{CM} \le 12V, DE = 0$                                                     | • | -0.20 |            | 0.20       | V        |

| $\Delta V_{TH}$      | Receiver Input Hysteresis                                        | V <sub>CM</sub> = 0V, DE = 0                                                         |   |       | ±30        |            | mV       |

| $\overline{V_{OH}}$  | CD Output High Voltage                                           | $I_{OUT} = -10\mu A$ , $(V_A - V_B) = 0V$                                            | • | 3.4   |            |            | V        |

|                      | RO Output High Voltage                                           | $I_{OUT} = -4mA, (V_A - V_B) = 200mV$                                                | • | 3.5   |            |            | V        |

| $V_{0L}$             | RO and CD Output Low Voltage                                     | $I_{OUT} = 4mA, (V_A - V_B) = -200mV$                                                | • |       |            | 0.4        | V        |

| I <sub>OZR</sub>     | Three-State (High Impedance) Receiver Output Current in Shutdown | $V_{CC} = Max$ , $0.4V \le V_{OUT} \le 2.4V$<br>DI/SHDN = 0, DE = 0                  | • |       |            | ±1         | μА       |

| R <sub>IN</sub>      | Receiver Input Resistance                                        | $-7V \le V_{CM} \le 12V$                                                             | • | 12    | 22         |            | kΩ       |

| I <sub>CC</sub>      | Supply Current                                                   | No Load, Driver Enabled (DE = V <sub>CC</sub> )<br>No Load, Driver Disabled (DE = 0) | • |       | 580<br>430 | 900<br>700 | μA<br>μA |

| I <sub>SHDN</sub>    | Supply Current in Shutdown Mode                                  | DE = 0, DI = 0                                                                       | • |       | 10         | 20         | μΑ       |

| I <sub>OSD1</sub>    | Driver Short-Circuit Current, V <sub>OUT</sub> = High (Note 4)   | $-7V \le V_{OUT} \le 10V$                                                            |   | 35    |            | 250        | mA       |

| I <sub>OSD2</sub>    | Driver Short-Circuit Current, V <sub>OUT</sub> = Low (Note 4)    | $-7V \le V_{OUT} \le 10V$                                                            |   | 35    |            | 250        | mA       |

| I <sub>OS</sub>      | RO and CD Short-Circuit Current                                  | $0V \le V_{OUT} \le V_{CC}$                                                          | • | 7     |            | 85         | mA       |

| I <sub>PULL-UP</sub> | CD Pull-Up Current                                               | $\overline{CD} = 0V$                                                                 | • | 15    | 30         | 60         | μА       |

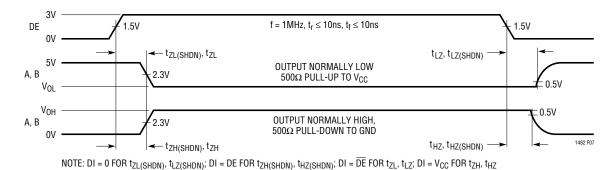

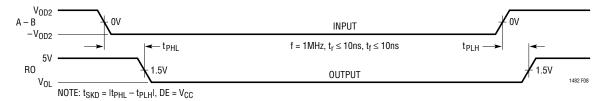

## **SWITCHING CHARACTERISTICS** $V_{CC} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL                | PARAMETER                                                         | CONDITIONS                                                                                |   | MIN | TYP  | MAX  | UNITS |

|-----------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---|-----|------|------|-------|

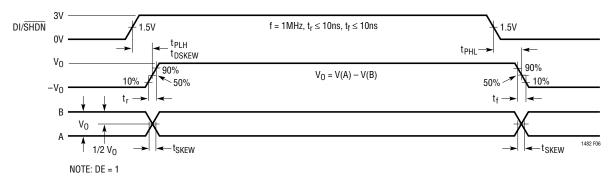

| t <sub>PLH</sub>      | Driver Input to Output                                            | $R_{DIFF} = 54\Omega, C_{L1} = C_{L2} = 100pF$                                            | • | 10  | 25   | 60   | ns    |

| t <sub>PHL</sub>      | Driver Input to Output                                            | (Figures 4, 6)                                                                            | • | 10  | 25   | 60   | ns    |

| t <sub>SKEW</sub>     | Driver Output to Output                                           |                                                                                           | • |     | 5    | 10   | ns    |

| $t_r, t_f$            | Driver Rise or Fall Time                                          |                                                                                           | • | 3   | 15   | 40   | ns    |

| t <sub>ZH</sub>       | Driver Enable to Output High                                      | C <sub>L</sub> = 100pF (Figures 5, 7) S2 Closed                                           | • |     | 40   | 70   | ns    |

| t <sub>ZL</sub>       | Driver Enable to Output Low                                       | C <sub>L</sub> = 100pF (Figures 5, 7) S1 Closed                                           | • |     | 40   | 100  | ns    |

| t <sub>LZ</sub>       | Driver Disable Time from Low                                      | C <sub>L</sub> = 15pF (Figures 5, 7) S1 Closed                                            | • |     | 40   | 70   | ns    |

| t <sub>HZ</sub>       | Driver Disable Time from High                                     | C <sub>L</sub> = 15pF (Figures 5, 7) S2 Closed                                            | • |     | 40   | 70   | ns    |

| t <sub>ZH(SHDN)</sub> | Driver Enable from Shutdown to Output High (Note 5)               | C <sub>L</sub> = 100pF (Figures 5, 7) S2 Closed                                           | • |     | 40   | 100  | ns    |

| t <sub>ZL(SHDN)</sub> | Driver Enable from Shutdown to Output Low                         | C <sub>L</sub> = 100pF (Figures 5, 7) S1 Closed                                           | • |     | 40   | 100  | ns    |

| t <sub>HZ(SHDN)</sub> | Driver Disable on Shutdown from Output High                       | C <sub>L</sub> = 15pF (Figures 5, 7) S2 Closed                                            | • |     | 40   | 100  | ns    |

| t <sub>LZ(SHDN)</sub> | Driver Disable on Shutdown from Output Low                        | C <sub>L</sub> = 15pF (Figures 5, 7) S1 Closed                                            | • |     | 40   | 100  | ns    |

| f <sub>MAX</sub>      | Maximum Data Rate (Note 6)                                        |                                                                                           | • | 4   | 5    |      | Mbps  |

| t <sub>PLH</sub>      | Receiver Input to Output (Note 7)                                 | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100$ pF, (Figures 4, 8)                        | • | 30  | 140  | 200  | ns    |

| t <sub>PHL</sub>      | Receiver Input to Output                                          | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ , (Figures 4, 8)                        | • | 30  | 140  | 200  | ns    |

| t <sub>SKD</sub>      | It <sub>PLH</sub> – t <sub>PHL</sub> I Differential Receiver Skew | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ , (Figures 4, 8)                        |   |     | 5    |      | ns    |

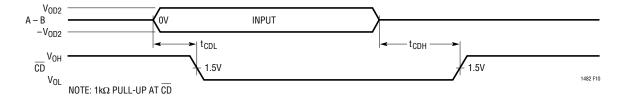

| t <sub>CDH</sub>      | Receiver Input to CD Output High (Note 7)                         | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ , (Figures 4, 10) DI/SHDN = $V_{CC}$    | • |     | 2900 | 5000 | ns    |

| t <sub>CDL</sub>      | Receiver Input to CD Output Low (Note 7)                          | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100$ pF,<br>(Figures 4, 10) DI/SHDN = $V_{CC}$ | • |     | 150  | 300  | ns    |

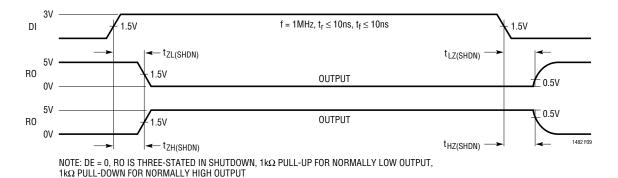

### **SWITCHING CHARACTERISTICS** $V_{CC} = 5V \pm 5\%$ (Notes 2 and 3) unless otherwise noted.

| SYMBOL                 | PARAMETER                                                         | CONDITIONS                                                                                                           |   | MIN | TYP  | MAX  | UNITS |

|------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---|-----|------|------|-------|

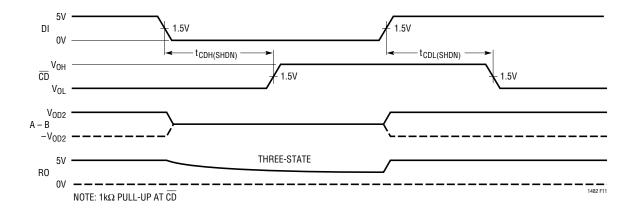

| t <sub>CDH(SHDN)</sub> | Receiver Input to $\overline{\text{CD}}$ Output High at Shutdown  | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100pF$ , (Figures 4, 11) DI/SHDN = DE                                     | • |     | 2600 | 5000 | ns    |

| t <sub>CDL(SHDN)</sub> | Receiver Input to $\overline{\text{CD}}$ Output Low from Shutdown | $R_{DIFF} = 54\Omega$ , $C_{L1} = C_{L2} = 100$ pF,<br>(Figures 4, 11) DI/SHDN = DE                                  | • |     | 2600 | 5000 | ns    |

| t <sub>ZH(SHDN)</sub>  | Receiver Enable from Shutdown to Output High                      | $C_L$ = 15pF (Figures 3, 9) S2 Closed,<br>A = $750$ mV, B = $-750$ mV, DE = 0,<br>DI/SHDN = $\sqrt{s}$               | • |     | 30   | 600  | ns    |

| t <sub>ZL(SHDN)</sub>  | Receiver Enable from Shutdown to Output Low                       | $C_L = 15pF$ (Figures 3, 9) S1 Closed,<br>A = -750 mV, $B = 750 mV$ , $DE = 0$ ,<br>$DI/SHDN = \mathcal{L}$          | • |     | 2600 | 5000 | ns    |

| t <sub>HZ(SHDN)</sub>  | Receiver Disable from High on Shutdown                            | $C_L = 15pF$ (Figures 3, 9) S2 Closed,<br>A = 750mV, $B = -750mV$ , $DE = 0$ ,<br>$DI/\overline{SHDN} = 7$           | • |     | 200  | 600  | ns    |

| t <sub>LZ(SHDN)</sub>  | Receiver Disable from Low on Shutdown                             | $C_L = 15pF$ (Figures 3, 9) S1 Closed,<br>A = -750mV, $B = 750mV$ , $DE = 0$ ,<br>$DI/\overline{SHDN} = \sqrt[T]{L}$ | • |     | 200  | 600  | ns    |

The ● denotes specifications which apply over the full specified temperature range.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** All typicals are given for  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$ .

**Note 3:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified.

**Note 4:** For higher ambient temperatures, the part may enter thermal shutdown during short-circuit conditions.

**Note 5:** Both driver input and driver enable pins are pulled high simultaneously.

Note 6: Guaranteed by design.

Note 7: Measured with an external LTC1485 driver.

### PIN FUNCTIONS

**RO (Pin 1):** Receiver Output. If a carrier is present ( $\overline{CD}$  low) and the part is not in shutdown, RO is high if the receiver input differential voltage  $(A-B) \ge V_{THRO(MAX)}$  and low if  $(A-B) \le V_{THRO(MIN)}$ . RO is forced to high (fail-safe state) if a carrier is not present ( $\overline{CD} = 1$ ). In shutdown, RO is three-stated. If the driver is enabled, RO follows the logic level at the driver input.

$\overline{\text{CD}}$  (Pin 2): Open-Drain Carrier Detect Output. Provided that the part is not in shutdown, the  $\overline{\text{CD}}$  output is low if  $V_{\text{THCD}(\text{MIN})} \geq (A-B) \geq V_{\text{THCD}(\text{MAX})}$  and high if  $V_{\text{THCD}(\text{MIN})} < (A-B) < V_{\text{THCD}(\text{MAX})}$ . A weak internal pull-up removes the need for an external pull-up resistor if fast rise times are not important. Several LTC1482s can share the same  $\overline{\text{CD}}$  line.  $\overline{\text{CD}} = 1$  forces RO to the high fail-safe state. In shutdown,  $\overline{\text{CD}}$  is three-stated. This pin can be pulled above  $V_{\text{CC}}$  but should not be taken above 8V to avoid damage.

**DE (Pin 3):** Driver Enable Input. DE = 0 disables or threestates the driver outputs. DE = 1 enables the driver outputs with the high/low state of the outputs set by  $DI/\overline{SHDN}$ . **DI/SHDN (Pin 4):** Driver Input and Shutdown Input. It is used together with the DE pin to put the part in shutdown (DE = 0, DI/SHDN = 0) or to disable the driver while keeping the receiver alive (DE = 0, DI/SHDN = 1). When the driver is enabled (DE = 1), DI/SHDN = 0 forces the A output low and the B output high. DI/SHDN = 1 forces the A output high and the B output low.

GND (Pin 5): Ground.

**A (Pin 6):** Driver Output/Receiver Input. The input resistance is typically 22k when the driver is disabled (DE = 0). When the driver is enabled, the A output follows the logic level at the DI/ $\overline{SHDN}$  pin.

**B** (Pin 7): Driver Output/Receiver Input. The input resistance is typically 22k when the driver is disabled (DE = 0). When the driver is enabled, the B output is inverted from the logic level at the  $DI/\overline{SHDN}$  pin.

$V_{CC}$  (Pin 8): Positive Supply. 4.75V <  $V_{CC}$  < 5.25V. A 0.1μF bypass capacitor is recommended.

### **FUNCTION TABLES**

Driver Enabled (DE = 1)

|         | , ,    |          |    |    |

|---------|--------|----------|----|----|

| DI/SHDN | A      | В        | R0 | CD |

| 0       | 0      | 1        | 0  | 0  |

| 1       | 1      | 0        | 1  | 0  |

| Х       | A Shor | ted to B | 1  | 1  |

**Note 1:** DE = 0, DI/ $\overline{SHDN}$  = 0 puts the part in I<sub>CC</sub> shutdown and the supply current drawn by the V<sub>CC</sub> pin drops to 20µA max. The receiver is always alive except in shutdown.

**Note 2:** The table is valid regardless of the presence of an external termination resistor.

**Note 3:** Although the RO and the driver outputs are three-stated, the A and B pins each present a  $22k\Omega$  receiver input resistance to ground.

#### Driver Disabled (DE = 0, Notes 1, 2)

| DI/SHDN | A – B                                                                            | R0 | CD                   |

|---------|----------------------------------------------------------------------------------|----|----------------------|

| 0       | Z (Note 3)                                                                       | Z  | 1 (Internal Pull-Up) |

| 1       | $V_{THCD(MIN)} < (A - B) < V_{THCD(MAX)}$                                        | 1  | 1                    |

| 1       | A and B are Open                                                                 | 1  | 1                    |

| 1       | A and B are Shorted                                                              | 1  | 1                    |

| 1       | $V_{THCD(MIN)} \ge (A - B) \ge V_{THCD(MAX)}$<br>and $(A - B) \le V_{THRO(MIN)}$ | 0  | 0                    |

| 1       | $V_{THCD(MIN)} \ge (A - B) \ge V_{THCD(MAX)}$<br>and $(A - B) \ge V_{THRO(MAX)}$ | 1  | 0                    |

Z = High Impedance

### **TEST CIRCUITS**

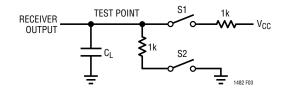

Figure 1. Driver DC Test Load #1

Figure 2. Driver DC Test Load #2

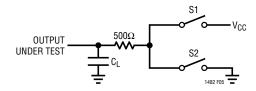

Figure 3. Receiver Timing Test Load

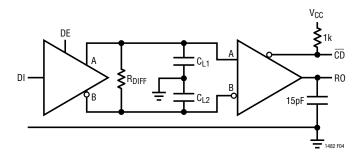

Figure 4. Driver/Receiver Timing Test Load

Figure 5. Driver Timing Test Load #2

### **SWITCHING TIME WAVEFORMS**

Figure 6. Driver Propagation Delays

Figure 7. Driver Enable and Disable Timing

Figure 8. Receiver Propagation Delays

Figure 9. Receiver Enable and Shutdown Timing

### **SWITCHING TIME WAVEFORMS**

Figure 10. Carrier Detect Timing

Figure 11. Shutdown Carrier Detect Timing

### APPLICATIONS INFORMATION

#### **Carrier Detect Operation**

The carrier detect or CD pin is an open-drain output with a weak internal pull-up (30µA typical). This allows several LTC1482s to share the same carrier detect line. The internal pull-up has a series diode, permitting users to tie the  $\overline{\text{CD}}$  output to a voltage higher than  $V_{CC}$  (8V max). When driving low, the  $\overline{\text{CD}}$  output can sink up to 4mA while maintaining the output below a TTL  $V_{OL}$  of 0.4V. An external pull-up resistor is recommended if fast rise times are important.

The LTC1482 defines the presence of a carrier as  $V_{THCD(MIN)} \ge (A-B) \ge V_{THCD(MAX)}$ .  $\overline{CD}$  pulls low when a carrier is present. When the carrier is absent, the weak internal pull-up pulls  $\overline{CD}$  high. For slow moving input signals (below about 32kHz for signals conforming to EIA485 specifications), the  $\overline{CD}$  output will go high when the (A-B) signal is within the  $V_{THCD(MIN)}$  to  $V_{THCD(MAX)}$  range. For faster input signals, the  $\overline{CD}$  output does not glitch high when the (A-B) signal is traversing the transition region. This is achieved through internal delays in the  $\overline{CD}$  signal path. It takes  $t_{CDH}$  ( $\le 5\mu s$ ) for  $\overline{CD}$  to go high after the carrier signal is removed. There are no additional built-in delays for  $\overline{CD}$  going low so that  $t_{CDL}$  is only 300ns max.

When the LTC1482 is not in shutdown mode,  $\overline{CD} = 1$  always forces the receiver output (RO) high. If the driver is enabled,  $\overline{CD}$  goes high when A is shorted to B. If the driver is disabled,  $\overline{CD}$  is guaranteed to go high when:

- a) A is shorted to B.

- b) A and B are open (with or without termination) or

- c)  $V_{THCD}$  min  $\leq A B \leq V_{THCD}$  max

In shutdown mode, RO is three-stated and  $\overline{CD}$  is taken high by the weak internal pull-up. On exiting shutdown, it takes longer ( $t_{CDL(SHDN)} = 5\mu s$  max) for  $\overline{CD}$  to pull low when a carrier is present.

When  $V_{CC}$  is applied, some time is needed for  $\overline{CD}$  and RO to become valid. The time needed depends on the capacitance at the  $\overline{CD}$  pin, the  $V_{CC}$  rise time and the loads connected to the A and B pins. For a load capacitance of 15pF and a 1 $\mu$ s  $V_{CC}$  rise time, a wait time of 10 $\mu$ s is recommended.

#### **Receiver Output and Fail-Safe**

If CD is low, the receiver output, RO, responds to the input differential voltage and is guaranteed (by testing) to go high if  $(A-B) \ge V_{THRO(MAX)}$  and low if  $(A-B) \le V_{THCD(MIN)}$ .

Some data encoding schemes require that the output of the receiver maintain a known state (usually logic 1) when data transmission ends and all drivers on the line are forced into three-state. The carrier detect mechanism ensures that RO will be high regardless of whether the line is open, floating or shorted together, or whether the line is terminated or not. This removes external components required with earlier EIA485 devices for the case where the required known state is a logic 1. External components are needed if the required state is a logic 0.

Fail-safe operates over the -7V to 12V common mode range and fast common mode steps do not affect the receiver output.

Note that the  $\overline{\text{CD}}$  output only goes high after all the drivers are three-stated due to built-in delays ( $t_{\text{CDH}}$ ) in the  $\overline{\text{CD}}$  signal path (see Carrier Detect Operation). During the time interval (see Figure 11) beginning at driver three-state and ending at  $\overline{\text{CD}}$  going high, the receiver output stays at the last state just prior to the driver three-stating.

#### I<sub>CC</sub> Shutdown Mode

The supply current of the LTC<u>1482</u> is reduced to  $20\mu A$  max by taking both the DE and DI/SHDN pins low. In shutdown, all internal circuits are powered down <u>and</u> the driver and receiver outputs are three-stated. The <u>CD</u> output is taken high by the weak internal pull-up.

Logic within the LTC1482 prevents slow DE and DI/SHDN transitions from generating internal shutdown pulses by rejecting "shutdown pulses" of less than 50ns (typ) in duration. Without this logic, the driver outputs will glitch when three-stated momentarily.

The supply current does not drop below  $20\mu\text{A}$  immediately. DE and DI/SHDN must be low for a least 600ns simultaneously for I<sub>CC</sub> to drop to half its operating value (driver outputs unloaded) and for t<sub>CDH(SHDN)</sub> before dropping to the  $20\mu\text{A}$  level. Taking either DE or DI/SHDN high will wake the LTC1482 within  $5\mu\text{s}$ .

### APPLICATIONS INFORMATION

In some applications, the A and B lines are pulled to  $V_{CC}$  or GND through external resistors to force the line to a high or low state when all connected drivers are disabled. In shutdown, the supply current will be higher than  $10\mu A$  due to the additional current drawn through the external pullup and the 22k input resistance of the LTC1482.

#### **ESD Protection**

The ESD performance of the LTC1482 A and B pins is characterized to meet  $\pm 15$ kV using the Human Body Model (100pF, 1.5k $\Omega$ ), IEC-1000-4-2 Level 4 ( $\pm 8$ kV) contact mode and IEC-1000-4-2 Level 3 ( $\pm 8$ kV) air discharge mode. This means that external voltage suppressors are not required in many applications, when compared with parts that are only protected to  $\pm 2$ kV. Pins other than the A and B pins are protected to  $\pm 3$ kV typical per the Human Body Model.

When powered up, the LTC1482 does not latch up or sustain damage when the A and B pins are tested using any of the three conditions listed. The data during the ESD event may be corrupted, but after the event the LTC1482 continues to operate normally. The additional ESD protection at the A and B pins is important in applications where these pins are exposed to the external world via connections to sockets.

#### **Fault Protection**

When shorted to -7V or 10V at room temperature, the short-circuit current in the driver pins is limited by internal protection circuitry to 250mA. Over the industrial temperature range, the absolute maximum positive voltage at any driver pin should be limited to 10V to avoid damage to the part. At higher ambient temperatures, the rise in die temperature, due to the short-circuit current, may trip the thermal shutdown circuit. This circuit protects the part against prolonged shorts at the driver outputs. If a driver output is shorted to another output or to  $V_{CC}$ , the current will be limited to 250mA. If the die temperature rises above 150°C, the thermal shutdown circuit three-states the driver outputs to open the current path. When the die cools down to about 130°C, the driver outputs are taken out of three-state. If the short persists, the part will heat again and the cycle will repeat. This thermal oscillation occurs at about 10Hz and protects the part from excessive power dissipation. The average fault current drops as the driver cycles between active and three-state. When the short is removed, the part will return to normal operation.

When the driver is disabled, the receiver inputs can withstand the entire -7V to 12V EIA485 common mode range without damage.

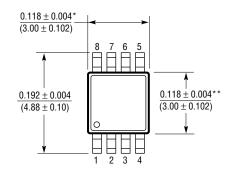

### PACKAGE DESCRIPTION

Dimensions in inches (millimeters), unless otherwise noted.

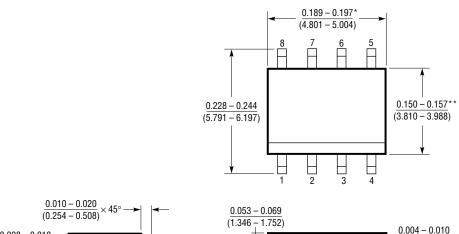

#### MS8 Package 8-Lead Plastic MSOP

(LTC DWG # 05-08-1660)

- \* DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

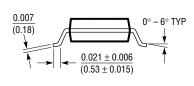

### PACKAGE DESCRIPTION

Dimensions in inches (millimeters), unless otherwise noted.

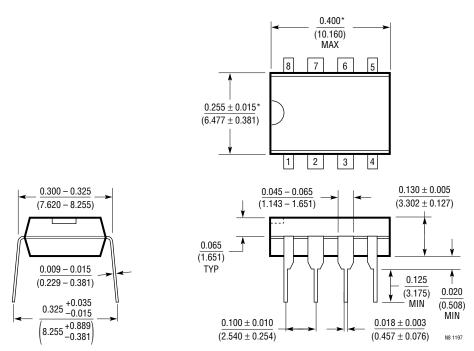

N8 Package 8-Lead PDIP (Narrow 0.300)

(LTC DWG # 05-08-1510)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

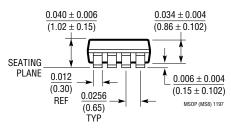

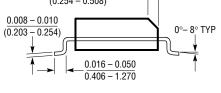

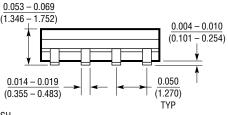

PACKAGE DESCRIPTION Dimensions in inches (millimeters), unless otherwise noted.

### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

<sup>\*</sup>DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

S08 0996

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                 | COMMENTS                                                                    |

|-------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| LTC485      | 5V Low Power EIA485 Interface Transceiver                                   | Low Power                                                                   |

| LTC1480     | 3.3V Ultralow Power EIA485 Transceiver with Shutdown                        | Lower Supply Voltage                                                        |

| LTC1481     | 5V Ultralow Power EIA485 Transceiver with Shutdown                          | Lowest Power                                                                |

| LTC1483     | 5V Ultralow Power EIA485 Low EMI Transceiver with Shutdown                  | Low EMI/Lowest Power                                                        |

| LTC1484     | 5V Low Power EIA485 Transceiver with Fail-Safe Receiver Output              | Low Power, High Output State When Inputs are Open,<br>Shorted or Terminated |

| LTC1485     | 5V Differential Bus Transceiver                                             | Highest Speed                                                               |

| LTC1487     | 5V Ultralow Power EIA485 with Low EMI, Shutdown and<br>High Input Impedance | Highest Input Impedance, Low EMI, Lowest Power                              |

| LTC1690     | 5V Differential Driver and Receiver Pair with Fail-Safe Receiver Output     | Low Power                                                                   |

<sup>\*</sup>DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE