No. 2326

# LM88PG99A

N Channel E/D MOS LSI EPROM-mountable 8-bit microcomputer for evaluating the LM8800 series microcomputers

#### 1. Overview

The LM88PG99A is an EPROM-mountable single-chip 8-bit microcomputer, and can be used to develop and evaluate programs for the LM8800 series microcomputers.

Evaluation using an application program for a target microcomputer

The LM88PG99A will be able to have the same functions as these of the LM8800 series microcomputers by mounting EPROM 2732 or 2764, which enables the evaluation of a user application product before the user program is masked in the ROM by the mask options.

#### Program development

The LM88PG99A can be used to execute, stop and correct programs by combining it with the program debugging unit (EVA-410C) and the target board (TB88PG).

#### 2. Characteristics

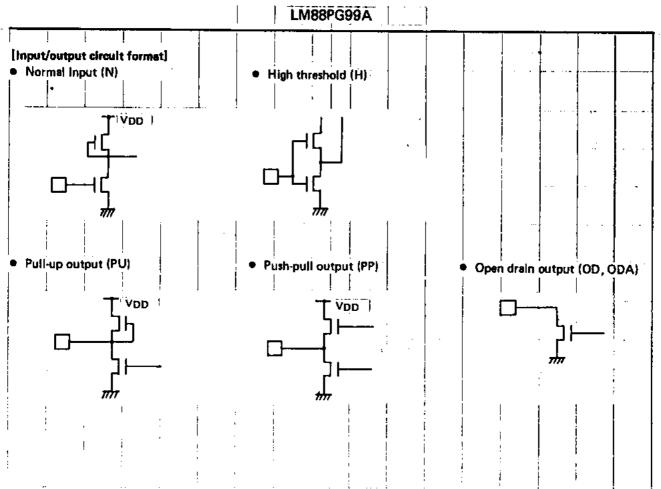

- (1) Evaluation capabilities for input/output option functions. Input/output option functions can be selected by using data in the program ROM (On the LM8854, LM8804 and LM8802, input/output options can be selected by mask options).

- (2) The mountable EPROMs are 2732, 2732A and 2764.

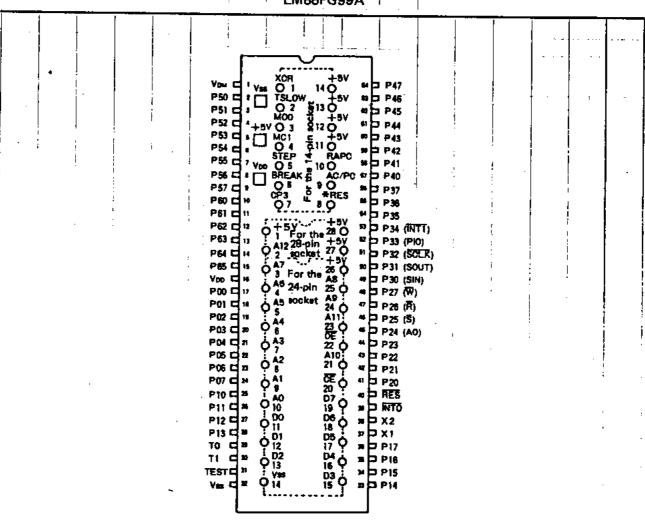

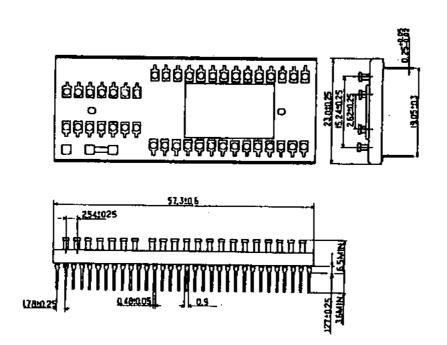

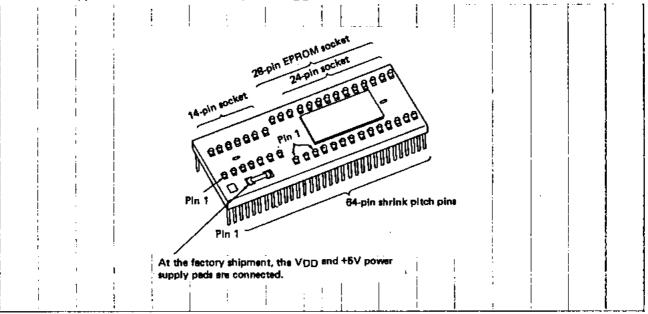

- (3) Shrink type 64-pin configuration compatible with the LM8854 pin configuration.

- (4) Memory capacity selectable

The memory capacity can be selected by setting external pins for evaluating the LM8854, LM8804 or LM8802 microcomputer. The program of 4K bytes or more can be evaluated.

(5) Program developing and evaluating functions

The LM88PG99A microcomputer allows programs to be executed and stopped if used together with the program debugging unit EVA-410C.

This microcomputer has the 28-pin socket on the package surface, which is used to mount the program EPROM. It also has the 14-pin socket used for controlling program execution. And the LM88PG99A microcomputer has the shrink type 84-pin configuration at the bottom, which is compatible with the LM8864 microcomputer. When evaluating the LM8804 and LM8802 microcomputers, use the pin conversion board (SK8804S) with the LM88PG99A microcomputer. With this board, the LM88PG99A microcomputer could have the shrink type 42-pin configuration which is compatible with the LM8804 and LM8802 microcomputers.

#### Notes on use

The following points should be taken into consideration when you use the LM88PG99A microcomputer. This microcomputer is designed for special use. In other words, the LM88PG99A is designed exclusively to develop and evaluate programs for the LM8800 series microcomputers.

- The LM88PG99A microcomputer has different operating conditions from those of any production chip

including a masked ROM. Especially, this microcomputer is adversely affected by high temperature and

excessive humidity.

- (2) The electric characteristics do not include the representative values and limit values of any production masked-ROM chip. For strict evaluation of an application where a production masked-ROM chip is used, use recommended constants for the electric characteristics of a production masked-ROM chip.

- (3) Since the LM88PG99A microcomputer has different internal system configuration pattern from that of a production masked-ROM chip, keep the following in mind: (a) Initial values of RAM at the moment the power is first supplied (b) Static noise figures.

The application circuit diagrams and circuit constants herein are included as an example and provide no guarantee for designing equipment to be mass-produced.

The information herein is believed to be accurate and reliable. However, no responsibility is assumed, by SANYO for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

These specifications are subject to change without notice.

| Pin name       | Number<br>of pins                                | 1/0               | Functions                                                                                                         | Remarks      |

|----------------|--------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------|--------------|

| VSS            | 1 1                                              |                   |                                                                                                                   |              |

| VDD            | i                                                | -                 | Power source for During the normal operation, the                                                                 |              |

|                |                                                  |                   | other than the RAM. power must be supplied to the VDM                                                             |              |

| VDM .          | 1                                                | _                 | Power source for pin. And when the signal level at the                                                            |              |

|                |                                                  |                   | RAM J RES terminal changes from "L" to                                                                            |              |

|                | 1                                                |                   | "H", the VDD voltage must be equal                                                                                |              |

|                |                                                  |                   | or greater than that of the VDM                                                                                   | †            |

| <u>v.</u>      | <del>  </del>                                    | 1.10              | terminal,                                                                                                         |              |

| X <sub>1</sub> | ¦                                                | 1,1/0             | For external oscillation circuit or external clock circuit.                                                       | (Note 2)     |

| X2<br>RES      | <del>                                     </del> | <u> </u>          | For the ceramic resonator oscillation circuit, (Note 1) Reset input (with Pull-up Tr)                             | Option       |

| TEST           | <del>                                     </del> | ,<br>,            | For testing the LSI inside (connected to Vss during the                                                           |              |

| , 201          | 1 1                                              | •                 | normal operation)                                                                                                 |              |

| TO             | 1                                                | <u> </u>          | For the test 0 signal input or zero cross detection signal                                                        | Option       |

|                |                                                  | •                 | input. Also for the external interrupt 1 signal input.                                                            | Cption       |

| T1             | 1                                                | i                 | For the test 1 signal input or counter signal input of                                                            | <u> </u>     |

|                |                                                  |                   | timer 0                                                                                                           | }            |

| INTO           | 1                                                | ı                 | For the external interrupt 0 signal input or test falg                                                            | <del> </del> |

|                |                                                  |                   | Input                                                                                                             | i            |

| P00 to P07     | 8                                                | 1/0               | Used as port 0 or as bi-directional data buses.                                                                   |              |

|                |                                                  | (N,PP)            | Goes to high impedance at the reset,                                                                              |              |

| P10 to P17     | 8                                                | 1/0               | Used as port 1,                                                                                                   | Ī            |

|                |                                                  | (H, ODA)          | Goes to high impedance at the reset. Large current port.                                                          |              |

| P20 to P27     | 8                                                | 1/0               | Used as port 2. Or P24 used as A0, P26 as S, P26 as R                                                             | Option       |

|                |                                                  | (H, N;            | and P27 as W. The output signal level at the reset can be                                                         | i            |

| 000 · 001      |                                                  | OD, PU).          | selected as the "H" or "L" by using the mask options.                                                             | <u> </u>     |

| P30 to P37     | 8                                                | I/O               | Used as port 3. Or P30 used as SIN (1), P31 as SOUT (0),                                                          | Option       |

|                |                                                  | (H, N,<br>OD, PU) | P32 as SCLK (I/O), P33 as PI0 (I/O) and P34 as TNT1.  The output signal level at the reset can be selected as the | <u> </u>     |

|                |                                                  | υ <u>υ</u> , ευτ  | "H" or "L" by using the mask options,                                                                             |              |

| P40 to P47     | 8                                                | I(H)              | Used as port 4                                                                                                    | <u> </u>     |

| P50 to P57     | 8                                                | O                 | Used as port 5                                                                                                    | Option       |

|                | ĺ                                                | (OD, PU)          | The output signal level at the reset can be selected as the                                                       |              |

|                | <u> </u>                                         |                   | "H" or "L" by using the mask options.                                                                             |              |

| P60 to P65     | 6                                                | O (OD)            | Used as port 6,                                                                                                   | Option       |

|                | (Total                                           |                   | The output signal level at the reset can be selected as the                                                       |              |

|                | 64)                                              |                   | "H" or "L" by using the mask options.                                                                             |              |

| XCR            | 1                                                | I(N)              | Used to select an oscillation circuit. (Note 2) The ceramic                                                       | Pull-down    |

|                |                                                  |                   | resonator oscillation circuit is selected when this input                                                         |              |

|                |                                                  |                   | circuit is left open-circuited.                                                                                   |              |

| TSLOW          | 1                                                | I(N)              | Used to select a divider circuit for a selected oscillation                                                       | Pull-down    |

|                | İ                                                |                   | circuit. When this circuit is left open-circuited, the 1/1                                                        | •            |

|                |                                                  |                   | divider circuit is selected. When the "H" level signal is                                                         | •            |

| MC0 to MC1     | 2                                                | I(N)              | Input to this circuit, the 1/2 divider circuit is selected.                                                       | Post 1       |

| STEP           | 2                                                | 1(N)              | Used to select the capacities of the RAM and ROM.  Used to specify the step and break functions for the           | Pull-down    |

| BREAK          | _ [                                              | , (14)            | program currently being executed.                                                                                 | FUII-QOWN    |

| CP3            | 1                                                | O(PU)             | For the internal system clock pulse output,                                                                       | Pull-up      |

| AC/PC          | 2                                                | 1(N)              | Used to select the A0 to A12 output data. Normally left                                                           | Pull-down    |

| RAPC           | _                                                | 11141             | open during program execution.                                                                                    | · un-uuwii   |

| 00 to D7       | 8                                                | I(N)              | Used to input instructions.                                                                                       |              |

| 40 to A12      | 13                                               | O(PU)             | For PC output, or ACC or RAM address output,                                                                      | Pull-up      |

(Note 1) Contact our sales personnel for more information on the crystal oscillation.

(Note 2) At present time, only the ceramic resonator oscillation is available.

(Note 3) The above options can be selected by inputting the 2-byte data information to the area between the (last address minus 1) address and the last address in the ROM.

#### 4. How to specify options

As explained below, the input/output circuit formats for the LM8800 series microcomputers can be selected by using the mask option.

When you evaluate programs for the LM8800 series microcomputers using the LM88PG99A, you can select the same input/output format and function as those of a production chip by mounting an EPROM whose option select area contains option codes and setting external switches, respectively. The use of the external switches enables the selections of the OSC, divider ratio and memory capacity.

| ROM area       | Bit | Input data and selectable input/output circuit formats                                    |

|----------------|-----|-------------------------------------------------------------------------------------------|

| , <u> </u>     | 7   | Used for specifying the output formet for P54 through P57.                                |

|                | L   | 1 for selecting PU (Pull-up). 0 for OD (Open drain).                                      |

|                | 6   | Used for specifying the output format for P50 through P53.                                |

|                |     | 1 for selecting PU (Pull-up). 0 for OD (Open drain).                                      |

|                | 5   | Used for sepcifying the output format for P34 through P37.                                |

|                | ;   | 1 for selecting PU (Pull-up). 0 for OD (Open drain).                                      |

|                | 4   | Used for specifying the output format for P30 through P33.                                |

| (Last address  |     | 1 for selecting PU (Pull-up). 0 for OD (Open drain).                                      |

| miņus 1)       | 3   | Used for specifying the output format for P24 through P27, https://www.bistich.com/       |

| •              |     | 1 for selecting PU (Puil-up). 0 for OD (Open drain).                                      |

|                | 2   | Used for specifying the output format for P20 through P23. A for selection P31 (1) and    |

|                |     | 1 for selecting PU (Puil-up). 0 for OD (Open drain).                                      |

|                | 1   | Used for specifying the output signal level of P30 through P37 and P60 through P65        |

|                |     | at the reset. 1 for selecting the H level signal. 0 for the L level signal.               |

|                | 0   | Used for specifying the output signal level of P20 through P27 and P50 through P57        |

|                |     | at the reset. 1 for selecting the H level signal. 0 for the L level signal.               |

|                | 7   | Not available yet. Note 1                                                                 |

|                | 6   | Used for specifying a divider ratio (TSLOW) of the OSC. *Note 2.                          |

|                | LI  | 1 for specifying the 1/2 SLOW, 0 for the 1/1 FAST,                                        |

|                | 5   | Used for specifying an OSC type. Note 2.                                                  |

|                |     | 1=*Reserved, 0 for specifying the CF oscillation.                                         |

| (Last address) | 4   | Used for specifying the zero cross detection circuit for the T0 input. If the cross forms |

|                | f   | 1 for specifying the internal circuit. O for nonuse of the internal circuit,              |

|                | 3   | Used for specifying the input format of P34 through P37.                                  |

|                | L   | 1≈H (High threshold input). 0=N (Normal input).                                           |

|                | 2   | Used for specifying the input format of P30 through P33. 1=H. 0=N.                        |

|                | 1   | Used for specifying the input format of P24 through P27. 1=H, 0=N.                        |

|                | 0   | Used for specifying the input format of P20 through P23. 1=H. 0=N.                        |

The option specification area varies depending on each ROM size. For the LM8854, it is between address OFFEH and OFFFH.

When evaluating programs for the LM8800 series microcomputers using either the LM8899A or LM88PG99A, you can select the following option specification areas by setting the external switches for selecting the memory capacities: (1FFEH, 1FFFH) for the 8K-byte ROM. (0FFEH, 0FFFH) for the 4K-byte ROM. (7FEH, 7FFH) for the 2K-byte ROM.

<sup>\*</sup>Reserved: For Type Nos. under development or future Type Nos.

<sup>\*</sup>Note 1: Specify 0. The data of 0 is automatically set when the Sanyo assembler is used.

<sup>\*</sup>Note 2: Use external switches when evaluating programs using the LM8899A or LM88PG99A. CF oscillation means the ceramic resonator oscillation.

#### 5. Notes on use

- (1) The LM88PG99A has the 28-pin socket for mounting either the 2732, 2732A or 2764 EPROM. Pins 1, 2, 27 and 28 should be open when the 2732 or 2732A EPROM is mounted on.

- (2) How to select the OSC, divider ratio and memory capacities. The OSC, divider ratio and memory capacity can be selected by setting plns 1 through 4 on the 14-pin socket on the package surface as follows.

To select other options, input option data to the option specification area.

| Function type             | Pin no. | Pin name   | Pin s          | etting | Function                | n mode | Option o                                         | data     |            |

|---------------------------|---------|------------|----------------|--------|-------------------------|--------|--------------------------------------------------|----------|------------|

| OSC                       |         | VOD        | OFF<br>ON      |        | CF oscillation RESERVED |        | Bit 5 of the                                     | 0        | 1          |

| osc                       | 1       | XCR        |                |        |                         |        | last address ——————————————————————————————————— |          |            |

| Clock prescaler divider   |         | TD1 0141   | OFF 1/1 ON 1/2 |        | Bit 6 of the 0          |        | Ī ·                                              |          |            |

| ratio                     | 2       | TSLOW      |                |        | 1/2                     |        | last address                                     | 1        | ]          |

|                           |         |            | Pin s          | etting | tting Memory capacity   |        | Option data area                                 |          | 1          |

|                           | an 3    | MC0<br>MC1 | MCO            | MC1    | ROM                     | RAM    | Option det                                       | .a ar sa |            |

| Memory capacity selection |         |            | OFF            | OFF    | 4KB                     | 256B   | FFE, FF                                          | FH       | KLM8864/04 |

|                           |         |            | ON             | OFF    | ВКВ                     | 2568   | 1FFE, 1F                                         | FFH      |            |

|                           |         |            | OFF            | ON     | 2KB                     | 128B   | 7FE, 7F                                          | FH       | (LM8802)   |

|                           |         | l          | ON             | ON     | Hese                    | erved  |                                                  |          | Ţ '        |

ON: +6V voltage supply. OFF: Open-circuited. Reserved: For the Type Nos, under development or future Type Nos.

<sup>\*</sup>The BK-byte ROM is selected only to debug programs (Use assembler LM8899 COM. In this case, the option specification area is between address 1FFEH and address 1FFFH).

Pins 14, 13, 12 and 11 of the 14-pin socket are connected with +5V pin. These pins can be used only to supply +5V voltage to pins 1, 2, 3 and 5 respectively. Note that these pins cannot be used for any other purpose.

Pins 5, 6, 7, 8, 9 and 10 of the 14-pin socket are used for program debugging when the TB88PG of the program debugging unit (EVA-410C) is used together with the LM88PG99A microcomputer. Otherwise, all these pins should be left open.

#### (3) EPROM power supply source

- Each EPROM normally consumes current of 50 to 100mA. When sufficient power cannot be supplied to an EPROM from an application product, an independent external power supply source can be used to operate the EPROM.

- At the shipment of the LM88PG99A, the +5V pin and the VDD pin are connected. This means, the power

is supplied to an EPROM from the pin 16 (VDD) which is used for supplying the power to the LM8899.

Of the power supply pads on the package surface, the +5V pad is used to supply power to an EPROM.

Beautiful and the package surface, the +5V pad is used to supply power to an EPROM.

EPROM power supply pad (This is a different power supply source from that of a production chip.)

(4) Evaluation of programs for the LM8804/02 microcomputer

The LM8804/02 microcomputer has 42 pins. Therefore, the pin conversion board (SK8804S) needs to be used when the programs for the LM8804/02 microcomputer are evaluated by the LM88PG99A microcomputer.

### 6. Specifications

## (1) Absolute maximum ratings (VSS=0V, Ta=25°C)

| ltem                             | Symbol            | Conditions                                                     |                             | Unit |

|----------------------------------|-------------------|----------------------------------------------------------------|-----------------------------|------|

| Maximum supply voltage           | V <sub>DM</sub>   |                                                                | -0.3 to +8                  | V    |

| Input/output voltage<br>Note 1   | V <sub>IO1</sub>  | TNTO, T1, P4, P1 and input/output ports with open drain format | -0.3 to +15                 | ٧    |

|                                  | V <sub>IO2</sub>  | Input/output pins other than the above -                       | 0.3 to V <sub>DD</sub> +0.3 | v    |

|                                  | IOHA              | Per pull-up or push-pull pin                                   | -2.0                        | mA   |

|                                  | IOLA1             | Per output pin other than P1                                   | 18                          | mΑ   |

| Average output current           | IOLA2             | Per output pin of P1                                           | 30                          | mA   |

| Note 2                           | IOLA3             | Total output of P0, P5 and P6                                  | 120                         | mA   |

|                                  | IOLA4             | Total output of P2 and P3                                      | 80                          | mA   |

|                                  | I <sub>OLA5</sub> | Total output of upper four pins or lower four pins of P1       | 75                          | mA   |

|                                  | IOHP              | Per pull-up or push-pull pin                                   | -2.0                        | mA   |

|                                  | IOLP1             | Per output pin other than P1                                   | 18                          | mA   |

| Peak output current              | IOLP2             | Per output pin of P1                                           | 30                          | mA   |

| Note 3                           | IOLP3             | Total output of P0, P5 and P6                                  | 120                         | mA   |

|                                  | OLP4              | Total output of P2 and P3                                      | 80                          | mA   |

|                                  | IOLP5             | Total output of upper four pins or lower four pins of P1       | 75                          | mA   |

| Recommended power<br>dissipation | P <sub>dmax</sub> | Ta=10 to 40°C, DIC-84S                                         | 1000                        | Wm   |

| Operating temperature range      | Торд              |                                                                | +10 to +40                  | °c   |

| Storage temperature range        | T <sub>stg</sub>  |                                                                | -55 to +150                 | °c   |

Note 1: Output≂OFF or "H". The output signal level width can be allowed at the X1 pin.

Note 2: Limit values: Average output current measured at any interval of 100ms should be less than those values.

Note 3: Celling limit values should not be exceeded at any moment,

|                                       | Item                             | Symbol             | Cor                                                                                                                    | nditi  | ons                         | min                | typ                                              | max                                              | un       |

|---------------------------------------|----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------|--------------------|--------------------------------------------------|--------------------------------------------------|----------|

| Supply volts                          | ige                              | VDD                |                                                                                                                        |        |                             | 4.5                | · · · · ·                                        | 5.5                                              | İΫ       |

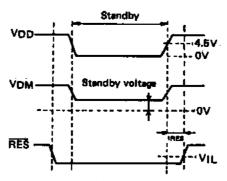

| RAM power                             | supply voltage                   | VDM                | At the normal operation                                                                                                |        | figure 6 for interrelations | 4.5                |                                                  | 5.5                                              | V        |

|                                       |                                  | (V <sub>DM</sub> ) | RES="L" at<br>the standby<br>mode                                                                                      | RES    |                             | 3.5                |                                                  | 5.5                                              | V        |

| Normal inpu                           |                                  | VIH1               | PO, and norma                                                                                                          | l Inp  | ut options for              | 2.2                |                                                  | 5.5                                              | V        |

| ports                                 | "L" level input voltage          | VIL1               | P2 and P3                                                                                                              |        |                             | VSS                |                                                  | 0.6                                              | ٧        |

| High                                  | "H" level input voltage          | VIH2               | P1 and P4, and                                                                                                         | l hial | h-threshold                 | 0.6V <sub>DD</sub> |                                                  | <del>                                     </del> | Īν       |

| threshold                             | "L" level input voltage          | VIL2               |                                                                                                                        |        |                             | Vss                |                                                  | 0.3V <sub>DD</sub>                               | ۱v       |

| input ports                           |                                  |                    | input options for P2 and P3.  Note that only the normal input option can be selected for A <sub>0</sub> , S, R, and W. |        | . 22                        |                    | 0.3400                                           | *                                                |          |

| ÎNTO, T1                              | "H" level input voltage          | VIH3               | 1                                                                                                                      |        | ·····                       | 0.6V <sub>DD</sub> | <del>                                     </del> |                                                  | V        |

| •                                     | "L" level Input voltage          | VIL3               |                                                                                                                        |        |                             | VSS                | <del>                                     </del> | 0.3V <sub>DD</sub>                               | v        |

| RES                                   | "H" level input voltage          | VIH4               | <u> </u>                                                                                                               |        |                             | 0.6V <sub>DD</sub> |                                                  | V <sub>DD</sub>                                  | Ť        |

|                                       | "L" level input voltage          | VIL4               |                                                                                                                        |        | <u> </u>                    | VSS                | $\vdash$                                         | 0.9                                              | Ť        |

|                                       | "L" level input voltage          | VILE               | V <sub>DM=3,5</sub> V                                                                                                  |        |                             | VSS                | <del> </del>                                     | 0.9                                              | ΙŤ       |

| ·-·-                                  | "H" level input voltage          | VIHE               | External drive                                                                                                         | onti   |                             | 0.4V <sub>DD</sub> | <del> </del> -                                   | V <sub>DD</sub>                                  | ľ        |

|                                       | L                                |                    | (Ceramic reson                                                                                                         | • .    |                             | +1.0               |                                                  |                                                  |          |

| u a                                   | "L" level input voltage          | VILE               |                                                                                                                        |        |                             | Vşş                |                                                  | 0,9                                              | L V      |

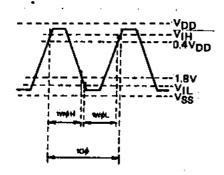

| X1                                    | Clock pulse width                | tCΦ                | See Figure 1                                                                                                           |        | <u> </u>                    | 0.14               |                                                  | 0.5                                              | JJ1      |

|                                       | Instruction cycle time           | tCI                | tCT x 8 x divid                                                                                                        | ier ra | etio (1 or 2)               | 1.12               |                                                  | 4                                                | וע       |

|                                       | "H" level clock pulse width      | НФW                | External drive option (Ceramic resonator oscillation)                                                                  |        |                             | 0.06               |                                                  |                                                  | Щ        |

|                                       | "L" level clock pulse width      | ₩ΦL                | External drive option<br>(Ceramic resonator oscillation)                                                               |        | 0.06                        |                    | <del></del>                                      | ) I                                              |          |

| TEST                                  | "L" level input voltage          | VIL7               |                                                                                                                        |        | O a contraction of          | VSS                |                                                  | 0.6                                              | V        |

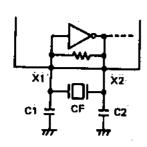

| X1                                    | Caramic resonator oscillation    | C1                 | Ceramic resona                                                                                                         | tor o  | oscillation                 | 30                 | 33                                               | 36                                               | ρF       |

| X2                                    | oscillation<br>External capacity | C2                 | options (4MHz                                                                                                          | , 6M   | Hz and                      | 42                 | 47                                               | 52                                               | pF       |

|                                       | "H" level input voltage          | VIHB               | 7MHz) See figure 2, Note 4,<br>Normal input option                                                                     |        |                             | 2.2                |                                                  | V <sub>DD</sub>                                  | v        |

| то                                    | "L" level input voltage          | VIL8               | Normal input option                                                                                                    |        | VSS                         |                    | 0.6                                              | Ÿ                                                |          |

|                                       | Zero-cross input level           | VZIN               | Capacitor-coup                                                                                                         |        |                             | 1.0                |                                                  | 2.2                                              | v        |

|                                       | Zero-cross input                 | fZIN               | Zero-cross opti                                                                                                        |        | hear to hear                | 50                 |                                                  | 1000                                             | Hz       |

| · · · · · · · · · · · · · · · · · · · | frequency                        |                    |                                                                                                                        |        |                             |                    |                                                  |                                                  | L        |

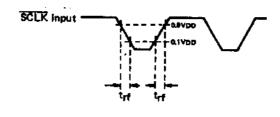

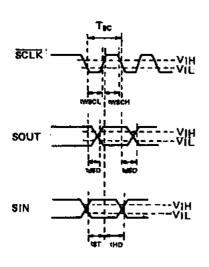

|                                       | input pulse cycle time           | tsc                |                                                                                                                        |        |                             | 1.0                |                                                  |                                                  | μs       |

| SCLK<br>(P32)                         | Pulse width of "H"               | tWSCH              | See figure 3. Externs                                                                                                  |        | nal clock                   | 0.4                |                                                  |                                                  | μs       |

| -                                     | Pulse width of "L"               | twscl              |                                                                                                                        |        |                             | 0.4                |                                                  |                                                  | 'ns      |

| 1                                     | Rise or fall time of input       | t <sub>rf</sub>    | See figure 4. E                                                                                                        | xteri  | nal clock                   |                    |                                                  | 1.0                                              | Ήŧ       |

| CLK (P32)                             | Data Input set-up time           | tST                | See figure 3                                                                                                           |        |                             | 0.3                |                                                  | <del></del>                                      | ŢŢŹ      |

| SIN (P30)                             | Data input hold time             | tHD.               | See figure 3                                                                                                           |        | 0.03                        |                    |                                                  | T18                                              |          |

| AO (P24)                              | Pre-R/W input set-up             | tSUP               | See figure 5. 8                                                                                                        | bit b  | ous interface               | 0.26               |                                                  |                                                  | TI8      |

| 5 (P25)                               | Post-R/W input hold              | tHLD               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                |        |                             | 0                  |                                                  |                                                  | ns<br>su |

| T (P26)                               | Data input set-up time           | †DSUP              |                                                                                                                        |        |                             | 0.15               |                                                  |                                                  | ), IS    |

| N (P27)                               | Data input hold time             | tDHLD              | 17                                                                                                                     |        |                             | 0.03               |                                                  |                                                  | LIS.     |

|                                       | . — **** ********** 41116        | WOLU !             | "                                                                                                                      |        | U.UU                        | - 1                | L                                                | - 113                                            |          |

Note 4: Includes the stray capacitance of Board, Wiring, etc.

| P4, T0, T1                              | İtem                                  | Symbol            | Conditions                                                             | l main                                           |                   |                 |            |

|-----------------------------------------|---------------------------------------|-------------------|------------------------------------------------------------------------|--------------------------------------------------|-------------------|-----------------|------------|

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | "H" level input current               | I <sub>IH1</sub>  | V <sub>IN</sub> =13.5V                                                 | min                                              | typ               | max             | uni        |

|                                         | i i i i i i i i i i i i i i i i i i i | יוחוין            | (In this case, the normal input                                        |                                                  |                   | 5               | μA         |

|                                         |                                       | !                 | option must be selected for TO.)                                       |                                                  |                   |                 |            |

| INTO                                    | "L" level input current               | IIL1              | VIN=VSS, (In this case, the                                            | -5                                               | $\vdash$          |                 | 1          |

|                                         |                                       | 1,15,1            | -0                                                                     |                                                  |                   | μA              |            |

|                                         | ł                                     |                   | normal input option must be selected for T0,)                          |                                                  |                   |                 |            |

| P0 port                                 | "H" level input current               | <del> </del>      | ╂╼╌┤                                                                   | 5                                                | LΑ                |                 |            |

|                                         | "L" level input current               | IIH2              | VIN=VDD, (with output OFF) VIN=VSS, (with output OFF)                  | _5                                               | <del>  </del>     |                 | JJA        |

| Pull-up                                 | "L" level input current               | IIL3              | VDD=5V±10% and VIN=0.4V                                                | -1.6                                             | <del>  </del>     |                 | m/         |

| Input/output                            |                                       |                   | when the pull-up option is                                             |                                                  |                   |                 | ""         |

| ports                                   |                                       |                   | selected for P2 and P3, and the                                        |                                                  |                   |                 | }          |

|                                         |                                       |                   | output level is "H"                                                    |                                                  |                   |                 | i i        |

| Open drain                              | "H" level input current               | IIH4              | VIN=13.5V when the open drain                                          |                                                  |                   | 5               | μA         |

| input/output                            |                                       |                   | option is selected for P1, and P2                                      |                                                  |                   |                 |            |

| ports                                   | 44 44                                 | <u> </u>          | and P3, and with output OFF.                                           |                                                  |                   |                 |            |

|                                         | "L" level input current               | IL4               | VIN=VSS, when the open drain                                           | <b></b> 5                                        |                   |                 | ĮμΑ        |

|                                         |                                       | Í                 | option is selected for P1, and P2                                      |                                                  |                   |                 |            |

| X1                                      | "H" level input current               | 1                 | and P3, and with output OFF.                                           | <u> </u>                                         |                   |                 | <u> </u>   |

| ^'                                      | ri level input current                | (IHE              | VIN=VDD, when the ceremic reso-                                        | 2                                                | 1                 | 13              | μА         |

| •                                       | "L" level input current               | llL5              | netor oscillation option is selected.  VIN=VSS, when the ceramic reso- | 1 45                                             |                   | <u>-2</u>       |            |

| •                                       |                                       | פווין             | nator oscillation option is selected.                                  | -13                                              |                   | -2              | μА         |

| RES                                     | "H" level input current               | IHE               | VIN=VDD                                                                | <del> </del> -                                   |                   |                 | -          |

|                                         | "L" level input current               | IIL6              | VIN=VSS                                                                | _35                                              |                   | 6               | ЦΑ         |

|                                         | "H" level input current               | IH7               | VIN=VDD, when the zero-cross                                           | -35                                              |                   | <u>6</u><br>195 | μA         |

|                                         |                                       | 1,11,1            | detection option is selected.                                          |                                                  |                   | 180             | "^         |

| то                                      | "L" level input current               | l <sub>1L</sub> 7 | VIN=VSS when the zero-cross                                            | -70                                              |                   |                 | uА         |

|                                         | -                                     | '-'               | detection option is selected.                                          | ] "                                              |                   |                 | <b></b> `` |

|                                         | Zero-cross detection                  | VZA               | 60Hz sine wave input when the                                          | † · · · · · · · · · · · · · · · · · · ·          |                   | ±100            | mV         |

|                                         | Accuracy ,                            |                   | zero-cross detection option is                                         | [                                                |                   |                 | 1          |

|                                         | -                                     |                   | selected.                                                              | ]                                                |                   |                 |            |

| PO port                                 | "H" level output voltage              |                   | VDD=5V±10%, IOH=-0.4mA                                                 | 2.4                                              |                   |                 | V          |

|                                         | "L" level output voltage              |                   | I <sub>OL</sub> =14mA                                                  | <u></u>                                          |                   | 1.5             | V          |

|                                         |                                       | VOH2              | IOH=-50uA when the pull-up                                             | 0.8V <sub>DD</sub>                               |                   |                 | \ V        |

|                                         |                                       |                   | option is selected for P2, P3 and                                      |                                                  |                   |                 |            |

| Pull-up                                 | MAP touch make under make             | 3.6               | P5.                                                                    |                                                  | <del></del>       | <del></del>     | <u> </u>   |

| output                                  | "H" ievel output voltage              | <b>№ОНЗ</b>       | IOH=-100uA when the pull-up                                            | 0.48V <sub>DD</sub>                              | ì                 |                 | V          |

| ports                                   |                                       |                   | option is selected for P2, P3 and P5.                                  |                                                  |                   |                 |            |

|                                         | "L" level output voltage              | Vola              | IQL=14mA when the pull-up                                              | † ·· <del></del>                                 | $\longrightarrow$ | 1.5             | ₩          |

|                                         |                                       | 1012              | option is selected for P2, P3 and                                      |                                                  |                   | 1.0             | ] *        |

|                                         |                                       |                   | P5.                                                                    | ·                                                |                   |                 | ľ          |

|                                         |                                       | OFF1              | VOH=13.5V when the open                                                | <del>                                     </del> | $\dashv$          | 5               | μA         |

|                                         |                                       |                   | drain option is selected for P6,                                       |                                                  |                   |                 |            |

| Open drain                              | Leakage current with                  |                   | and P2, P3 and P5.                                                     | <u> </u>                                         | ľ                 |                 | 1          |

| output                                  | output OFF                            | lOFF2             | VOH=VDD when the open                                                  |                                                  |                   | 1               | μA         |

| ports                                   |                                       |                   | drain option is selected for P6,                                       |                                                  |                   |                 | 1          |

| ļ                                       | <i>//</i>                             |                   | and P2, P3 and P5.                                                     |                                                  |                   |                 | ļ          |

|                                         | "L" level output voltage              | AOL3              | IOL=15mA when the open                                                 |                                                  |                   | 1.5             | V          |

|                                         | Ì                                     |                   | drain option is selected for P6,                                       |                                                  |                   |                 |            |

|                                         | 1                                     | 1                 | and P2, P3 and P5.                                                     | <b></b>                                          |                   |                 | <u> </u>   |

|                                         | L BOYSES ALITYANT WITH                | INCEA             | V <sub>OH</sub> =13.6V                                                 | 4 I                                              | - 1               | 5               | μA         |

| P1 port                                 |                                       | OFF4              | VOH=VDD                                                                | <del>                                     </del> | <b></b> ∤-        | <u></u>         | μA         |

Continued on next page.

| LN | 188PC | 399 | IΑ |

|----|-------|-----|----|

|                   | Item        |               | Symbol           | T 0                                             | onditions   |          | min         | typ    | max      | unit   |

|-------------------|-------------|---------------|------------------|-------------------------------------------------|-------------|----------|-------------|--------|----------|--------|

| EST               | "L" level 1 | nput current  | IIL8             | VIN=VSS                                         |             |          | -10         | 1.75   |          | μĀ     |

| erial output      | Output de   | lay time      | tdSD             | See Figure 3 up resistor=2 SOUT load of         | Kohm: Cl    | L: SCLK/ |             |        | 0.36     | ВS     |

| (P26)<br>00 to 07 | Ì           | able period   | ₹dEN             | See figure 5.<br>CL: P00 to f                   | CL=150p     | F,       |             |        | 0.22     | βų     |

| <u></u>           | Output dis  | enable period | tdDE             | See figure 5                                    |             |          |             |        | 0.17     | μS     |

| OM                | RAM pow     | by current    | DMS              | V <sub>DM</sub> =4.5V,<br>V <sub>DM</sub> =5V±1 | RES=L       |          | <del></del> |        | 30       | mA     |

|                   | current     | er suppry     | <sup>1</sup> DM  | ADM-BATH                                        | J76         | }        |             |        | 30       | mA     |

| /DM               | Total power | er supply     | IDD              | OSC oscillati                                   | on mode. (  | Den with |             | 105    | 135      | mA     |

| OD_               | current     |               | +I <sub>DM</sub> | output "H",                                     | Ta=10 to 4  | 40°C.    |             |        | 100      | ""     |

| nput              | Pin capacit | ance          | CI               | When 1MHz                                       | is selected | as f.    |             | 10     |          | pF     |

| i                 | i           | i . I         |                  | . 1                                             |             | 1 1      |             | +      | <u> </u> | 1      |

|                   | i           |               | :                |                                                 | j           |          |             |        | j        |        |

| 1 !               | į           |               | İ                |                                                 | j           |          | [           |        |          | 1      |

|                   | į           |               | '                |                                                 | 1           |          | 1           |        | i        | 1      |

| ·                 | 1           | . !           |                  | .                                               | İ           |          |             | !      | Ì        | 1      |

|                   | 1           | !             |                  |                                                 | i           | 1        | :           | j      | ļ        | 1      |

|                   | i           |               |                  |                                                 |             |          | i           | i<br>I |          | }      |

|                   |             | ·             |                  | i                                               | į           | 1 !      |             |        | 1        | 1      |

|                   |             | ;             |                  |                                                 | 1<br>1      |          | i           | ļ      |          | i      |

|                   |             |               |                  | :                                               |             |          |             |        | ļ        |        |

|                   |             | 1             | 1                | :                                               |             |          |             | į      | ļ        |        |

|                   |             |               |                  | 1                                               | į           | i ;      |             | İ      |          |        |

|                   |             |               |                  |                                                 |             | . !      |             | i      | i        | í      |

|                   |             |               |                  |                                                 |             | 1        | •           | ł      |          | ĺ      |

|                   |             |               |                  |                                                 |             | į.       |             | i      |          | İ      |

|                   |             |               |                  |                                                 |             | :        |             |        | 1        | Ì      |

|                   |             | i             |                  |                                                 |             | Ī        |             | i      |          |        |

|                   |             | į             |                  |                                                 |             |          |             | i      | '        |        |

|                   |             | į.            |                  |                                                 | 1           |          |             | į      |          | Ī      |

|                   |             |               |                  |                                                 |             |          |             |        | :        | 1      |

|                   |             | ļ             |                  |                                                 | :           | :        |             | ļ.     | •        | ;<br>  |

|                   |             | ·             |                  |                                                 | :           | ;        |             |        |          | :<br>( |

|                   |             |               |                  |                                                 | !           | l        |             |        |          | i      |

|                   |             |               |                  |                                                 |             | 1        |             | i      |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          | •<br>: |

|                   |             |               |                  |                                                 |             |          |             | :      |          | ì      |

|                   |             |               |                  |                                                 |             | ;        |             |        |          | 1      |

|                   |             |               |                  |                                                 |             | 1        |             |        |          | •      |

|                   |             |               |                  |                                                 |             |          |             | :      |          | :      |

|                   |             |               |                  |                                                 |             |          |             | :      | 1        | !<br>: |

|                   |             |               |                  |                                                 |             |          |             |        | :        | 1      |

|                   |             |               |                  |                                                 |             |          |             |        |          | i      |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          | (      |

|                   |             |               |                  |                                                 |             |          |             |        |          | :      |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          | :      |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          |        |

|                   |             |               |                  |                                                 |             |          |             |        |          | :      |

|                   |             |               |                  |                                                 |             |          |             |        |          | !<br>! |

|                   |             |               |                  |                                                 |             |          |             | :      |          | :<br>  |

|                   |             |               |                  |                                                 | 1           |          |             |        | •        | }      |

|                   |             |               |                  |                                                 |             |          |             |        | -        |        |

Fig. 1 X1 Input waveform

Fig. 4 SCLK rise/fall time

Fig. 5. 8-bit bus interface timings

Fig. 2 Ceramic resonator oscillation circuit

CF: CSA 4.00MG (Mureta)

KBR 4.0MS (Kyocere)

CSA 8.00MT (Mureta)

KBR 8.0M (Kyocere)

CSA 7.00MT (Mureta)

POO to PO7

Effective data

POO to PO7

POO to PO7

Effective data

POO to PO7

Effective data

Fig. 6. Reset waveforms and power supply waveforms at the standby mode

Fig. 3 Serial input/output timings

(Note) When the RES signal level changes from "L" to "H", the condition (of 5.5≥Vpp≥VpM≥4.6) must be setisfied. And the condition of reset release time (Tres)≥oscillation stabilizing period + 2 instruction cycles) must be also mat.