CMOS LSI

No. 3054

# LC86108A

Liquid Crystal Display Controller/

Driver, On-chip 8K Bytes ROM and On-chip

168 Bytes RAM

8-BIT SINGLE CHIP MICROCOMPUTER LC86108A

The LC86108A microcomputer is an 8-bit single chip microcomputer with the following onchip functional blocks:

- CPU: Operable at a minimum cycle time of 1 microsecond.

- On-chip ROM: Capacity = 8K bytes

- On-chip RAM: Capacity = 168 bytes

- Dot matrix Liquid Crystal automatic display controller/driver

- Two 16-bit timers/counters

- Seven-source 5-level vectored interrupt system

All of the above functions are fabricated on a single chip.

# General purpose applications:

- (1) Data bank control

- (2) Remote controlling for VCR, tuner, and the like.

- (3) Controlling for CD, tuner, and the like.

- (4) Controlling for small-sized measuring instruments

#### Features:

- (1) Read-Only Memory (ROM): 8192 x 8 bits

- (2) Random Access Memory (RAM): 168 bytes. 128 x 8 bits for computation (general purpose RAM) and 40 x 8 bits for data display (display RAM)

- (3) Cycle time: Cycle time varies depending on system clock sources. The selectable system clock sources are shown in the table below.

| Cycle time | System clock source                                   | Oscillation frequency | Operating voltage range | Remarks |

|------------|-------------------------------------------------------|-----------------------|-------------------------|---------|

| 1µs        | Ceramic (CF) resonator oscillation specification      | 12MHz                 | 4.5 ~ 6.0V              |         |

| 4µs        | Ceramic (CF) resonator oscillation specification      | 3MHz                  | 2.5 ~ 6.0V              |         |

| 15µs       | RC (Resistor and Capacitor) oscillation specification | 800kHz                | 2.5 ~ 6.0V              |         |

| 366µs      | Crystal (X'tal) oscillation specification             | 32kHz                 | 2.5 ~ 6.0V              |         |

| 183µs      | Crystal(X'tal) oscillation specification              | 65kHz                 | 2.5 ~ 6.0V              |         |

## (4) Current dissipation

# a. Basic system operation mode

| Current dissipation | System clock source                                   | Oscillation frequency | Operating voltage range | Remarks                                                  |

|---------------------|-------------------------------------------------------|-----------------------|-------------------------|----------------------------------------------------------|

| 9.5mA TYP           | Ceramic(CF) resonator oscillation specification       | 12MHz                 | 5 <b>.</b> 0V           | Display segments OFF                                     |

| 1.4mA TYP           | Ceramic(CF) resonator oscillation specification       | ЗМНг                  | 2.9V                    | Display segments OFF                                     |

| 390дА ТҮР           | RC (Resistor and Capacitor) oscillation specification | 800KHz                | 2.9V                    | Display segments OFF                                     |

| 15µA TYP            | Crystal (X'tal) oscillation specification             | 32KHz                 | 2.9V                    | Display segments OFF and CF/RC oscillation in idle state |

# b. HALT operation mode

| Current dissipation | System clock source                                   | Oscillation frequency | Operating voltage range | Remarks                                                  |

|---------------------|-------------------------------------------------------|-----------------------|-------------------------|----------------------------------------------------------|

| 3mA TYP             | Ceramic(CF) resonator oscillation specification       | 12MHz                 | 5.0V                    | Display segments OFF                                     |

| 440µA TYP           | Ceramic(CF) resonator oscillation specification       | ЗМНг                  | 2.9V                    | Display segments OFF                                     |

| 150µA TYP           | RC (Resistor and Capacitor) oscillation specification | 800KHz                | 2.9V                    | Display segments OFF                                     |

| 5µA TYP             | Crystal (X'tal) oscillation specification             | 32KHz                 | 2.9V                    | Display segments OFF and CF/RC oscillation in idle state |

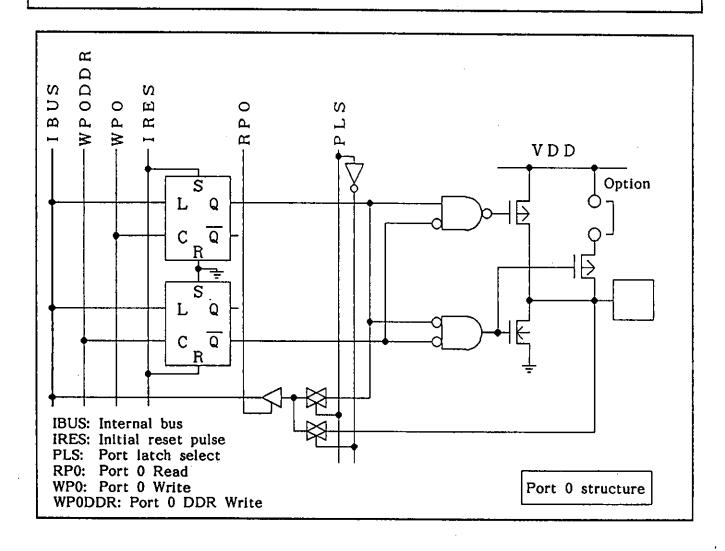

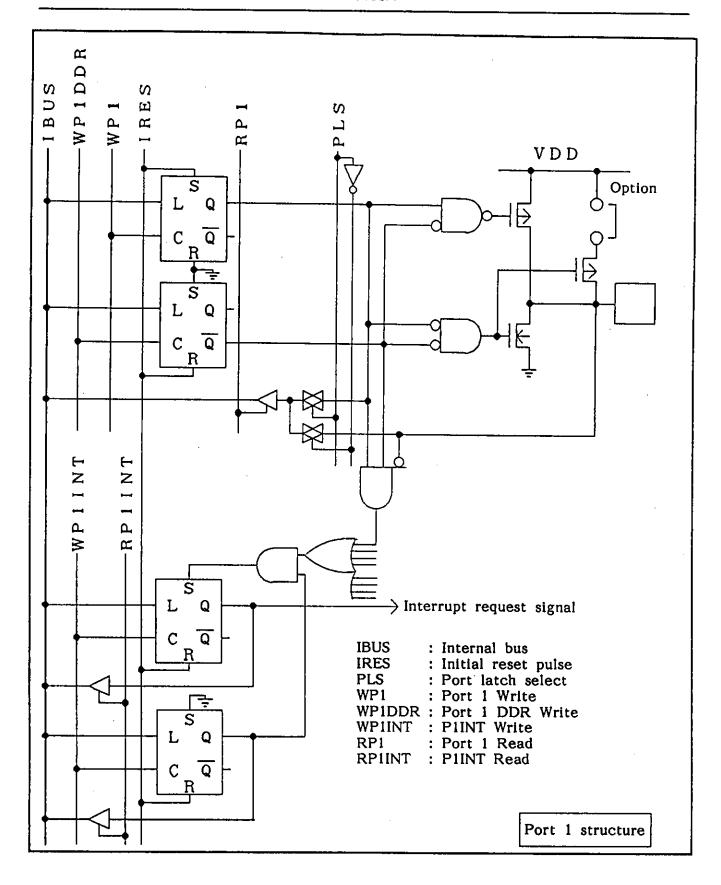

# (5) Ports

- Input/output ports: 5 ports (37 port pins) Input/output port software programmable in 8-bit units: 1 port (8 port pins) Input/output port software programmable in bit units: 4 ports (29 port pins)

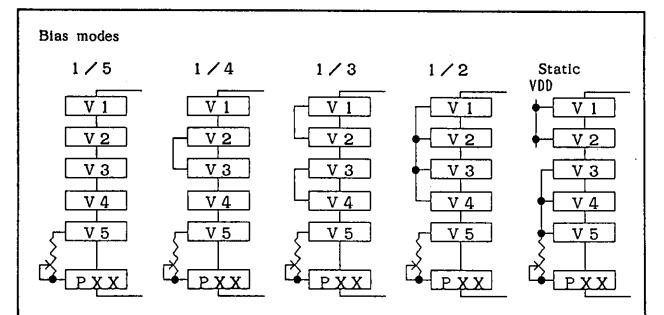

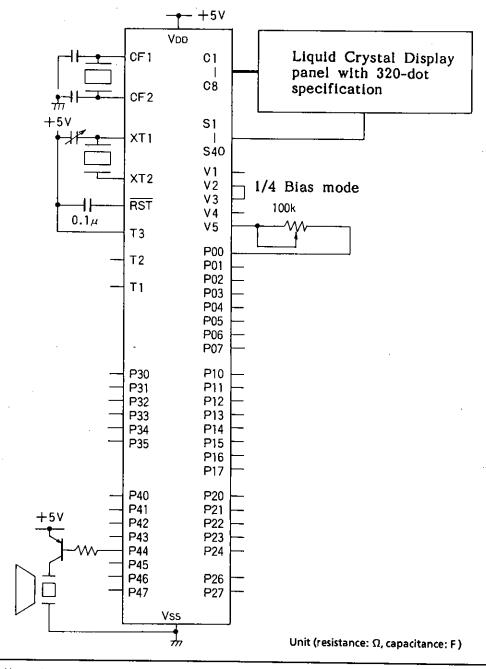

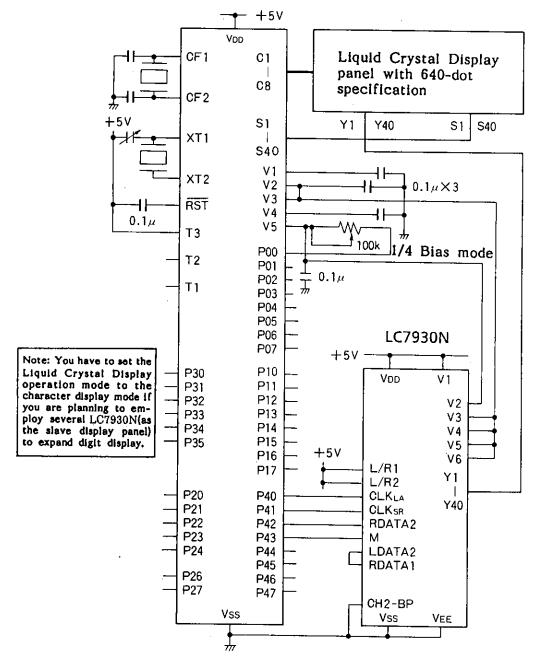

## (6) Liquid Crystal Display Drivers

- Common driver pins: 8

- Segment driver pins: 40 (Extendable to 200 segments with LC7930 x 4) Display signal duty mode: Static duty cycle to 1/8 duty cycle

- Display biasing mode: Static bias to 1/5 bias

# (7) On-chip character generator ROM

- ROM capacity: 5600 bits

- Character font: 5 x 7 dots (Max.)

- Number of characters: 160

# (8) Liquid Crystal Display control instruction

- Cursor display ON/OFF/blinking

- Display character blinking

- Display ON/OFF

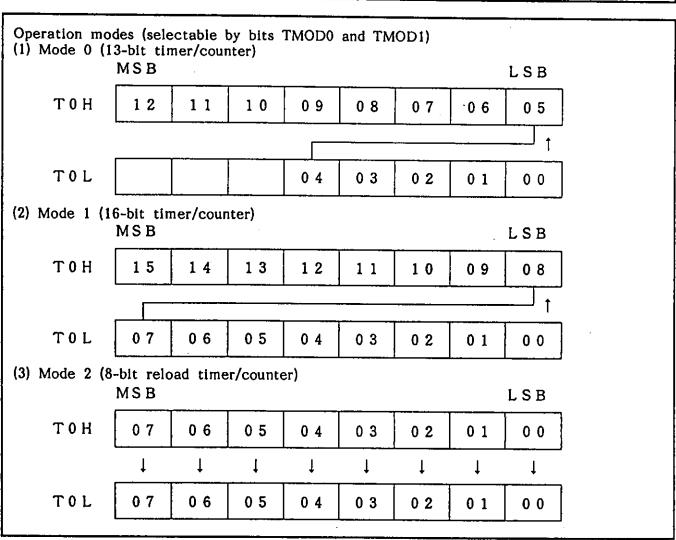

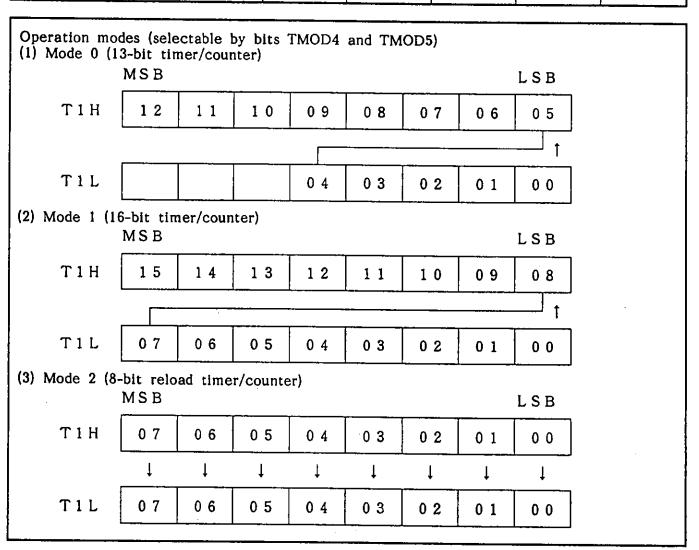

# (9) Timer

- Two 16-bit timers/counters software programmable

Mode 0: 13-bit timers/counters

Mode 1: 16-bit timers/counters

Mode 2: 8-bit automatic reloadable timers/counters

(10) Interrupt mechanism:

- 7 sources and 5 vectored interrupts:

External interrupt INTO

External interrupt INT1

Timer/counter interrupt T0

Timer/counter interrupt T1, and

Divider/port 1/port 3 interrupt

#### (11) Stack levels

- 128 levels (Max.): Stack area included in the RAM area

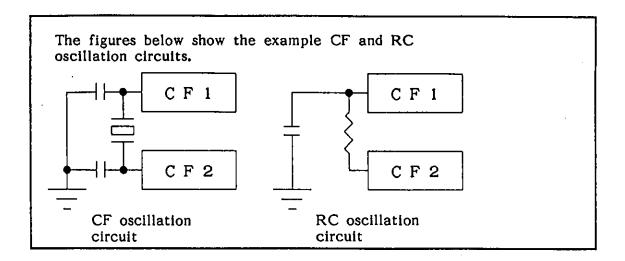

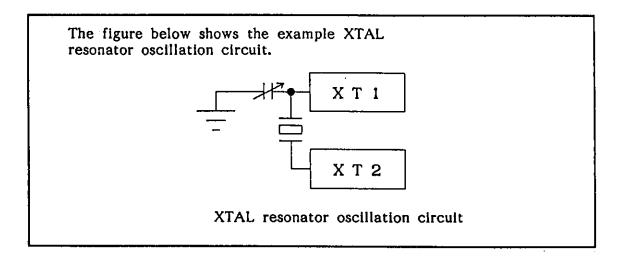

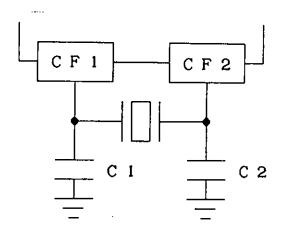

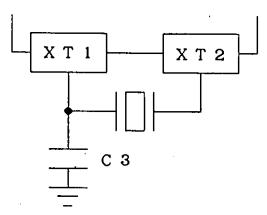

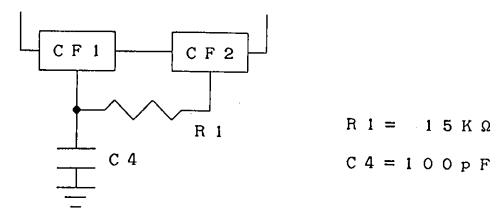

## (12) Two oscillation circuits

- One for CF or RC oscillation: Generate the system clocks and Liquid Crystal Display clocks. Note that the CF resonator oscillation or the RC oscillation can be selected by the mask option.

- One for X'tal oscillation: Generate time base clock, Liquid Crystal Display clocks and the system clock.

## (13) Liquid Crystal Display display data transfer rates

- 2/Fcf, 4/Fcf, 8/Fcf --- 256/Fcf 2/Fxt, 4/Fxt, 8/Fxt --- 256/Fxt

One of the display data transfer rates can be selected by the mask option.

Note: The Fcf indicates the oscillation frequency output by the CF resonator oscillation circuit or the RC oscillation circuit.

Note: The Fxt indicates the oscillation frequency output by the crystal (X'tal) oscillation circuit.

Note: The frame frequency Ffrm for Liquid Crystal display can be gained in the following manner:

Ffrm = 1//display data transfer rate x total display data number)

Ffrm = 1/(display data transfer rate x total display dot number)

#### (14) Standby function

- HALT mode function

The HALT mode is used to reduce power dissipation. In this operation mode, program execution is stopped. This operation mode can be released by interrupt request signals or the initial system reset request signal.

- HOLD mode function

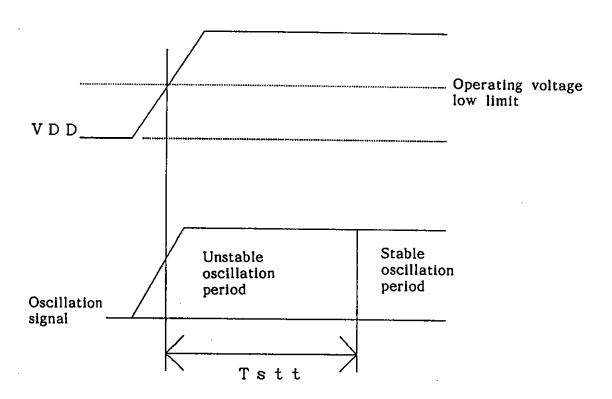

The HOLD mode is used to freeze both of the CF/RC oscillation and crystal (X'tal) oscillation. It can be released by the system reset request signal or the "L" level input signal to the external interrupt pin (INTO).

Program execution is started again after the HOLD mode is released by the input signal to the  $\overline{\text{INTO}}$  pin. However, in this release operation, it should be kept in mind that program execution may enter abnormal state due to unstable oscillation.

In order to prevent it, you can set a desired data in timer/counter 0 to generate a wait time period. The oscillation will become stable for this wait time period.

#### (15) Factory shipment

- Chip delivery form

- QIP100 delivery form

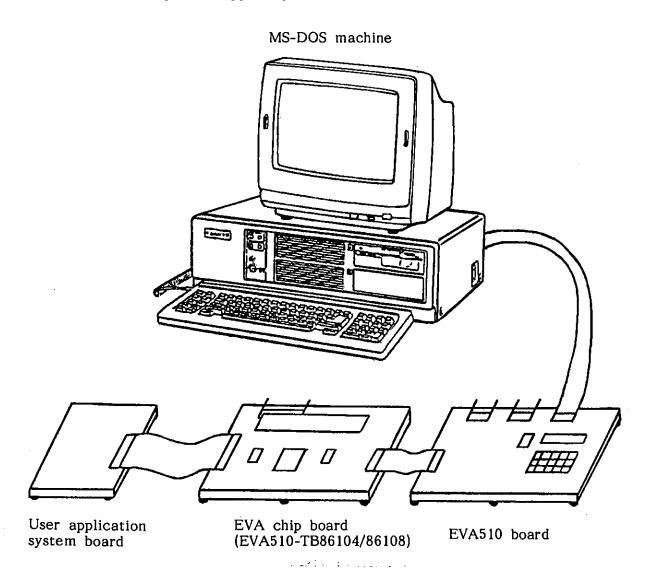

### Development support system

The development support system for the LC86108A applications consists of the following support tools:

(1) User's Manual

LC86108A/C user's manual

(2) Development support tool manual

LC86108A/C development support tool manual

(3) Development support tools

(a) Tools for developing the LC86108A application programs

- MS-DOS machine

- Macro assemblers (M86108.EXE and L86108.EXE)

- Mask option selections program (SU86108.EXE)

(b) Tools for evaluating the LC86108A application systems

- Evaluation (EVA) chip: LC86999

- Evaluation (EVA) chip board: TB86104/86108

- Evaluation (EVA) kit: EVA510

Note: MS-DOS is a trademark of Microsoft Corporation.

Note: The EVA510 board has the same function as the EVA410 board except the monitor ROM.

# Outline of the development support system

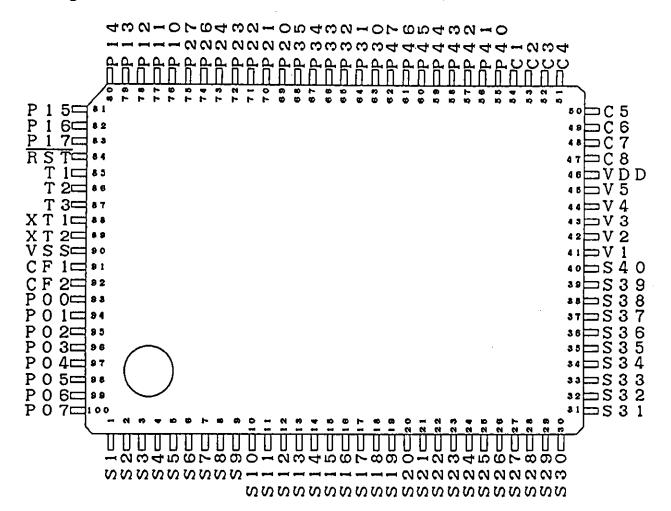

# Pin assignment

# Package Dimensions 3089-Q100ALSI (unit: mm) 0.15 0.27 0.27 0.575 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20.0 20

# Pad assignment

|            |             | <u> </u>                  |                |                   |

|------------|-------------|---------------------------|----------------|-------------------|

|            |             |                           |                | Chip size (X x Y) |

| 8685       |             | 76 74 72 70 68 66 64 62   | 60 59 58 57 56 | 6.06mm×4.76mm     |

| □87        | 83 81 79 77 | 7 75 73 71 69 67 65 63 61 |                |                   |

|            |             |                           | •              | Chip height       |

|            |             | •                         | (P07)55□       | 480 µm            |

|            | (831)       |                           | 54[            |                   |

| □89        |             |                           | 53□            | Pad size          |

| □90        |             |                           | 52□            | 1 2 0 μm×1 2 0 μm |

| 91         |             |                           | 51             |                   |

| 92         |             |                           | 50□            |                   |

| □93        |             |                           | 49□            |                   |

| 94         |             |                           | 48             |                   |

| □95        |             |                           |                |                   |

| □96        |             |                           | 47             |                   |

| 97         |             | Y                         |                |                   |

| □98        |             | (0,0)                     | 46□            |                   |

| □99        |             | <del></del>               |                |                   |

| □10        |             | Ι .                       | (VSS)45□       |                   |

| □10        |             |                           |                |                   |

| □10        |             |                           | 44 🔲           |                   |

| <b>1</b> ( | VDD)        |                           | 43□            |                   |

| <b>□</b> 2 |             |                           | 42             |                   |

| □3         |             |                           | 41 🔲           |                   |

| □4         |             |                           | - 40□          |                   |

| □5(        | C5)         |                           | . 39□          |                   |

| -          |             |                           | 38□            |                   |

| ĺ          |             |                           | (P16)37        |                   |

|            | 11 13       |                           | _              |                   |

| 6          | 7 8 9 10 12 | 14 16 18 20 22 24 26 28   | 30 32 35□      |                   |

|            |             |                           | □□□□ 34□       |                   |

# Pad coordinate values

| Pin Pad | Pin    | Pad coordinate I |          | Pin Pad  | Pin    | Pad coordinate value |       |       |       |

|---------|--------|------------------|----------|----------|--------|----------------------|-------|-------|-------|

| 1       | number | name             | Xμm      | Υμm      | number | number               | name  | Xμm   | Υμm   |

| 4 6     | 1      | VDD              | -2827    | - 775    | 5 6    | 1 1                  | P 4 1 | -1819 | -2035 |

| 4 7     | 2      | C 8              | <b>↓</b> | - 935    | 5 7    | 12                   | P 4 2 | -1659 | ļ     |

| 48      | 3      | C 7              | ↓        | -1095    | 5 8    | 13                   | P 4 3 | -1499 | ļ     |

| 4 9     | 4      | C 6              | ↓        | -1255    | 5 9    | 14                   | P 4 4 | -1339 | 1     |

| 5 0     | 5      | C 5              | ↓        | -1415    | 6.0    | 15                   | P 4 5 | -1179 | ↓     |

| 5 1     | 6      | C 4              | -2827    | -2035    | 6 1    | 16                   | P 4 6 | -1019 | · •   |

| 5 2     | 7      | C 3              | -2581    | <b>↓</b> | 6 2    | 17                   | P 4 7 | - 859 | ļ     |

| 5 3     | 8      | C 2              | -2400    | ↓        | 6 3    | 18                   | P30   | - 699 | 1     |

| 5 4     | 9      | C 1              | -2190    | ↓ ↓      | 6 4    | 19                   | P 3 1 | - 539 | 1     |

| 5 5     | 10     | P 4 0            | -1979    | -2035    | 6 5    | 20                   | P 3 2 | - 379 | -2035 |

| Pin _                                                                   | Pad                                     | Pin                                                                                                                                                                                   | Pad coo                                                          | ordinate | Pin                                                                                                   | Pad                                                                         | Pin                                                                                                                | Pad coo                                                                                                                                                                                                                                                                                                                                                                                 | rdinate                                      |

|-------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| number                                                                  | number                                  | name                                                                                                                                                                                  | Xμm                                                              | Υμm      | number                                                                                                | number                                                                      | name                                                                                                               | Xμm                                                                                                                                                                                                                                                                                                                                                                                     | Υμm                                          |

| 66789012345678901234567890123456789012345678901234567890123456789012345 | 2 2 2 2 2 2 2 2 2 3 3 3 3 3 3 3 3 3 3 3 | P33<br>P34<br>P35<br>P20<br>P21<br>P22<br>P23<br>P24<br>P26<br>P27<br>P11<br>P13<br>P14<br>P15<br>P16<br>P17<br>RST<br>T3<br>XT2<br>VSS1<br>CF2<br>P06<br>P07<br>S1<br>S2<br>S3<br>S5 | $\begin{array}{c} - & 2 & 1 & 9 & 9 & 9 & 9 & 9 & 9 & 9 & 9 & 9$ | -2035    | 7<br>8<br>9<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 6 2 3 4 5 6 6 7 8 9 0 1 2 3 4 5 6 6 7 7 7 7 7 7 8 8 8 8 8 8 9 9 9 9 9 9 9 9 | S7<br>S8<br>S10<br>S112<br>S13<br>S15<br>S16<br>S17<br>S17<br>S17<br>S17<br>S17<br>S17<br>S17<br>S17<br>S17<br>S17 | $\begin{array}{c} 1 & 5 & 3 & 7 \\ 1 & 3 & 4 & 4 \\ 1 & 1 & 5 & 5 & 7 \\ 6 & 6 & 3 & 3 & 3 \\ 1 & 2 & 6 & 6 & 6 & 6 \\ 6 & 7 & 7 & 6 & 6 & 6 \\ 7 & 9 & 9 & 6 & 6 & 6 \\ - & - & - & - & 1 & 2 & 2 & 5 & 6 \\ - & - & 1 & 2 & 2 & 6 & 6 & 7 \\ - & - & 1 & 2 & 2 & 6 & 6 & 7 \\ - & - & 1 & 2 & 2 & 6 & 6 & 7 \\ - & - & 2 & 2 & 4 & 3 & 7 \\ - & - & 2 & 2 & 6 & 8 & 2 \\ \end{array}$ | 2 1 7 8  ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ |

Note: Test pins T1 and T2 should be left unconnected. Note: Test pin T3 should be connected with the VDD pin.

Note: The chip substrate should be connected with the VSS pin or be left unconnect-

Note: Pin-to-pin soldering connection should be adopted in mounting the QIP100 package onto the printed circuit board (PCB). Entire package dipping should be avoided for this purpose.

# Pin description

| Pin name                                           | Pin<br>number                   | I/O                                       | Function description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------|---------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS                                                | 9 0                             | Output                                    | Should be connected with the negative supply voltage pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDD                                                | 4 6                             | Input                                     | Should be connected with the positive supply voltage pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P 0 0<br>↓<br>P 0 7                                | 9 3<br>↓<br>1 0 0               | Input/<br>output                          | Eight-bit input/output port with internal pull-up transistors.  Data can be input/output from/to the port in 8-bit units.                                                                                                                                                                                                                                                                                                                                                               |

| P 1 0<br>↓<br>P 1 7                                | 7 6<br>↓<br>8 3                 | Input/<br>output                          | Eight-bit input/output port with internal pull-up transistors.  Data can be input/output from/to the port in bit units.                                                                                                                                                                                                                                                                                                                                                                 |

| P 1 0<br>P 1 1<br>P 1 2<br>P 1 3                   | 7 6<br>7 7<br>7 8<br>7 9        | Input<br>Input<br>Input<br>Input          | Port pins 76 to 79 can be also used as the external signal input pins:  T0: External signal input pin to timer/counter 0.  T1: External signal input pin to timer/counter 1.  INTO: External interrupt 0 input pin  INTI: External interrupt 1 input pin                                                                                                                                                                                                                                |

| P 2 0<br>↓<br>P 2 4<br>P 2 6<br>P 2 7              | 6 9<br>7 3<br>7 4<br>7 5        | Input/<br>output                          | Seven-bit input/output port with internal pull-up transistors. Data can be input/output from/to the port in bit units.                                                                                                                                                                                                                                                                                                                                                                  |

| P30<br>↓<br>P35                                    | 6 3<br>↓<br>6 8                 | Input/<br>output                          | Six-bit input/output port with internal pull-up transistors.  Data can be input/output from/to the port in bit units.                                                                                                                                                                                                                                                                                                                                                                   |

| P 4 0<br>↓<br>P 4 7                                | 5 5<br>↓<br>6 2                 | Input/<br>output                          | Eight-bit input/output port with internal pull-up transistors. Data can be input/output from/to the port in bit units.                                                                                                                                                                                                                                                                                                                                                                  |

| P 4 0<br>P 4 1<br>P 4 2<br>P 4 3<br>P 4 4<br>P 4 5 | 5 6<br>5 7<br>5 8<br>5 9<br>6 0 | Output Output Output Output Output Output | Port pins 55 to 60 can be also used as the special output pins:  CL1: Latch signal output to external Liquid Crystal Display driver circuit  CL2: Shift signal output to external Liquid Crystal Display driver circuit  D0: Data signal output to external Liquid Crystal Display driver circuit  M: Synchronization signal output to external Liquid Crystal Display driver circuit  ALM: Alarm signal output to the ALM output pin  PLS: Pulse signal output to the pulse output pin |

| V 1<br>↓<br>V 5                                    | 4 1<br>↓<br>4 5                 | Input/<br>output                          | Voltage supply pins to Liquid Crystal Display drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C 1                                                | 5 4<br>↓<br>4 7                 | Output                                    | Common driver pins to Liquid Crystal Display drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Continued on next page.

# LC86108A

Continued from preceding page.

| Pin name          | Pin<br>number | I/O    | Function description                                                                                                                                                  |  |  |  |

|-------------------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| S 1<br>↓<br>S 4 0 | 1<br>↓<br>4 0 | Output | Segment driver pins to Liquid Crystal Display.                                                                                                                        |  |  |  |

| RST               | 8 4           | Input  | Reset signal input pin with an internal pull-up transistor.                                                                                                           |  |  |  |

| Т1                | 8 5           | Output | Should be left unconnected.                                                                                                                                           |  |  |  |

| Т 2               | 8 6           | Output | Should be left unconnected.                                                                                                                                           |  |  |  |

| Т3                | 8 7           | Output | Should be connected with the VDD pin.                                                                                                                                 |  |  |  |

| XT1               | 8 8           | Input  | Crystal oscillation input pin. Should be connected with the Crystal (X'tal) resonator.                                                                                |  |  |  |

| XT2               | 8 9           | Output | Crystal oscillation output pin. Should be connected with the Crystal (X'tal) resonator.  The internal 20pF capacitor is provided between the XT2 pin and the VSS pin. |  |  |  |

| CF1               | 9 1           | Input  | Ceramic resonator oscillation input pin. Or RC (Resistor and Capacitor) oscillation input pin.                                                                        |  |  |  |

| CF2               | 9 2           | Output | Ceramic resonator oscillation output pin. Or RC (Resistor and Capacitor) oscillation output pin.                                                                      |  |  |  |

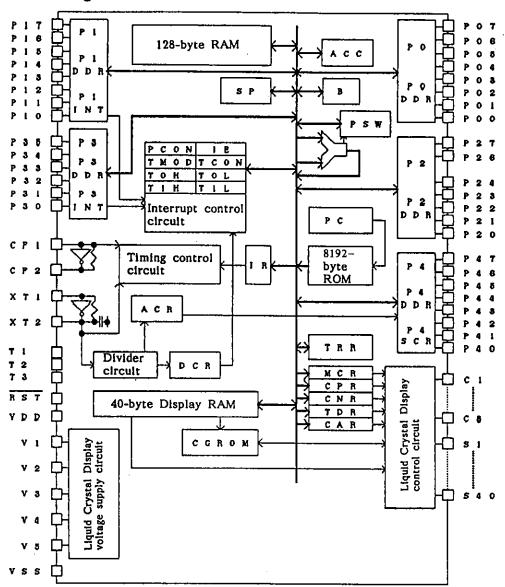

# Functional block diagram

| ACC     | ACCUMULATOR                                              | IE    | INTERRUPT ENABLE REGISTER           |

|---------|----------------------------------------------------------|-------|-------------------------------------|

| В       | ACCUMULATOR B REGISTER PROGRAM STATUS WORD STACK POINTER | TMOD  | TIMER/COUNTER MODE CONTROL REGISTER |

| PS\     | PROGRAM STATUS WORD                                      | TCON  | TIMER/COUNTER CONTROL REGISTER      |

| SP      | STACK POINTER                                            | тон   | TIMER/COUNTERO HIGH BYTE            |

| TRL     | TABLE REFERENCE REGISTER LOW BYTE                        |       | TIMER/COUNTERO LOW BYTE             |

| TRH     | TABLE REFERENCE REGISTER HIGH BYTE                       | TlH   | TIMER/COUNTER1 HIGH BYTE            |

| P0      | PORTO LATCH                                              | TlL   | TIMER/COUNTER1 LOW BYTE             |

| PODDR   | PORTO DATA DIRECTION REGISTER                            | PCON  | POWER CONTROL REGISTER              |

| P1      | PORT1 LATCH                                              | PC    | PROGRAM COUNTER                     |

| PIDDR   | PORTI DATA DIRECTION REGISTER                            | IR    | INSTRUCTION REGISTER                |

| Plint   | PORT1 INTERRUPT REGISTER                                 | MCR   | MODE CONTROL REGISTER               |

| P2      | PORT2 LATCH                                              | CPR   | CHARACTER PITCH REGISTER            |

| P2DDR   | PORT2 DATA DIRECTION REGISTER                            | CNR   | CHARACTER NUMBER REGISTER           |

| P3      | PORT3 LATCH                                              |       | TIME DIVISION REGISTER              |

| P3DDR   | PORT3 DATA DIRECTION REGISTER                            |       | CURSOR ADDRESS REGISTER             |

| P3 I NT | PORT3 INTERRUPT REGISTER PORT4 LATCH                     | DR    | DISPLAY RAM                         |

| P4      | PORT4 LATCH                                              | CGROM | CHARACTER GENERATOR ROM             |

| P4DDR   | PORT4 DATA DIRECTION REGISTER                            | ACR   | ALARM CONTROL REGISTER              |

| P4SCR   | PORT4 SIGNAL CHANGE REGISTER                             | DCR   | DIVIDER CONTROL REGISTER            |

|         |                                                          |       |                                     |

#### LC86108A

| Symbol | Address | Read/write | Name         | Initial reset value |

|--------|---------|------------|--------------|---------------------|

| _      | -       | -          | Memory space | _                   |

(1) Program memory (ROM) space

The LC86000 series microcomputers have a program memory (ROM) space of 64K bytes.

(2) Data memory (RAM) space

The LC86000 series microcomputers have a data memory (RAM) space of 512 bytes. The 512-byte RAM area can be functionally divided into the two areas: 256-byte data memory (RAM: 000H to 0FFH)) and 256-byte special function register (SFR) area (100H to 1FFH).

The 256-byte RAM area includes the stack area and the SFR area contains the accumulator (ACC), the program status word (PSW), timers, ports and the like. The SFR area allows the LC86000 series microcomputers to employ the full memory mapped I/O architecture.

The first 4 address areas (00H to 03H) in the data memory (RAM) can be used as the four 8-bit indirect address registers for allowing the user to make an access to the RAM in the indirect address mode. Of the above 4 indirect address registers, the first two registers with addresses 00H and 01H are used when the RAM area between address 00H and FFH is indirectly accessed. The remaining two index registers are used when the SFR area between address 100H and address 1FFH is indirectly accessed.

Bits 3 and 4 of the program status word (PSW) can be used with the indirect address registers to select 4 RAM banks.

The relationship between the indirect address registers, bits 3 and 4 of the PSW and the RAM addresses is shown in the table below.

| PSW<br>bit 4 | PSW<br>blt 3 | Indirect<br>address<br>register | RAM<br>address | Function                |

|--------------|--------------|---------------------------------|----------------|-------------------------|

|              |              | R 0                             | 0 0 H          | Indirect RAM addressing |

| 0            | 0            | R 1                             | 0 1 H          | Indirect RAM addressing |

|              |              | R 2                             | 0 2 H          | Indirect SFR addressing |

|              |              | R 3                             | 0 3 H          | Indirect SFR addressing |

|              |              | R 0                             | 0 4 H          | Indirect RAM addressing |

| 0            | ,            | R 1                             | 0 5 H          | Indirect RAM addressing |

| 0            | 1            | R 2                             | 0 6 H          | Indirect SFR addressing |

|              |              | R 3                             | 0 7 H          | Indirect SFR addressing |

|              |              | R 0                             | 0 8 H          | Indirect RAM addressing |

| ,            | 0            | R 1                             | 0 9 H          | Indirect RAM addressing |

| 1            | 0            | R 2                             | 0 A H          | Indirect SFR addressing |

|              |              | R 3                             | 0 B H          | Indirect SFR addressing |

|              |              | R 0                             | 0 C H          | Indirect RAM addressing |

| ,            | 1            | R 1                             | 0 D H          | Indirect RAM addressing |

| 1            |              | R 2                             | 0 E H          | Indirect SFR addressing |

|              |              | R 3                             | 0 F H          | Indirect SFR addressing |

| Symbol | Address | Read/write | Name            | Initial reset<br>value |

|--------|---------|------------|-----------------|------------------------|

| PC     | _       |            | Program counter | 0 0 0 0 Н              |

The program counter (PC) is a 16-bit register. It is used to point to the address in the program memory (ROM), which stores the next instruction to be executed. Normally, the content of the program counter (PC) is incremented by 1 each time one instruction is executed. However, the PC register will be loaded with predefined address data when branch instruction or subroutine instruction is executed in your application program.

In addition to this, the PC content will change according to interrupt requests and the initial reset request.

The table below shows the contents of the program counter (PC) when the above mentioned operations are performed.

| Operation type                  | <b>:</b>                                 |       | Program counter value                                |  |  |  |  |

|---------------------------------|------------------------------------------|-------|------------------------------------------------------|--|--|--|--|

| Initial reset                   |                                          |       | 0000Н                                                |  |  |  |  |

| External interr                 | upt 0                                    |       | 0 0 0 3 H                                            |  |  |  |  |

| Timer/counter                   | 0 interrupt                              |       | 0 0 0 B H                                            |  |  |  |  |

| External interr                 | upt 1                                    |       | 0 0 1 3 H                                            |  |  |  |  |

| Timer/counter                   | 1 interrupt                              |       | 0 0 1 B H                                            |  |  |  |  |

|                                 | Divider circuit/port 1/ port 3 interrupt |       | 0 0 2 3 H                                            |  |  |  |  |

|                                 | JMP                                      | a 1 2 | PC15 $\sim$ 12=Current page, PC11 $\sim$ 00=a12      |  |  |  |  |

| Unconditional branching         | JMPF                                     | a 1 6 | PC15~00=a16                                          |  |  |  |  |

| operation                       | BR                                       | r 8   | $(PC+2) + (-128 \sim +127)$                          |  |  |  |  |

|                                 | BRF                                      | r 1 6 | (PC+2) + (0~+65536)                                  |  |  |  |  |

| Conditional branching operation | BZ r 8                                   | 3     | $(PC+2) + (-128 \sim +127)$                          |  |  |  |  |

|                                 | CALL                                     | a 1 2 | PC15 $\sim$ 12 = Current page, PC11 $\sim$ 00 = a 12 |  |  |  |  |

| Subroutine all operation        | CALLF                                    | a 1 6 | PC15~00=a16                                          |  |  |  |  |

|                                 | CALLR                                    | r 1 6 | (PC+2) + (0~+65536)                                  |  |  |  |  |

Note: The current page indicates the page area storing the instruction to be executed next.

| Symbol | Address | Read/write | Name           | Initial reset<br>value |

|--------|---------|------------|----------------|------------------------|

| ROM    |         | Read only  | Program memory |                        |

The program memory is an 8K-byte ROM (8192 x 8 bits). It stores a user application program to be executed on the LC86108A microcomputer. The whole content of the program memory (ROM) can be referenced by using the LDC instruction.

| Symbol | Address             | Read/write | Name        | Initial reset |

|--------|---------------------|------------|-------------|---------------|

| RAM    | 0 0 H<br>↓<br>7 F H | Read/write | Data memory | Unpredictable |

The data memory is a 128-byte static RAM (128 x 8 bits). The first four bytes (00H to 03H) of the RAM are used as the indirect address registers for indirect addressing. The first two indirect address registers (00H and 01H) of the four are used for indirect RAM addressing and the remaining two registers (02H and 03H) for indirect special function register (SFR) addressing. In addition, these indirect address registers can be used with bits 3 and 4 of the program status word (PSW) to select 4 banks.

| Symbol | Address | Read/write | Name    | Name |       |       | reset |

|--------|---------|------------|---------|------|-------|-------|-------|

| ACC    | 100H    | Read/write | Accumul | ator | 0 0 Н | 0 0 H |       |

| MSB    |         |            |         |      |       |       | LSB   |

| ACC7   | ACC6    | ACC5       | ACC4    | ACC3 | ACC2  | ACC1  | ACC0  |

The accumulator (ACC) is a register used for calculation (logical or arithmetic), data transfer and data input/output.

Note: If the current content of the accumulator (ACC) is transferred to the ACC itself, the data in the accumulator (ACC) will be destroyed. For example, this may happen if you use the LD ACD instruction in your application program.

| Symbol | Address | Read/write | Name    | Name        |       |                   | al<br>: value |  |

|--------|---------|------------|---------|-------------|-------|-------------------|---------------|--|

| PSW    | 101H    | Read/write | Program | status word | 0 0 × | 0 0 × 0 0 0 × × B |               |  |

| MSB    |         |            |         |             |       | <u> </u>          | LSB           |  |

| CY     | A C     | _          | IRBK1   | IRBK0       | OV    | _                 | _             |  |

CY: Carry flag

The carry flag (CY) is a flag which is set or reset when arithmetic operation is carried out. The carry flag (CY) will be set when an addition type instruction is executed in your application program and then a carry from the most significant bit (MSB) occurs. It will be reset when an addition type instruction is executed in your application program but a carry from the most significant bit (MSB) does not occur.

The carry flag (CY) will be set when a subtraction type or comparison type instruction is executed in your application program and a borrow to the most significant bit (MSB) occurs. It will be reset when a subtraction type or comparison type instruction is executed in your application program and a borrow to the most significant bit (MSB) does not occur. In addition, the carry flag (CY) will be affected when a carry-through rotation type instruction is executed in your application program. It will be reset when an

multiplication/division type instruction is executed in your application program.

AC: Auxiliary Carry Flag

The auxiliary carry flag (AC) is a flag which is set or reset when arithmetic operation instruction is executed in your application program.

The auxiliary carry flag (AC) will be set when an addition type instruction is executed in your application program and a carry from the third bit occurs. It will be reset when an addition type instruction is executed in your application program but a carry from the third bit does not occur.

The auxiliary carry flag (AC) will be set when a subtraction type instruction is executed in your application program and a borrow to the third bit occurs. It will be reset when a subtraction type instruction is executed in your application program but a borrow to the third bit does not occur.

IRBK1: Indirect address register bank 1 IRBK0: Indirect address register bank 0

These two bits (IRBKO and IRBK1) of the program status word (PSW) are used to select 4 bank

values for the indirect address registers.

As previously stated, the first 4 bytes of the RAM are used as the four indirect address registers for indirect addressing. Bits IRBK0 and IRBK1 can be jointly used with these four indirect address registers to make an indirect access to an address in a selected RAM bank area. For detailed information, please refer to Memory Space.

OV: Overflow flag

The overflow flag (OV) is a flag which is set or reset when an addition type or subtraction type instruction with signed variables is executed in your application program.

The overflow flag (OV) will be set when an addition type or subtraction type instruction with signed variables is executed in your application program and an overflow error then occurs. Otherwise it will be reset.

The overflow flag (OV) will be set when a multiplication type instruction is executed in your application program and the resulted product exceeds 256. It will be reset if the resulted product is less than 256.

In addition, the overflow flag (OV) will be set when a division type instruction is executed in your application program and the divisor is "0". Otherwise, it will not be affected.

| Symbol | Address | Read/write | Name     |     | ,   | Initia<br>reset | l<br>value |

|--------|---------|------------|----------|-----|-----|-----------------|------------|

| В      | 102H    | Read/write | B regist | er  | 00Н | 0 0 H           |            |

| MSB    |         |            |          |     |     |                 | LSB        |

| В7     | В 6     | B 5        | B 4      | В 3 | B 2 | B 1             | В 0        |

The B register is paired with the accumulator (ACC) and then used when a multiplication type or division type instruction is executed in your application program. In other operations, this register can be used as a general purpose register.

| Symbol | Address | Read/write | Name        | Name                    |      |       | value |

|--------|---------|------------|-------------|-------------------------|------|-------|-------|

| TRL    | 104H    | Read/write | Table re    | eference reg<br>er byte | 00Н  | 0 0 H |       |

| MSB    |         |            | <del></del> |                         |      |       | LSB   |

| TRL7   | TRL6    | TRL5       | TRL4        | TRL3                    | TRL2 | TRL1  | TRLO  |

The table reference register low-order byte is used to hold the low-order byte of a ROM address specified by the LDC instruction. This 8-bit register can be used as a general purpose register when any instruction other than the LDC instruction is executed in your application program.

| Symbol | Address | Read/write | Name                 |                        |      |       | reset |  |

|--------|---------|------------|----------------------|------------------------|------|-------|-------|--|

| TRH    | 105H    | Read/write | Table re<br>high-ord | ference reg<br>er byte | 00Н  | 0 0 H |       |  |

| MSB    |         |            |                      |                        |      |       | LSB   |  |

| TRH7   | TRH6    | TRH5       | TRH4                 | ткнз                   | TRH2 | TRH1  | TRH0  |  |

The table reference register high-order byte is used to hold the high-order byte of a ROM address specified by the LDC instruction. This 8-bit register can be used as a general purpose register when any instruction other than the LDC instruction is executed in your application program.

| Symbol | Address | Read/write | Name     |        |               | Initial reset value |     |

|--------|---------|------------|----------|--------|---------------|---------------------|-----|

| S P    | 106H    | Read/write | Stack po | ointer | Unpredictable |                     |     |

| MSB    |         |            |          |        |               |                     | LSB |

| S P 7  | SP6     | SP5        | SP4      | SP3    | SP2           | SP1                 | SPO |

The stack pointer (SP) is incremented by 1 when the PUSH instruction is executed in your application program. It is decremented by 1 when the POP instruction is executed in your application program.

The stack pointer (SP) is incremented by 2 when the CALL instruction is used in your application program. It is decremented by 2 when the RET instruction is executed in your application program.

The stack pointer (SP) will be incremented by 2 when an interrupt request is accepted by the system, and will be decremented by 2 when the RETI instruction is executed at the end of the interrupt servicing routine. Note that the RETI instruction is used to transfer program execution back to the main routine from the interrupt service routine.

The stack pointer value will become unpredictable at power on.

Therefore, you should set an appropriate value in the stack pointer within the initial routine after power is applied.

| Symbol | Address | Read/write | Name      |               | Initial<br>reset | value     |       |  |

|--------|---------|------------|-----------|---------------|------------------|-----------|-------|--|

| PCON   | 107H    | Read/write | Power con | itrol registe | ×××              | ×××××000B |       |  |

| MSB    |         |            |           |               |                  |           | LSB   |  |

| _      | _       | _          | _         | _             | PCON2            | PCON1     | PCON0 |  |

PCON2: Power control register bit 2

0: Disable the INTO HOLD mode release request. Note that the INTO request signal becomes active when the L level voltage is applied to the P12 pin.

1: Enable the INTO HOLD mode release request. Note that the INTO request signal becomes active when the L level voltage is applied to the P12 pin. In this case, program execution will start when timer/counter 0 outputs an overflow signal. As stated in the preceding paragraph, the overflow signal from timer/counter 0 will start the program execution. Therefore, timer/counter 0 can be used to prevent program execution from entering abnormal state when it is restarted immediately after the HOLD mode is released. For this purpose, you have to set an appropriate data in timer/counter 0 in advance. As a result, program execution will be restarted after the wait time period defined by the data in timer/counter 0 elapses. Note that the oscillation stabilization time period requires such wait time period.

PCON1: Power control register bit 1

0: Disable the HOLD mode request.

1: Enable the HOLD mode request. The HOLD mode stops both of the CF/RC oscillation circuit and the X'tal oscillation circuit. The microcomputer is allowed to operate in the low current dissipation mode. That is, only the leakage current operates the LSI.

The HOLD mode can be released by the reset request signal or by applying L level voltage to the INTO (P12) pin with PCON2 = 1. In this case, the HOLD mode should be selected after all the interrupt requests are disabled. If you fail to follow this procedure, program may enter abnormal run state. Please keep it in mind.

PCON0: Power control register bit 0

0: Disable the HALT mode request.

1: Enable the HALT mode request. The HALT mode stops the program execution. This mode can be released by the reset request. It can be also released when an interrupt request is accepted by the system.

| Symbol | Address | Read/write | Name     |              | Initial reset |                                     |       |  |

|--------|---------|------------|----------|--------------|---------------|-------------------------------------|-------|--|

| IE     | 108H    | Read/write | Interrup | t enable con | 0 ××          | 0 ×× 0 0 0 0 0 B                    |       |  |

| MSB    |         |            |          |              |               | · · · · · · · · · · · · · · · · · · | LSB   |  |

| 1 E 7  | _       |            | IE4      | IE3          | 1 E 2         | I E 1                               | I E O |  |

IE7: Interrupt enable control register bit 7

0: Disable all the interrupt requests.

1: Enable all the interrupt requests selected by bits IE4 to IE0.

IE4: Interrupt enable control register bit 4

0: Disable an interrupt request from the divider circuit, port 1 or port 3.

1: Enable an interrupt request from the divider circuit, port 1 or port 3. --- Vectored address 23H

IE3: Interrupt enable control register bit 3

0: Disable the interrupt request from timer/counter 1.

1: Enable the interrupt request from timer/counter 1. --- Vectored address 1BH

IE2: Interrupt enable control register bit 2

0: Disable the external interrupt 1 request.

1: Enable the external interrupt 1 request. --- Vectored address 13H

IE1: Interrupt enable control register bit 1

0: Disable the interrupt request from timer/counter 0.

1: Enable the interrupt request from timer/counter 0. --- Vectored address 0BH IEO: Interrupt enable control register bit 0

0: Disable the external interrupt 0 request.

1: Enable the external interrupt 1 request. --- Vectored address 03H

Note: Some interrupt request flags are automatically reset or others are not automatically reset when interrupt requests are accepted by the system. These flags are as follows:

Interrupt flags to be automatically reset:

Timer/counter control register bit 7 (interrupt request by timer/counter 1)

Timer/counter control register bit 5 (interrupt request by timer/counter 0)

Timer/counter control register bit 3 (external interrupt 1) --- Falling edge detection mode

Timer/counter control register bit 1 (external interrupt 0) --- Falling edge detection mode

Interrupt request flags not to be automatically reset:

Timer/counter control register bit 3 (external interrupt 1) --- L level detection mode

Timer/counter control register bit 1 (external interrupt 0) --- L level detection mode

Divider circuit control register bit 1 (interrupt from the divider circuit)

Port 1 interrupt register bit 1 (interrupt from port 1)

Port 3 interrupt register bit 1 (interrupt from port 3)

Note: Timer/counter interrupt detection mode from the falling edge detection and L level signal detection modes is selected by software.

| Symbol | Address | Read/write | Name                           |       | Initial<br>reset |       |       |

|--------|---------|------------|--------------------------------|-------|------------------|-------|-------|

| TCON   | 1 1 0 H | Read/write | Timer/counter control register |       |                  | 0 0 Н |       |

| MSB    |         |            |                                |       |                  |       | LSB   |

| TCON7  | тсог    | N6 TCON5   | TCON4                          | TCON3 | TCON2            | TCON1 | TCON0 |

TCON7: Timer/counter control register bit 7

Timer/counter control register bit 7 is set when timer/counter 1 outputs an overflow signal and then automatically reset when an interrupt servicing routine is started.

TCON6: Timer/counter control register bit 6

0: Stop the timer/counter 1 operation.

1: Start the timer/counter 1 operation.

TCON5: Timer/counter control register bit 5

Timer/counter control register bit 5 is set when timer/counter 0 outputs an overflow signal and then automatically reset when an interrupt servicing routine is started.

TCON4: Timer/counter control register bit 4

0: Stops the timer/counter 0 operation.

1: Start the timer/counter 0 operation.

TCON3: Timer/counter control register bit 3

Timer/counter control register bit 3 is set when an external interrupt request signal from the INT1 pin is generated and then automatically reset when the interrupt servicing routine is started. Please note that this bit is automatically reset only when the falling edge detection mode has been selected.

TCON2: Timer/counter control register bit 2

Timer/counter control register bit 2 is used to select a desired INT1 interrupt detection mode from the falling edge detection and L level signal detection modes.

O: Select the L level signal detection mode.

1: Select the falling edge detection mode.

The H level signal before the interrupt request and the L level signal for triggering an interrupt should remain active for more than one machine cycles.

TCON1: Timer/counter control register bit 1

Timer/counter control register bit 1 is set when an external request signal from the INTO pin is generated and then automatically reset when the interrupt servicing routine is started. Please note this bit is automatically reset only if the falling edge detection mode has been selected.

TCON0: Timer/counter control register bit 0

Timer/counter control register bit 0 is used to select a desired INTO interrupt detection mode from the falling edge detection and L level signal detection modes.

0: Select the L level signal detection mode.

1: Select the falling edge detection mode.

The H level signal before the interrupt request and the L level signal for triggering an interrupt should remain active for more than one machine cycles.

| Symbol | Address | Read/write | Name                  |             | Initial reset |       |       |

|--------|---------|------------|-----------------------|-------------|---------------|-------|-------|

| TMOD   | 111H    | Read/write | Timer/cou<br>register | nter mode o | 0 0 H         |       |       |

| MSB    |         |            |                       |             |               |       | LSB   |

| TMOD   | TMO     | O 6 TMOD 5 | TMOD4                 | TMOD3       | TMOD2         | TMOD1 | TMOD0 |

TMOD7: Timer/counter mode control register bit 7

Timer/counter mode control register bit 7 is used to specify a desired input pulse to the timer/counter 1 gate.

0: Select the unconditional pulse input to the timer/counter 1 gate.

1: Select the conditional pulse input to the timer/counter 1 gate. In this case, pulses are input to timer/counter 1 only if the INT1 (P13) = H level. Otherwise, they are not input to the timer/counter 1 gate.

TMOD6: Timer/counter mode control register bit 6

Timer/counter mode control register bit 6 is used to select the operation mode of timer/counter 1 from the timer operation and counter operation.

0: Select the timer operation mode. In this operation mode, timer/counter 1 will increment its value by 1 for each machine cycle.

1: Select the event counter operation mode. In this operation mode, timer/counter 1 will count up the input clocks from the T1 (P11) pin.

TMOD5: Timer/counter mode control bit 5 TMOD4: Timer counter mode register bit 4

| Mode | TMOD5 | TMOD4 | Timer/counter 1 mode       |

|------|-------|-------|----------------------------|

| 0    | 0     | 0     | 13-bit timer/counter       |

| 1    | 0     | 1     | 16-bit timer/counter       |

| 2    | 1     | 0     | 8-bit reload timer/counter |

TMOD3: Timer/counter mode control register bit 3

Timer/counter mode control register bit 3 is used to specify a desired input pulse to the timer/counter 0 gate.

0: Select the unconditional pulse input to the timer/counter 0 gate.

1: Select the conditional pulse input to the timer/counter 0 gate. In this case, pulses are input to timer/counter 0 only if the INTO (P12) = H level. Otherwise, they are not input to the timer/counter 0 gate.

TMOD2: Timer/counter mode control register bit 2

Timer/counter mode control register bit 2 is used to select the operation mode of timer/counter 0 from the timer operation and counter operation.

0: Select the timer operation mode. In this operation mode, timer/counter 0 will increment its value by 1 for each machine cycle.

1: Select the event counter operation mode. In this operation mode, timer/counter 0 will count up the input clocks from the TO (P10) pin.

TMOD1: Timer/counter mode control bit 1 TMOD0: Timer counter mode register bit 0

| Mode | TMOD1 | TMOD0 | Timer/counter 0 mode                                                 |

|------|-------|-------|----------------------------------------------------------------------|

| 0    | 0     | 0     | 13-bit timer/counter 16-bit timer/counter 8-bit reload timer/counter |

| 1    | 0     | 1     |                                                                      |

| 2    | 1     | 0     |                                                                      |

| Symbol | Address | Read/write | Name     | Name                           |         |    |     | value |  |  |

|--------|---------|------------|----------|--------------------------------|---------|----|-----|-------|--|--|

| TOL    | 112H    | Read/write | Timer/co | Timer/counter 0 low-order byte |         |    |     | 0 0 H |  |  |

| MSB    |         |            |          |                                |         |    |     | LSB   |  |  |

| T0L7   | T0L6    | T0L5       | T 0 L 4  | T0L3                           | T 0 L 2 | Τ0 | L 1 | TOLO  |  |  |

| Symbol | Address | Read/write | Name                            | Name    |      |   |       | value |  |

|--------|---------|------------|---------------------------------|---------|------|---|-------|-------|--|

| тон    | 114H    | Read/write | Timer/counter 0 high-order byte |         |      |   | 0 0 Н |       |  |

| MSB    |         |            |                                 |         |      |   |       | LSB   |  |

| T.OH7  | T0H6    | T0H5       | T 0 H 4                         | T 0 H 3 | T0H2 | Т | 0 H 1 | Т0Н0  |  |

| Symbol | Address | Read/write | Name     | Name         |       |          |       | value |

|--------|---------|------------|----------|--------------|-------|----------|-------|-------|

| T1L    | 113H    | Read/write | Timer/co | ounter 1 lov | 0 0 H |          |       |       |

| MSB    |         |            |          |              |       | <u>t</u> |       | LSB   |

| T1L7   | T1L6    | T1L5       | T1L4     | T1L3         | T1L2  | T:       | 1 L 1 | T1L0  |

| Symbol | Address | Read/write | Name     | Name                            |      |     |   | value |  |  |

|--------|---------|------------|----------|---------------------------------|------|-----|---|-------|--|--|

| Т1Н    | 115H    | Read/write | Timer/co | Timer/counter 1 high-order byte |      |     |   | 0 0 H |  |  |

| MSB    |         |            |          |                                 |      |     |   | LSB   |  |  |

| Т1Н7   | T1H6    | T1H5       | T1H4     | Т1Н3                            | T1H2 | Т1Н | 1 | Т1Н0  |  |  |

| Symbol | Address | Read/write | Name     |       |       | Initial reset value |       |  |

|--------|---------|------------|----------|-------|-------|---------------------|-------|--|

| P 0    | 140H    | Read/write | Port 0 1 | atch  | FFH   | FFH                 |       |  |

| MSB    |         |            |          |       |       |                     | LSB   |  |

| P 0 7  | P 0 6   | P 0 5      | P 0 4    | P 0 3 | P 0 2 | P 0 1               | P 0 0 |  |

| Symbol | Address | Read/write Name Initial reset |          |             | Name |             |       |  |

|--------|---------|-------------------------------|----------|-------------|------|-------------|-------|--|

| PODDR  | 141H    | Write only                    | Port 0 d | ata directi | ×××  | ××××××× 0 B |       |  |

| мѕв    |         |                               |          | -           |      |             | LSB   |  |

|        | _       |                               | -        | _           | _    | _           | PODDR |  |

The port 0 data direction register is used to select a desired port 0 operation mode from the input and output modes in byte units.

PODDR 0: Int

0: Input mode

1: Output mode

Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol | Address | Read/write | Name   | Name         |       | Initial<br>reset value                |       |  |

|--------|---------|------------|--------|--------------|-------|---------------------------------------|-------|--|

| P 1    | 144H    | Read/write | Port 1 | Port 1 latch |       |                                       | FFH   |  |

| MSB    |         |            |        |              |       | · · · · · · · · · · · · · · · · · · · | LSB   |  |

| P 1 7  | P 1 6   | P 1 5      | P 1 4  | P 1 3        | P 1 2 | P 1 1                                 | P 1 0 |  |

The following port 1 pins can be used for special signal input.

| Port<br>name                     | Special signal input                                                                                                                                                    |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P 1 3<br>P 1 2<br>P 1 1<br>P 1 0 | External interrupt signal input (INT1) External interrupt signal input (INT0) External clock input to Timer/counter 1 (T1) External clock input to Timer/counter 0 (T0) |

| Symbol     | Address    | Read/write | Name       |               |            | Initial<br>reset | value      |  |

|------------|------------|------------|------------|---------------|------------|------------------|------------|--|

| P 1 D D R  | 145H       | Write only | Port 1 c   | lata directio | 0 0 H      | 0 0 H            |            |  |

| MSB        |            |            |            |               |            | -                | LSB        |  |

| P17<br>DDR | P16<br>DDR | P15<br>DDR | P14<br>DDR | P13<br>DDR    | P12<br>DDR | P11<br>DDR       | P10<br>DDR |  |

The port 1 data direction register is used to select a desired port 1 operation mode from the input and output modes in bit units.

P1XDDR (X: 0 to 7) 0: Input mode

1: Output mode

Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol       | Address  | Read/write | Name Port 1 interrupt control register |   |   | Initial reset value |     |  |

|--------------|----------|------------|----------------------------------------|---|---|---------------------|-----|--|

| PIINT        | 146H     | Read/write |                                        |   |   |                     |     |  |

| MSB          |          |            |                                        |   |   |                     | LSB |  |

| <del>-</del> | <u> </u> | _          | 1                                      | _ | _ | P1F                 | P1C |  |

PIF: Port 1 interrupt flag

The port 1 interrupt flag is set when an L level signal is applied to an input port pin of port 1. In this case, the input port pin of port 1 should be set to the input mode in advance. In addition, the port output latch, and port 1 interrupt control bit PIC should be also set beforehand.

P1C: Port 1 interrupt control bit

0: Disable the interrupt from port 1.

1: Enable the interrupt from port 1.

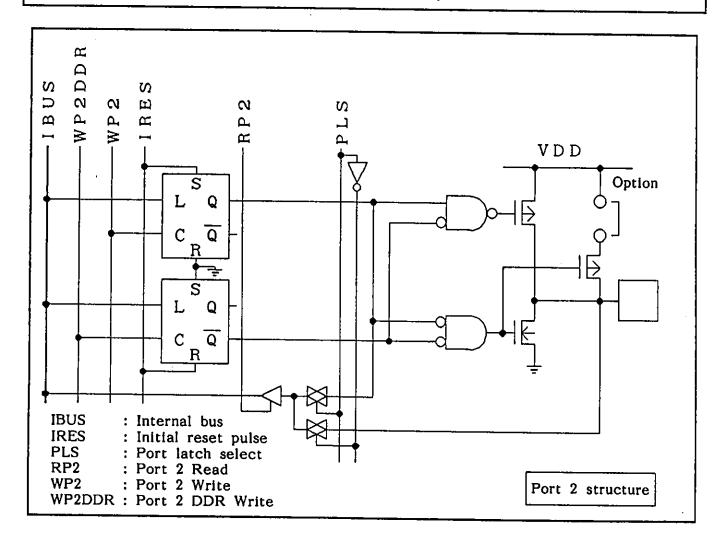

| Symbol | Address | Read/write | Name         |       |       |             | Initial reset value |  |  |

|--------|---------|------------|--------------|-------|-------|-------------|---------------------|--|--|

| P 2    | 148H    | Read/write | Port 2 latch |       |       | 1 1×        | 11×11111B           |  |  |

| MSB    |         |            | <u> </u>     |       |       | ·· <u> </u> | LSB                 |  |  |

| P 2 7  | P 2 6   |            | P 2 4        | P 2 3 | P 2 2 | P 2 1       | P 2 0               |  |  |

| Symbol     | Address    | Read/write | Name       |              |              |            | Initial reset value |  |

|------------|------------|------------|------------|--------------|--------------|------------|---------------------|--|

| P 2 D D R  | 149H       | Write only | Port 2     | data directi | 0 0 ×        | 00×00000B  |                     |  |

| MSB        |            |            |            |              |              |            | LSB                 |  |

| P27<br>DDR | P26<br>DDR | . —        | P24<br>DDR | P23<br>DDR   | P 2 2<br>DDR | P21<br>DDR | P20<br>DDR          |  |

The port 2 data direction register is used to select a desired port 2 operation mode from the input and output modes in bit units.

P2XDDR (X: 0 to 4,6,7) 0: Input

0: Input mode 1: Output mode

Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol | Address | Read/write | Name         |       |       |       | Initial reset value |  |  |

|--------|---------|------------|--------------|-------|-------|-------|---------------------|--|--|

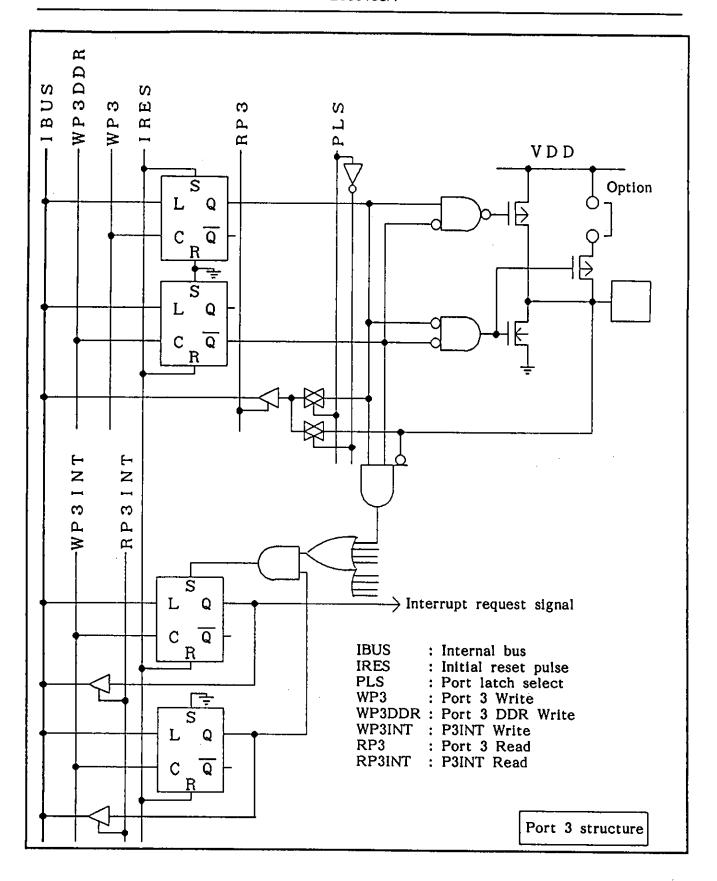

| Р3     | 14CH    | Read/write | Port 3 latch |       |       | ×× 1  | 11111B              |  |  |

| MSB    |         | _          |              |       |       |       | LSB                 |  |  |

| _      | -       | P 3 5      | P 3 4        | P 3 3 | P 3 2 | P 3 1 | P 3 0               |  |  |

| Symbol    | Address | Read/write | Name       |              |            | Initial reset | value      |

|-----------|---------|------------|------------|--------------|------------|---------------|------------|

| P 3 D D R | 14DH    | Write only | Port 3     | data directi | ×× 0       | ××000000B     |            |

| MSB       |         |            |            |              |            | 1             | LSB        |

| . —       |         | P35<br>DDR | P34<br>DDR | P33<br>DDR   | P32<br>DDR | P31<br>DDR    | P30<br>DDR |

The port 3 data direction register is used to select a desired port 3 operation mode from the input and output modes in bit units.

P3XDDR (X: 0 to 5)

0: Input mode

I: Output mode

Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol | Address    | Read/write | Name                                        | Name |   |         | Initial<br>reset value |  |  |

|--------|------------|------------|---------------------------------------------|------|---|---------|------------------------|--|--|

| P3INT  | 14EH       | Read/write | Port 3 interrupt control register ××××××00B |      |   |         |                        |  |  |

| MSB    | · <u>-</u> |            |                                             |      |   | <u></u> | LSB                    |  |  |

|        |            | _          | -                                           | _    | _ | P 3 F   | РЗС                    |  |  |

P3F: Port 3 interrupt flag

The port 3 interrupt flag is set when an L level signal is applied to an input port pin of port 1. In this case, the input port pin of port 3 should be set to the input mode in advance. In addition, the port output latch, and port 3 interrupt control bit P3C should be also set beforehand.

P3C: Port 3 interrupt control bit

0: Disable the interrupt from port 3.

1: Enable the interrupt from port 3.

## LC86108A

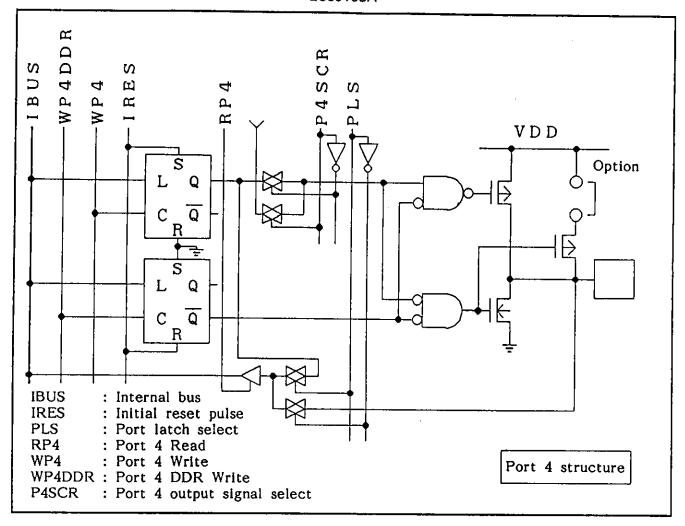

| Symbol | Address | Read/write | Name         |       |       | Initial reset value |       |

|--------|---------|------------|--------------|-------|-------|---------------------|-------|

| P 4    | 150H    | Read/write | Port 4 latch |       |       | FFH                 |       |

| MSB    |         |            |              |       |       |                     | LSB   |

| P 4 7  | P 4 6   | P 4 5      | P 4 4        | P 4 3 | P 4 2 | P 4 1               | P 4 0 |

The following port 4 pins can be used for special output function.

| Port pin name | Special output function                                                             |

|---------------|-------------------------------------------------------------------------------------|

| P 4 5         | Pulse output pin                                                                    |

| P 4 4         | Alarm output pin                                                                    |

| P 4 3         | External Liquid Crystal Display driver output pin (synchronization signal output M) |

| P 4 2         | External Liquid Crystal Display driver output pin (data signal output DO)           |

| P 4 1         | External Liquid Crystal Display driver output pin (shift signal output CL2)         |

| P 4 0         | External Liquid Crystal Display driver output pin (latch signal output CL1)         |

| Symbol     | Address    | Read/write   | Name       |              |            | Initial reset | value        |

|------------|------------|--------------|------------|--------------|------------|---------------|--------------|

| P 4 D D R  | 151H       | Write only   | Port 4     | data directi | 0 0 H      | 0 0 H         |              |

| MSB        |            |              |            |              |            | <u> </u>      | LSB          |

| P47<br>DDR | P46<br>DDR | P 4 5<br>DDR | P44<br>DDR | P43<br>DDR   | P42<br>DDR | P41<br>DDR    | P 4 0<br>DDR |

The port 4 data direction register is used to select a desired port 4 operation mode from the input and output modes in bit units.

P4XDDR (X: 0 to 7) 0: Input mode 1: Output mode Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol | Address | Read/write     | Name                                    | Name |  | Initial reset | value      |  |

|--------|---------|----------------|-----------------------------------------|------|--|---------------|------------|--|

| P4SCR  | 152H    | Write only     | Port 4 output signal selection register |      |  | ××0           | ××00×××0B  |  |

| MSB    |         |                |                                         |      |  |               | LSB        |  |

|        | _       | P 4 5<br>S C R | P44<br>SCR                              | _    |  | _             | P40<br>SCR |  |

P45SCR: P45 output signal selection bit

0: Select the P45 port latch output.

1: Select the pulse signal output.

P44SCR: P44 output signal selection bit

0: Select the P44 port latch output.

1: Select the alarm signal output. P40SCR: P40-P43 output signal selection bit

| P 4 0 ~ P 4 3 | P40SCR | Output signal                                                                                                                 |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| P 4 3         | 0      | Select the P43 port latch output.                                                                                             |

| P 4 2         | 0      | Select the external Liquid Crystal Display driver output (synchronization signal output M). Select the P42 port latch output. |

| P 4 1         | 1<br>0 | Select the external Liquid Crystal Display driver output (data signal output DO). Select the P41 port latch output.           |

|               | 1      | Select the external Liquid Crystal Display driver output (shift signal output CL2).                                           |

| P 4 0         | 0<br>1 | Select the P40 port latch output. Select the external Liquid Crystal Display driver output (latch signal output CL1).         |

Note: If you are to select the external Liquid Crystal Display driver output, please reset bit 0 of the mode control register to activate the character display mode.

Note: This register cannot be accessed by a bit manipulation instruction.

| Symbol | Address           | Read/write | Name        | Initial<br>reset value |

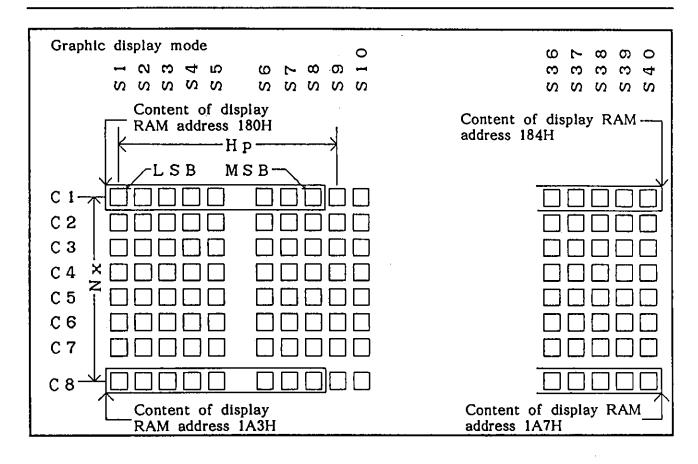

|--------|-------------------|------------|-------------|------------------------|

| DR     | 180H<br>↓<br>1A7H | Read/write | Display RAM | Unpredictable          |

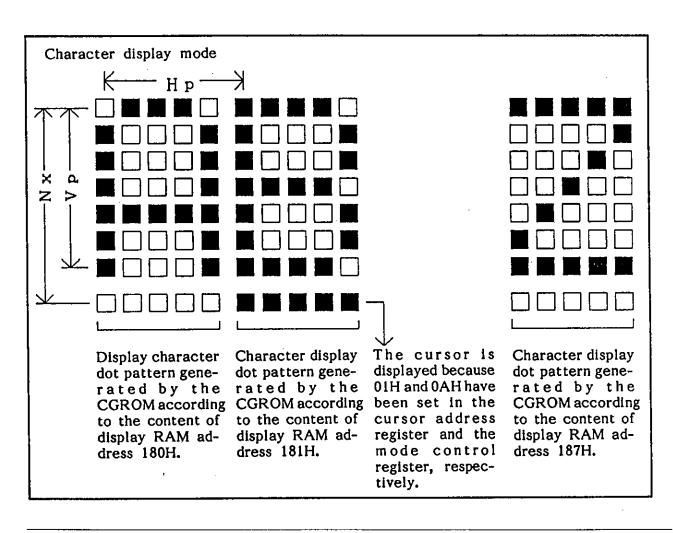

The display RAM is a static RAM with a capacity of 40 bytes (40 x 8 bits). The Liquid Crystal Display driver circuit receives the display data from the display RAM and then generates dot matrix Liquid Crystal Display driver signals. There are two types of Liquid Crystal Display modes available on the LC86108A microcomputer: Graphic display mode and Character display mode. In the graphic display mode, every single bit of the display RAM can be used to turn on/off a single Liquid Crystal Display dot. In the character display mode, the Internal character generator ROM is used to output a predefined dot character pattern to the Liquid Crystal Display driver circuit after receiving a character code already stored in the display RAM from the Liquid Crystal Display control circuit.

| Symbol       | Address | Read/write | Name                    | Initial<br>reset value |

|--------------|---------|------------|-------------------------|------------------------|

| C G<br>R O M | 4000    | ÷          | Character generator ROM | _                      |