# **Closed-Caption Decoder IC**

### Overview

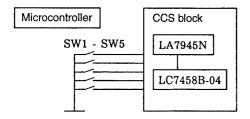

The LC7458B-04 is a closed-caption system (CCS) decoder and OSD display IC that conforms to the most recent American FCC standard issued on April 12, 1991. Together with an LA7945N Front End IC it forms a complete 2-chip system

#### **Features**

- FCC Standard Conforming signal Demodulation.

- Caption optional line display (new function).

- Color character display.

- Lower-case character display.

- Underline display.

- Flashing

- Italic display.

- Channel 1/Channel 2 mode switching and display.

- Field 1/Field 2 mode switching and display.

- Caption/Text mode switching and display.

- Control System

- Serial/Parallel signal mode switching.

- 5 parallel inputs or serial mode (PWM) interface selectable.

- Miscellaneous

- Supports 16 characters from the EIA-608 Optional Extended Character set.

- Automatic display ON/OFF.

- On-Screen Display positioning input pins.

- 5V supply voltage.

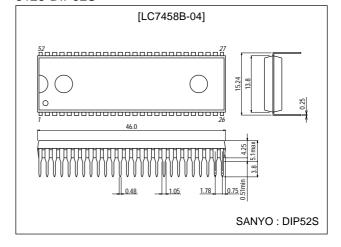

## **Package Dimensions**

unit:mm

3128-DIP52S

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges,or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

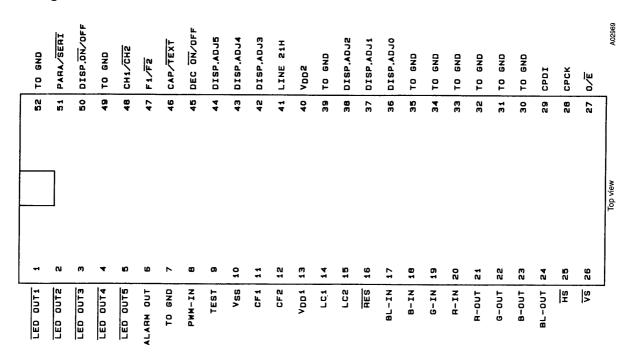

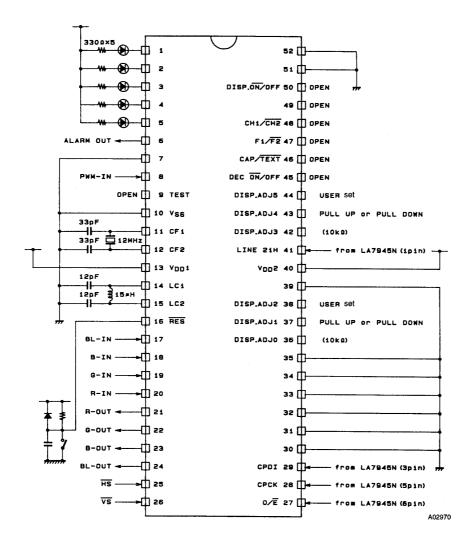

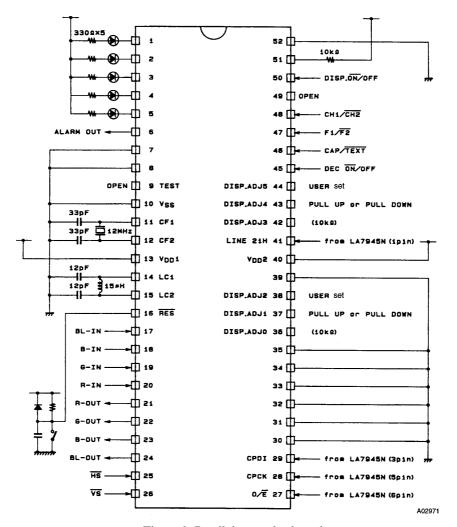

### **Pin Assignment**

#### **Pin Functions**

| Number | Name              | I/O | After reset <sup>1</sup> | Built-in resistance | Function description                                             | Connection when not in use |

|--------|-------------------|-----|--------------------------|---------------------|------------------------------------------------------------------|----------------------------|

| 1      | LED OUT1          | 0   | Hi-Z                     | Nch-OD              | Caption ON output (active low)                                   | GND                        |

| 2      | LED OUT2          | 0   | Hi-Z                     | Nch-OD              | Text ON output (active low)                                      | GND                        |

| 3      | LED OUT3          | 0   | Hi-Z                     | Nch-OD              | Channel 1 ON output (active low)                                 | GND                        |

| 4      | LED OUT4          | 0   | Hi-Z                     | Nch-OD              | Channel 2 ON output (active low)                                 | GND                        |

| 5      | LED OUT5          | 0   | Hi-Z                     | Nch-OD              | Field 2 mode output (active low)                                 | GND                        |

| 6      | ALARM OUT         | 0   | Hi-Z                     | Nch-OD              | Alarm signal output (active high)                                | GND                        |

| 7      | -                 | -   | -                        | -                   | Not used (tied to GND)                                           | GND                        |

| 8      | PWM-IN            | ı   | Hi-Z                     | Nch-OD              | PWM control signal input                                         | GND                        |

| 9      | TEST              | 0   | -                        | Pull-up             | Test pin (normally open)                                         | Open                       |

| 10     | V <sub>SS</sub>   | -   | -                        | -                   | Supply negetive pin                                              |                            |

| 11     | CF1               | I   | -                        | -                   | 12MHz ceramic filter oscillator element, system clock connection |                            |

| 12     | CF2               | 0   | -                        | -                   | 12MHz ceramic filter oscillator element, system clock connection |                            |

| 13     | V <sub>DD</sub> 1 | -   | -                        | -                   | Supply positive pin                                              |                            |

| 14     | LC1               | ı   | -                        | -                   | LC oscillator circuit input pin                                  |                            |

| 15     | LC2               | 0   | -                        | -                   | LC oscillator circuit output pin                                 |                            |

| 16     | RES               | I   | -                        | -                   | System reset input pin                                           |                            |

| 17     | BL-IN             | I   | Hi-Z                     | -                   | Blanking signal input pin (active high)                          | GND                        |

| 18     | B-IN              | I   | Hi-Z                     | -                   | RGB signal input pin (active high)                               | GND                        |

| 19     | G-IN              | ı   | Hi-Z                     | -                   | RGB signal input pin (active high)                               | GND                        |

| 20     | R-IN              | ı   | Hi-Z                     | -                   | RGB signal input pin (active high)                               | GND                        |

| 21     | R-OUT             | 0   | Low                      | -                   | RGB signal output pin (active high)                              | Open                       |

| 22     | G-OUT             | 0   | Low                      | -                   | RGB signal output pin (active high)                              | Open                       |

| 23     | B-OUT             | 0   | Low                      | -                   | RGB signal output pin (active high)                              | Open                       |

| 24     | BL-OUT            | 0   | Low                      | -                   | Blanking signal output pin (active high)                         | Open                       |

| 25     | HS                | - 1 | Hi-Z                     | -                   | Horizontal sync signal input pin (active low)                    |                            |

| 26     | VS                | - 1 | Hi-Z                     | -                   | Vertical sync signal input pin (active low)                      |                            |

| 27     | O/Ē               | 1   | Hi-Z                     | -                   | Field control pin (connects to LA7945)                           |                            |

| 28     | CPCK              | 1   | Hi-Z                     | -                   | Caption clock input pin (connects to LA7945)                     |                            |

| 29     | CPDI              | 1   | Hi-Z                     | -                   | Caption data input pin (connects to LA7945)                      |                            |

| 30     | -                 | _   | _                        | _                   | Not used (tied to GND)                                           | GND                        |

Continued on next page.

### Continued from preceding page.

| Number | Name              | I/O | After reset <sup>1</sup> | Built-in resistance | Function description                                   | Connection when not in use |

|--------|-------------------|-----|--------------------------|---------------------|--------------------------------------------------------|----------------------------|

| 31     | -                 | -   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

| 32     | -                 | -   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

| 33     | -                 | -   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

| 34     | -                 | -   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

| 35     | -                 | -   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

| 36     | DISP ADJ0         | I   | Hi-Z                     | Nch-OD              | OSC display start position adjust                      |                            |

| 37     | DISP ADJ1         | I   | Hi-Z                     | Nch-OD              | OSC display start position adjust                      |                            |

| 38     | DISP ADJ2         | I   | Hi-Z                     | Nch-OD              | OSC display start position adjust                      |                            |

| 39     | _                 | -   | -                        | _                   | Not used (tied to GND)                                 | GND                        |

| 40     | V <sub>DD</sub> 2 | -   | -                        | _                   | Supply positive pin                                    |                            |

| 41     | LINE 21H          | I   | Hi-Z                     | Nch-OD              | Line 21H sync signal input (connects to LA7945)        |                            |

| 42     | DISP ADJ3         | I   | Hi-Z                     | Nch-OD              | OSD display start position adjust                      |                            |

| 43     | DISP ADJ4         | I   | Hi-Z                     | Nch-OD              | OSD display start position adjust                      |                            |

| 44     | DISP ADJ5         | _   | Hi-Z                     | Nch-OD              | OSD display start position adjust                      |                            |

| 45     | DEC ON/OFF        | _   | High                     | Pull-up             | Parallel signal control, caption decode ON/OFF         | Open                       |

| 46     | CAP/TEXT          | I   | High                     | Pull-up             | Parallel signal control, caption/text switching        | Open                       |

| 47     | F1/F2             | I   | High                     | Pull-up             | Parallel signal control, field 1/field 2 switching     | Open                       |

| 48     | CH1/CH2           | I   | High                     | Pull-up             | Parallel signal control, channel 1/channel 2 switching | Open                       |

| 49     | -                 | -   | _                        | -                   | Not used (tied to GND)                                 | Open                       |

| 50     | DISP ON/OFF       | ı   | High                     | Pull-up             | Parallel signal control, caption display ON/OFF        | Open                       |

| 51     | PARA/SERI         | I   | Hi-Z                     | Nch-OD              | Parallel/serial control select                         |                            |

| 52     | _                 | ı   | -                        | -                   | Not used (tied to GND)                                 | GND                        |

<sup>1.</sup> Hi-Z=high impedance, Nch-OD=N-channel open-drain

# **Specifications**

# Maximum Ratings at Ta=25 $^{\circ}C,\,V_{SS}\!\!=\!\!0V$

| Parameter                                 | Cumphal             | Conditions                                        |         | Ratings              |                      |      |

|-------------------------------------------|---------------------|---------------------------------------------------|---------|----------------------|----------------------|------|

| Parameter                                 | Symbol              | Conditions                                        | min     | typ                  | max                  | Unit |

| Maximum supply voltage                    | V <sub>DD</sub> max | $V_{DD}$ , $V_{DD}V_{PP}$ : $V_{DD}=V_{DD}V_{PP}$ | -30     |                      | +7.0                 | V    |

| Input voltage                             | V <sub>I1</sub>     | RES, HS, VS, CPCK, CPDI, O/E, DISP, ADJ0 to 5,    |         | V <sub>DD</sub> +0.3 | V                    |      |

| Output voltage                            | V <sub>O1</sub>     | BL-OUT, R-OUT, G-OUT, B-OUT                       | -0.3    |                      | V <sub>DD</sub> +0.3 | V    |

| [Output high-level current]               |                     |                                                   |         |                      |                      |      |

|                                           | I <sub>OPH1</sub>   | LED OUT1 to 5, ALARM OUT (per pin)                |         |                      |                      | mA   |

| Peak output current (per pin)             | I <sub>OPH2</sub>   | BL-OUT, R-OUT, G-OUT, B-OUT, (per CMOS output)    | -5      |                      |                      | mA   |

| Total output current (total for all pins) | Σl <sub>OAH1</sub>  | LED OUT1 to 5, ALARM OUT (sum of all pins)        |         |                      |                      | mA   |

| Total output current (total for all pins) | Σl <sub>OAH2</sub>  | BL-OUT, R-OUT, G-OUT, B-OUT, (sum of all pins)    | -12     |                      |                      | mA   |

| [Output low-level current]                | ·                   |                                                   | •       |                      |                      |      |

| Peak output current (per pin)             | I <sub>OPL1</sub>   | LED OUT1 to 5, ALARM OUT (per pin)                |         |                      | 20                   | mA   |

| reak output current (per pin)             | I <sub>OPL2</sub>   | BL-OUT, R-OUT, G-OUT, B-OUT, (per pin)            |         |                      | 5                    | mA   |

| Total output current (total for all pins) | ΣlOAL1              | LED OUT1 to 5, ALARM OUT (sum of all pins)        |         |                      | 40                   | mA   |

| Total output current (total for all pins) | Σl <sub>OAL2</sub>  | BL-OUT, R-OUT, G-OUT, B-OUT, (sum of all pins)    |         |                      | 12                   | mA   |

| Maximum power dissipation                 | Pd max              | DIP52S : Ta=-30 to +70°C                          |         |                      | 430                  | mW   |

| Operating temperature                     | Topr                |                                                   | -30 +70 |                      | °C                   |      |

| Storage temperature                       | Tstg                |                                                   | -55     |                      | +150                 | °C   |

## Allowable Operating Ranges at Ta=-30 to +70°C, $V_{SS}$ =0V

| Parameter                                  | Symbol                                                                                                                | Conditions                                                                                                                                                                |                     | Ratings |                     |      |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|---------------------|------|

| Falametei                                  | Symbol                                                                                                                | Conditions                                                                                                                                                                | min                 | typ     | max                 | Unit |

| Operating supply voltage                   | V <sub>DD</sub>                                                                                                       | V <sub>DD</sub>                                                                                                                                                           | 4.5                 |         | 5.5                 | V    |

|                                            | V <sub>IH1</sub> PARA/SERI, DISP ON/OFF, CAP/TEXT, F1/F2, DEC ON/OFF, CH1/CH2 (Schmitt); V <sub>DD</sub> =4.5 to 5.5V |                                                                                                                                                                           | 0.6V <sub>DD</sub>  |         | V <sub>DD</sub>     | ٧    |

| Input high-level voltage                   | V <sub>IH2</sub>                                                                                                      | DISP ADJ0 to 5, HS, VS, O/E, CPCK, CPDI, LINE21, RES (Schmitt) ; V <sub>DD</sub> =4.5 to 5.5V                                                                             | 0.75V <sub>DD</sub> |         | V <sub>DD</sub>     | V    |

|                                            | V <sub>IH3</sub>                                                                                                      | BL-IN, B-IN, G-IN, R-IN : V <sub>DD</sub> =4.5 to 5.5V                                                                                                                    | 0.7V <sub>DD</sub>  |         | V <sub>DD</sub>     | V    |

|                                            | V <sub>IL1</sub>                                                                                                      | PARA/SERI, DISP ON/OFF, CAP/TEXT, F1/F2, DEC ON/OFF, CH1/CH2 (Schmitt); V <sub>DD</sub> =4.5 to 5.5V                                                                      | V <sub>SS</sub>     |         | 0.2V <sub>DD</sub>  | ٧    |

| Input low-level voltage                    | V <sub>IL2</sub>                                                                                                      | DISP ADJ0 to 5, $\overline{\text{HS}}$ , $\overline{\text{VS}}$ , $\overline{\text{O/E}}$ , CPCK, CPDI, LINE21, $\overline{\text{RES}}$ (Schmitt) ; $V_{DD}$ =4.5 to 5.5V | V <sub>SS</sub>     |         | 0.25V <sub>DD</sub> | V    |

|                                            | V <sub>IL3</sub>                                                                                                      | BL-IN, B-IN, G-IN, R-IN : V <sub>DD</sub> =4.5 to 5.5V                                                                                                                    | Vss                 |         | 0.3V <sub>DD</sub>  | V    |

| Oscillator frequency range <sup>1</sup>    | FmCF                                                                                                                  | CF1, CF2 ; 12MHz ceramic oscillator, see Figure 1, V <sub>DD</sub> =4.5 to 5.5V                                                                                           | 11.76               | 12      | 12.24               | MHz  |

| -                                          | FmLC                                                                                                                  | LC1, LC2; 12MHz LC oscillator, V <sub>DD</sub> =4.5 to 5.5V                                                                                                               |                     | 12      |                     | MHz  |

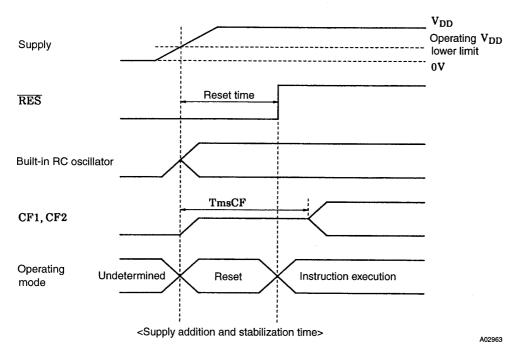

| Oscillator stabilization time <sup>2</sup> | TmsCF                                                                                                                 | CF1, CF2 ; 12MHz ceramic oscillator, see Figure 3, V <sub>DD</sub> =4.5 to 5.5V                                                                                           |                     | 0.02    | 0.2                 | ms   |

<sup>1.</sup> Oscillator constants are shown in Tables 1 and 2.

## **Electrical Characteristics** at Ta=-30 to +70°C, $V_{SS}=0V$

| Parameter                         | Symbol           | Symbol Conditions                                                                                                                                                                                            |                      | Ratings            |     |      |

|-----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-----|------|

| Parameter                         | Symbol           | Conditions                                                                                                                                                                                                   | min                  | typ                | max | Unit |

| Input high-level current          | I <sub>IH1</sub> | PARA/SERI, DISP ON/OFF, CAP/TEXT, CH1/CH2, F1/F2, DEC ON/OFF, DISP ADJ0 to 5, BL-IN, LINE21, B-IN, G-IN, R-IN, RES, HS, VS, O/E, CPCK, CPDI; V <sub>IN</sub> =V <sub>DD</sub> , V <sub>DD</sub> =4.5 to 5.5V |                      |                    | 1   | μΑ   |

| Input low-level current           | I <sub>IL1</sub> | PARA/SERI, DISP ON/OFF, CAP/TEXT, CH1/CH2, F1/F2, DEC ON/OFF, DISP ADJ0 to 5, BL-IN, LINE21, B-IN, G-IN, R-IN, RES, HS, VS, O/E, CPCK, CPDI; V <sub>IN</sub> =V <sub>SS</sub> , V <sub>DD</sub> =4.5 to 5.5V | -1                   |                    |     | μΑ   |

| Output high lovel veltage         | V <sub>OH1</sub> | R-OUT, G-OUT, B-OUT, BL-OUT, LED OUT1 to 5, ALARM OUT; I <sub>OH</sub> =-1.0mA, V <sub>DD</sub> =4.5 to 5.5V                                                                                                 | V <sub>DD</sub> -1   |                    |     | V    |

| Output high-level voltage         | V <sub>OH2</sub> | R-OUT, G-OUT, B-OUT, BL-OUT, LED OUT1 to 5, ALARM OUT; I <sub>OH</sub> =-0.1mA, V <sub>DD</sub> =4.5 to 5.5V                                                                                                 | V <sub>DD</sub> -0.5 |                    |     | V    |

|                                   | V <sub>OL1</sub> | LED OUT1 to 5, ALARM OUT; I <sub>OL</sub> =10mA, V <sub>DD</sub> =4.5 to 5.5V                                                                                                                                |                      |                    | 1.5 | V    |

| Output low-level voltage          | V <sub>OL2</sub> | LED OUT1 to 5, ALARM OUT; I <sub>OL</sub> =1.6mA, V <sub>DD</sub> =4.5 to 5.5V                                                                                                                               |                      |                    | 0.4 | V    |

|                                   | V <sub>OL3</sub> | R-OUT, G-OUT, B-OUT, BL-OUT; I <sub>OL</sub> =3.0mA, V <sub>DD</sub> =4.5 to 5.5V                                                                                                                            |                      |                    | 0.4 | V    |

| Pull-up MOS transistor resistance |                  | PARA/SERI, DISP ON/OFF, CAP/TEXT, CH1/CH2, F1/F2, DEC ON/OFF; V <sub>OH</sub> =0.9V <sub>DD</sub> , V <sub>DD</sub> =4.5 to 5.5V                                                                             | 13                   | 38                 | 80  | ΚΩ   |

| Hysteresis voltage                |                  | RES, HS, VS, O/E, CPCK, CPDI, PARA/SERI, DISPON/OFF, CAP/TEXT, CH1/CH2, F1/F2, DEC ON/OFF, DISP ADJ0 to 5, LINE21; V <sub>DD</sub> =4.5 to 5.5V                                                              |                      | 0.1V <sub>DD</sub> |     | V    |

| Pin capacitance                   | C <sub>P</sub>   | All pins <sup>1</sup> ; f=1MHz, V <sub>DD</sub> =4.5 to 5.5V                                                                                                                                                 |                      | 10                 |     | pF   |

<sup>1.</sup> All pins other than the pin measured have  $V_{IN}=V_{SS}$ , Ta=25°C

## Pulse Input Conditions at Ta=-30 to +70°C, $V_{SS}=0V$

| Parameter                                                    | Symbol                                 | Conditions                                                                                                       |     | Ratings |     |      |

|--------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| Falanetei                                                    | Symbol                                 | Conditions                                                                                                       | min | typ     | max | Unit |

|                                                              | TP <sub>IH1</sub><br>TP <sub>IL1</sub> |                                                                                                                  |     |         |     | Тсус |

| High/low-level pulse width                                   | TP <sub>IL2</sub>                      | RES; device can be reset, V <sub>DD</sub> =4.5 to 5.5V                                                           | 200 |         |     | μs   |

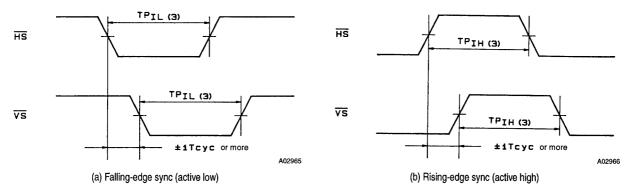

| riginion lete, palee mail                                    | TO <sub>IH2</sub><br>TP <sub>IL3</sub> | HS, VS; display position can be controlled. HS and VS active edges > 1 Tcyc apart, see Figure 5, VDD=4.5 to 5.5V | 2   |         |     | Тсус |

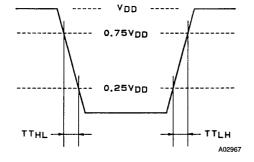

| Rise/fall transition time TT <sub>HL</sub> /TT <sub>LH</sub> |                                        | HS; see Figure 6, V <sub>DD</sub> =4.5 to 5.5V                                                                   |     |         | 500 | ns   |

<sup>2.</sup> The oscillator stabilization time is the time from the moment the supply is applied or main clock oscillation is resumed after a stop until the oscillations stabilize. See Figure 3.

## Current Drain Characteristics at Ta=-30 to +70°C, $V_{SS}=0V$

| Parameter |                                             | Symbol Conditions |                                                                                                                                          | Ratings |     |     | Unit  |

|-----------|---------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|-------|

|           | Falametei                                   | Symbol            | Conditions                                                                                                                               |         | typ | max | Offic |

|           | Normal operating current drain <sup>1</sup> | IDDOP1            | V <sub>DD</sub> ; FmCF=12MHz ceramic oscillator,<br>FmLC=12MHz LC oscillator, system clock : main<br>clock, V <sub>DD</sub> =4.5 to 5.5V |         | 15  | 25  | mA    |

<sup>1.</sup> The current drain does not include the output transistor and pull-up MOS transistor current.

Table1. Ceramic oscillator guaranteed constants (main clock)

| Oscillator type          | Manufacturer | Oscillator element | C1 <sup>1</sup> | C1 <sup>2</sup> |

|--------------------------|--------------|--------------------|-----------------|-----------------|

|                          |              | CSA12.0MTZ         | 33pF            | 33pF            |

| 12MHz ceramic oscillator | Murata       | CSA12.0MT          | 33pF            | 33pF            |

| 12MHZ Ceramic Oscillator |              | CST12.0MT          | Bui             | lt-in           |

|                          | Kyocera      | KBR-12.0M          | 33pF            | 33pF            |

<sup>1.</sup> C1 and C2 should be  $\pm 10\%$  K tolerance types with SL characteristics.

#### Table2. LC oscillator recommended constants (OSD clock)

| Oscillator type     | L    | C3   | C4   |

|---------------------|------|------|------|

| 12MHz LC oscillator | 12µH | 18pF | 18pF |

Note that the parts making up the oscillator should be mounted as close as possible with circuit patterns as short as possible to reduce the effects of the circuit pattern.

The oscillator characteristics above are not guaranteed for oscillator elements other than those listed.

Figure 1. Main clock (ceramic oscillator)

Figure 2. OSD clock (LC oscillator)

Figure 3. Oscillator stabilization time

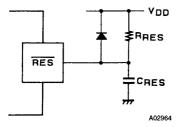

Note. Choose values for  $C_{RES}$  and  $R_{RES}$  such that the reset time is > 200  $\mu s.$

Figure 4. Reset circuit

Figure 5. Pulse input timing conditions 1

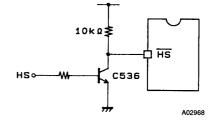

Figure 7. Recommended interface circuit

Figure 6. Pulse input timing conditions 2

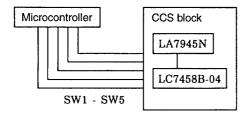

#### **Mode Control**

The LC7458B-04 allows, using a simple interface, a CCS function to be added to any of the existing television systems. The degree of freedom of using microcontroller input/output pins and different program changes mean that any one of three possible interfaces can be selected to best match design requirements. The LC7458B-04 interface methods can broadly be classified into two categories—direct control by external keys and indirect control using signals from a microcontroller.

The control method, parallel signal control (types 1 and 2) or pulse width signal (PWM) control (type 3), is selected by the level on pin 51 when power is applied.

High: Parallel signal control (types 1 and 2) Low: Pulse width signal (PWM) control (type 3)

Type 1: External Key Control

Changed microcontroller parameters:

1. Hardware

None

2. Software

None

If pin 50 (DISP  $\overline{ON}/OFF$ ) is tied to GND, then 4-key control is also possible. Note that pin 51 (PARA/ $\overline{SERI}$ ) is used pull-up.

Type 2: 5 Parallel input Control

Changed microcontroller parameters:

- 1. Hardware

- 5 output pins required

- 2. Software

Parallel signal generation

Note that pin 51 (PARA/SERI) is used pull-up.

Type 3: Pulse Width Signal (PWM)

Changed microcontroller parameters:

- 1. Hardware

- 1 output pin required

- 2. Software

- PWN control signal generation

Note that pin 51 (PARA/SERI) and pin 52 are connected to GND.

### **Parallel Input Control**

## DEC ON/OFF (pin 45)

Caption system decoder function ON/OFF switching

High: Caption OFF Low: Caption ON CAP/TEXT (pin 46) Caption/text switching

High: Caption

Low: Text

F1/F2 (pin 47)

Caption field switching

High: Field 1 Low: Field 2

## CH1/CH2 (pin 48)

Caption channel switching

High: Channel 1 Low: Channel 2

## DISP ON/OFF (pin 50)

Caption display ON/OFF switching

High: Caption display OFF Low: Caption display ON

Each switch should be lock-type with a chattering rejection

time of 60ms

#### **Parallel Input Mode Transitions**

|                   | Mode                                 |                                          |                |             |             |  |  |  |

|-------------------|--------------------------------------|------------------------------------------|----------------|-------------|-------------|--|--|--|

| Input             | TV mode<br>(captin OFF) <sup>1</sup> | Caption<br>CH1                           | Caption<br>CH2 | Text<br>CH1 | Text<br>CH2 |  |  |  |

| DEC ON/OFF        | High                                 | Low                                      | Low            | Low         | Low         |  |  |  |

| CAPTION/TEXT      | ×                                    | High                                     | High           | Low         | Low         |  |  |  |

| FIELD1/FIELD2     | ×                                    | FIELD1=High and FIELD2=Low for each mode |                |             |             |  |  |  |

| CHANNEL1/CHANNEL2 | ×                                    | High                                     | Low            | High        | Low         |  |  |  |

1. ×=don't care

Decoding commences when DEC  $\overline{ON}/OFF$  is ON. While DISP  $\overline{ON}/OFF$  is not ON, the caption is not displayed on the screen. Also if DISP  $\overline{ON}/OFF$  goes from ON to OFF while decoding, then decoding continues and the screen display is removed.

TV mode is restored after a reset.

## **Pulse Width Signal (PWM) Control**

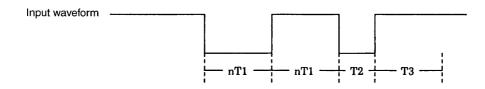

#### **PWM Timing**

2≤n≤10

T1: Command time (490 to 510µs)

T2: Command decision time (300 to 500µs)

T3: Input prohibit time (33ms)

#### **PWM Command Summary**

2T: Display stop

3T : Display re-start

4T : Caption channel 1

5T: Text channel 1

6T : Caption channel 2

7T : Text channel 2

8T:TV mode

9T: Field 1

10T : Field 2

## **LED Display Functions**

The LC7458B-04 has 5 built-in LED driver circuits which are used to indicate the different modes of operation.

## LED OUT1 (pin 1)

Caption mode when ON. Text mode or decoder when OFF.

## LED OUT2 (pin 2)

Text mode when ON. Caption mode or decoder when OFF.

#### LED OUT3 (pin 3)

Channel 1 selected when ON. Channel 2 selected or decoder when OFF.

### LED OUT4 (pin 4)

Channel 2 selected when ON. Channel 1 selected or decoder when OFF.

#### LED OUT5 (pin 5)

Field 2 selected when ON. Field 1 selected or decoder when OFF.

#### **Automatic Display ON/OFF**

The LC7458B-04 uses the presence of valid data on line 21H to automatically switch display ON/OFF to prevent the inadvertent display of erroneous captions. If 45 continuous instances of invalid data (parity error) are detected, the display is automatically removed. Then if 15 continuous instances of valid data is received, the display is restarted.

#### **Alarm Function**

If the caption data on line 21H is the alarm ON code, then ALARM OUT (pin 6) goes high. This condition is maintained until either an alarm OFF code is received or a decoder reset occurs.

## **OSD Display Start Positioning Function**

After a reset, the levels on DISP ADJ0 to DISP ADJ5 (pins 36 to 38 and 42 to 44) at the next horizontal sync signal HS rising edge determine the horizontal display start position out of a possible 64 positions.

The display start posision is given by

Start Position=[DISP ADJ5 to 0]×2×T<sub>LC</sub>

where T<sub>LC</sub> is the LC oscillator period.

### **Extended Characters**

Of the 64 EIA-608 Optional Extended Characters, the following 16 are supported.

| Data channel 1 | Data channel 2 | Symbol | Description                          | Also used for :            |

|----------------|----------------|--------|--------------------------------------|----------------------------|

| 12 20          | 1A 20          | Á      | Capital 'A' with acute accent        | Portuguese                 |

| 12 21          | 1A 21          | É      | Capital 'E' with acute accent        | French, Portuguese         |

| 12 22          | 1A 22          | Ó      | Capital 'O' with acute accent        | Portuguese                 |

| 12 23          | 1A 23          | Ú      | Capital 'U' with acute accent        | Portuguese                 |

| 12 24          | 1A 24          | Ü      | Capital 'U' with diaeresis or umlaut | French, German, Portuguese |

| 12 25          | 1A 25          | ü      | Small 'u' with diaeresis or umlaut   | French, German, Portuguese |

| 12 26          | 1A 26          | 4      | Opening single quote                 |                            |

| 12 27          | 1A 27          | i      | Inverted exclamation mark            |                            |

| 12 28          | 1A 28          | *      | Asterisk                             | ASCII                      |

| 12 29          | 1A 29          | 1      | Plain single quote                   |                            |

| 12 2A          | 1A 2A          | -      | em dash                              |                            |

| 12 2B          | 1A 2B          | ©      | Copyright symbol                     |                            |

| 12 2C          | 1A 2C          | SM     | Service mark symbol                  |                            |

| 12 2D          | 1A 2D          | •      | Round bullet                         |                            |

| 12 2E          | 1A 2E          | ar .   | Opening double quotes                |                            |

| 12 2F          | 1A 2F          |        | Closing double quotes                |                            |

## **Sample Application Circuits**

Figure 8. Serial (PWM) control interface

Figure 9. Parallel control selected

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of May, 2001. Specifications and information herein are subject to change without notice.