# LC7073, 7073M

# **Error Detection and Correction ICs for RDS Demodulators**

# **Preliminary**

## Overview

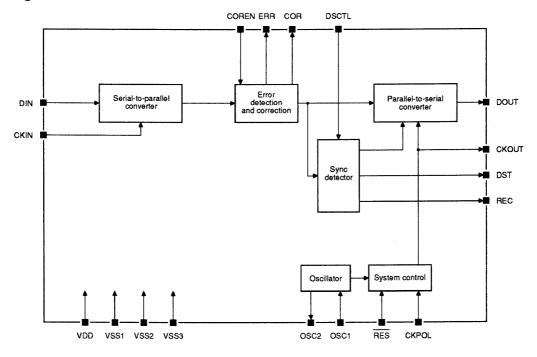

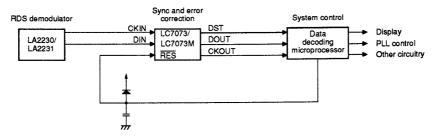

The LC7073 and LC7073M are error detection and correction ICs that provide an easy interface to the LA2230 and LA2231 radio data system (RDS) demodulators. Both devices incorporate an on-chip oscillator that connects directly to an external ceramic resonator.

The LC7073 and LC7073M provide group synchronization, selectable error detection and correction, output clock polarity selection, a block data start signal output and an error output that signals error correction failures.

The LC7073 and LC7073M operate from a 5 V supply and are available in 18-pin DIPs and MFPs, respectively.

# **Features**

- RDS error detection and correction.

- Easy interface with LA2230 and LA2231 demodulator ICs

- Serial data transfer system.

- Group synchronization capability.

- Selectable error detection and correction.

- Output clock polarity selection.

- Block data start output.

- Error output.

- On-chip oscillator.

- 5 V supply.

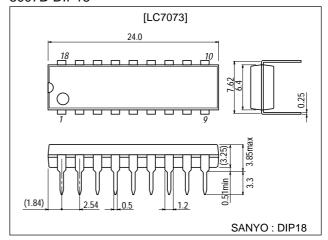

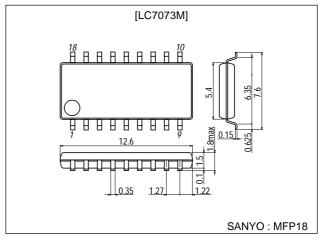

- 18-pin DIP (LC7073) and 18-pin MFP (LC7073M).

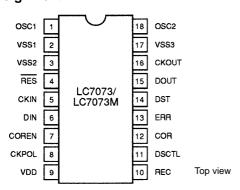

#### **Pin Assignment**

# **Package Dimensions**

unit:mm

3007B-DIP18

#### unit:mm

#### 3095-MFP18

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges,or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

# **Block Diagram**

# **Pin Function**

| Number | Name             | Equivalent circuit                      | Description                                                                                    |

|--------|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|

| 1      | OSC1             |                                         | External ceramic resonator connection 1                                                        |

| 2      | V <sub>SS1</sub> |                                         | Ground                                                                                         |

| 3      | V <sub>SS2</sub> |                                         | Ground                                                                                         |

| 4      | RES              | VDD<br>****                             | Schmitt-trigger reset input. Held LOW for a minimum of 4 clock cycles                          |

| 5      | CKIN             | <b>•</b>                                | Serial data input clock. Connects to RDS demodulator output clock                              |

| 6      | DIN              | *                                       | Serial data input. Connects to RDS demodulator data output                                     |

| 7      | COREN            | *************************************** | Error-correction enable input. LOW disables error correction and HIGH enables error correction |

Continued on next page.

# LC7073, 7073M

# Continued from preceding page.

| Number | Name             | Equivalent circuit | Description                                                                                                                                     |

|--------|------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | CKPOL            |                    | Serial data output clock polarity select input                                                                                                  |

| 9      | V <sub>DD</sub>  |                    | 5 V supply                                                                                                                                      |

| 10     | REC              |                    | Serial data receive detect output. LOW while receiving, after sync detection. High impedance when not receiving. High impedance after reset     |

| 11     | DSTCTL           | *                  | Data start control input. LOW initiates data start for second block, and HIGH, for all blocks                                                   |

| 12     | COR              |                    | Error-correction enabled/disabled output. LOW when error correction occurs and HIGH when no error correction occurs. High impedance after reset |

| 13     | ERR              |                    | Error-detect output. LOW when error correction fails. High impedance when error correction does not fail. High impedance after reset            |

| 14     | DST              | VDD VDD            | Serial data start output. LOW indicates no data start, and HIGH, data start. HIGH after reset                                                   |

| 15     | DOUT             | VDD VDD            | Serial data output. HIGH after reset                                                                                                            |

| 16     | скоит            | VDD VDD            | Serial data output clock                                                                                                                        |

| 17     | V <sub>SS3</sub> |                    | Ground                                                                                                                                          |

| 18     | OSC2             |                    | External ceramic resonator connection 2                                                                                                         |

# **Specifications**

# Absolute Maximum Ratings at $Ta=+25^{\circ}C,\,V_{SS1},\,V_{SS2},\,V_{SS3}=0V$

| Parameter                                       | Symbol              | Conditions           | Ratings                      | Unit |

|-------------------------------------------------|---------------------|----------------------|------------------------------|------|

| Maximum supply voltage                          | V <sub>DD max</sub> |                      | -0.3 to +7.0                 | V    |

| OSC2, DST, DOUT and CKOUT output voltage        | V <sub>O1</sub>     |                      | −0.3 to V <sub>DD</sub> +0.3 | V    |

| REC, COR and ERR output voltage                 | V <sub>O2</sub>     |                      | -0.3 to +15                  | V    |

| RES and OSC1 input voltage                      | V <sub>I1</sub>     |                      | -0.3 to V <sub>DD</sub> +0.3 | V    |

| CKIN, DIN, COREN, CKPOL and DSCTL input voltage | V <sub>I2</sub>     |                      | -0.3 to +15                  | V    |

| REC, COR and ERR output current                 | l <sub>01</sub>     |                      | 20                           | mA   |

| DST, DOUT and CKOUT output current              | I <sub>O2</sub>     |                      | -2 to +20                    | mA   |

| Output pins total current                       | lo                  |                      | -14 to +90                   | mA   |

| DIP allowable power dissipation                 | Pd max              | DIP: Ta=-40 to +85°C | to 280                       | mW   |

| MFP allowable power dissipation                 | Pd max              | MFP: Ta=-40 to +85°C | to 200                       | mW   |

| Operating temperature                           | Topr                |                      | -40 to +85                   | °C   |

| Storage temperature                             | Tstg                |                      | -55 to +125                  | °C   |

# $\textbf{Reommended Operating Conditions} \ \ at \ Ta = -40 \ to \ +85 ^{\circ}C, \ V_{SS1}, \ V_{SS2}, \ V_{SS3} = 0V, \ V_{DD} = 4.5 \ to \ 6.0V$

| Parameter                                                  | Symbol Conditions | Conditions | Ratings            |     |                     | Unit  |

|------------------------------------------------------------|-------------------|------------|--------------------|-----|---------------------|-------|

| r alametei                                                 |                   | Conditions | min                | typ | max                 | Offic |

| Supply voltage range                                       | $V_{DD}$          |            | 4.5                |     | 6.0                 | V     |

| CKIN, DIN, COREN, CKPOL and DSCTL high-level input voltage | V <sub>IH1</sub>  |            | 0.7V <sub>DD</sub> |     | 13.5                | V     |

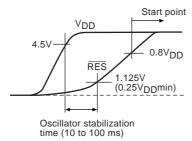

| RES and OSC1 high-level input voltage                      | V <sub>IH2</sub>  |            | 0.8V <sub>DD</sub> |     | $V_{DD}$            | V     |

| CKIN, DIN, COREN, CKPOL and DSCTL low-level input voltage  | V <sub>IL1</sub>  |            | V <sub>SS</sub>    |     | 0.3V <sub>DD</sub>  | V     |

| RES low-level input voltage                                | V <sub>IL2</sub>  |            | V <sub>SS</sub>    |     | 0.25V <sub>DD</sub> | V     |

# **Electrical Characteristics** at Ta = -40 to +85 °C, $V_{SS1}$ , $V_{SS2}$ , $V_{SS3} = 0V$ , $V_{DD} = 4.5$ to 6.0V

| Parameter                                                  | Symbol            | Conditions                          | Ratings              |                    |     | Unit  |

|------------------------------------------------------------|-------------------|-------------------------------------|----------------------|--------------------|-----|-------|

| Farameter                                                  | Symbol Conditions |                                     | min                  | typ                | max | Offic |

| CKIN, DIN, COREN, CKPOL and DSCTL high-level input current | I <sub>IH1</sub>  | V <sub>I</sub> =13.5V               |                      |                    | 5.0 | μΑ    |

| CKIN, DIN, COREN, CKPOL and DSCTL low-level input current  | I <sub>IL1</sub>  | V <sub>I=VSS</sub>                  | -1.0                 |                    |     | μΑ    |

| RES low-level input current                                | I <sub>IL2</sub>  | V <sub>I</sub> =V <sub>SS</sub>     | -45                  | -10                |     | μΑ    |

| DST, DOUT and CKOUT high-level output                      | VOH               | I <sub>OH</sub> =-50μA              | V <sub>DD</sub> -1.2 |                    |     | V     |

| voltage                                                    |                   | I <sub>OH</sub> =-10μA              | V <sub>DD</sub> -0.5 |                    |     | V     |

| REC, COR, ERR, DST, DOUT and CKOUT                         | VOL               | I <sub>OL</sub> =10mA               |                      |                    | 1.5 | V     |

| low-level output voltage                                   |                   | I <sub>OL</sub> =1.8mA, See note 1. |                      |                    | 0.4 |       |

| REC, COR and ERR output leakage current                    | lOFF              | V <sub>O</sub> =13.5V               |                      |                    | 5.0 | μA    |

| NEO, CON and ENN output leakage current                    |                   | V <sub>O</sub> =V <sub>SS</sub>     | -1.0                 |                    |     | μΑ    |

| RES hysteresis voltage                                     | V <sub>HYS</sub>  |                                     |                      | 0.1V <sub>DD</sub> |     | V     |

| Supply current                                             | I <sub>DD</sub>   | See note 2.                         |                      | 4                  | 10  | mA    |

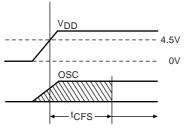

| Oscillator stabilization time                              | tCFS              | See figure 7.                       |                      |                    | 10  | ms    |

## Note

- 1. Idle pins have output currents less than 1mA.

- 2. Oscillator running, V<sub>I</sub>=V<sub>DD</sub>, I<sub>O</sub>=0mA

## **Timing Diagrams**

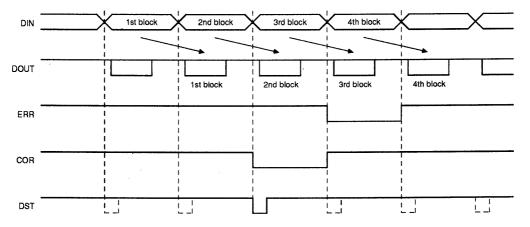

The relationship between the LC7073 and LC7073M input data (RDS demodulated data output) and output data is shown in figure 1.

Figure 1. Input and output data

#### Note

The dotted lines show data start (DST) pulses when the data start control (DSTCTL) is LOW. The serial output data is delayed by one block between input and output. The error (ERR) and correction (COR) signals remain active if errors are detected continually.

## **Serial Output Data Timing and Format**

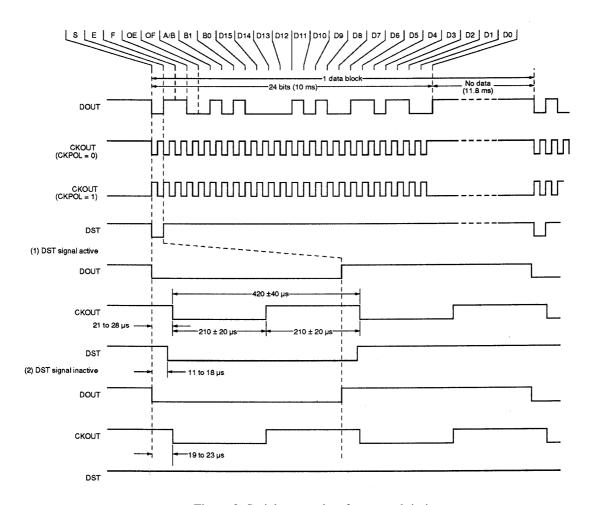

The following list shows the symbols used in the serial output data string in figure 2.

S Start bit (normally 0)

E Error flag (See table 1.)

F Correction flag (See table 1.)

OE Offset E (normally 0, not used)

OF Offset F (normally 0, not used)

A/B Group. 0–group A, 1–group B

B0, B1 Block bits. 00–1st block, 01–2nd block, 10–3rd block, 11–4th block

D0 to D15 Output data

Table 1. Error and correction flags

| Indication      | E | F |

|-----------------|---|---|

| No error        | 0 | 0 |

| Error corrected | 0 | 1 |

| Not correctable | 1 | × |

## Note

$\times$  = don't care

Figure 2. Serial output data format and timing

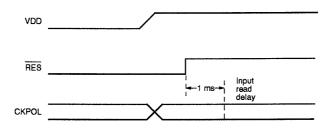

# **CKPOL Input Read Delay**

CKPOL is read 1 ms after a reset as shown in figure 3.

Figure 3. CKPOL input read delay

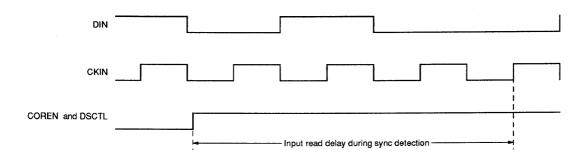

## **COREN and DSTCTL Input Read**

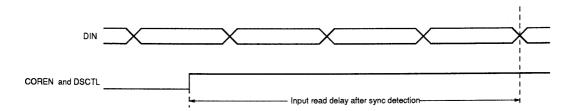

COREN and DSTCTL are monitored at intervals of one input clock cycle, and their logic states can be changed at any time. During sync detection, a change in input state occurs if either pin remains steady for four successive clock intervals as shown in figure 4.

Figure 4. Input read during sync detection

After sync detection a change in input state occurs if either COREN or DSTCTL remains steady for four successive input data blocks as shown in figure 5.

Figure 5. Input read after sync detection

## **Design Notes**

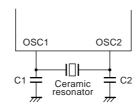

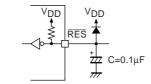

Oscillator specifications are shown in table 2 and figure 6. Oscillator stabilization delay is shown in figure 7. Reset input circuitry is shown in figure 8. Supply rise time versus  $\overline{RES}$  delay is shown in figure 9.

Table 2. Oscillator capacitor values

| 4 MHz resonator type | C1, C2     |

|----------------------|------------|

| Murata-CSA4.00MG     | 30 pF ±10% |

| Kyocera-KBR4.0M      | 30 pF ±10% |

Figure 6. Oscillator circuit

$t_{\mbox{CFS}}$  is the oscillator stabilization time

Figure 7. Oscillator stabilization delay

Figure 8. Reset input

Figure 9. Supply rise time vs. reset delay

A minimum delay of 10 ms should be allowed for oscillator stabilization. A 10 to 100 ms reset delay is generated using a 0.1 µF reset capacitor, C. A larger capacitor should be used if the supply rise time is longer.

Figure 10. System block diagram

# **Device Comparison**

The LC7070N, LC7070M and LC7071NM have identical basic functions, pinouts and input/output timing to those of the LC7073 and LC7073M. Their respective packages and output circuitry are compared in table 3.

Table 3. Device comparison

| Device   | Package    | Output type                      |

|----------|------------|----------------------------------|

| LC7070N  | 18-pin DIP | - Open-drain                     |

| LC7070NM | 18-pin MFP | open-urain                       |

| LC7071NM | 18-pin MFP |                                  |

| LC7073   | 18-pin DIP | Totem-pole using MOS transistors |

| LC7073M  | 18-pin MFP |                                  |

The differences in output data format between the LC7070N/LC7070NM/LC7071NM and LC7073/LC7073M are as follows.

#### Offset Words E and F

The LC7070N/LC7070NM/LC7071NM recognizes offset words E and F and performs group sync detection. The LC7073/LC7073M does not recognize offset words E and F—it only detects A, B, C, C' and D.

#### **Input Data Bits**

If all data bits are 0, the LC7070N/LC7070NM/LC7071NM only recognizes offset word E. The LC7073/LC7073M does not recognize the offset word E block. No sync detection occurs if all input data bits are 0. Once data cutoff has been determined, output data stops and the sync cutoff sequence begins.

# LC7073, 7073M

#### **Sync Detection Method**

The LC7070N/LC7070NM/LC7071NM searches for 5 consecutive blocks in the correct sequence within each group of 12 blocks. The LC7073/LC7073M searches for 2 consecutive blocks in the correct sequence within each group of 3 blocks.

## **Data Output After Sync Detection**

The LC7070N/LC7070NM/LC7071NM starts data output with the first block (offset A) directly after the last block in the sync detection group. If sync detection occurs during the first block (offset A), the LC7073/LC7073M starts data output with the second block (offset B). If sync detection occurs during the second or third block (offset B or C), and finishes before the end of the fourth block (offset D), the LC7073/LC7073M starts data output with the first block (offset A) of the second group.

## Sync Error

A sync error occurs if no offset word is detected for more than five consecutive blocks. This applies to both the LC7070N/LC7070NM/LC7071NM and LC7073/LC7073M.

## **Error Correction**

In error-correction mode, an error of less than 5 bits is corrected to an accuracy of 5 bits. This applies to both the LC7070N/LC7070NM/LC7071NM and the LC7073/LC7073M.

#### **Precaution**

Note that the solder-dip method should not be used for the LC7073M (MFP).

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of July, 2001. Specifications and information herein are subject to change without notice.