# L9947

# QUAD HALF-BRIDGE AND SINGLE HIGH-SIDE DRIVER

- LOW CONSUMPTION IN STANDBY MODE (<100μA AT ROM TEMP; < 150μA AT 130°C)

- TWO HALF BRIDGES FOR 3A LOAD  $(R_{DSON} = 0.25\Omega TYP; T_i = 25^{\circ}C)$

- TWO HALF BRIDGES FOR 0.5A LOAD  $(R_{DSON} = 2.5\Omega TYP; T_j = 25^{\circ}C)$

- HIGH SIDE DRIVER FOR 2.5A LOAD  $(R_{DSON} = 0.45\Omega TYP; T_i = 25^{\circ}C)$

- DIRECT CONTROLLED BY µC (MULTIPLEX SYSTEM)

- OUTPUT HIGH/LOW LEVEL DIAGNOSTIC

- OVERCURRENT SWITCH OFF AND DIAG-NOSTIC

- OVERTEMPERATURE DIAGNOSTIC BE-FORE SWITCH OFF

- OPEN LOAD DIAGNOSTIC

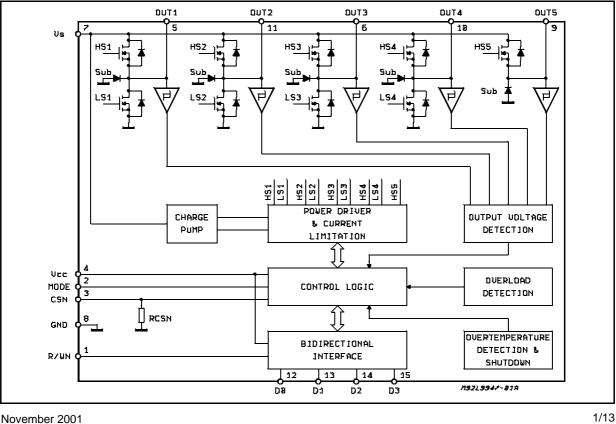

# DESCRIPTION

The L9947 is a bus controlled power interface in-

#### **BLOCK DIAGRAM**

tended for automotive applications realized in multipower BCD60II technology. Up to three DC motors and one grounded resistive load can be driven with its four half-bridge and one high-side driver power outputs. The microcomputer compatible bidirectional parallel bus allows several interfaces connected on the same bus (multiplex system). The full diagnostic information is available on the bus.

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                    | Parameter                               | Value                        | Unit |

|-----------------------------------------------------------|-----------------------------------------|------------------------------|------|

| Vs                                                        | DC Supply Voltage                       | 26                           | V    |

|                                                           | Single Pulse t <sub>max</sub> < 400ms   | 40                           | V    |

| Is                                                        | Negative Supply Current                 | -9                           | А    |

| V <sub>CC</sub>                                           | Stabilized Supply Voltage               | -0.3 to 6V                   | V    |

| V <sub>CSN</sub> , V <sub>R/WN</sub><br>V <sub>MODE</sub> | Digital Input Voltage                   | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>D0 -D3</sub>                                       | Digital Input/ Output Voltage           | -0.3 to V <sub>CC</sub> +0.3 | V    |

| I <sub>OUT1 - OUT5</sub>                                  | Output Current Power                    | internal limited             |      |

| Tj                                                        | Operating Junction Temperature          | -40 to 150                   | °C   |

| T <sub>j - SD</sub>                                       | Thermal Shutdown Junction Temperature   | min 150                      | °C   |

| Т <sub>ј - НҮЅ</sub>                                      | Thermal Junction Temperature Hysteresis | 20                           | К    |

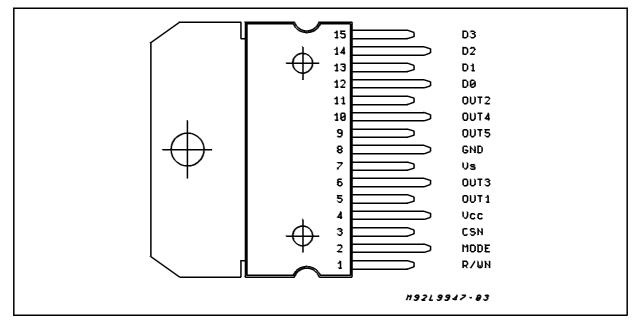

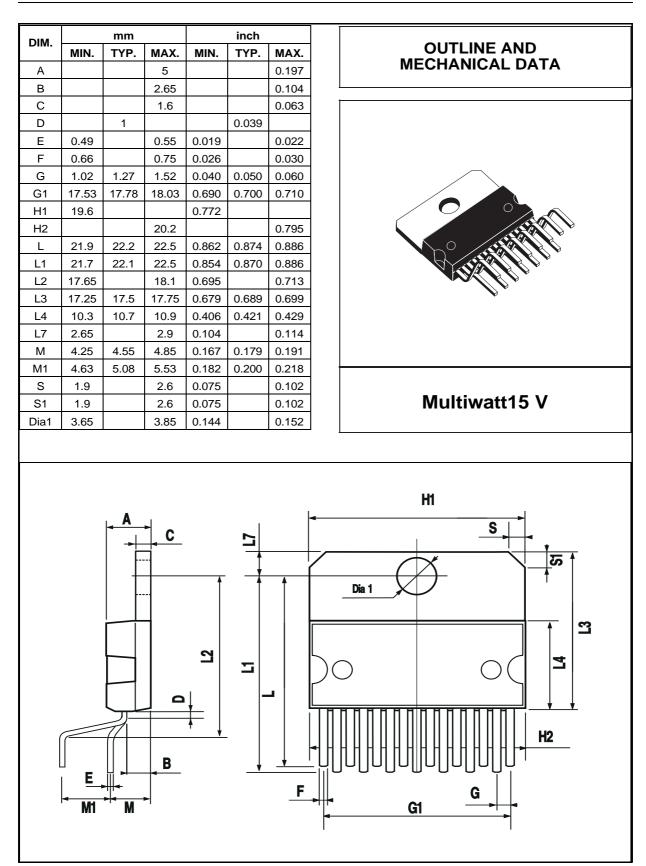

# **PIN CONNECTION**

# THERMAL DATA

| Symbol                | Parameter                                                               | Value | Unit |

|-----------------------|-------------------------------------------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction Ambient Ptot = 25W; free air; DC            | 38    | °C/W |

| Z <sub>th j-amb</sub> | Thermal Resistance Junction Ambient still air;<br>single pulse tp = 20s | 10    | °C/W |

**ELECTRICAL CHARACTERISTICS** ( $V_S = 8$  to 16V;  $V_{CC} = 4.5$  to 5.5V;  $T_j = -40$  to 150°C;unless otherwise specified; the voltage are referred to GND and currents are assumed positive, when the current flows into the pin.)

# SUPPLY:

| Symbol   | Parameter                         | Test Condition                                                                                                                                                                                   | Min. | Тур. | Max. | Unit |

|----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| lcc      | DC Supply Current                 | $V_{S} = 16V; V_{CC} = 5.5V; (status 8)$                                                                                                                                                         |      | 5    |      | mA   |

| ls       | DC Supply Current                 | V <sub>S</sub> = 16V; V <sub>CC</sub> = 5.5V; (status 8)                                                                                                                                         |      | 10   |      | mA   |

| ICC + IS | Sum Supply Current <sup>(1)</sup> | $\begin{array}{l} I_{OUT1} = \ I_{OUT2} = \ I_{OUT3} = \ I_{OUT4} = \\ I_{OUT5} = \ 0; \ Standby \ (status \ 2) \\ V_S = \ 14V; \ V_{CC} = \ 5.5V; \\ T_j = \ -40 \ to \ 25^\circ C \end{array}$ |      |      | 100  | μA   |

|          |                                   | $\begin{array}{l} I_{OUT1} = \ I_{OUT2} = \ I_{OUT3} = \ I_{OUT4} = \\ I_{OUT5} = \ 0; \ Standby \ (status \ 2) \\ V_S = \ 14V; \ V_{CC} = \ 5.5V; \\ T_j > 25^{\circ}C \end{array}$             |      |      | 150  | μΑ   |

|          |                                   | V <sub>S</sub> < 14V; V <sub>CC</sub> = 5.5V; I <sub>OUT</sub> = 0;<br>(status 17);                                                                                                              |      |      | 3    | mA   |

| Vsovt    | Overvoltage Shutdown<br>Threshold |                                                                                                                                                                                                  | 17   |      | 25   | V    |

# CONTROL INPUTS: CNS, R/WN, MODE

| Symbol           | Parameter                                        | Test Condition             | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------------|----------------------------|------|------|------|------|

| V <sub>INL</sub> | Input Low Level                                  | $V_{CC} = 5V$              |      |      | 1.5  | V    |

| VINH             | Input High Level                                 | $V_{CC} = 5V$              | 3.5  |      |      | V    |

| VINHyst          | Input Hysteresis                                 | $V_{CC} = 5V;$             | 0.5  |      |      | V    |

| I <sub>INL</sub> | Input Current Low                                | $V_{CC} = 5V; V_{IN} = 0$  | -10  |      | 10   | μA   |

| I <sub>INH</sub> | Input Current High (with exception of CSN Input) | $V_{CC} = 5V; V_{IN} = 5V$ | -10  |      | 10   | μA   |

| Rcsn             | Input Resistance to GND (pull down at CSN pin)   |                            | 20   |      |      | KΩ   |

# DATA INPUT: D0 - D3

| Symbol            | Parameter          | Test Condition             | Min. | Тур. | Max. | Unit |

|-------------------|--------------------|----------------------------|------|------|------|------|

| V <sub>DINL</sub> | Input Low Level    | $V_{CC} = 5V; MODE = 0$    |      |      | 1.5  | V    |

| V <sub>DINH</sub> | Input High Level   | $V_{CC} = 5V; MODE = 0$    | 3.5  |      |      | V    |

| VDINHyst          | Input Hysteresis   | $V_{CC} = 5V; MODE = 0$    | 0.5  |      |      | V    |

|                   | Input Current Low  | $V_{CC} = 5V; V_{IN} = 0$  | -10  |      | 10   | μA   |

| I <sub>DINH</sub> | Input Current High | $V_{CC} = 5V; V_{IN} = 5V$ | -10  |      | 10   | μA   |

# DATA OUTPUT: D0 - D3

| Symbol            | Parameter        | Test Condition                         | Min. | Тур. | Max. | Unit |

|-------------------|------------------|----------------------------------------|------|------|------|------|

| V <sub>DOL</sub>  | Output Low Level | $V_{CC}$ = 5V; $I_D$ = 0.5mA; MODE = 1 |      |      | 0.6  | V    |

| V <sub>DINH</sub> | Input High Level | $V_{CC} = 5V; I_D = 0.5mA; MODE = 1$   | 4    |      |      | V    |

Note (1): Off-State Leakage Current of each single output  $\leq 25\mu A$ ,  $T_j = -40$  to  $150^{\circ}C$ .

# L9947

# ELECTRICAL CHARACTERISTICS (continued) OUTPUTS:

| Symbol             | Parameter                                     | Test Condition                                                                                   | Min.       | Тур.                       | Max.               | Unit        |

|--------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------|------------|----------------------------|--------------------|-------------|

| RON OUT1           | On Resistance to Supply or<br>GND             | $V_S = 8V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 0.5A$                                          |            |                            | 6                  | Ω           |

|                    |                                               | $ \begin{array}{l} V_S \geq \!\! 10V; \ T_j = 125^\circ\!C; \\ I_{OUT} = \pm  0.5A \end{array} $ |            |                            | 3.95               | Ω           |

| RON OUT2           | On Resistance to Supply or<br>GND             | $V_S = 8V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 0.5A$                                          |            |                            | 6                  | Ω           |

|                    |                                               | $V_S \ge 10V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 0.5A$                                       |            |                            | 3.95               | Ω           |

| Ron out3           | On Resistance to Supply or<br>GND             | $V_S = 8V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 2.5A$                                          |            |                            | 600                | mΩ          |

|                    |                                               | $V_S \ge 10V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 2.5A$                                       |            |                            | 395                | mΩ          |

| RON OUT4           | On Resistance to Supply or GND                | $V_S = 8V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 2.5A$                                          |            |                            | 600                | mΩ          |

|                    |                                               | $V_S \ge 10V; T_j = 125^{\circ}C;$<br>$I_{OUT} = \pm 2.5A$                                       |            |                            | 395                | mΩ          |

| RON OUT5           | On Resistance to Supply                       | $V_{S} = 8V; T_{j} = 125^{\circ}C; I_{OUT} = -2A$                                                |            |                            | 1.0                | Ω           |

|                    |                                               | V <sub>S</sub> ≥ 10V; T <sub>j</sub> = 125°C;<br>I <sub>OUT</sub> = -2A                          |            |                            | 0.7                | Ω           |

| I <sub>OUT1</sub>  | Output Current Limitation to<br>Supply or GND | For the function of the short circuit current limitation see the                                 | 0.67       |                            | 2                  | A           |

| I <sub>OUT2</sub>  | Output Current Limitation to<br>Supply or GND | functional description (pag)                                                                     | 0.67       |                            | 2                  | A           |

| I <sub>OUT3</sub>  | Output Current Limitation to<br>Supply or GND |                                                                                                  | 4          |                            | 12                 | A           |

| I <sub>OUT4</sub>  | Output Current Limitation to<br>Supply or GND |                                                                                                  | 4          |                            | 12                 | A           |

| I <sub>OUT5</sub>  | Output Current Limitation to GND              |                                                                                                  | 2.5        |                            | 7.5                | Α           |

| I <sub>OUT1</sub>  | Output Current                                | V <sub>OUT1</sub> =2.5V; (status 18)                                                             | 5          |                            | 15                 | mA          |

| I <sub>OUtT2</sub> | Output Current                                | V <sub>OUT2</sub> =2.5V; (status 18)                                                             | 5          |                            | 15                 | mA          |

| I <sub>OUT3</sub>  | Output Current                                | V <sub>OUT3</sub> =2.5V; (status 18)                                                             | 5          |                            | 15                 | mA          |

| I <sub>OUT4</sub>  | Output Current                                | V <sub>OUT4</sub> =2.5V; (status 17)                                                             | 80         |                            | 500                | mA          |

|                    |                                               | V <sub>OUT4</sub> =V <sub>S</sub> -2.5V; (status 16 or 18)                                       | -80        |                            | -500               | mA          |

| I <sub>OUT5</sub>  | Output Current                                | V <sub>OUT5</sub> =V <sub>S</sub> -2.5V; (status 18)                                             | -5         |                            | -15                | mA          |

| Vout1-5            | Output Voltage Detection<br>Thresholds        | V <sub>S</sub> =13V; (status 11)<br>LOW<br>HIGH<br>HYSTERESIS                                    | 4.9<br>7.5 | 0.4 Vs<br>0.6 Vs<br>0.2 Vs | 5.5<br>8.1         | V<br>V<br>V |

| T <sub>JOT</sub>   | Overtemperature Detection                     | status 12 - 15                                                                                   |            | 130                        |                    | °C          |

|                    | Thresholds                                    | steady state t >20ms                                                                             | 125        |                            | <t<sub>JSD</t<sub> | °C          |

| t <sub>ISC</sub>   | Overcurrent Switch off Time                   |                                                                                                  | 50         |                            |                    | μs          |

| fosc               | Internal Oscillator Frequency                 |                                                                                                  |            | 250                        |                    | KHz         |

57

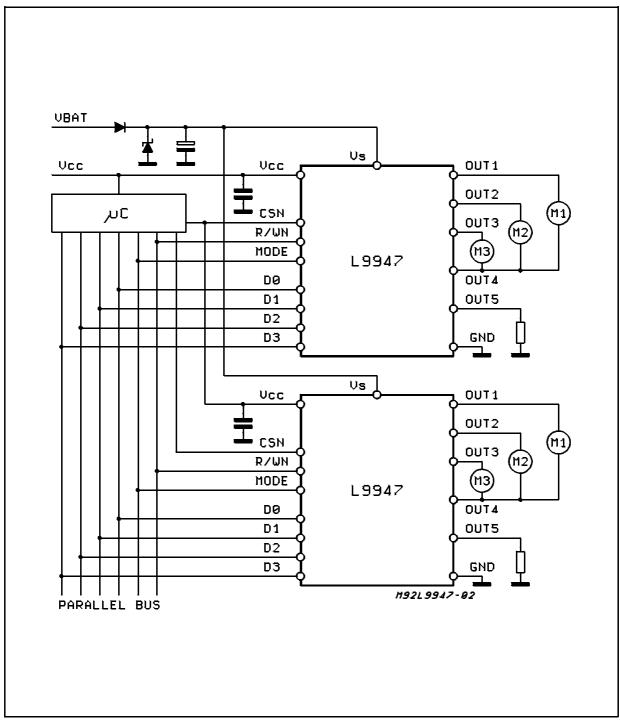

# **APPLICATION CIRCUIT DIAGRAM**

Fogure 1: Recommended Application Circuit.

# FUNCTIONAL DESCRIPTION

The L9947 is a power interface circuit designed for a multiplex system controlled by a parallel  $\mu$ C bus. The bus consists of four bidirectional data wires D0 - D3 and three control wires read/write (R/WN), mode (MODE) and chip select (CSN). The device needs two supply voltages. The first voltage supplies the half bridges, high side driver and its driving part. The second one is a 5V stabilized supply. The function of the device in the typical operating modes is described in the following tables.

# L9947

# **Output Activating/write Table 1**

| Status | CSN | R/WN | MODE | D0              | D1 | D2 | D3 | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | FUNCTION                                      |

|--------|-----|------|------|-----------------|----|----|----|------|------|------|------|------|-----------------------------------------------|

| 1      | 1   | Х    | х    | Х               | Х  | Х  | Х  | AB   | AB   | AB   | AB   | AB   | Hold output behavious as<br>programmed before |

| 2      | IJ  | 0    | 0    | 0               | 0  | 0  | 0  | Т    | Т    | Т    | Т    | Т    | All Outputs, Standby mode                     |

| 3      | IJ  | 0    | 0    | 0               | 0  | 1  | 0  | SRC  | Т    | Т    | SNK  | Т    | M1, right                                     |

| 4      | IJ  | 0    | 0    | 1               | 1  | 0  | 0  | SNK  | Т    | Т    | SRC  | Т    | M1, left                                      |

| 5      | IJ  | 0    | 0    | 1               | 0  | 1  | 0  | Т    | SRC  | Т    | SNK  | Т    | M2, right                                     |

| 6      | IJ  | 0    | 0    | 0               | 1  | 0  | 0  | Т    | SNK  | Т    | SRC  | Т    | M2, left                                      |

| 7      | IJ  | 0    | 0    | 0               | 1  | 1  | 0  | Т    | Т    | SRC  | SNK  | Т    | M3, right                                     |

| 8      | IJ  | 0    | 0    | Т               | 0  | 0  | 0  | Т    | Т    | SNK  | SRC  | Т    | M3, left                                      |

| 9      | IJ  | 0    | 0    | <sup>_1</sup> 1 | 1  | 1  | 0  | SNK  | SNK  | SNK  | SNK  | Т    | Braking                                       |

| 10     | U   | 0    | 0    | 0               | 0  | 0  | 1  | Т    | Т    | Т    | Т    | SRC  | High side driver                              |

#### Notes:

Where CSN = 0 the device is (for t  $\leq 100\mu$ s) transparent, in this condition any change of Data D0 .... D3 will lead to the apprpriate output response.

Deselecting the circuit (CSN ) the last programmed status will be stored.

# Diagnostic / read. Table 2:

In readout modes the port D0 .... D3 is acting as an output showing the conditions detected before.

| Status | CSN | R/WN | MODE | D0   | D1   | D2   | D3   | Fund                                  | ction |       |

|--------|-----|------|------|------|------|------|------|---------------------------------------|-------|-------|

| 11     | IJ  | 1    | 0    | OUT1 | OUT2 | OUT3 | OUT4 | OUT1, OUT2,                           | OUT3, | OUT4; |

| 12     | IJ  | 1    | 1    | 0    | 0    | ОТ   | OUT5 | No failure,                           | OT,   | OUT5; |

| 13     | IJ  | 1    | 1    | 1    | 0    | OT   | OUT5 | • OVC1,                               | OT,   | OUT5; |

| 14     | IJ  | 1    | 1    | 0    | 1    | ОТ   | OUT5 | • OVC2,                               | OT,   | OUT5; |

| 15     | U   | 1    | 1    | 1    | 1    | ОТ   | OUT5 | OVV<br>or OVV + OVC1<br>or OVV + OVC2 | OT,   | OUT5; |

# Diagnostic / write. Table 3:

Diagnostic modes are used to check the load status for broken or shorted wires.

| Status | CSN | R/WN | MODE | D0 | D1 | D2 | D3 | OUT1        | OUT2        | OUT3        | OUT4         | OUT5        | Function                                                 |

|--------|-----|------|------|----|----|----|----|-------------|-------------|-------------|--------------|-------------|----------------------------------------------------------|

| 16     | U   | 0    | 1    | 0  | 1  | 0  | Х  | Т           | Т           | Т           | 140mA<br>SRC | Т           |                                                          |

| 17     | U   | 0    | 1    | 1  | 0  | 0  | Х  | Т           | Т           | Т           | 140mA<br>SNK | Т           | $I_s + I_{cc} \le 1 \text{mA} \text{ for } I_{OUT4} = 0$ |

| 18     | U   | 0    | 1    | 0  | 1  | 1  | Х  | 10mA<br>SNK | 10mA<br>SNK | 10mA<br>SNK | 140mA<br>SRC | 10mA<br>SRC |                                                          |

Standby and clear / write. Table 4:

| Status | CSN | R/WN | MODE | D0 | D1 | D2 | D3 | OUT1 | OUT2 | OUT3 | OUT4 | OUT5 | Function                                                                                                         |

|--------|-----|------|------|----|----|----|----|------|------|------|------|------|------------------------------------------------------------------------------------------------------------------|

| 19     | U   | 0    | 0    | 1  | 1  | 1  | 1  | Т    | Т    | Т    | Т    | Т    | Clear                                                                                                            |

| 20     | 0   | Х    | Х    | Х  | Х  | Х  | Х  | Т    | Т    | Т    | Т    | Т    | Clear, Static CSN = 0 will<br>force clear status and<br>standby after 100µs<br>without respect of data<br>inputs |

Symbols:

1: Logic High 0: Logic Low

T: Tristate

X: Don't care

AB: As before ↓ Low pulse t < 100µs SRC: Source SNK: Sink OT: Overtemperature OVC1: Overcurrent 1 OVC2: Overcurrent 2 OVV: Overvoltage OUTX: - High if output voltage was >0.6Vs during test - Low if output voltage was <  $0.4V_{s}$  during test

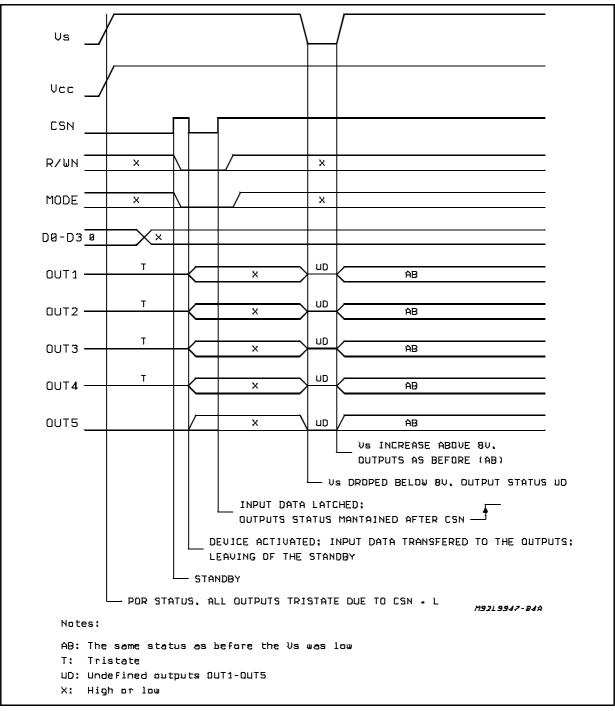

Figure 2: System Startup Sequence

# **SYSTEM STARTUP** (figure 2)

It is not mandatory that Vs is present before Vcc. With the presence of the Vcc the internal logic would be reseted and the system restarts under control of the inputs. If CSN = 0 for more than 100µs after the presence of Vcc the standby mode is activated. Standby is also activated when the CSN and VCC would be high at the same

time. When CSN = 0 and Vcc goes up, the device is not controlled by the bus. The outputs remain in tristate but the current consumption is larger than 100 $\mu$ A. A high - low - signal at the CSN - wire is mandatory to control the outputs. There is no undervoltage detection level for the supply voltage VS implemented. The VCC should be supplied from the same voltage supply as the driver of the D0 -D3 pins (eg.  $\mu$ C).

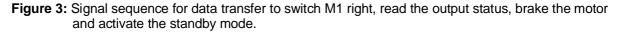

#### DATA TRANSFER AND OUTPUTS ACTIVAT-ING (Figure 3)

The half bridges of OUT1, OUT2 and OUT3 can be used with OUT4 to drive three bidirectional motors in full bridge configuration as shown in fig.1 Only one motor can be driven in the same time. The  $\mu$ C writes the corresponding word status 1 till 10 at the bus and latch it with a low pulse in the L9947. So the motor is activated. To stop the motor it is useful to insert a braking phase (status 9). In the braking condition there are all low side DMOS of the half bridges switched-on in this case the flyback currents flows through the low side switches instead of the intrinsic diodes of the half bridges. After that, the half bridges could be switched in tristate (T). The high side driver, OUT5 can be switched only when all the half bridges are in tristate status 10.

The  $\mu$ C works always as master and the L9947 Power Interface as slave. That means: the  $\mu$ C starts the communication between the Power Interface and itself with low transition at the CSN line. CSN = 0, R/WN= 0 the L9947 reads the data at the bus and execute the command as shown in tables 1,3,4 (write mode). The high slope of the CSN stores the last command and execute it further. All inputs are disabled if CSN= 1. So the bus can be used for another device. With CSN = 0 and R/WN = 1 the L9947 writes the status of the diagnostic at the parallel bus until CSN becomes high (table 2; status  $\mu$  + 15) (read mode). The power outputs maintain the same status as before.

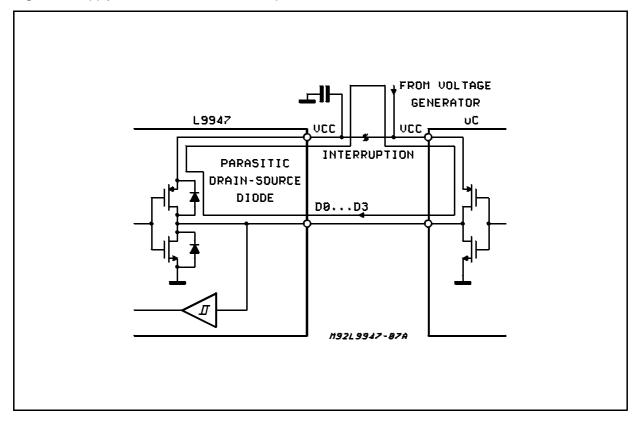

#### **Bus Timing** (figure 4)

The bus signal must be defined  $t_3 = 1\mu s$  before CSN goes low. It is allowed to change the level of R/WN during CSN = 0. The other signals could be changed. To store a command it is mandatory to fix the D0 - D3 and MODE signals  $t_9 = 1\mu s$  before the positive edge of CSN.

OVERCURRENT AT OUT1 - OUT5:

The output currents of OUT1 - OUT5 are internally limited. This is realized in the following way:

Figure 4: Bus and Outputs Timing Diagram

When the output current reaches a certain level (see pag...) the Gate - Source voltage will be clamped to a lower level. The output current is now limited and follows the output ID, UDS characteristic for this Gate - Source voltage. An internal timer starts when the output voltage drop (Drain - Source) increases above 0.4Vs.

Àfter 100µs typ. the output is switched OFF and the corresponding overcurrent bit (OVC1 or OVC2) will be set. The outputs can be activated again with the next input data word.

#### TIMING CHARACTERISTICS

| Symbol         | Parameter                                                      | Min. | Тур. | Max. | Unit |

|----------------|----------------------------------------------------------------|------|------|------|------|

| t <sub>1</sub> | Width of CSN Low                                               | 20   |      | 90*  | μs   |

| t <sub>2</sub> | Width of CSN High                                              | 10   |      |      | μs   |

| t3             | Input Signals Before Negative Cdge of CSN                      | 1    |      |      | μs   |

| t4             | Input Signals After Positive Edge of CSN                       | 1    |      |      | μs   |

| t5             | Valid Diagnostic Data                                          |      |      | 10   | μs   |

| t6             | Valid Diagnostic Data                                          |      |      | 10   | μs   |

| t7             | Delay Time from Input to Power Output, VS = 13V                |      |      | 300  | μs   |

| t8             | CSN = Low Duration (Pulse Length) for CLEAR of latched Data    | 100  |      |      | μs   |

| t9             | Input Data Before Positive Edge of CSN Which Should be Latched | 1    |      |      | μs   |

$t_1 \, \text{and} \, t_5$  are derived from the internal oscillator frequency

$t_7$  varies with the supply voltage  $\mathsf{V}_\mathsf{S},$  relating to the output voltage slope limitation

(\*) for t1  $\geq$  100µs the latched data will be reseted due to CLEAR (status 20)

#### Diagnostic (TABLE 2; STATUS 11 - 15):

The diagnostic delivers the information of the output voltage status (high or low) at the outputs OUT1 - OUT5, overcurrent, overvoltage shutdown and over temperature. The output voltage detection is done by hysteresis comparators with thresholds at 0.4VS and 0.6 VS. The overcurrent (OVC) information is latched till a new or repeated write command was received. The OVC1 is set to high with the overcurrent condition at any of the half-bridge outputs. OVC2 error bit will be set with the overcurrent condition at OUT5. The overvoltage (OVV) is high till the supply voltage Vs exceeds the overvoltage threshold of 20V typ.

The overtemperature (OT) is high if the junction temperature is less than typ. 30 Kevin below the thermal shutdown junction temperature (TJSD).

#### **Detection of Load Interruption** (TABLE 3):

The outputs OUT1 - OUT4 are connected by the motors in the application. The output OUT4 can be switched as current source or sink with typ. 140mA current capability (status 16 + 17). The sum of current consumption is <1mA if the output current IOUT4 = 0 (status 17). The diagnostic of the output voltage delivers the information if one or more of the half bridges is shorted to Vs or GND or the motor connections are interrupted. In status 18 the outputs OUT1 - OUT3 are switched as current sinks (typ. 10mA), OUt4 and OUt5 as current sources (OUT4 140mA, OUT5 10mA). With this current the influence of leakage currents and oxidized contacts is eliminated.

#### Standby (TABLE!; STATUS 2):

The L9947 is set in standby mode with the positive edge of CSN when all other inputs are low. All latched data will be cleared and the inputs and outputs are in tristate.

The total current consumption is less than  $100\mu$ A. CSN=0 quits the standby. All latched data are cleared.

#### Clear (TABLE 4: STATUS 20):

If the chip select is low for ore than  $T_{CLR} = 100 \mu s$ , the internal latched data will be cleared and the outputs become tristate. Repetitive high low edges activate the inputs again. Also a broken CSN-wire activates this clear function due to the internal pull down resistor at CSN input. After a clear, the L9947 goes in standby and can be

wake up with a negative edge of CSN.

#### Thermal Shutdown:

When the junction temperature increases above TJSD the power DMOS transistors are switched off until the junction temperature drops below the value TJSD - TJHYST.

#### Clamp Current of The Power Outputs:

For output voltages 10V and larger a clamp current of appr. 50µA will flow in the power outputs due to the internal gate-source voltage limitation, when the device is not in standby.

#### Overvoltage Shutdown:

When the supply voltage VS exceeds the overvoltage threshold Vsqvr, typ. 20V, the outputs OUT1 OUT5 go in tristate condition. If the supply voltage goes under the overvoltage shutdown treshold, the status is the same as before the overvoltage condition occurred.

#### Undervoltage:

In the voltage range 2V <Vcc < 4V the internal logic is reseted and all outputs go in tristate. Also ground spikes on the Vcc reset the logic. After an internal reset of the logic, the L9947 is controlled again by the inputs.

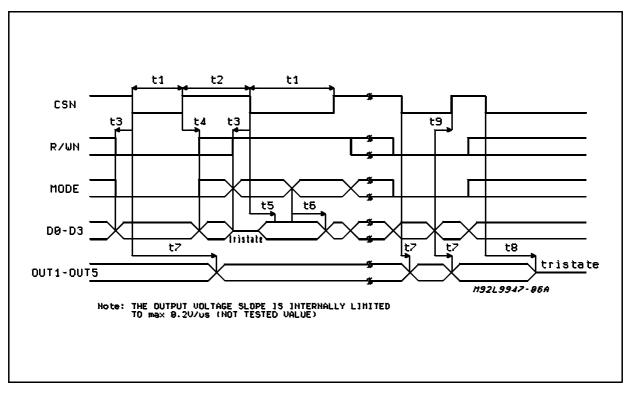

#### Ground Interrupt:

The L9947 is protected against interruption. The output OUt5 switches off at ground interruption. The outputs OUT1 - OUt4 are driven in full bridge configuration as shown in the application. There is no path through the load or direct to another ground. Thus, the device protected.

#### Vcc Interruption

If the supply voltage Vs is present and Vcc is interrupted or not supplied, than two cases can be distinguished:

- 1 The data pins D0 D3 are not driven by the  $\mu$ C or they are low. So the outputs OUT1 -OUT5 and D0 - D3 are in tristate.

- 2 One of the pins D0 D3 is driven high the  $\mu$ C. This pin supplies the VCC pin by the drain-bulk-diode of the p-channel mos (fig.5). Depending of the CSN, R/WN and MODE inputs some undesiderable functions can occur.

**K7/**

Figure 5: Supply Current Path at Vcc Interruption

57

12/13

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

$\ensuremath{\textcircled{\sc 0}}$  2001 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com

57