## OCTAL LINE RECEIVER

**ADVANCE DATA**

■ OCTAL LINE RECEIVER FOR:

- EIA STD RS232D

RS423A

**RS422A**

- CCIT V.10

V.11 V.28

X.26

■ NO EXTERNAL COMPONENTS

■ INPUT FAIL SAFING CAPABILITY

■ HIGH CROSSTALK REJECTION

■ L6180 DATA RATE < 100KBIT/S

■ L6181 DATA RATE < 1MBIT/S

50V EOS OUTPUT PROTECTION

## **DESCRIPTION**

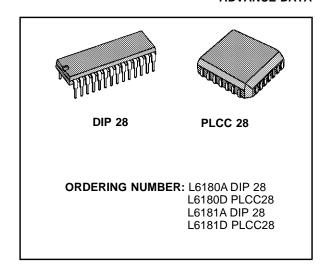

L6180/1 is an octal line receiver in a plastic DIP or PLCC designed to meet a wide range of digital communications requirements as outlined in the EIA standards RS232A without additional components, as well as the low speed applications of RS422A.

The receiver meets the CCIT recommendations V.10, V.11, X.26 and V.28 low speed applications (below 100KBS).

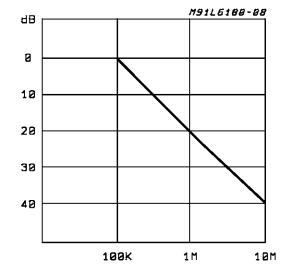

À low pass filter on the input starts to roll off at a frequency of 100KHz.

## **BLOCK DIAGRAM**

October 1993 1/10

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol   | Parameter                            | Value             | Unit |

|----------|--------------------------------------|-------------------|------|

| Vcc      | Supply Voltage                       | 7                 | V    |

| Vdd      | Supply Voltage                       | 13.5              | V    |

| $V_{SS}$ | Logic Supply Voltage                 | -13.5             | V    |

| Crr      | Common Mode Range                    | ±15               | V    |

| $V_{ID}$ | Differential Input Voltage           | ±25               | V    |

| Ptot     | Power Dissipation (PLCC 28)          | 800               | mW   |

|          | Power Dissipation (DIP 28)           | 1200              | mW   |

| los      | Output Sink Current                  | 50                | mA   |

| t        | Output Short Circuit Time            | 1                 | sec  |

| Тор      | Operating Free Air Temperature Range | 0 to 70           | °C   |

| Tstg     | Storage Temperature Range            | -65 to 150        | °C   |

|          | ESD                                  | 2KV max ESD 50μJ  |      |

|          | Input Transient Protection           | 50V min EOS 100μs |      |

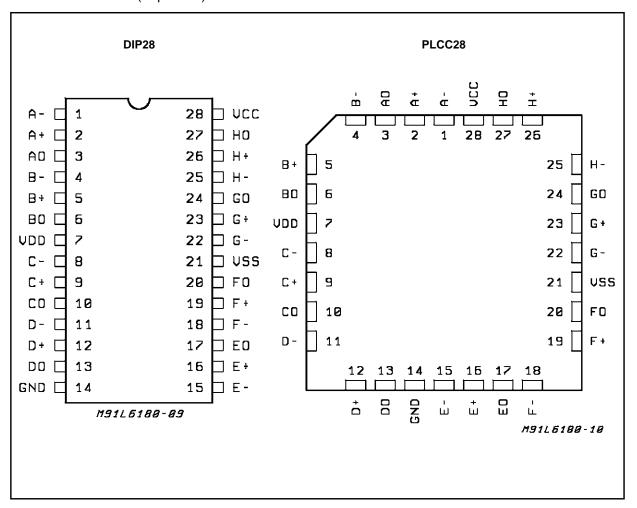

## **PIN CONNECTIONS** (Top views)

# **ELECTRICAL CHARACTERISTICS** (Vcc = 5V $\pm$ 5%; VcM = -7 to 7V; Tamb = 0 to 70°C; Vss = -9 to 13.5V; VdD = 9 to 13.5V; unless otherwise specified.)

| Symbol             | Parameter                                             | Test Condition                                                                                                | Min. | Тур. | Max.        | Unit     |

|--------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|-------------|----------|

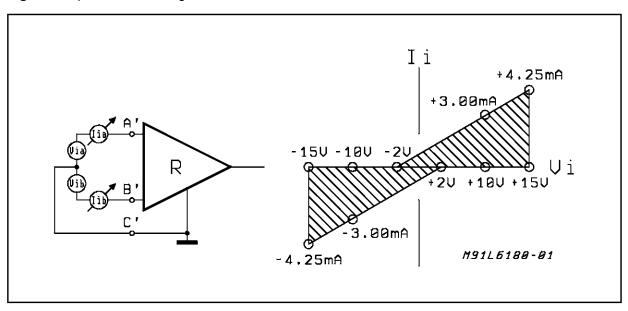

| V <sub>IN</sub>    | Input Current                                         | (See Fig.1 and note2)<br>Vcc = 0 to 5.25V;<br>Vss, Vdd = 0 to 13.5V<br>VIN = - 10 to 10V<br>VIN = - 15 to 15V |      |      | ±3<br>±4.25 | mA<br>mA |

| Rı                 | Input Resistance                                      | VIA or VIB = 3 to 15V; (see fig.1)                                                                            | 3    |      | 7           | KΩ       |

|                    |                                                       | $R_{I} = \frac{[(V_{IA} \text{ or } V_{IN}) - V_{IOC}]}{I_{IN}}$                                              |      |      |             |          |

| $V_{FS}$           | Failsafe Output Voltage                               | Io = -440μA (See Fig.3)                                                                                       | 2.7  |      |             | V        |

| V <sub>OH</sub>    | High Level Output Voltage                             | Vcc = 4.75V; ViD = -1V;<br>IoH = -440μA                                                                       | 2.7  |      |             | >        |

| V <sub>OL</sub>    | Low Level Output Voltage                              | Vcc = 5.25V; VID = -1V;<br>IOL = 2mA                                                                          |      |      | 0.4         | >        |

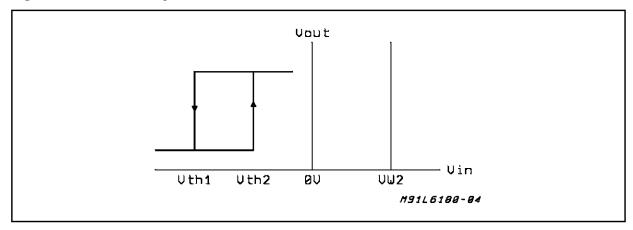

| V <sub>IT2</sub>   | V <sub>IOH</sub> Comparator Threshold<br>Voltage      | (See Fig.4)                                                                                                   | 1.8  | 2.2  | 2.6         | <b>V</b> |

| I <sub>IH2</sub>   | High Operating Threshold Voltage                      | VoL = 0.4V; loL = 2mA;<br>(See Fig.4)                                                                         | -25  |      | -75         | mV       |

| I <sub>IH1</sub>   | Low Operating Threshold Voltage                       | Voн = 2.7V; lo = -440μA<br>(See Fig.4)                                                                        | -125 |      | -175        | mV       |

| V <sub>H</sub>     | Input Hysteresis Voltage                              | VTH2 - VTH1                                                                                                   | 50   |      | 150         | mV       |

| V <sub>IOC1</sub>  | Open Circuit Input Voltage                            | Measured in accordance with V.28 and RS-232D (see note 4 and 7)                                               |      | 0.6  | 2           | <b>V</b> |

| Vioch              | Open Circuit Input Voltage                            | Measured in presence of AC Input Signal (see note 7)                                                          | 3.5  | 4    | 4.5         | >        |

| los                | Open Short Circuit Current                            | Vcc = 5.25V; Vo = 0; VID = 1V; (see note 5)                                                                   | 20   |      | 100         | mA       |

| $V_{IBV}$          | Input for Balance Test                                | (see Figure 7 and note 11)                                                                                    |      |      | 0.4         | V        |

| Cı                 | Input Capacitance                                     |                                                                                                               |      |      | 100         | pF       |

| V <sub>CC</sub>    | Supply Current                                        | Vcc = 4.75V to 5.25V; (see note 6)                                                                            |      |      | 100         | mA       |

| $V_{dd}$           | Supply Current                                        | V <sub>dd</sub> = 9 to 3.5V; (see note 6)                                                                     |      |      | 30          | mA       |

| Vss                | Supplyt Current                                       | Vss = -9 to 13.5V; (see note 6)                                                                               |      |      | 30          | mA       |

| los                | Open Short Circuit Current                            | Vcc = 5.25V; Vo = 0; VID = 1V; (see note 5)                                                                   | 20   |      | 100         | mA       |

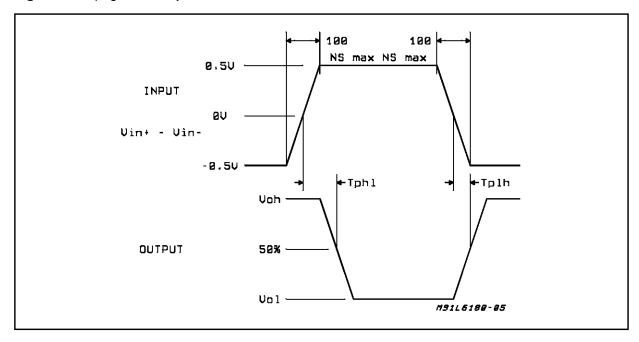

| $T_{plh}$          | Propagation Delay Low to High                         | RL = $390\Omega$ ; CL = $50pF$ ;<br> VIN = $1V$  ; (see fig 5 test Circuit Fig. 6)                            | 0    |      | 1500        | ns       |

| $T_{phl}$          | Propagation Delay Low to High                         | RL = $390\Omega$ ; CL = $50pF$ ;<br> VIN = $1V$  ; (see fig 5 test Circuit Fig. 6)                            | 0    |      | 1500        | ns       |

| Vioch              | Delay Vioci to Vioch Switching                        | (see note 7A)                                                                                                 |      |      | 5           | ms       |

| V <sub>IOCL</sub>  | Delay VIOCH to VIOCL Switching                        | (see note 7B)                                                                                                 | 200  |      |             | ms       |

| V <sub>ist</sub>   | Tplh - Tphl                                           | R <sub>L</sub> = 390Ω; C <sub>L</sub> = 50pF;<br> V <sub>IN</sub>   = 1V;(see fig. 5; Test<br>Circuit Fig. 6) | 0    |      | 500         | ns       |

| T <sub>SKEW1</sub> | Skew between rec's in PKg Tp (1) hl/1h - Tp (2) hl/1h | R <sub>L</sub> = 390Ω; C <sub>L</sub> = 50pF;<br> V <sub>IN</sub>   = 1V;(see fig. 5; Test<br>Circuit Fig. 6) | 0    |      | 300         | ns       |

| f <sub>A</sub>     | Frequency Accepted (Receiver will Output)             | VIN = 200mVpp; (see fig. 8 and note 7;                                                                        | 100  |      |             | KHz      |

**ELECTRICAL CHARACTERISTICS** (Vcc =  $5V \pm 5\%$ ; VcM = -7 to 7V; Tamb = 0 to 70°C; Vss = -9 to 13.5V; VDD = 9 to 13.5V; unless otherwise specified.)

| Symbol         | Parameter                               | Test Condition                         | Min. | Тур. | Max. | Unit |

|----------------|-----------------------------------------|----------------------------------------|------|------|------|------|

| f <sub>R</sub> | Frequency Rejected (No Receiver Output) | VIN = 2Vpp;<br>(see fig. 8 and note 7) |      | 5    |      | MHz  |

#### Note:

- 1) The algebric convention, where the less positive (more negative) is designed the minimum

- 2) With the voltage VIA or (VIB) ranging between ±15V, while VIB or (VIA) is open or grounded, the resultant input current IIA or (IIB) shall remain within the shaded region shown in the graph in Fig.1.

- 3) Either Point B' or Point A' is grounded in Figure 1

- 4) Vicc measured from grounded to (+) input with (-) input grounded Vicc measured from grounded to (+) input with (-) input grounded

- 5) Not more than one output should be shorted at a time and for less than 1 seond

- 6) The sum of the product of the maximum supply currents and voltages cannot exceed themaximum power dissipation

- 7) A: The conditions for the inpit switching from Vioci to Vioci mode is: Vid in start bit "spacing condition"for less than TpVioch (5ms).

- B: The conditions for the input switching from VIOCH to VIOCL mode is: Vid > Ww2 for greater than TpVIOCL (200ms)

- 8) An example of a frequency response plot meeting the rejection/acceptance requirements is provided in figure 8.

## **LINE TRANSIENT IMMUNITY** (Considering the following cases; powered ON, Powered OFF-LOW impedance power supply and powered OFF-HIGH impedance supply)

| Symbol | Parameter | Test Condition                                                    | Min. | Тур. | Max. | Unit |

|--------|-----------|-------------------------------------------------------------------|------|------|------|------|

| ESD    | Static    | tested per MIL-STD-883<br>(see note 9)                            | 2    |      |      | KV   |

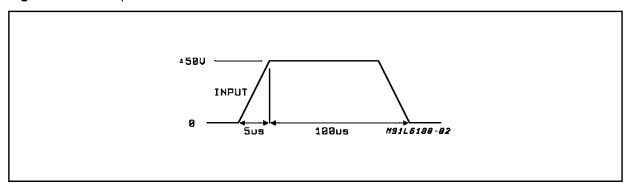

| EOS    | Stress    | transient pulse both polarities for 100µs (see note 9 and Fig. 2) | 50   |      |      | V    |

### Note:

- 9) All pins are required to withstand this parameters.

- 10) Input pins are required to withstand fig.2 without any degradation to the circuit.

- 11) The balance test requirement can be met by use of a current limit circuit which reduces the input bias current lib (see figure 7) for input voltages below a threshold voltage given by (lib x 1K) 400mV.

Figure 1: Input Current Voltage Mesurements

Figure 2: EOS Requiremets

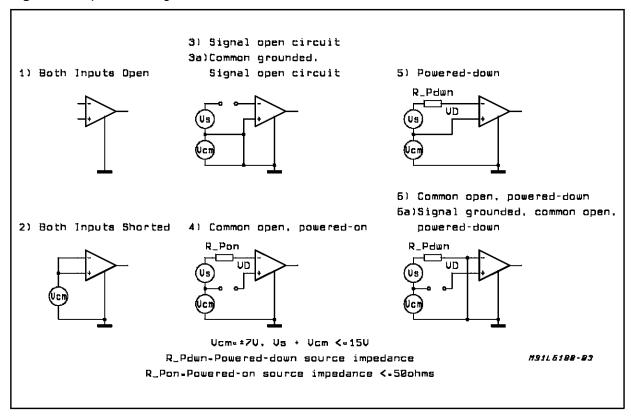

Figure 3: Output Failsafing

The output assumes a logic "1" under the following conditions, (see figure 3)

- 1 Both inputs open

- 2 Both inputs shorted

- 3 Signal Opencircuit

- 3a Common grounded, signal open circuit

- 4 Common open, generator powered-on

- 5 Generator powered-down (see note 7)

- 6 Common open, generator powered-down

- 6a Signal grounded, common open, generator powered-down

- 7 Less than 250mVpp differential signal

Figure 4: Threshold voltage definition

Figure 5: Propagation Delay

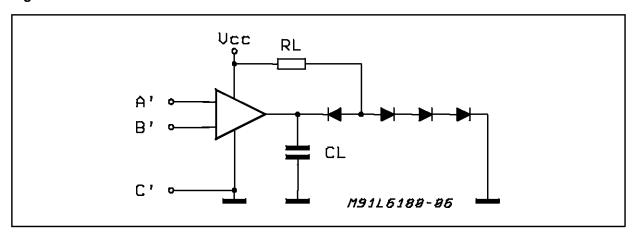

Figure 6: AC Test Circuit

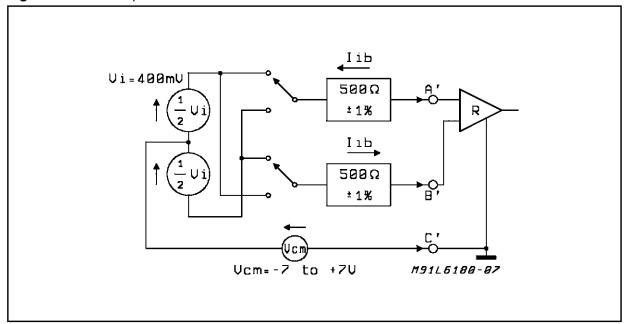

Figure 7: Receiver input Balance Measurement

**INPUT BALANCE MEASUREMENT**

The balance of the receiver input voltage-current characteristics and bias voltages shall be such that the receiver will remain in the intended binary state when a differential voltage Vi of 400mV is applied through  $500\Omega\,\pm1\%$  to each input terminal, as shown above, and Vcm is varied between -7 and +7V.

When the polarity of Vi is reversed, the opposite binary state shall be maintained under the same conditions. Maintain input balance with input B common with another receiver.

The voltage input (VIN) rejection is checked at the center point between the High Operating Threshold (Vth2) and the Low Operating Threshold (Vth1)

Figure 8: High Frequency Signal Rejection

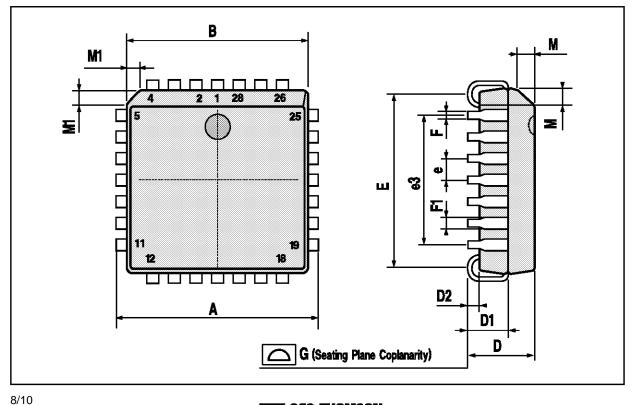

## PLCC28 PACKAGE MECHANICAL DATA

| DIM. | mm    |       |       | inch  |       |       |  |

|------|-------|-------|-------|-------|-------|-------|--|

|      | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |

| Α    | 12.32 |       | 12.57 | 0.485 |       | 0.495 |  |

| В    | 11.43 |       | 11.58 | 0.450 |       | 0.456 |  |

| D    | 4.2   |       | 4.57  | 0.165 |       | 0.180 |  |

| D1   | 2.29  |       | 3.04  | 0.090 |       | 0.120 |  |

| D2   | 0.51  |       |       | 0.020 |       |       |  |

| E    | 9.91  |       | 10.92 | 0.390 |       | 0.430 |  |

| е    |       | 1.27  |       |       | 0.050 |       |  |

| e3   |       | 7.62  |       |       | 0.300 |       |  |

| F    |       | 0.46  |       |       | 0.018 |       |  |

| F1   |       | 0.71  |       |       | 0.028 |       |  |

| G    |       |       | 0.101 |       |       | 0.004 |  |

| М    |       | 1.24  |       |       | 0.049 |       |  |

| M1   |       | 1.143 |       |       | 0.045 |       |  |

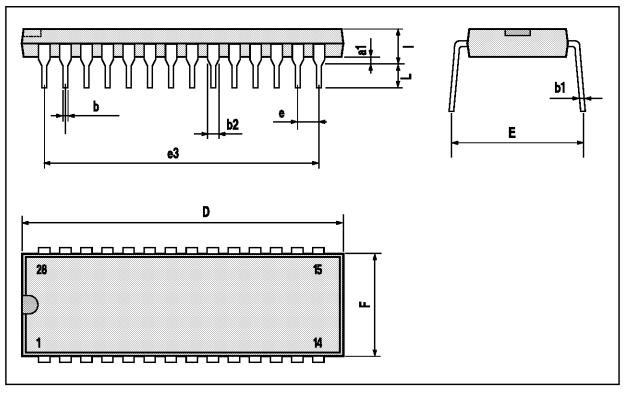

## **DIP28 PACKAGE MECHANICAL DATA**

| DIM. | mm   |       |       | inch  |       |       |  |

|------|------|-------|-------|-------|-------|-------|--|

|      | MIN. | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |  |

| a1   |      | 0.63  |       |       | 0.025 |       |  |

| b    |      | 0.45  |       |       | 0.018 |       |  |

| b1   | 0.23 |       | 0.31  | 0.009 |       | 0.012 |  |

| b2   |      | 1.27  |       |       | 0.050 |       |  |

| D    |      |       | 37.34 |       |       | 1.470 |  |

| E    | 15.2 |       | 16.68 | 0.598 |       | 0.657 |  |

| е    |      | 2.54  |       |       | 0.100 |       |  |

| e3   |      | 33.02 |       |       | 1.300 |       |  |

| F    |      |       | 14.1  |       |       | 0.555 |  |

| I    |      | 4.445 |       |       | 0.175 |       |  |

| L    |      | 3.3   |       |       | 0.130 |       |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore -