# TABLE OF CONTENTS

### **OVERVIEW**

# 1. KS82C388 FUNCTIONAL DESCRIPTION

- 1.1 Reset and Shutdown Logic

- 1.2 Clock Generation and Selection Logic

- 1.3 Port B Register and NMI generation logic

- 1.4 Action Mode Codes Generation

- 1.5 CPU State Machine, Local Memory State Machines, Cache State Machine, AT Bus State Machine

- 1.5.1 CPU State Machine

- 1.5.2 Local Memory State Machine

- 1.5.3 Cache State Machine

- 1.5.4 AT Bus State Machine

- 1.6 Bus Arbitration

- 1.7 Coprocessor Support

- 1.8 Cache Controller

- 1.8.1 Cache Performance

- 1.8.2 KS82C388 Cache Organization

- 1.8.3 General Operations

- 1.8.3.1 Read Hit Cycle

- 1.8.3.2 Read Miss Cycle

- 1.8.3.3 Write Cycle

- 1.8.3.4 DMA/MASTER Cycle

- 1.8.4 Other Issues in Cache System Design

- 1.8.4.1 Non-Cacheable Regions

- 1.8.4.2 Direct SRAM and Tag RAM access

- 1.9 DRAM Controller

- 1.9.1 DRAM Operation

- 1.9.2 Refresh Logic

- 1.9.2.1 AT Refresh

- 1.9.2.2 Slow Refresh

- 1.9.3 Shadow RAM

- 1.9.4 Memory Remapping

- 1.9.5 EPROM Control Logic

- 1.9.6 OS/2 Optimization

- 1.9.7 Memory Subsystem Design Specification

- 1.10 Action Decode and Control

- 1.11 Data Transfer Modules

- 1.11.1 CPU/DRAM Data Transfer Module

- 1.11.2 CPU/AT/IO/ROM Data Transfer Module

- 1.11.3 DMA Cycles Transfer Module

- 1.11.4 MASTER Cycles Transfer Module

Page: 1 (KS82C388)

- 1.12 Parity Handler

- 1.13 Timer Clock

- 1.14 Local Bus Support

- 1.14.1 Local Bus Hardware Support

- 1.15 Pins used for internal configuration

- 1.15.1 8 Bit / 16 Bit ROM selection

- 1.15.2 Mode selection

- 1.16 AT Peripheral Controller (On-chip 82C206)

- 1.16.1 Clock and Wait State Control

- 1.16.2 DMA Controller

- 1.16.2.1 DMA Registers

- 1.16.2.2 Address Generation

- 1.16.3 Interrupt Controller

- 1.16.4 Counter/Timer

- 1.16.5 Real Time Clock

- 1.16.5.1 Registers Access

- 1.16.5.2 Time Calendar and Alarm Bytes

- 1.16.5.3 Control and Status Registers

# 2. CONFIGURATION REGISTERS

- 2.1 Summary of Configuration Registers

- 2.2 Configuration Registers Full Description

- 2.3 How to Program the Configuration Registers

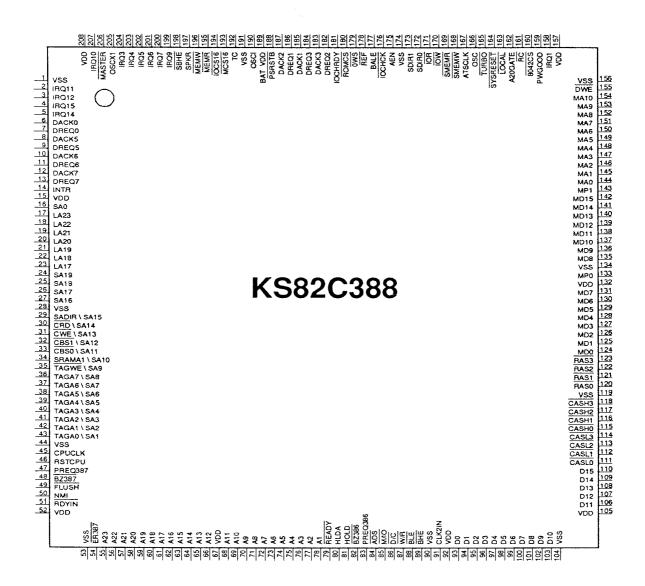

# 3. KS82C388 PIN DESCRIPTION

- 3.1 KS82C388 Pin Diagram

- 3.2 KS82C388 Pin List

# 4. ELECTRICAL CHARACTERISTICS

- 4.1 Absolute Maximum Ratings

- 4.2 Recommended Operating Conditions

- 4.3 DC Characteristics

- 4.4 AC Characteristics

- 4.5 Timing Diagrams

# 5. KS82C388 PACKAGE

# SAMSUNG 386SX PC/AT SINGLE CHIP KS82C388

### **OVERVIEW**

The SAMSUNG KS82C388, 386SX PC/AT single chip, is a controller for high performance PC-ATs with the 80386SX or the Cx486SLC CPU. Major features of the KS82C388 include:

- · Two modes of operation

- MODE1 for cache systems (DRAM banks reside on MD bus)

Zero wait state cache read hit operation up to 40MHz

- MODE2 for non-cache systems (DRAM banks reside on D bus)

Zero wait state DRAM page read hit operation up to 33MHz

- · High performance cache controller for 25, 33 and 40MHz systems (MODE1 only)

- Direct mapped cache organization

- Buffered posted write-through DRAM updating scheme

- Supports I6KB, 32KB and 64KB of data cache

- Non-cacheable region that can range from 1KB to 1MB

- Uses external TAG RAM and internal TAG comparator

- · High performance DRAM controller

- Supports the full 16MB physical address space

- Supports 256Kb/lMb/4Mb DRAM

- Page mode operation with programmable wait states and RAS/CAS timing

- 384K memory relocation option

- System and Video BIOS shadow RAM function

- Zero wait state page read hit operation up to 33MHz (MODE2 only).

- · On-chip Integrated Peripheral Controller (82C206)

- 7 DMA channels

- 13 Interrupt request channels

- 2 Timer/Counter

- Real Time Clock with 114 bytes of CMOS RAM

- · Supports 80387SX Coprocessor

- · Supports 8-Bit / 16-Bit ROM

- · Synchronous PC-AT bus clock with programmable frequency

- · Provides local bus VGA graphics support

- Fast Gate A20 and Fast Reset for OS/2 optimization

- · 100% IBM PC/AT compatible

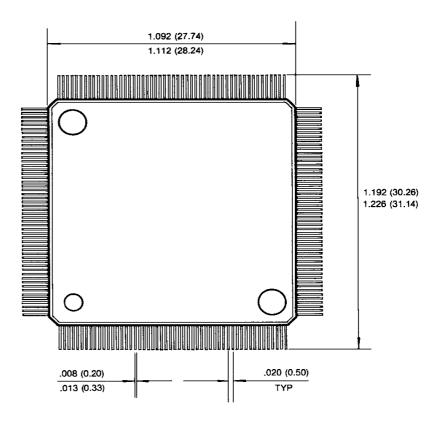

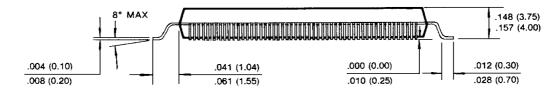

- · 208 Pin PQFP (Plastic Quad Flat Package)

Page: 3 (KS82C388)

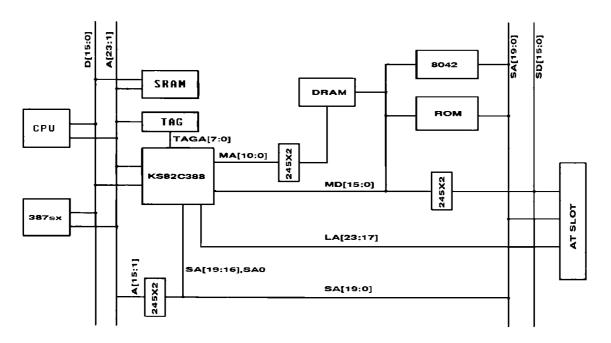

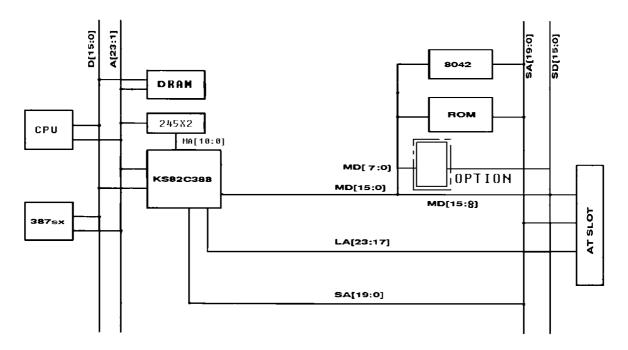

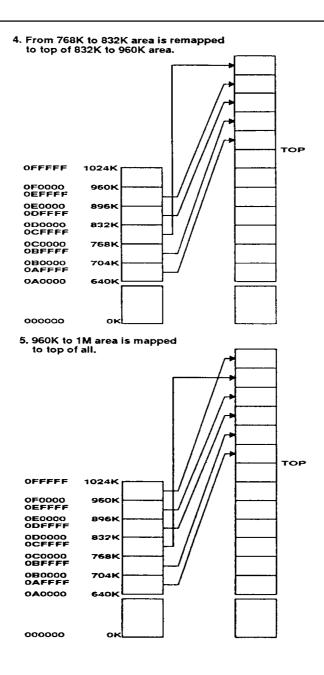

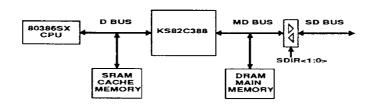

The KS82C388 has two modes of operaion (MODE1 for cache based systems, MODE2 for systems without cache). With these two modes, two types of PC-AT system can be implemeted. The resulting system organization is illustrated in Figure 0-1.

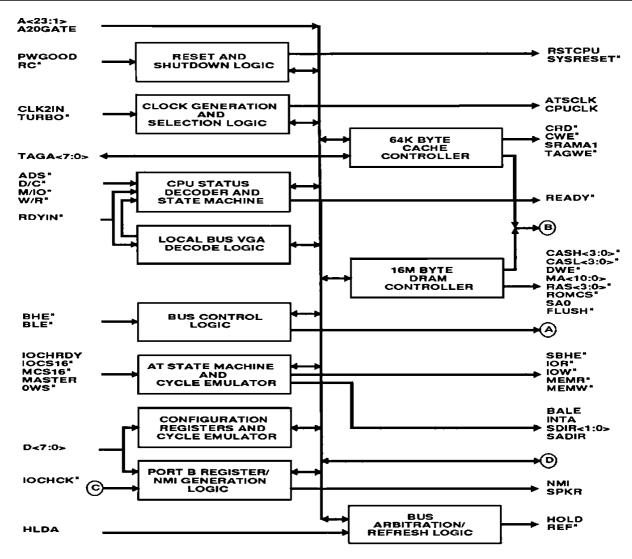

The KS82C388 generates and synchronizes all control signals for busses and manages the interfaces of all function blocks inside the chip, e.g. Reset/Shutdown logic, CPU/Local Memory/AT/Cache state machines, arbitration and refresh logic, DRAM and cache controller (refer to Figure 0-2a.). The internal cache controller supports direct mapped cache organization with data cache sizes of 16KB, 32KB or 64KB. It implements a posted write-through DRAM updating scheme.

By integrating the cache controller along with the DRAM controller, the KS82C388 can further enhance system performance by time-sharing cache and DRAM cycles. For example, when a read cycle starts, cache access and DRAM access are performed in parallel and DRAM cycles can continue and/or be terminated depending on the outcome of the cache hit/miss signal from the TAG RAM directory. The KS82C388 thus can achieve a faster cache line fill during a cache miss cycle.

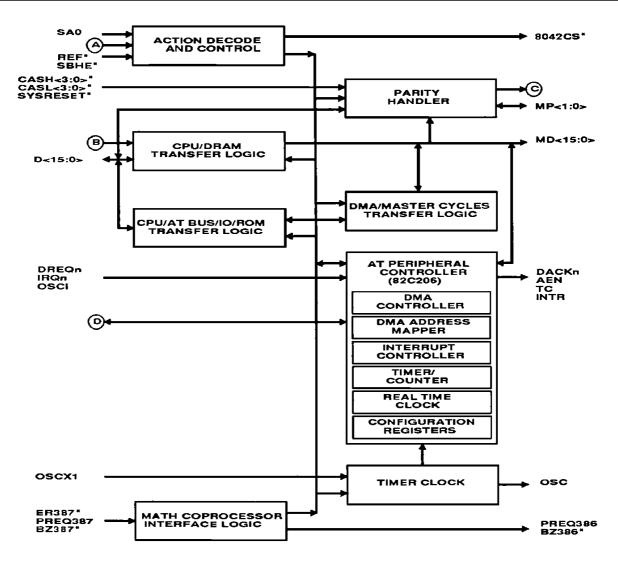

Figure 0-1a. Desktop System Block Diagram - MODE1 (DRAM on MD bus mode for CACHE based systems)

The KS82C388 also contains the control logic to manage the interface between the CPU data bus, local main memory data bus, local system bus, PC-AT bus, ROM, and on board peripherals (refer to Figure 0-2b). It also implements the byte alignment and byte swapping logic for data transfer where source and target are of different bus widths. The parity logic embedded in the chip generates and writes the parity bits into the DRAM array during main memory write cycles. It also latches the data parity for each byte during memory read cycle. The parity handler and associated NMI logic is designed to assure data integrity throughout the system operation. The built-in coprocessor detection/interface circuitry supports the 80387SX Math Coprocessor without additional discrete logic.

The AT peripherals - 8237 DMA, 8254 Timer and the 8259 Interrupt controller as well as the Real Time Clock and the associated CMOS memory are included on the KS82C388. This results in an AT system with very few external logic devices.

The KS82C388 is available in 208 Pin PQFP (Plastic Quad Flat Package)

Figure 0-1a. Desktop System Block Diagram - MODE2 (DRAM on MD bus mode for CACHE based systems)

Figure 0-2a. KS82C388 Block Diagram

Figure 0-2b. KS82C388 Block Diagram (Cont.)

# 1. KS82C388 FUNCTIONAL DESCRIPTION

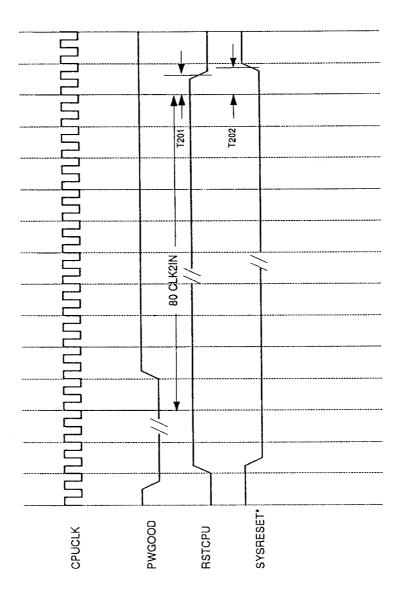

# 1.1 Reset and Shutdown Logic

The KS82C388 takes PWGOOD and RC\* inputs and generates the signals RSTCPU and SYSRESET\* that trigger both warm and cold reset. PWGOOD is the Power Good signal and originates at the power supply. When PWGOOD is low, the KS82C388 will assert RSTCPU and SYSRESET\* thereby initiating a cold reset of the complete system. If RC\* is asserted by the keyboard controller (8042 or 8742) a system warm reset is generated, the KS82C388 asserts RSTCPU to reset the CPU. RSTCPU is also asserted by the KS82C388 when a shutdown bus cycle is detected.

Both RSTCPU and SYSRESET\* last for at least 80 CPUCLK cycles. The HIGH to LOW transition of RSTCPU and the LOW to HIGH transition of SYSRESET\* signal is synchronous with the CLK2 input signal of the CPU. This guarantees that the phase of the internal clock of the KS82C388 state machine is the same as the phase of the internal clock of the CPU.

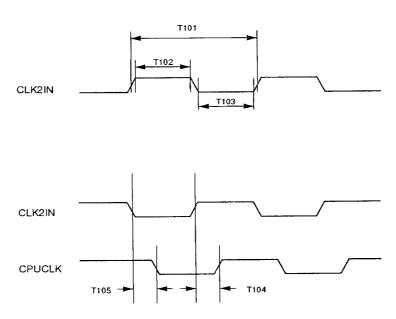

# 1.2 Clock Generation and Selection Logic

The KS82C388 receives three clock inputs: CLK2IN, OSCX1 and OSCI. It generates various clock signals to drive the CPU, the coprocessor, DRAM/Cache/AT state machines and the AT bus system. CLK2IN is derived from a crystal oscillator running at twice the rated frequency of the CPU.

The KS82C388 generates two clock output signals: CPUCLK and ATSCLK. The processor clock CPUCLK drives the CLK2 inputs of the CPU and the coprocessor. It is also used to drive KS82C388 internal DRAM/Cache state machines. ATSCLK is the AT bus system clock.

CPUCLK is derived from CLK2IN to allow the CPU to operate at the maximum speed. ATSCLK is a subdivision of CLK2IN. The ATSCLK frequency can be programmed to be CLK2IN/4, CLK2IN/6, CLK2IN/8 or CLK2IN/10 by setting bits <7:6> of configuration register 11h.

Page: 8 (KS82C388)

# 1.3 Port B Register and NMI generation logic

The KS82C388 provides access to the Port B defined for PC/AT system level function control. The port can be accessed through any odd I/O port address between 61h and 6Fh. Table 1-1 shows the register definition:

BITS **READ/WRITE** DEFINITION Memory Parity Check 7 **READ ONLY PCK** 6 **READ ONLY** IO CH CK IO Channel Check 5 READ ONLY OUT 2 Timer 2 (8254) Out 4 **READ ONLY** REF DET Refresh Detect 3 READ/WRITE ENA IO CK\_ Enable IO Channel Check 2 **READ/WRITE** ENA RAM PCK\_ Enable RAM Parity Check **READ/WRITE** 1 SPKR DATA Speaker Data 0 **READ/WRITE** T2GATE SPK Timer 2 Gate Speaker

Table 1-1. Port B register Definition

The master enable for NMI (non-maskable interrupt) is programmed through bit 7 of system I/O port 70h inside the KS82C388. If this bit is set to 1, NMI generation is disabled and if set to 0, it is enabled. After bit 7 of system I/O port 70h is set to 0 and the corresponding NMIs are enabled in Port B, a non-maskable interrupt is generated to the CPU and the source of the NMI is latched in Port B. Bits <7:6> indicate a memory parity error (PCK) or an I/O Channel Check error (IOCHCK).

#### 1.4 Action Mode Codes Generation

This logic performs data buffer action mode codes generation for CPU accesses to devices on the CPU (D) bus, system (SD) bus, or memory (MD) bus. The AT bus conversions are performed for 16-bit and 8-bit read or write operations. 16-bit transfers to and from the CPU are broken into 16- or 8- bit AT bus cycles. The KS82C388 generates action mode codes for internal use. These codes control the buffers in the KS82C388 for byte alignment, direction control and data conversion between the D, MD and SD data buses. Data buffer action mode codes are also used by the KS82C388 to generate encoded Chip Select (CS\*) signals for on-board I/O ports.

Page: 9 (KS82C388)

# 1.5 CPU State Machine, Local Memory State Machines, Cache State Machine, AT Bus State Machine

In the original IBM AT architecture, the CPU and AT bus run at the same speed. In order to maintain AT compatibility and to achieve the highest system performance, the CPU, the local DRAM and cache memory are driven by CPUCLK while the AT bus is driven by ATSCLK. This allows the CPU and memories to operate at much higher frequencies, whereas the AT bus runs at an AT compatible 8 MHz speed. For synchronization, the KS82C388 contains several state machines to control all the accesses initiated by the CPU, DMA/AT Bus Master or Refresh Request Timer.

The CPU state machine, DRAM and Cache state machines control all the accesses to the local bus (DRAM, Cache SRAM or coprocessor cycles). These state machines support only 16-bit data transfers between the CPU and the system memory; therefore no bus conversions are required.

The AT bus state machine is responsible for all non-local bus accesses and controls the AT bus for proper bus conversions.

# 1.5.1 CPU State Machine

In the KS82C388, the CPU state machine provides the interface to the CPU. The CPU state machine monitors and decodes the bus status lines, ADS\*, W/R\*, M/IO\*, D/C\* and establishes the type of bus cycle to be performed. The CPU state machine begins its cycle upon assertion of ADS\* and terminates the cycle upon generation of READY\* at completion of the access.

For each new CPU cycle, the CPU state machine generates an internal signal CYCSTART (cycle start). It is sent to other state machines to indicate the beginning of a CPU cycle. Another internal signal LMEM16\* is generated by the memory controller module to distinguish a local memory access (DRAM or SRAM) from a non-local memory access. After generation of CYCSTART, the CPU state machine samples the LMEM16\* signal. If LMEM16\* is active, it is a local memory cycle and control passes to the local DRAM and Cache state machines. DRAM or cache state machine generates the READY\* to terminate the CPU cycle. However, if LMEM16\* is inactive, the control is passed to the AT state machine. The CPU state machine then waits for the generation of the READY\* signal from the AT state machine to terminate the cycle.

# 1.5.2 Local Memory State Machines

The DRAM array can be accessed by three different sources - CPU memory cycles, DMA/MASTER to local DRAMs, and refresh requests from the internal timer output. These different accesses are controlled by three different state machines in the KS82C388 DRAM module.

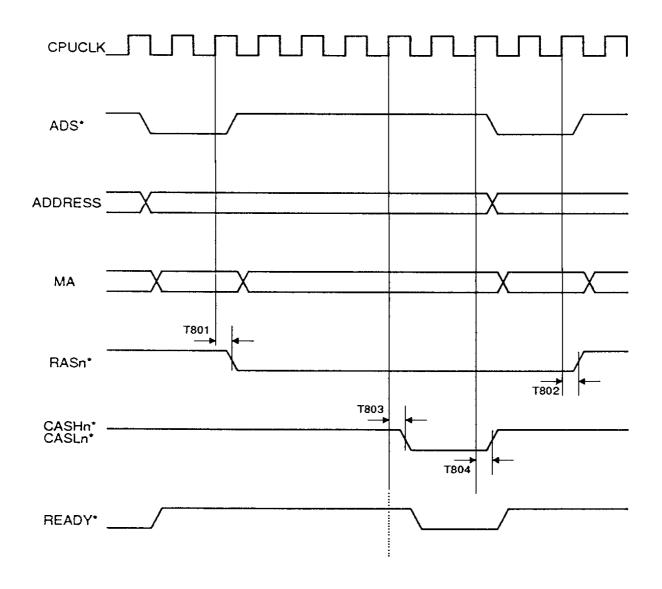

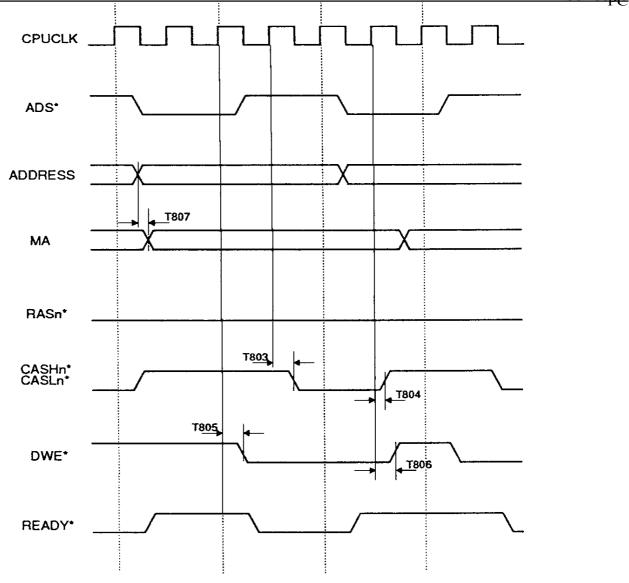

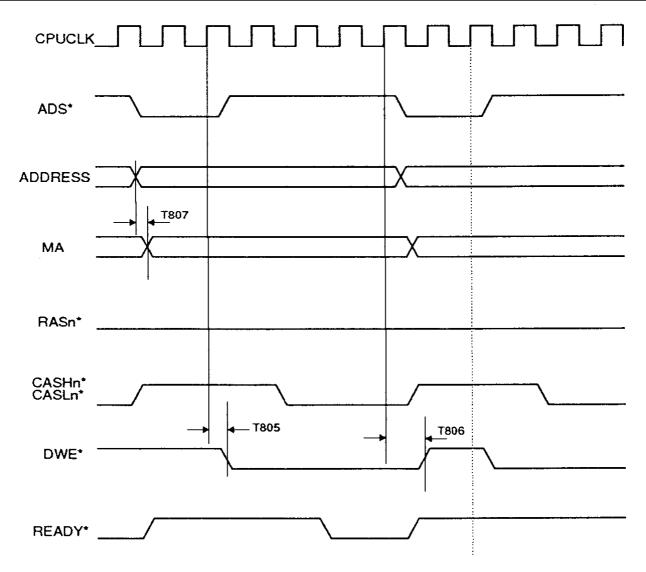

The KS82C388 DRAM controller can support one, two, three or four banks of local DRAMs. Each RAS\* line drives one DRAM bank, and each CAS\* line drives one byte of memory data. The DRAM row and column addresses are output on the MA<10:0> address pins.

When a memory location is decoded to be within the local DRAM range (LMEMI6\* active) and a cache miss/or a write hit cycle is detected, the CPU and Cache state machines pass control to the local DRAM state machine. The local DRAM state machine generates RAS<3:0>\*, CASH<3:0>\*, CASH<3:0>\*, DWE\*, and row/column address signals. The DRAM state machine also generates CWE\* to update the data cache during the cache read miss cycle. During a read miss the local DRAM state machine initiates two DRAM accesses with inverted and non-inverted A1 address for each cycle respectively.

The KS82C388 provides configuration registers to store memory system information for page mode, DRAM wait states, and shadow DRAM. For a "page hit" cycle, RAS\* stays asserted after the previous accesses. For a "page miss" the DRAM cycle starts by first de-asserting the RAS\* corresponding to the accessed bank. The local DRAM state machine also inserts programmed wait states into the DRAM cycle.

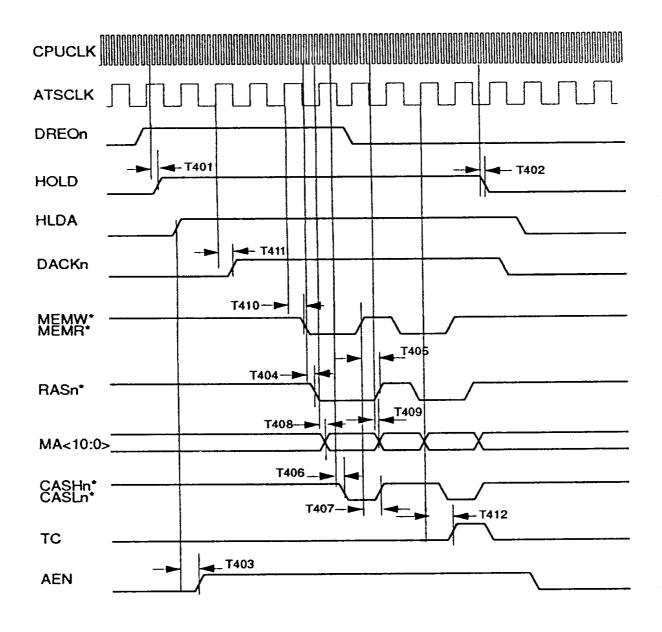

Local DRAMs can also be accessed by a DMA controller or an AT bus master. DMA/MASTER local DRAM access is initiated by asserting HLDA1(internal signal). The MEMR\* and MEMW\* determine if it is a read or write memory access per DMA/Master bus cycle. Local memory refreshes are controlled by a separate refresh state machine.

#### 1.5.3 Cache State Machine

The main function of the cache state machine in the KS82C388 is to manage the external tag directory and external cache memory through various CPU and DMA/Bus Master cycles. The KS82C388 runs in non-pipelined mode with zero or one wait state. For data coherency between the data SRAM and main memory, the cache state machine has to monitor the system bus used by the DMA controller or AT Bus Master. During a DMA/MASTER write hit cycle, when the other master overwrites DRAM contents of which the SRAM also has a copy, the cache state machine will update the data in the cache memory.

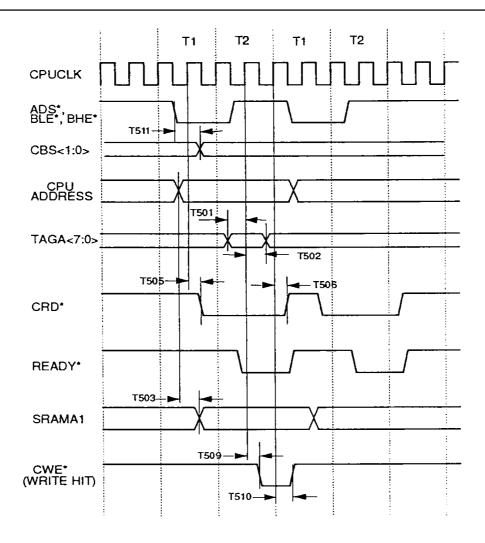

In zero wait state mode, a CPU cache read hit cycle completes the access in two T states. The cache state machine generates the READY\* signal back to CPU a quarter way into the second T state to terminate the cycle.

For one wait state, a CPU cache read hit cycle takes three T states to complete the access. The cache state machine generates a READY\* signal to the CPU at the beginning of the third T state.

For CPU memory cycles that are not cache read hits, the cache state machine passes control over to the DRAM or the AT state machine. This occurs at the middle of the second T state after ADS\* is active. One of the state machines generates the READY\* signal to the CPU and terminate the cycle. For the DRAM state machine, the number of T states between ADS\* and READY\* depends on whether RAS\* is active or inactive, page hit or miss, and the number of DRAM wait states programmed. Writing to cache SRAM is controlled by the cache state machine for cache write hit cycles. For read misses or cache line fill, the DRAM state machine controls the write operation to cache SRAM.

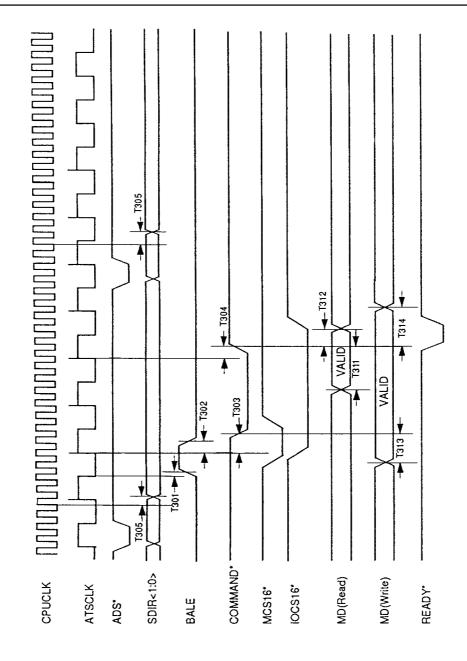

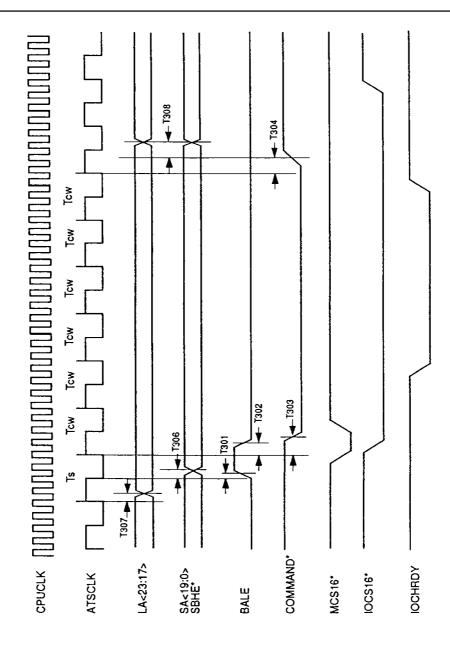

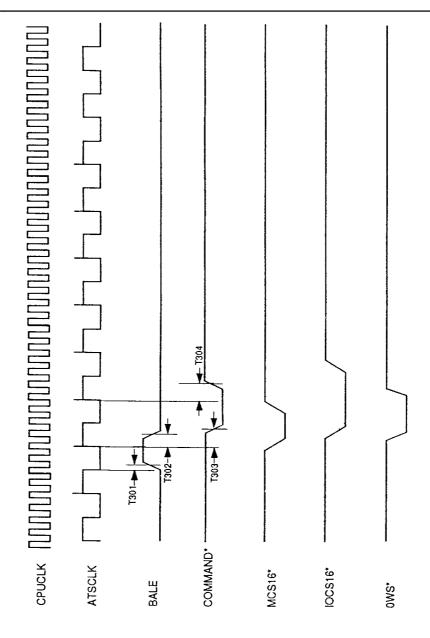

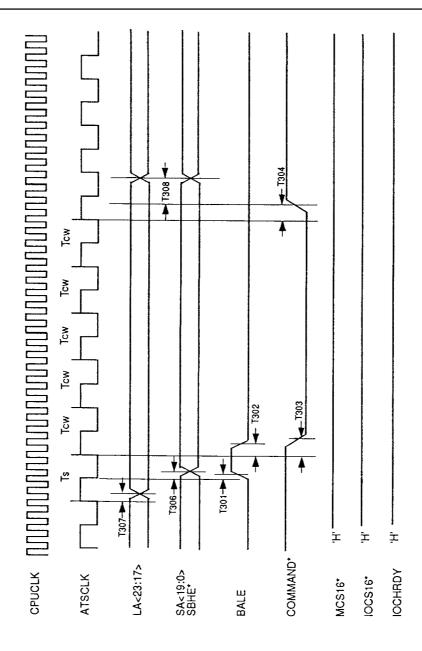

#### 1.5.4 AT Bus State Machine

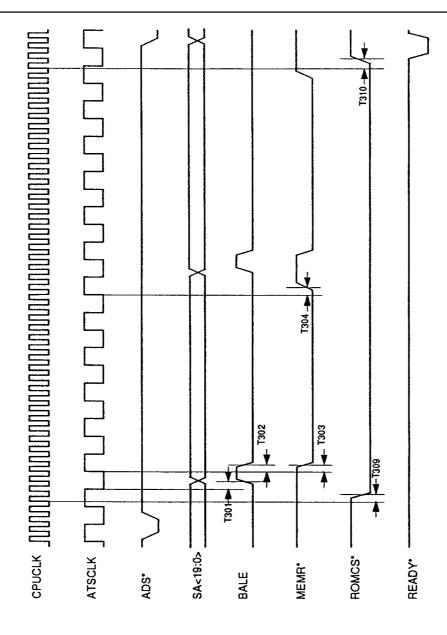

The AT bus state machine is invoked when CYCSTART is generated and LMEM16\* is inactive. The AT state machine is driven by ATCLK2, which runs twice the frequency of the AT bus clock (ATSCLK). The AT bus cycle is initiated by asserting the BALE signal and is terminated by asserting READY\*. The KS82C388 supports 8-bit or 16-bit transfers between the processor and 8-bit or 16-bit peripherals located on the AT bus. MCS16\* and IOCS16\* are sampled during the AT cycle to determine the bus size conversion and necessary byte alignment. For the AT memory cycle, MCS16\* is sampled at the falling edge of BALE. For the AT I/O cycle, IOCS16\* is sampled one-half of the ATSCLK after the falling edge of BALE to accommodate some slower I/O cards. If none of these 16-bit status signals are asserted, 8-bit transfers are assumed and the request is converted into 1 or 2 AT cycles based on BHE\* and BLE\*.

After BALE goes inactive, the AT state machine enters the command cycle. The command signals for the memory or I/O access remain active until the programmed number of wait states are executed. Bits <3:0> of register 11h control the AT Bus wait state generation for 8- and 16-bit accesses. Bits <5:4> provide the option to ensure enough recovery time for back to back I/O commands. The second I/O command is activated only after the programmed recovery time is satisfied.

After the programmed number of wait states are executed, IOCHRDY is sampled. If IOCHRDY is active (ready), the command becomes inactive after the next ATSCLK cycle. If IOCHRDY is not active (not ready), the commands are extended for an additional cycle (i.e., one ATSCLK) and IOCHRDY is sampled again. This process continues until IOCHRDY becomes active.

### 1.6 Bus Arbitration

The KS82C388 provides bus arbitration between CPU, DMA, AT bus Master and AT style refresh logic. HRQ, a level triggered signal from the on-chip 82C206, is active when a DMA or a Master is requesting a bus cycle. REFREQ, an edge triggered signal, initiates a DRAM refresh request from the refresh interval timer. The KS82C388 arbitrates between HRQ and REFREQ by sending a hold request (HOLD) to the CPU. The CPU responds to hold request (HOLD) by issuing HLDA to KS82C388 and relinquishes the CPU bus. The KS82C388 then issues HLDA1 (internal signal) or REF\* depending on which device prevailed during arbitration.

During a normal DMA cycle, the DMA controller has control of the bus until HRQ becomes inactive. During a refresh cycle, the refresh logic has control of the bus until REF\* goes inactive and will generate separate control signals for local DRAM as well as AT bus memory.

# 1.7 Coprocessor Support

The KS82C388 supports the interface logic for the 80387SX math coprocessor. Bus cycle generation is handled by the KS82C388. Interface signals consist of the input signal ER387\*, BZ387\*, PREQ387, and output signals BZ386\* and PREQ386.

At reset, the state of the ER387\* signal is sampled to detect the presence of the 80387SX coprocessor. The state is latched into bit 3 of register 12h.

The 80387SX asserts ER387\* after an operation resulting in an error not masked by the coprocessor's control register. The KS82C388 uses the ER387\* input to generate IRQ13.

During 80387SX operations, the CPU generates one or more I/O cycles to addresses 8000F8h through 8000FCh. The KS82C388 executes a local (non-AT) cycle and no DRAM or AT commands will be activated. When present, the 80387SX generates 387RDY\* at the end of the coprocessor cycle. In the absence of 80387SX, the KS82C388 will generate a ready signal (READY\*) to terminate the cycle.

Page: 13 (KS82C388)

#### 1.8 Cache Controller

The memory system in a PC/AT design is usually implemented with inexpensive, slow dynamic DRAMs. A cache memory is a small, high speed unit that resides between the CPU and the main memory. It increases the effective speed of the main memory by providing access to a copy of the most frequently used code or data from the main memory. When the CPU tries to read data from main memory, the high speed cache memory will respond first if the data resides in the cache memory (Hit cycle). Otherwise (miss cycle), a normal main memory cycle will take place.

A cache system can further enhance system performance by time-sharing cache and DRAM cycles. During write cycles, the data is held in a temporary buffer inside the KS82C388. Before the write cycle to main memory is completed, the CPU can access cache memory during a read hit cycle. However, if another read miss cycle or write cycle is performed, it has to wait until the previous write cycle is completed.

The KS82C388 integrates the cache controller and the DRAM controller into a single chip. When a read cycle starts, cache access and DRAM access are performed in parallel. In the case of a cache hit, DRAM commands to main memory are terminated and cache memory provides the data to the CPU. In the case of a miss, a DRAM cycle will be completed. The integrated cache controller reduces the time penalty during a miss cycle because it does not have to wait for a HIT/MISS signal from the external cache tag RAM to start a DRAM operation.

#### 1.8.1 Cache Performance

A cache reduces the average memory access time if it holds the most frequently requested code and data. The effectiveness of the cache is determined by the data cache size, line size, cache mapping scheme, cache replacement algorithm, and type of program execution.

The cache miss rate decreases with increasing data cache size. The gain is marginal, however, if the cache is 64KB or larger. The cache controller moves data from main memory to the cache during a miss cycle. A block is the basic unit of memory in that process. A typical block size (line size) is 4 bytes. A large line size increases the hit rate if the CPU is accessing consecutive addresses or repeating a short loop. On the other hand, a large line size takes longer to transfer and increases the likelihood of unneeded data being placed in the cache. In the KS82C388 direct mapped cache, each block holds one set of memory locations. The index field addresses are used to select one entry in the tag directory. The tag field addresses are compared with the contents of the tag directory to determine whether the access is a hit or a miss.

# 1.8.2 KS82C388 Cache Organization

The KS82C388 supports 16KB/32KB/64KB data cache options. The cache controller is a direct mapped organization.

Table 1-2 outlines direct mapped cache organization for the 16KB, 32KB and 64KB cache. It lists the physical address assignments of line select, set select, and tag field for all cache options supported by the KS82C388.

Table 1-2 Direct Mapped Cache Organization for 16KB, 32KB, and 64KB Data Cache

| CACHE DATA SIZE          | 16KB    | 32KB    | 64KB    |

|--------------------------|---------|---------|---------|

| Line Size(Byte per line) | 4       | 4       | 4       |

| Set #                    | 4K      | 8K      | 16K     |

| Line Select              | A1      | A1      | A1      |

| Set Select               | A2-A13  | A2-A14  | A2-A15  |

| Tag Field                | A14-A21 | A15-A22 | A16-A23 |

# 1.8.3 General Operations

In this section the following operations are illustrated in detail:

Read hit cycle Read miss cycle Write cycle DMA/Master cycle

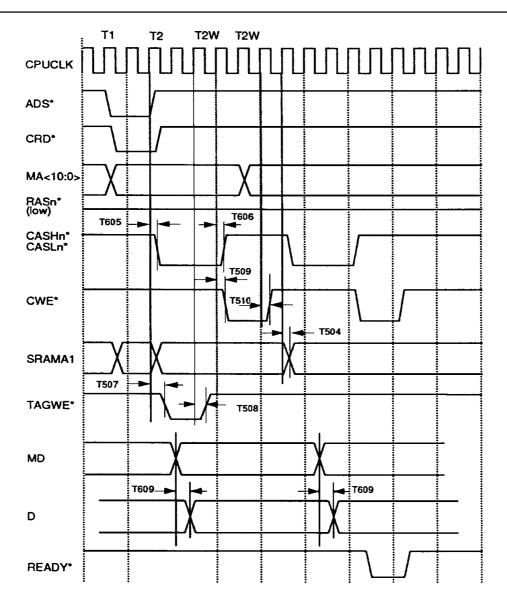

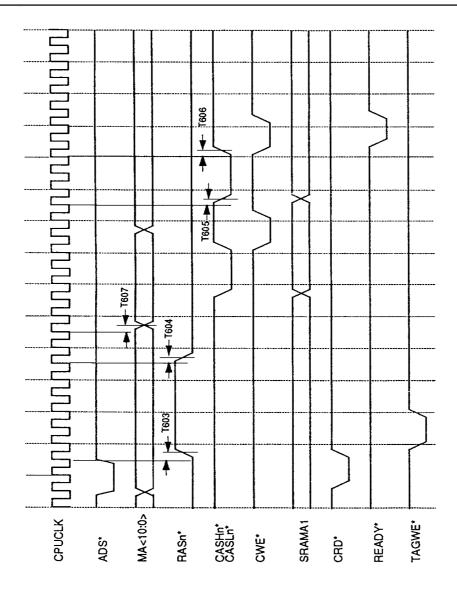

# 1.8.3.1 Read Hit Cycle

When the CPU starts a read cycle, the block (index) field of physical addresses selects a line from the cache directory. The tag bits stored in that location are compared with the CPU address inputs; a hit cycle is indicated when there is a match. The KS82C388 generates CRD\* to transfer data from cache memory to the CPU. A ready signal (READY\*) is sent to the CPU to terminate the cycle.

After power up, the tag directory is flushed by the BIOS. (During this time, the KS82C388 forces all local memory accesses to be DRAM cycles.)

Page: 15 (KS82C388)

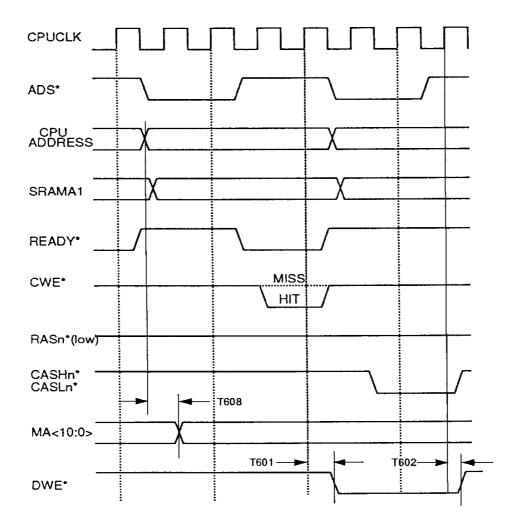

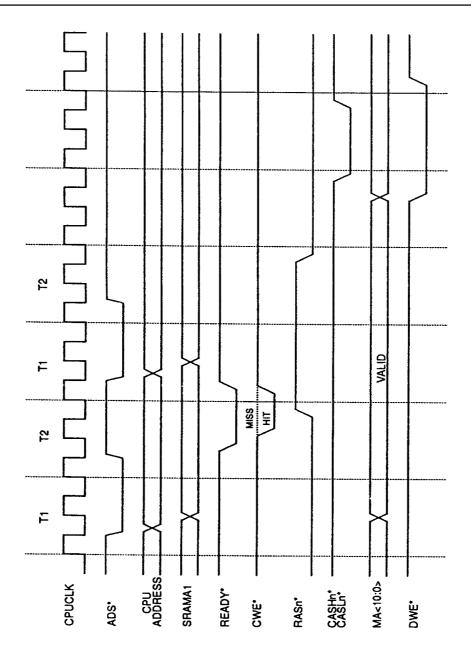

# 1.8.3.2 Read Miss Cycle

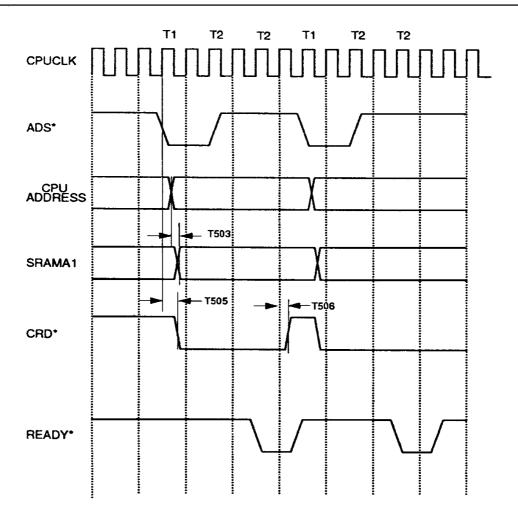

In a read miss cycle, the DRAM memory provides the data to the CPU and writes the same data to cache memory. The cache controller then updates the tag entry. The next time the same address is accessed, it will result in a hit cycle.

There are 4 bytes for each line. For each read miss cycle, two words are moved into the cache memory. Two DRAM accesses have to be completed before the current cycle can be terminated.

During the first data move-in and DRAM access, SRAMA1 drives inverted A1 address to data cache RAM and A1 is inverted to drive the DRAM address output. During the second data move-in and DRAM access, SRAMA1 returns to non-inverted A1 state and that same A1 drives the DRAM address output. At the end of the second DRAM access (non-inverted A1 access), the requested data is available on the CPU data bus and the ready signal, READY\* is generated to terminate the cycle.

### 1.8.3.3 Write Cycle

During a write miss cycle, no cache write or tag updates are performed. The CPU writes the data to the DRAM array without any interaction with cache memory. In the case of a hit access, CPU data is written to cache memory as well as to the DRAM array. This will ensure that cache memory maintains the same copy of data as the main memory so that no "stale data" problem occurs. Since a SRAM write is much faster than a DRAM write, additional wait states will be needed before the CPU data is copied into DRAM. In order to enhance system performance, the KS82C388 incorporates a "posted write" scheme. If the next cycle does not require DRAM accesses (cache hit, AT, I/O cycles), the write cycle is running an equivalent of a zero wait state to the CPU. However, if the following cycle requires another DRAM access while the DRAM is busy with the first write cycle, additional wait states will be asserted until the DRAM has completed its previous cycle.

### 1.8.3.4 DMA/MASTER Cycle

In an AT system, bus masters other than the CPU can access the main memory and alter its contents. When a cache hit access occurs within a master write cycle, data coherence between DRAM and cache memory must be maintained. The KS82C388 will update the cache for that tag location with the same data written into the DRAM. Subsequent CPU memory access to the same memory location will be a cache hit. For local memory read cycles initiated by another master or DMA controller, only local DRAM accesses will be activated.

# 1.8.4 Other Issues in Cache System Design

### 1.8.4.1 Non-Cacheable Regions

The KS82C388 provides one non-cacheable region to allow the user to set aside one blocks (size ranges from 1KB to 1MB) of address space as non-cacheable. The starting address of any non-cacheable region has to be on a boundary of that region's size. This region can then be used as ROM area, memory-mapped I/O space, shared memory accessed by multiple masters, or any other memory areas that should not be cacheable. Once the region is defined as non-cacheable, the memory operation can be re-directed to either local DRAM access or AT memory access via bits <7:6> in index register 50h. Non-cacheable features are defined through index registers 50h to 52h.

# 1.8.4.2 Direct SRAM and Tag RAM access

For diagnostic purposes, the contents of data cache and TAG RAM can be directly accessed by the CPU. Direct SRAM access is defined in index register 60h. If this feature is enabled, then the cache data RAM will be treated as an extension of main memory with 16KB/32KB/64KB block size at starting address 040000h. These features make system debugging and initialization easier, i.e., line invalidation, tag RAM, or data caches RAM purge.

Page: 17 (KS82C388)

#### 1.9 DRAM Controller

# 1.9.1 DRAM Operation

The KS82C388 supports page mode of memory access. The BIOS, following reset, provides automatic detection of the number of banks of DRAM present and the DRAM type present within each bank. If different types of DRAM are used, the largest type of DRAM must be in the first bank.

For normal DRAM access, both RAS\* and CAS\* have to be activated. The memory access time is determined by the Row Address Access time (Trac) rather than the much faster Column Address Access time (Tcac). Page mode DRAMs allow a number of locations within an area of memory (page) to be accessed without repeating the entire address. After providing the row address and asserting RAS\*, the column address can be changed a number of times to access a series of locations. Each time a new column address is strobed by CAS\*, RAS\* must be kept asserted throughout the process. The number of cycles that can be performed is limited by the maximum length of the RAS\* active pulse width. The effectiveness of the page-mode DRAM subsystem is determined by the page size and the locality of the program being executed. The page size can be increased by using higher density DRAMs. Table 1-3 illustrates the effective page size for different types of DRAM.

| DRAM type | Each bank |

|-----------|-----------|

| 256Kb x N | 1 KBytes  |

| 1Mb x N   | 2 KBytes  |

| 4Mb x N   | 4 KBvtes  |

Table 1-3 Effective Page Size for DRAMs

# 1.9.2 Refresh Logic

The KS82C388 provides the following refresh schemes:

- AT refresh

- Slow refresh option

# 1.9.2.1 AT Refresh

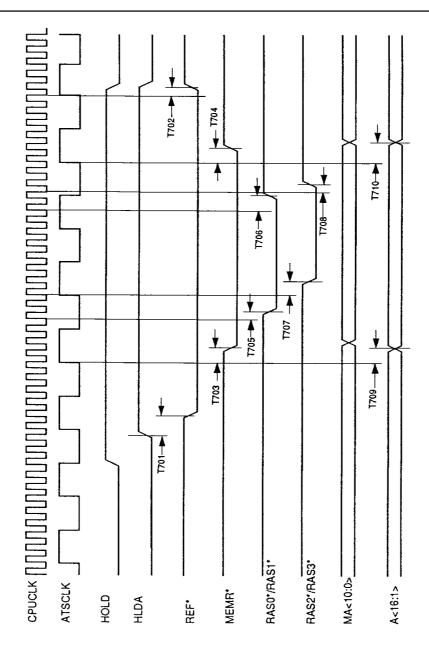

In an AT refresh scheme, the KS82C388 arbitrates the bus after receiving the REFREQ from the internal refresh interval timer and generates HOLD request to the CPU. The CPU relinquishes the bus by issuing the HLDA. The KS82C388 in turn will respond with the REF\* and starts the AT refresh cycle. The local DRAM will be refreshed with RAS\* active for all banks at the same time the AT bus is refreshed. For refresh, the internal refresh counters provide refresh addresses onto the MA<10:0> and the SA<10:0> and MEMR\* and all RAS\* lines are asserted.

#### 1.9.2.2 Slow Refresh

Slow refresh is an option provided for local DRAM refresh, not for an AT refresh. Instead of generating refresh request at a rate of 256 per 4ms, the Refresh control register (index 47H, bit 1 & 0) of the KS82C388 can be set to allow slower refresh rate, e.g., 128 per 4ms, 64 per 4ms or 32 per 4ms. The ability to run slow refresh option depends on the local DRAM used. This option is usually applicable when Low power DRAMs are used for local memory.

The KS82C388 refresh logic also provides a special mechanism to reduce system noise during simultaneous refreshing of each DRAM bank. RAS2\* and RAS3\* are delayed, after RAS0\* and RAS1\* are generated, to allow the refresh cycle for bank 2 and bank 3 to be performed immediately after refresh of bank 0 and bank 1. This "staggered Refresh" scheme results in a reduction of system level noise when multi-bank local DRAMs are installed.

### 1.9.3 Shadow RAM

It is preferable to execute codes through the faster local memory (DRAM or Cache RAM) than through the slower EPROMs. System performance can be enhanced by having the BIOS codes reside in local memory, rather than in EPROMs. This is especially true for applications with extensive BIOS calls. The KS82C388 provides a SHADOW RAM feature that, when enabled, allows the BIOS codes stored in the EPROMs to be executed (shadowed) from the local RAM area. However, these BIOS codes need to be transferred from EPROMs into local RAMs prior to use of the SHADOW RAM feature. A the KS82C388 implementation, this transfer is accomplished at system initialization by means of the following procedure:

- 1) Set register bits in configuration register 41h-44h for different memory access method

- 2) Copy ROM block to Shadow DRAM block

- 3) Set Corresponding bits in configuration register 41h-44h for blocks that are write protected.

The KS82C388 can shadow any DRAM block with an address from 0C0000H to 0FFFFFH (i.e., the C, D, E and F block) in 16KByte granularity. In another word, 256KBytes of total DRAM at 16KByte per chunk can be selectively activated for shadowing. With the cache option turned on, the shadow RAM region is then cacheable after the BIOS or other codes are copied into local DRAM. Special attention needs to be made to prevent any write operation onto the shadowed area. This is accomplished by setting write protection bits in procedure 3.

Page: 19 (KS82C388)

# 1.9.4 Memory Remapping

The KS82C388 memory remapping logic is able to remap physical memory locations between 640KB to 1MB (address 0A0000 to 0FFFFFH) in 64KByte chunks to the top of total system memory, provided that no portion of the 64KByte is shadowed. This feature is designed not to be limited by the amount of populated system DRAM.

A 64KByte block is not remappable even if only one 16KByte chunk is shadowed.

Special consideration has been given to the remapping logic so that the KS82C388 not only provides up to 384KBytes of remapping capability, but also assures all remapped memory to be contiguous on top of the total system memory.

The 384KByte reserved area at memory locations between 0A0000h and 0FFFFFH can be subdivided into A, B, C, D, E and F blocks, each with 64 KBytes. The KS82C388 supports the following remapping schemes:

- 1) No remap

- 2) A,B

- 3) A,B,D

- 4) A,B,D,E

- 5) A,B,D,E,C

- 6) A,B,D,E,C,F

While block A, B are remapped on top of the system memory, block "X" is remappable if no shadowed area exists within the block. Block "X" will be remapped by the KS82C388 if and only if:

- i) It is remappable and

- ii) corresponding remap control bit in index register 45h is set to 1;

- iii) Other block(s) to the left of block "X" is also remapped, based on the series of combination stated above.

Refer to Remapping Scheme Figure on the next page for detailed remap implementation.

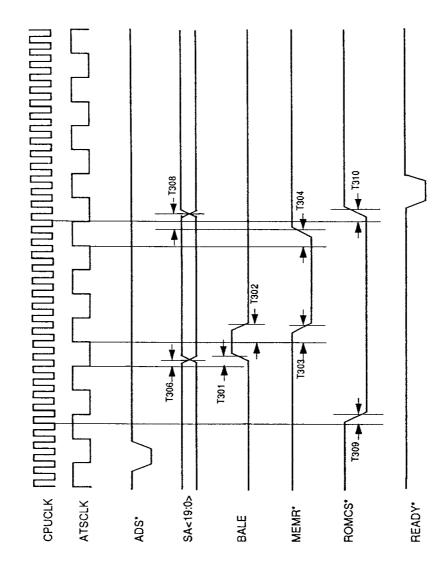

# 1.9.5 EPROM Control Logic

The KS82C388 provides control logic to generate the ROMCS\* signal for an EPROM access. The AT bus state machine generates the READY\* for this cycle. ROMCS\* is connected to the EPROM chip enable (CE\*) input. Since the KS82C388 supports both 8 and 16 bits of ROM, it needs to generate appropriate action codes indicating 8 bits or 16 bits ROM access. These action codes are used within the KS82C388 to transfer ROM data to the CPU data bus. 8 or 16 bits ROM selection is done by strapping DACK7 pin during system reset and the state of the DACK7 pin is latched into the bit 2 of register 40h.

Page: 20 (KS82C388)

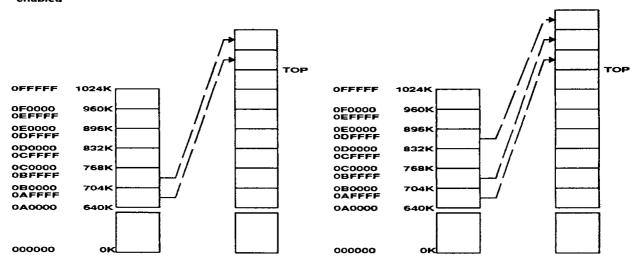

- The system always remaps 640K to 768K to top of physical memory, if remap is enabled

- 2. From 832K to 896K area is remapped to top of 640K to 768K area.

3. From 832K to 960K area is remapped to top of 640K to 768K area.

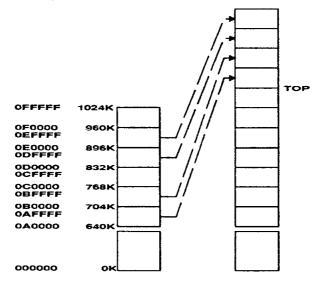

Figure 1-1. KS82C388 Remapping Scheme

Figure 1-2. KS82C388 Remapping Scheme (Continued)

# 1.9.6 OS/2 Optimization

The KS82C388 provides two specific features that are further enhancements to the criginal IBM AT design:

- · Fast Gate A20 (bit 1 of port 92h)

- · Fast Reset CPU (bit 0 of port 92h)

The OS/2 operating system developed by IBM and Microsoft has two operating mode. The OS/2 mode operates on CPU protected address region while DOS mode operates on CPU real address region. In the OS/2 mode, the operating system can make many function calls in DOS mode. The CPU needs to switch from Protected Mode to Real mode before the DOS call could be executed. A CPU reset (RSTCPU) is one way to make the mode change without executing a cold reset (Power Down/On). The address A20 must be switched low before the CPU changes to Real mode. This is necessary to assure downward compatibility with the 8086.

Both functions in the original PC/AT design were handled through the keyboard controller (8042). The interface between the CPU and the keyboard controller is very slow. To switch from Protected to Real mode, the CPU needs to set A20 low and reset the CPU. For each operation, the CPU checks the keyboard controller ready status and issues commands to the keyboard controller. The KS82C388 provides both functions through much faster I/O operations.

In the KS82C388 implementation, Fast Gate A20 is a read/write bit controlling internal address bit A20. This bit is set to 1 during system reset allowing CPUA20 from the 80386SX to pass onto address A20. Writing a 0 into this bit will force the address A20 to be low.

The Fast Reset CPU read/write bit (Bit 0 of port 92h) is set to 0 during system reset (cold reset). To generate Fast Reset CPU during normal operation, the CPU only needs to execute two I/O write cycles for this bit to make 0 to 1 transition. The RSTCPU pin is pulled high after a 2µs delay or until a HALT state is detected(if the bit 2 of the register 1Bh), whichever is earlier.

Page: 23 (KS82C388)

# 1.9.7 Memory Subsystem Design Specification

The following table describes the SRAM, DRAM speed required for a certain performance level as related to the CPU clock frequency.

Table 1-4. CPU/SRAM/DRAM Speed vs. Wait States (MODE1 only)

| CPU<br>Clock Freq. | SRAM<br>Tag / Cache<br>Addr. Access | DRAM<br>(Cache based)<br>tRAC | Cache Read<br>Hit |

|--------------------|-------------------------------------|-------------------------------|-------------------|

| 16 MHz             | 45 ns / 55 ns                       | 120 ns                        | 0 w.s.            |

| 20 MHz             | 35 ns / 45 ns                       | 100 ns                        | 0 w.s.            |

| 25 MHz             | 25 ns / 35 ns                       | 80 ns                         | 0 w.s.            |

| 33 MHz             | 20 ns / 25 ns                       | 70 ns                         | 0 w.s.            |

| 40 MHz             | 15 ns / 20 ns                       | 60 ns                         | 0 w.s.            |

Table 1-5. CPU/DRAM Speed vs. Wait States (MODE2 only)

| CPU<br>Clock Freq. | DRAM<br>tRAC | DRAM Read<br>Page Hit |

|--------------------|--------------|-----------------------|

| 16 MHz             | 120 ns       | 0 w.s.                |

| 20 MHz             | 100 ns       | 0 w.s.                |

| 25 MHz             | 80 ns        | 0 w.s.                |

| 33 MHz             | 70 ns        | 0 w.s.                |

Page: 24 (KS82C388)

#### 1.10 Action Decode and Control

The activities within the KS82C388 are initiated by internally generated action codes that originate in the Action Mode Generation Logic (see Figure 0-2a). The action codes determine what the current bus cycle is and prompt the Action Decode and Control logic (see Figure 0-2b) to control the direction of data flow by decoding these codes together with REF\*, SA0, and SBHE\*.

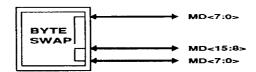

#### 1.11 Data Transfer Modules

As shown in the block diagram (Figure 0-2b), there are 4 data transfer modules. Each of these is controlled by the internal control signals generated by the Action Decode and Control module. Figure 1-3 demonstrates the memory and bus organization in a cached systems.

Figure 1-3. Memory and Data Bus Organization

The description and function of each of the data transfer modules, as they operate within a cached system, are given below.

#### 1.11.1 CPU/DRAM Data Transfer Module

The CPU/DRAM Data Transfer Module controls the data flow between the CPU and the main memory. During memory write, CPU data is latched by WDLE and driven onto the MD bus. During memory read, the memory data is latched by DLE and driven onto the D bus. The data flow involved is shown in Figure 1-4.

Figure 1-4. CPU/DRAM Data Transfer

#### 1.11.2 CPU/AT/IO/ROM Data Transfer Module

The CPU/AT-BUS/IO/ROM Data Transfer Module controls data flow between the CPU and the AT Bus, peripherals and system BIOS ROM. The data flows for 16-bit transfers are shown in Figure I-5a.

Figure 1-5a. CPU/AT/IO/ROM 16-bit Data Transfer

The data flows for 8-bit transfers are shown in Figure 1-5b.

Figure 1-5b. CPU/AT/IO/ROM 8-bit Data Transfer

# 1.11.3 DMA Cycles Transfer Module

The DMA Cycles Transfer Module, via the use of SDIR<1:0>, limits its control of 8-bit/8-bit and 16-bit/16-bit DMA transfers to data flow direction between the main memory MD bus and the AT SD bus. The data transfer between an 8-bit AT SD bus I/O and 16-bit AT SD bus memory is accomplished through a byte-swap mechanism as shown in Figure 1-6.

Figure 1-6. 16-bit AT Memory / 8-bit AT I/O DMA Memory Cycles Transfer

# 1.11.4 MASTER Cycles Transfer Module

In a cached system, the MASTER Cycles Transfer Module limits its control to data flow direction, vias the use of SDIR<1:0>, between the AT SD bus and the main memory MD bus.

CD-ROM(Edition.1.1) This Data Sheet is subject to change without notice.

(C) 1994 Samsung Electronics Printed in Korea.

# 1.12 Parity Handler

In order to maintain data integrity, the KS82C388 generates a parity bit for each byte of data written to local memory and also provides parity check to detect any mismatch whenever data is read from local memory.

During the local memory write cycle, source data (CPU, DMA or Master) is passed to the MD bus as well as to the parity generation logic. The parity generator generates one parity bit for each byte of write data and passes this bit to the memory parity outputs MP<1:0>. The memory write data (MD<15:0>) together with the parity bits (MP<1:0>) are written into the DRAM when the proper row address and/or column address strobes are issued by KS82C388.

During the local memory read cycle, memory data MD<15:0> and memory parity bits MP<1:0> are latched into the KS82C388. The MD data is redirected to the proper destinations (CPU, DMA or Master) as well as to the parity check logic. The parity check logic will regenerate new parity bits from the memory read data, one bit per byte, and compare them with the read memory parity bits.

The byte parity error bits are OR'ed together and latched to generate an internal parity error signal. The KS82C388 then generates an NMI (if it is enabled) to the CPU. Upon completion of error diagnosis, the parity error bit must be reset.

### 1.13 Timer Clock

The KS82C388 uses the OSCX1 (14.31818 MHz) oscillator input to derive the OSC119 internal clock signal by dividing OSCX1 by 12. This clock signal is used by the on-chip 82C206 Timer/Counter to perform the following functions under software control: timer, rate generator, pulse or square wave generators, and strobe signal. It is also used in the KS82C388 for refresh counters.

Page: 27 (KS82C388)

# 1.14 Local Bus Support

The KS82C388 provides hardware support to permit a peripheral controller to reside on the local or CPU bus. This results in faster data transfer rates between the CPU and the controller, whose data rates on the PC/AT bus would otherwise be restricted by that bus's bandwidth. A peripheral controller on the local bus can operate at the same frequency as the CPU.

# 1.14.1 Local Bus Hardware Support

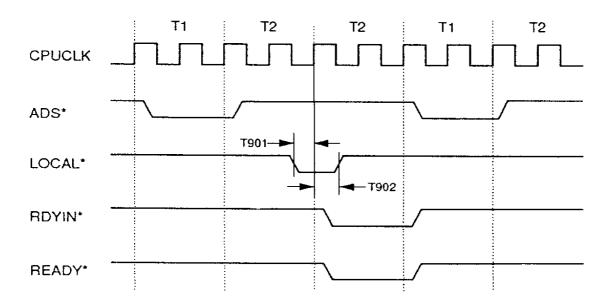

The LOCAL\* and the RDYIN\* pins permit peripheral controllers to share the local bus with the KS82C388. These might include VGA graphics controllers. Data on the Local or CPU bus can be transferred as the CPU clock rate instead of the more restrictive 8 MHz rate associated with the PC/AT bus.

When a local peripheral wants access to the Local bus, it must assert the LOCAL\* input to the KS82C388. The KS82C388 samples the LOCAL\* input at the end of the T2 state. If it is detected LOW, the KS82C388 releases control of and ceases futher access to the Local or CPU bus. The current cycle execution is suspended.

At the end of the cycle, the local peripheral controller must generate a RDYIN\* signal to terminate the cycle. This ready signal (RDYIN\*) is sampled by the KS82C388 to detect when to resume cycle execution. If Bit 6 of configuration register 3Ah is set to zero, RDYIN\* is internally directly connected or passed through to become READY\* as the READY to the CPU. If Bit 6 is set to one, the RDYIN\* is first synchronized with the CPU clock, then output to READY\*. (If no RDYIN\* is detected within 3.4µs to 6.8µs from the LOCAL\* input, the KS82C388 generates READY\* to terminate the cycle.)

Page: 28 (KS82C388)

# 1.15 Pins used for internal configuration

At system reset, DACK[7:5] pins are used to configure the KS82C388 operation modes. They should be strapped according to the following descriptions.

# 1.15.1 8 Bit / 16 Bit ROM selection

8 or 16 bit ROM selection can be accomplished by strapping the DACK7 pin.

0:8 Bit ROM, 1:16 Bit ROM

At system reset, the state of the DACK7 is inverted and latched into the bit 2 of the register 40h.

### 1.15.2 Mode selection

The KS82C388 can be configured into two different modes of operation by strapping the DACK6 pin according to the following table:

| MODE | DACK6 | DESCRIPTION                                                                      |

|------|-------|----------------------------------------------------------------------------------|

| 1    | 0     | Cache mode. DRAM banks reside on MD bus and the cache controller is enabled.     |

| 2    | 1     | Non-cache mode. DRAM banks reside on D bus and the cache controller is disabled. |

At system reset, the state of the DACK6 pin is latched into the bit 1 of the register 40h. The following is the description of the pins that are multiplexed for the two different operating modes:

| NAME                    | TYPE       | DESCRIPTION        |                                                             |  |

|-------------------------|------------|--------------------|-------------------------------------------------------------|--|

| TAGA[7:0] \<br>SA[8:1]  | 1/O<br>1/O | Mode 1:<br>Mode 2: | TAG Address bits 7 - 0.<br>System Address bus bits 8 - 1.   |  |

| TAGWE* \<br>SA9         | O<br>1/O   | Mode 1:<br>Mode 2: | TAG Write Enable.<br>System Address bus bit 9.              |  |

| SRAMA1 \<br>SA10        | 0 1/0      | Mode 1:<br>Mode 2: | SRAM Address bit 1.<br>System Address bus bit 10.           |  |

| CBS[1:0] \<br>SA[12:11] | O<br>1/O   | Mode 1:<br>Mode 2: | Cache Byte Select bits 1, 0. System Address bus bits 12,11. |  |

| CWE*\<br>SA13           | 0 1/0      | Mode 1:<br>Mode 2: | Cache Write Enable.<br>System Address bus bit 13.           |  |

| CRD* \<br>SA14          | 0 1/0      | Mode 1:<br>Mode 2: | Cache Read enable.<br>System Address bus bit 14.            |  |

| SADIR \<br>SA15         | O<br>1/O   | Mode 1:<br>Mode 2: | SA bus Direction control.<br>System Address bus bit 15.     |  |

Note: DACK5 pin is used for the internal mode setting. It should always be strapped to low...

Page: 29 (KS82C388)

Index: 01H

# 1.16 AT peripheral controller (On-chip 82C206)

The KS82C388 provides on-chip AT peripheral controller, which is functionally equivalent to 82C206. The AT peripheral controller logic consists of two 8237 DMA controllers, two 8259 Interrupt controllers, one 8254 Timer/Counter, one Real Time Clock and 74LS612 memory mapper.

# 1.16.1 Clock and Wait State Control

Clock and Wait State Control Register

The Clock and Wait State Control logic controls the DMA command width, the CPU Read/Write cycle length and selection of the DMA clock rate. Theses functions are programmable by writing to the Configuration Register described below. Reading and writing to this register is accomplished by first writing a 01H to I/O location 22H and then read or write to I/O location 23H.

| Bit 7 | 6                                             | 5                                                                                                        | 4               | 3                             | 2        | 1   | 0   |  |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|----------|-----|-----|--|

| RW1   | RW0                                           | 16W1                                                                                                     | 16W0            | 8W1                           | 8W0      | EMR | CLK |  |

| Bits  | Value                                         |                                                                                                          |                 |                               |          |     |     |  |

| 7:6   | increm<br>00: Read/<br>01: Read/<br>10: Read/ | <ul> <li>01: Read/Write Cycle Wait States = 2.</li> <li>10: Read/Write Cycle Wait States = 3.</li> </ul> |                 |                               |          |     |     |  |

| 5:4   | 00: 1 wait<br>01: 2 wait<br>10: 3 wait        | DMA Wait Sta<br>state; Default.<br>states.<br>states.<br>states.                                         |                 |                               |          |     |     |  |

| 3:2   | 00: 1 wait<br>01: 2 wait<br>10: 3 wait        | OMA Wait State<br>state; Default.<br>states.<br>states.<br>states.                                       |                 |                               |          |     |     |  |

| 1     | 0: MEMF                                       | ded MEMR* ful<br>R* is delayed 1<br>R* is asserted a                                                     | clock cycle lat | er than IOR*; D<br>e as IOR*. | Default. |     |     |  |

| 0     | DMA (                                         | Clock Selection                                                                                          | 1               |                               |          |     |     |  |

DMA Clock = ATSCLK/2; Default.

DMA Clock = ATSCLK.

Page: 30 (KS82C388)

### 1.16.2 DMA Controller

The DMA control logic has two 8237A compatible DMA controllers and 74LS612 memory mappers. Each controller has four DMA channels and will generate the memory addresses and control signals necessary to transfer information between an I/O channel and memory.

The two DMA controllers are internally cascaded to provide four DMA channels for transfers to 8-bit peripherals (DMA1), and three channels for transfers to 16-bit peripherals (DMA2). DMA2 channel 0 provides the cascade interconnection of the two DMA controllers.

# 1.16.2.1 DMA Registers

The two DMA controllers can be programmed any time HLDA is inactive. Table 1-7 lists the register address assignment. An internal flip-flop is used to supplement the addressing of the Count and Address registers. This bit is used to select between the high and low bytes of these registers. The flip-flop will toggle each time a read or write occurs to any of the Word Count or Address registers in the DMA. This internal flip-flop will be cleared by hardware reset, or a Master Clear command and may be set or cleared by the CPU issuing the appropriate command.

The internal 82C206 will enable programming whenever HLDA has been inactive for one DMA clock cycle. Erratic operation can occur if a request for service occurs on an unmasked channel which is being programmed.

#### 1.16.2.2 Address Generation

At the beginning of a DMA operation (during state S1), the intermediate addresses are output on the internal data lines XD0-XD7. These 8-bit addresses are latched by the internal address bit latches and used to drive the system address bus. Since DMA1 is used to transfer 8-bit data and DMA2 is used to transfer 16-bit data, an one bit skew occurs in the intermediate address fields. DMA1 will therefore output addresses A8-A15 on the data bus whereas DMA2 will output A9-A16.

During 8-bit DMA cycles, the lower address bits are output on A0-A7. The intermediate 8-bits of address are internally latched and output on A8-A15. A16-A23 are generated from a DMA Page Register.

During 16-bit DMA cycles, the lower address bits are output on A1-A8. The intermediate addresses are internally latched and output on A8-A15. The DMA Page Register now generates A17-A23.

| ADD   | RESS  | OPER       | ATION        | Flip-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA1  | DMA2  | IOR*       | IOW*         | Flop         | Register Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 000h  | 0C0h  | 0          | 1            | 0            | Read Channel 0 Current Address Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |       | 0          | 1            | 1            | Read Channel 0 Current Address High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       |       | 1 1        | 0            | 0            | Write Channel 0 Base and Current Address Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0041  | 0.001 |            | 0            | 1            | Write Channel 0 Base and Current Address High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 001h  | 0C2h  | 0          | 1            | 0            | Read Channel 0 Current Word Count Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       |       | 1          | 1            | 1 0          | Read Channel 0 Current Word Count High Byte Write Channel 0 Base and Current Word Count Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |       | i          | ŏ            | 1            | Write Channel 0 Base and Current Word Count High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 002h  | 0C4h  | 0          | 1            | 0            | Read Channel 1 Current Address Low Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |       | 0          | 1            | 1            | Read Channel 1 Current Address High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |