#### MULTISTANDARD VIDEO DECODER/SCALER

The KS0127B converts analog NTSC, PAL or SECAM video in composite, S-video, or component format to digitized component video. Output data can be selected for CCIR 601 or square pixel sample rates in either YCbCr or RGB formats. The digital video can be scaled down in both the horizontal and vertical directions. The KS0127B also decodes Intercast, Teletext, Closed Caption, and WSS data with a built-in bit data slicer. Digitized CVBS data can be output directly during VBI for external processing.

# **FEATURES**

- Accepts NTSC-M/N/4.43, PAL-M/N/B/G/H/I/D/K/L and SECAM formats with auto detection

- 6 analog inputs: 3 S-video, 6 composite, or 1 3-wire YCbCr component video

- 2-line luma and chroma comb filters including adaptive luma comb for NTSC

- Programmable luma bandwidth, contrast, brightness, and edge enhancement

- Programmable chroma bandwidth, hue, and saturation

- · High quality horizontal and vertical down scaler

- Intercast, Teletext and Closed Caption decoding with built-in bit slicer

- Direct output of digitized CVBS during VBI for Intercast application

- Analog square pixel or CCIR 601 sample rates

- Output in 4:4:4, 4:2:2, or 4:1:1 YCbCr component, or 24-bit or 16-bit RGB formats with dithering

- YCbCr 4:2:2 output can be 8 or 16 bits wide with embedded timing reference code support for 8-bit mode

- Simultaneous scaled and non-scaled digital output ports outputs for 8-bit mode.

- · Direct access to scaler via bi-directional digital port.

- Programmable Gamma correction table

- Programmable timing signals

- Industry standard IIC interface

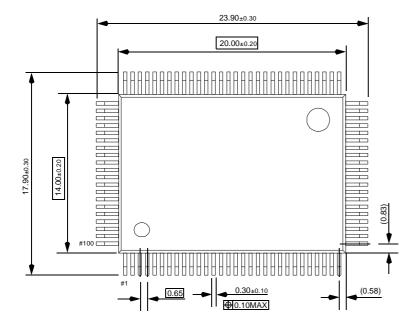

#### ORDERING INFORMATION

| Device  | Package  | Temperature Range |

|---------|----------|-------------------|

| KS0127B | 100 PQFP | -20°~+70°C        |

#### **APPLICATIONS**

- Multimedia

- Digital Video

- · Video Capture/Editing

# **RELATED PRODUCTS**

- KS0119Q2 NTSC VIDEO ENCODER

- KS0123 MULTISTANDARD VIDEO ENCODER

- KS0125 MULTISTANDARD VIDEO ENCODER

- KS0122 MULTISTANDARD VIDEO DECODER

- KS0127 MULTISTANDARD VIDEO DECODER

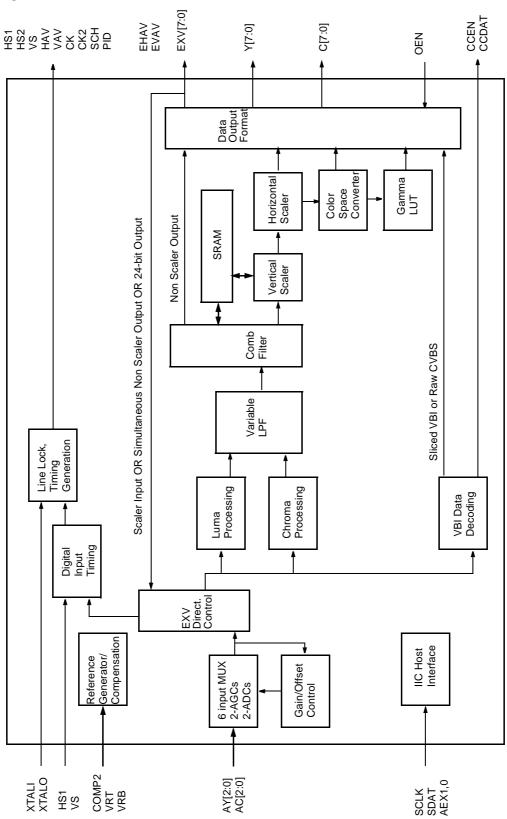

# **BLOCK DIAGRAM**

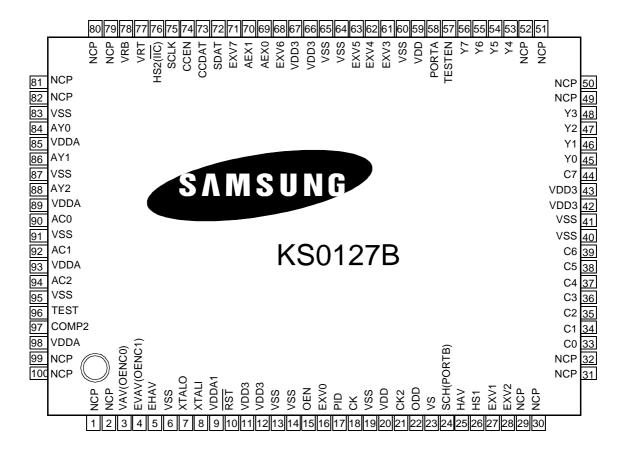

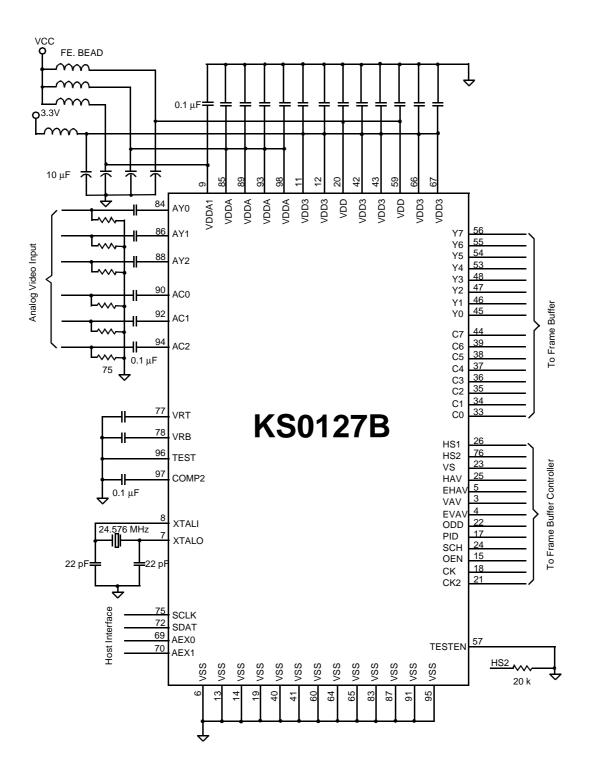

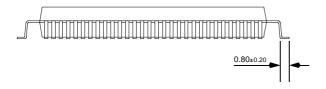

# **PIN ASSIGNMENT - 100 PQFP**

# **PIN DESCRIPTION**

| Pin Name | Pin # | Туре | Description                                                                               |

|----------|-------|------|-------------------------------------------------------------------------------------------|

| INPUT    |       |      |                                                                                           |

| AY0      | 84    | 1    | 1 of 6 analog CVBS or 1of 3 S-video Y inputs.                                             |

| AY1      | 86    | 1    | 1 of 6 analog CVBS or 1of 3 S-video Y inputs.                                             |

| AY2      | 88    | I    | 1 of 6 analog CVBS input or 1 of 3 S-video Y inputs or Y input for 3 wire component input |

| AC0      | 90    | 1    | 1 of 6 analog CVBS or 1 of 3 S-video C inputs.                                            |

| AC1      | 92    | I    | 1 of 6 analog CVBS or 1 of 3 S-video C inputs or Cb input for 3 wire component input      |

| AC2      | 94    | I    | 1 of 6 analog CVBS or 1 of 3 S-video C inputs or Cr input for 3 wire component input      |

| XTALI    | 8     | I    | Pin 1 for an external crystal or TTL clock input.                                         |

| XTALO    | 7     | 0    | Pin 2 for an external crystal.                                                            |

| RST      | 10    | 1    | Chip reset. Active low signal.                                                            |

# **OUTPUT (All output pins can be selectively three-stated)**

| Y0 - Y7, C0 - C7 | 45-48,53-56,33-<br>39,44 | 0   | Digital video outputs.                                                                                                                                                                                                                               |

|------------------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXV0 - EXV7      | 16,27,28,61-63,<br>68,71 | I/O | Expanded digital video I/O port. Can be configured as an additional 8-bit output port (no scaling), or additional outputs of the main digital output stream for 24 bit output modes, as an 8-bit input for direct digital access of the down scaler. |

| HS1              | 26                       | I/O | Programmable horizontal timing signal. One pulse every video line. When the EXV port is configured as an input, this pin can be programmed as an input.                                                                                              |

| HS2(IIC)         | 76                       | I/O | Programmable horizontal timing signal. One pulse every video line. At power up, this pin needs a 10 k $\Omega$ pull-down resistor to configure the chip to operate in IIC mode.                                                                      |

| VS               | 23                       | I/O | Programmable vertical timing signal. When the EXV port is configured as an input, this pin can be programmed as an input.                                                                                                                            |

| HAV              | 25                       | 0   | Programmable horizontal active video flag.                                                                                                                                                                                                           |

| VAV(OENC0)       | 3                        | I/O | Programmable vertical active video flag. During reset, the pin is an input and the logic state of this pin is latched into the <b>OENC</b> [0] register bit. Use a 10 k $\Omega$ resistor for pull-up or pull-down.                                  |

| EHAV             | 5                        | 0   | Valid pixel data flag. Polarity is programmable. Active when output video data is valid.                                                                                                                                                             |

# **PIN DESCRIPTION (Continued)**

| Pin Name    | Pin # | Туре | Description                                                                                                                                                                                                                                                      |

|-------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVAV(OENC1) | 4     | I/O  | Valid line flag. Polarity is programmable. Active when output video line is valid. During reset, the pin is an input and the logic state of this pin is latched into the $\textbf{OENC}[1]$ register bit. Use a 10 k $\Omega$ resistor for pull-up or pull-down. |

| ODD         | 22    | 0    | Odd field flag. Polarity is programmable. Active for fields 1 and 3.                                                                                                                                                                                             |

| PID         | 17    | 0    | PAL ID flag. High for phase alternating line.                                                                                                                                                                                                                    |

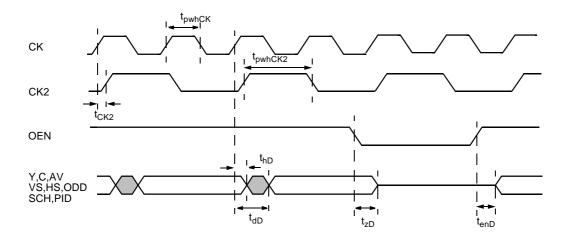

| OEN         | 15    | I    | Digital video data, timing and clock output 3-state control.                                                                                                                                                                                                     |

| СК          | 18    | I/O  | Pixel clock. In normal decoding mode, this is an output. When the EXV port is used as an input, this can be programmed as an input pixel clock.                                                                                                                  |

| CK2         | 21    | 0    | Pixel output clock (rate is one half of CK) aligned to HAV signal.                                                                                                                                                                                               |

| CCDAT       | 73    | 0    | Sliced VBI data output. Data can be from Closed Caption, Teletext, Intercast, or WSS type encoded data.                                                                                                                                                          |

| CCEN        | 74    | 0    | When high, this pin indicates that valid VBI data is being clocked out at the CCDAT pin or at the digital video output.                                                                                                                                          |

# MULTI-PURPOSE I/O PORTS AND TEST ENABLE

| PORTA      | 58 | I/O | Multi-purpose I/O port.                                                                                    |

|------------|----|-----|------------------------------------------------------------------------------------------------------------|

| SCH(PORTB) | 24 | I/O | Multi-purpose I/O port.                                                                                    |

| TESTEN     | 57 | I   | When tied to VDD, the chip is put into the test mode. For normal use, this pin should be connected to VSS. |

| TEST       | 96 | I   | When tied to VDD, the chip is put into the test mode. For normal use, this pin should be connected to VSS. |

# REFERENCE AND COMPENSATION

| VRT   | 77 | I/O | ADC VRT compensation (requires an external 0.1 $\mu\text{F}$ capacitor connected to VSS). |

|-------|----|-----|-------------------------------------------------------------------------------------------|

| VRB   | 78 | I/O | ADC VRB compensation (requires an external 0.1 μF capacitor connected to VSS).            |

| COMP2 | 97 | I/O | Internal 1.3 V reference (requires an external 0.1 µF capacitor connected to VSS).        |

# **HOST INTERFACE**

| SCLK        | 75      | I   | Serial clock for IIC host interface.        |  |  |  |

|-------------|---------|-----|---------------------------------------------|--|--|--|

| SDAT        | 72      | I/O | Serial data for IIC host interface.         |  |  |  |

| AEX0 - AEX1 | 69 - 70 | I   | Device ID selection for IIC host interface. |  |  |  |

# **PIN DESCRIPTION (Continued)**

| Pin Name    | Pin #                                         | Туре  | Description                                                                                                                               |

|-------------|-----------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| POWER AND O | ROUND                                         | •     |                                                                                                                                           |

| VDD         | 20,59                                         | PWR   | Digital power supply for output buffers. The voltage can be +5V or 3.3V depending on interface requirement.                               |

| VDD3        | 11,12,42,43,66,<br>67                         | +3.3V | Digital power supply for internal logic.                                                                                                  |

| VDDA        | 85,89,93,98                                   | +5V   | Analog power supply for ADC, AGC and reference circuits.                                                                                  |

| VDDA1       | 9                                             | +5V   | Analog power supply for clock generation circuitry.                                                                                       |

| VSS         | 6,13,14,19,40,<br>41,60,64,65,83,<br>87,91,95 | GND   | Common ground.                                                                                                                            |

| NC          |                                               |       |                                                                                                                                           |

| NCP         | 1,2,29-32,49-52,<br>79-82,99,100              | -     | These pins are directly connected to the die substrate. If electrical connect is desired (not required) only connection to VSS is allowed |

# PIN CROSS REFERENCE: NUMERICAL ORDER BY PIN NUMBER

| Pin# | Pin Name    | Pin# | Pin Name | Pin# | Pin Name | Pin# | Pin Name |

|------|-------------|------|----------|------|----------|------|----------|

| 1    | NCP         | 26   | HS1      | 51   | NCP      | 76   | HS2(IIC) |

| 2    | NCP         | 27   | EXV1     | 52   | NCP      | 77   | VRT      |

| 3    | VAV(OENC0)  | 28   | EXV2     | 53   | Y4       | 78   | VRB      |

| 4    | EVAV(OENC1) | 29   | NCP      | 54   | Y5       | 79   | NCP      |

| 5    | EHAV        | 30   | NCP      | 55   | Y6       | 80   | NCP      |

| 6    | VSS         | 31   | NCP      | 56   | Y7       | 81   | NCP      |

| 7    | XTALO       | 32   | NCP      | 57   | TESTEN   | 82   | NCP      |

| 8    | XTALI       | 33   | C0       | 58   | PORTA    | 83   | VSS      |

| 9    | VDDA1       | 34   | C1       | 59   | VDD      | 84   | AY0      |

| 10   | RST         | 35   | C2       | 60   | VSS      | 85   | VDDA     |

| 11   | VDD3        | 36   | C3       | 61   | EXV3     | 86   | AY1      |

| 12   | VDD3        | 37   | C4       | 62   | EXV4     | 87   | VSS      |

| 13   | VSS         | 38   | C5       | 63   | EXV5     | 88   | AY2      |

| 14   | VSS         | 39   | C6       | 64   | VSS      | 89   | VDDA     |

| 15   | OEN         | 40   | VSS      | 65   | VSS      | 90   | AC0      |

| 16   | EXV0        | 41   | VSS      | 66   | VDD3     | 91   | VSS      |

| 17   | PID         | 42   | VDD3     | 67   | VDD3     | 92   | AC1      |

| 18   | СК          | 43   | VDD3     | 68   | EXV6     | 93   | VDDA     |

| 19   | VSS         | 44   | C7       | 69   | AEX0     | 94   | AC2      |

| 20   | VDD         | 45   | Y0       | 70   | AEX1     | 95   | VSS      |

| 21   | CK2         | 46   | Y1       | 71   | EXV7     | 96   | TEST     |

| 22   | ODD         | 47   | Y2       | 72   | SDAT     | 97   | COMP2    |

| 23   | VS          | 48   | Y3       | 73   | CCDAT    | 98   | VDDA     |

| 24   | SCH(PORTB)  | 49   | NCP      | 74   | CCEN     | 99   | NCP      |

| 25   | HAV         | 50   | NCP      | 75   | SCLK     | 100  | NCP      |

#### 1. FUNCTIONAL DESCRIPTION

#### 1.1. VIDEO INPUT

The KS0127B supports complete video decoding of many analog video standards. In addition, the chip can support direct 8-bit YCbCr input for high quality video scaling and other processing.

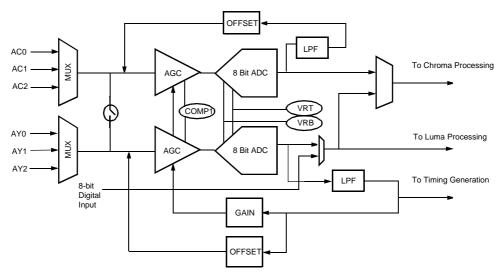

# 1.1.1. Analog Video Input

Figure 1 shows the detailed block diagram of the analog front end. Up to six composite video sources, three S-video sources, one 3-wire YCbCr component video source, or any combination can be selected. The allowed inputs are selected using the <code>INSEL[3:0]</code> bits in the <code>CMDB</code> register. Table 1 lists all possible input selections. The front end has two paths each containing an analog gain control, a clamping control, and an 8-bit ADC. Composite video input uses only the luma path. S-video and analog component YCbCr inputs utilize both the luma and chroma paths. The ADC digital data is used to calculate the correct gain and clamp values. The data is feedback to the analog clamping and gain control. This architecture eliminates any offset and gain mismatch in the analog front end.

Figure 1. Analog Front End

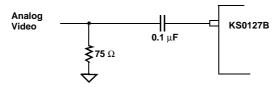

The analog inputs must be AC coupled through an external 0.1  $\mu$ F capacitor clamp. Due to the high sampling rate of the ADCs inside the KS0127B, most video sources will not require a low-pass filter for alias reduction. For those video sources with harmonics above 13 MHz, a simple single order pole at 6 MHz will provide sufficient high frequency signal reduction. This can be implemented with a 400 pF capacitor in parallel with the 75  $\Omega$  load.

Figure 2. Typical Analog Video Input

Video Type INSEL[3:0](hex) Selected Input(s) AY0 0 Composite AY1 1 Composite 2 AY2 Composite 4 AC<sub>0</sub> Composite 5 AC1 Composite 6 AC2 Composite 8 AY0, AC0 S-Video 9 AY1, AC1 S-Video Α AY2, AC2 S-Video F AY2(Y), AC1(Cb), AC2(Cr) YCbCr component video

Table 1: Analog Video Input selections

#### 1.1.2. Digital AGC Control

The AGC normally references to the ADC code difference between sync tip and back porch. Two sets of sync tip-back porch ADC values are available for different AGC gain requirements: if **AGCGN** = 0, the sync tip locks to code 2, and the back porch locks to code 70; when **AGCGN** = 1, the sync tip locks to 16, and the back porch locks to code 70. Video signal with abnormal sync tip or very bright saturated colors may cause the ADC to limit the maximum value. This situation can be corrected by enabling the **AGCOVF** bit in the **CMDB** register to force the gain tracking loop to reduce AGC when maximum limiting conditions occur. The AGC may also be programmed to freeze the AGC at the current value by setting the **AGCFRZ** bit in the **CMDB** register. Once the AGC is frozen, the gain can be manually adjusted with the **AGC** register. The tracking time constant for the AGC can be controlled with the **AGC\_LPG[1:0]** bits in the **TRACKB** register. In addition, the AGC tracking time constant can be configured as 2X faster during acquisition via the **AGC\_LKG**.

# 1.1.3. Digital Video Input

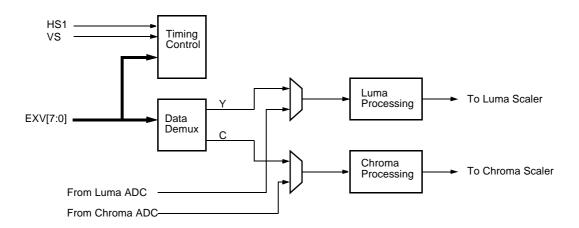

The high quality digital video down scaler in the KS0127B can be directly accessed via the EXV bi-directional port. The KS0127B accepts CCIR 656 compliant 8-bit YCbCr digital video input with embedded or external timing. Video timing may also be generated by the KS0127B. Data path for 8-bit YCbCr input is shown in Figure 3. Selection of analog video input or digital CCIR 656 data is with the INPSL[1:0] register bits. The KS0127B can operate in master or slave timing mode when the chip is programmed for digital video input.

# 1.1.4. Pixel Clock and Timing Mode Selection for Digital Video Input

Pixel clock and synchronization timing can be individually selected to either come from an external generator or be generated internally. In addition, if synchronization is provided by an external source, the KS0127B supports embedded syncs as defined in CCIR 656, or TTL HS and VS inputs. Selection of pixel clock is via **CKDIR** bit in

CMDD register. Timing selection is through either SYNDIR or EAV bit.

Figure 3. 8-bit YCbCr Input Data Path

By using an external pixel clock, the reference clock input at XTALI is no longer required. Additional register bits have to be programmed for different selections of pixel clock and timing, which are detailed in Table 2. The following register/bit-settings are required for digital video input:

INSEL[3:0] = 8, 9, A, or F.

TSTCGN = 1.

**DMCTL**[1:0] = 2 or 3.

UGAIN = 238.

BRT = 34.

SAT = 229.

RGBH = UNIT = PED = 1.

Table 2: Digital Video Input Pixel Clock and Timing Selection

| Pixel Clock | TTL Timing | Embedded<br>Timing | Additional Register Programming |        |        |        |                   |       |                     |

|-------------|------------|--------------------|---------------------------------|--------|--------|--------|-------------------|-------|---------------------|

| CKDIR*1     | SYNDIR*2   | EAV*3              | VMEN                            | TSTGPH | TSTGEN | TSTGFR | PIXSEL            | MNFMT | IFMT                |

| 0           | 0          | 0                  | 1                               | 0      | 1      | 3      | 0 if input        | 1     | 0 if input          |

| 0           | 0          | 1                  | 0                               | 1      | 1      | 3      | data is at square | 1     | is 50 Hz<br>video.  |

| 0           | 1          | 0                  | 0                               | 1      | 1      | 1      | pixel<br>rate.    | 1     | 1 if input is 60 Hz |

| 1           | 0          | 0                  | 1                               | 0      | 1      | 3      | 1 if input        | 1     | video.              |

| 1           | 0          | 1                  | 0                               | 1      | 1      | 1      | is at<br>CCIR     | 1     |                     |

| 1           | 1          | 0                  | 0                               | 1      | 1      | 1      | 601 rate.         | 1     | ļ                   |

<sup>\*1:</sup> **CKDIR** = 0 - CK is output and is internally generated. **CKDIR** = 1 - CK is input from an external source.

<sup>\*3:</sup> **EAV** = 0 - chip will not sync to embedded timing. **EAV** = 1 - chip will sync to embedded timing. Note: the combination X11 for **CKDIR**, **SYNDIR**, **EAV** is not valid.

<sup>\*2:</sup> **SYNDIR** = 0 - HS1 and VS are output. **SYNDIR** = 1 - HS1 and VS are inputs from external sources.

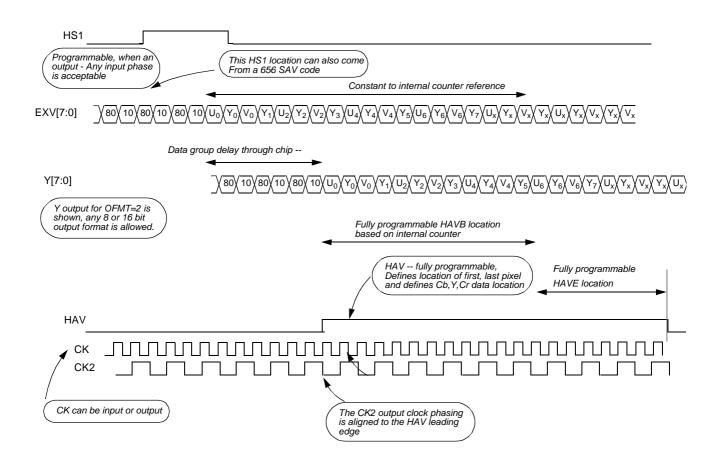

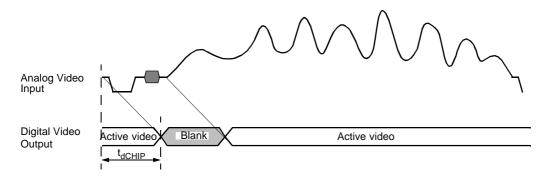

When in digital input mode, all programmable timing registers (such as HAVB,HAVE, HS2B etc.) are still functional. If HS1 and VS are programmed as inputs, the associated output timing controls such as HS1B,E will have no effect. An example of horizontal timing for digital input is shown in Figure 4.

Figure 4. Horizontal Timing for EXV Port as Digital Input

# 1.1.5. Additional Information for Analog Component Video Input

For the KS0127B to correctly set the V component phase in analog component video input mode, PID (pin 17) and PORTA (pin 58) need to be connected together. PORTA has to be configured as input (**DIRA** = 0) and connected to the internal CBG signal (**DATAA**[2:0] = 3).

It is also recommended that external clamp circuit be used for Cb and Cr inputs (before the coupling caps) and the internal chroma clamp be disabled (**COFFENB** = 1) due to slight Cb/Cr leakage.

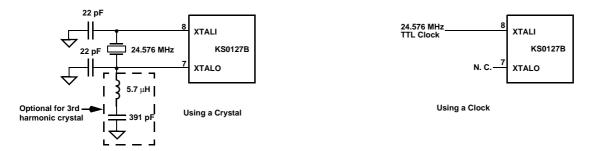

#### 1.2. VIDEO TRACKING AND TIMING GENERATION

When the KS0127B is configured for analog video input, the chip tracks the video input and generates a sampling clock that is line locked to the input video. The KS0127B requires an external reference clock for video tracking. This reference can be supplied via a crystal using the on chip crystal interface or any TTL compatible source. These configurations are shown in Figure 5

# 1.2.1. Clock Input Timing Reference

The KS0127B can use either a 24.576 MHz or a 26.8 MHz reference. However, it is recommended that the 24.576 MHz reference be used for CCIR 601 operation, and the 26.8 MHz reference be used for square pixel or dual mode operation. Other specifications for the crystal are:

- · Fundamental or third overtone

- Load capacitance of ~20 pF

- Series resistance of 40  $\Omega$  or less

- Frequency deviation of 50 ppm or less over operating temperature range

Figure 5. Standard Clock Configurations

# 1.2.2. The Sampling Clock

The sampling clock is generated by multiplying the line rate by N. This ensures that samples are aligned horizontally, vertically and in time. The required N factor for the KS0127B is based upon the field rate (60 Hz or 50 Hz) and the desired sampling rates (CCIR 601 or square pixel). Field rate can be automatically detected and can be monitored with the **FFRDET** bit in the **STAT** register. Manual control of the field rate can be controlled with the **MNFMT** and **IFMT** bits. The **PIXSEL** bit in register **CMDA** selects CCIR 601 or square pixel. Table 3 shows the constants for the various combinations of input formats and output pixel rates.

**Table 3: Timing for Different Pixel Rates**

|                    | CCIR 601 | Data Rates         | Square Pixe |                    |        |

|--------------------|----------|--------------------|-------------|--------------------|--------|

|                    | М        | N,B,G,H,I,D,K,K1,L | M           | N,B,G,H,I,D,K,K1,L | Units  |

| Field Rate         | 60       | 50                 | 60          | 50                 | Hz     |

| Pixels/Line (N)    | 858      | 864                | 780         | 944                | Pixels |

| Active Pixels/Line | 720      | 720                | 640         | 768                | Pixels |

| Active Lines/Frame | 480      | 580                | 480         | 580                | Lines  |

| Pixel Rate         | 13.5     | 13.5               | 12.27       | 14.75              | MHz    |

| ADC Sampling Rate  | 27       | 27                 | 24.54       | 29.5               | MHz    |

The time constants for the pixel clock tracking loop can be adjusted with the HFSEL[1:0] bits.

In addition to providing the pixel clock, the KS0127B also outputs various timing signals to indicate the beginning of a line, a field, and for field and frame identification. All the timing and clock pins may be optionally put into high impedance state. Three-state of these pins are software controlled and initial state of these pins at power up is controlled via two configuration pins: 3 and 4.

The KS0127B can generate all the video timing without video input. This enables the KS0127B to be used as a video timing generator for a system that contains both the KS0127B for live video input and a MPEG decoder which requires a video timing generator.

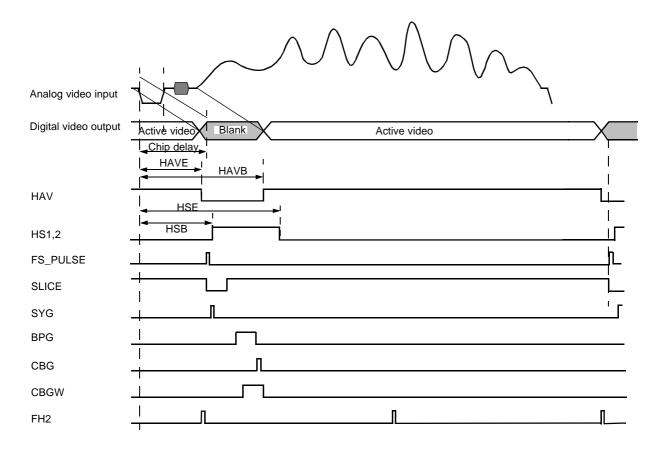

# 1.2.3. Horizontal Timing

The KS0127B creates many internal timing signals aligned to the horizontal sync tip (mid-way of the falling edge of horizontal sync, typically ADC code 36). These include locations of color burst (CBG, CBGW) used in chrominance processing, back porch (BPG), and sync tip timing signals (SLICE, FS\_PULSE) used for AGC and clamp functions. SLICE is low whenever the input is below half way level of horizontal sync (typically ADC code 36). FS\_PULSE is a single clock pulse coincide with the start of SLICE. One of these internal signals can be made available at the PORTA or PORTB pin at any time.

The chip outputs two horizontal synchronization signals: HS1 and HS2. The start and stop locations for these signals are fully programmable. Offset programmed to **HSxB**, **HSxE**, and **HSxBE0** are added to the default edge locations as shown in Table 4. Note that there are different modulo numbers for different input video standards and output pixel rates.

Table 4: Horizontal Timing Signal Edge Locations (in # of CK)

|                                       |        | 60                        | Hz                            | 50 Hz                     |                               |  |

|---------------------------------------|--------|---------------------------|-------------------------------|---------------------------|-------------------------------|--|

| Description                           | Signal | CCIR 601<br>(modulo 1716) | Square Pixel<br>(modulo 1560) | CCIR 601<br>(modulo 1728) | Square Pixel<br>(modulo 1888) |  |

| Chip delay                            |        | 120                       | 120                           | 120                       | 120                           |  |

| Sync gate (1-CK pulse)                | SYG    | 72                        | 72                            | 72                        | 72                            |  |

| Back porch gate                       | BPG    | [147 222]                 | [129 204]                     | [154 234]                 | [168 254]                     |  |

| Color burst gate (1-CK pulse)         | CBG    | 222                       | 204                           | 234                       | 254                           |  |

| Wide color burst gate                 | CBGW   | [159 254]                 | [147 233]                     | [173 254]                 | [186 277]                     |  |

| Two pulses per line (1-CK each pulse) | FH2    | 42, 900                   | 42, 822                       | 42, 906                   | 42, 986                       |  |

| Default one pulse per line            | HS1    | [65 238]                  | [45 220]                      | [69 250]                  | [65 270]                      |  |

| Default one pulse per line            | HS2    | [65 238]                  | [45 220]                      | [69 250]                  | [65 270]                      |  |

| Default horizontal cropping           | HAV    | [351 75]                  | [334 58]                      | [379 91]                  | [415 59]                      |  |

An additional signal, HAV, is provided for horizontal video cropping. This signal has programmable polarity, start and stop locations. Two 11-bit registers, **HAVB** and **HAVE**, are used to define the first and last pixel locations of the horizontal portion of the cropped video. Numbers programmed into these registers are used as offset to the default locations as shown in Table 4. Note that even though **HAVB** and **HAVE** have 1-CK resolution, the difference between them should be maintained at multiple of 4 CKs for correct output.

Table 4 shows the default edge locations relative to the midway of the falling edge of the analog horizontal sync. Note the numbers shown are in multiple of CK clocks. Figure 6 shows the approximate locations for the horizontal timing signals. Horizontal timing signals used for scaling will be described in Section 1.6.1.

Figure 6. Approximate Locations for the Horizontal Timing Signals

# 1.2.4. Vertical Timing

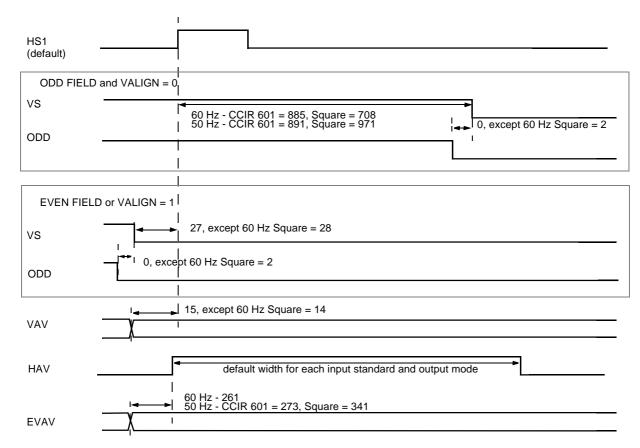

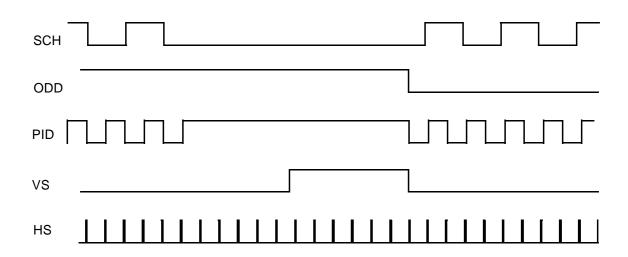

The vertical timing signals include VS, VAV, ODD, SCH, and PID.

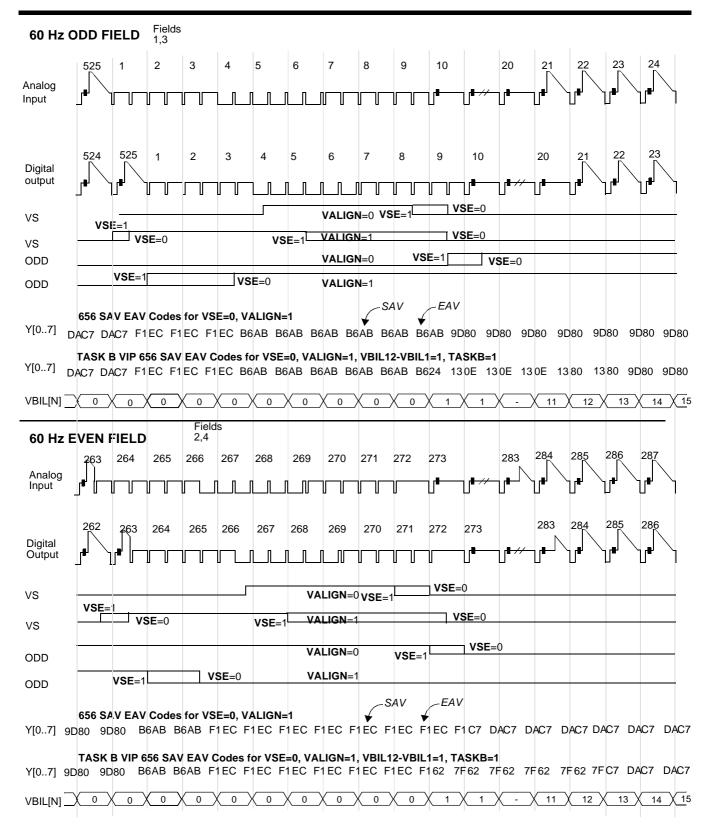

The VS is used for identifying the first line of video in the vertical position. The VS leading edge can be programmed to either track the incoming video's serration pulses or to be aligned to the beginning of the video line or half way, as shown in Figure 36 and Figure 37. If **VALIGN** = 0, the VS leading edge is based on the output of an internal low pass filter, and its location is dependent on the noise conditions of the video input. The trailing edge of VS is locked to either the beginning of the video line or half way. The half way location relative to the beginning of the video line changes depending on current input standard and output format. If **VALIGN** = 1, the leading edge of the VS is aligned to the beginning of the video line or half way. The trailing edge is always aligned to the beginning of the video line. The **VSE** bit in the **CMDA** register can be programmed to shorten the VS falling edge by one horizontal line.

The VAV signal is used for vertical cropping. The start and stop lines for VAV are programmable through the **VAVB** and **VAVE** registers, respectively.

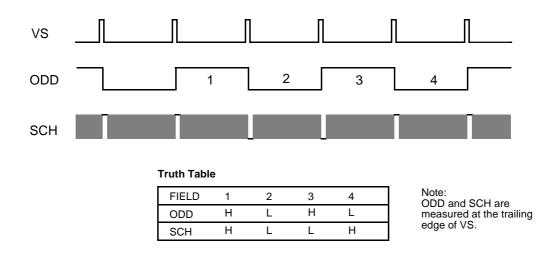

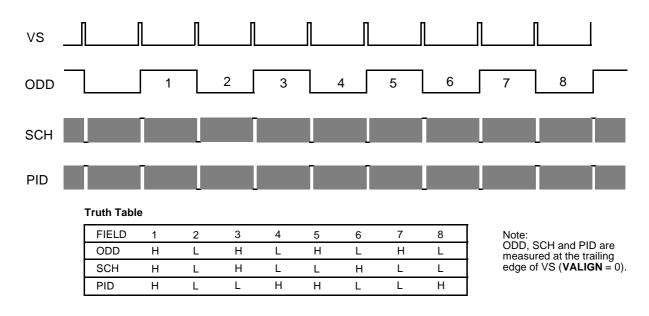

The ODD signal signifies the current field number. When ODD is active, the current field is 1 or 3 (or 5 or 7 if in PAL mode). The leading and trailing edges of ODD can be aligned to either the leading edge of VS (**VALIGN** = 1) or the trailing edge of VS (**VALIGN** = 0). The signal may be used in conjunction with SCH and PID to exactly identify the

current field. To distinguish between fields 1, 2 verse fields 3, 4 (or fields 1, 2, 3, 4 verse fields 5, 6, 7, 8 for PAL) the phase of the color burst relative to the sync tip must be measured. That information is provided by the SCH pin. The KS0127B provides the output of a comparator that measures whether the current color burst phase relative to the falling edge of the sync is greater or less than a predetermined constant. This constant is controlled with **SCHCMP[3:0]**. The polarity of the SCH output pin depends on the current **SCHCMP[3:0]** value. The SCH signal changes every video line. The SCH for line 260 is held for the entire vertical blanking period. By using the SCH signal for the same line from each field, proper field identification can be determined. Figure 8 shows field identification values for **SCHCMP[3:0]**=0. It is important to note that the SCH value is only valid for video signals that have a constant sync tip to color burst relationship. This is not the case with consumer VCRs.

Note: Numbers shown are in CK. Active high polarities are used. Timing shown for VAV and EVAV are with qualifier off.

Figure 7. Short Term Vertical Timing

Figure 8. NTSC Vertical Timing Signals

The PID pin is used to identify whether the current V-axis is inverted in PAL mode. This signal changes at the color burst. By noting this value at the same line of each field, a determination of whether a field is from {1-4} or {5-8} can be made. As with the SCH pin, the KS0127B is designed to hold the line 260 PID measurement for the entire vertical blank period. This allows easy sampling of the PID or current field identification.

The ODD, SCH and PID signals change at different times and more than once within the video fields. Proper data for field identification is determined by latching all three signals at the trailing edge of VS. Figure 9 shows the VS, ODD, SCH, and PID signals and their latched values for each of the 8 possible fields. Figure 10 is the line to line timing diagram for these signals in PAL mode.

Figure 9. PAL Vertical Timing Signals

Figure 10. Line to Line VS, SCH and PID Timing (PAL input)

#### 1.3. HORIZONTAL LUMA PROCESSING

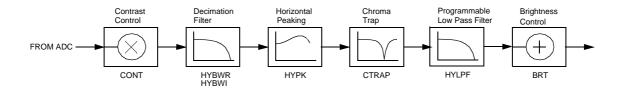

A simplified block diagram for the luma path is shown in Figure 11.

Figure 11. Horizontal Luma Processing Unit

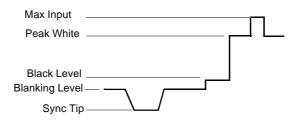

# 1.3.1. Luminance DC Gain

The KS0127B can accommodate CCIR 624 M/N/H/G standards, which fall into categories of -40 or -43 sync tip and inclusion or exclusion of 7.5 setup. The KS0127B can produce correct CCIR 601 luminance output levels by controlling the gain and offset in the luminance path via **PED**. This register should be set for the appropriate input standard. The programmable **CONT** and **BRT** registers provide the user with additional flexibility to create non-standard luminance gain and offset values.

Figure 12. Luminance Signal

Luminance levels produced by the KS0127B for different broadcast standards (assuming AGCGN=0, CONT=0 and BRT=0) are summarized in Table 5.

M/N PED=1 M/N PED=0 B/G/H PED=1 **ADC ADC ADC** Level Level Level Signal Y[7:0] Y[7:0] Y[7:0] (CVBS) (CVBS) (IRE) (IRE) (IRE) (CVBS) Max Input 109 255 255 109 255 117 255 255 255 Peak White 100 240 235 100 240 235 229 235 100 Black 7.5 83 16 0 70 16 0 70 16 Blank 0 70 1 0 70 16 0 70 Sync -40 2 1 -40 2 1 -43 2 KS0127B Data  $C_Y = 1.37 CVBS - 100$  $C_v = 1.288CVBS-74$  $C_V = 1.37CVBS-80$ Path Equation

**Table 5: Luminance Digital Level Code**

When digital component output is desired in RGB mode, the **RGBH** register can be programmed to increase the 0-100% values from standard CCIR 601 levels to full range levels. The gain variations are shown in Table 6.

Table 6: RGB Output Range

|            | RGB normal gain (RGBH=0) |             | RGB high gain (RGBH=1) |             |  |

|------------|--------------------------|-------------|------------------------|-------------|--|

| Signal     | Су                       | RGB (U,V=0) | Су                     | RGB (U,V=0) |  |

| Peak White | 235                      | 235         | 255                    | 255         |  |

| Black      | 16                       | 16          | 0                      | 0           |  |

For CCIR 601 digital video input (INPSL[1:0] = 1), register UNIT must be set to 1 to produce unit gain.

# 1.3.2. Horizontal Luma Frequency Shaping

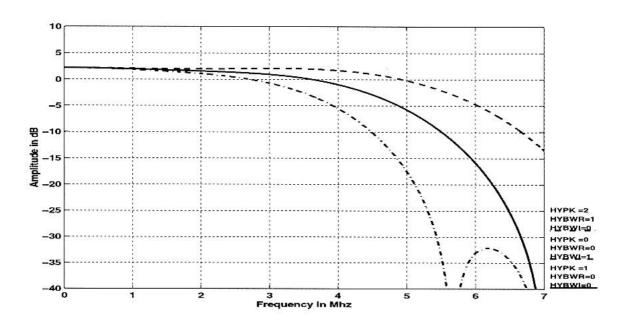

The luma path contains many programmable filters for different purposes. The combination of these filters will give different frequency characteristics.

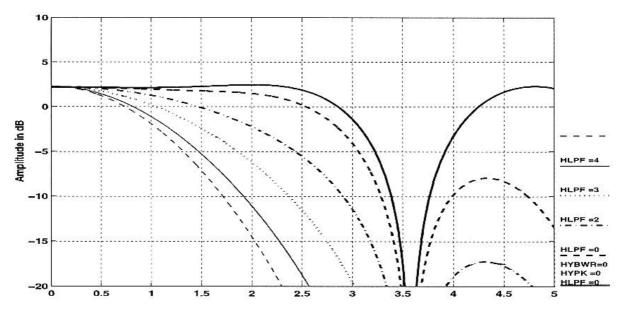

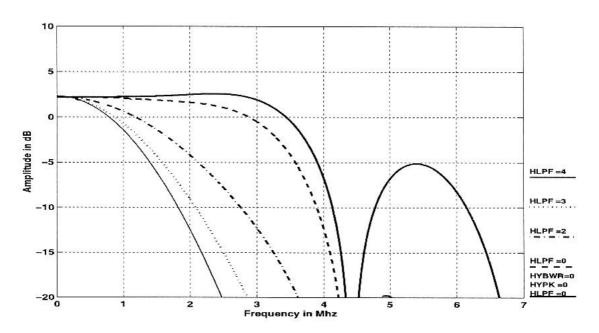

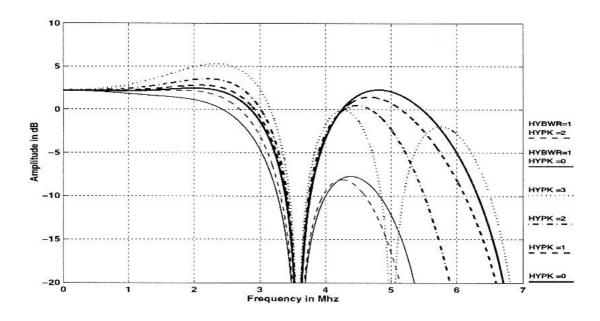

The over sampled video data from the ADC pass through a decimation filter. The decimation filter has user programmable bandwidth. Three registers are used to control the decimation filter characteristics and each is designed for certain purposes. The **HYBWI**, when set to "1", provides extra bandwidth for very high quality video source. The **HYBWR**, when set to "1", reduces the bandwidth so high frequency noise can be eliminated. The 3-bit register **HYLPF[2:0]** provides the necessary bandwidth reduction for horizontal scaling. When all three registers are programmed to '0", the decimation filter has the bandwidth of the normal video. The KS0127B provides the option of bypassing the decimation filter. This option should be used only when the input video is band limited and with low high frequency noise.

For composite video input, the notch filter can be enabled (CTRAP set to "1") to extract the luminance. The notch filter has different center frequencies for different input video format. User selectable peaking function is included for edge enhancement. The notch filter should be bypassed for S-video and component video input, or if luma comb filter is enabled.

The luminance filter characteristics have been designed to be very similar for all combinations of 60/50 Hz video and CCIR 601/square pixel sampling rates. Figure 13 and Figure 14 show the output characteristics of the luminance path with different filter combinations for the supported input standards and output pixel rates.

Figure 13. Medium to High Frequency Luma Filter Characteristics (CTRAP=0)

Figure 14. Medium to Low Frequency Luma Filter Characteristics (NTSC, CTRAP=1)

Figure 15. Medium to Low Frequency Luma Filter Characteristic (PAL, CTRAP=1)

Figure 16. Luma Filter Characteristic with Peaking On (NTSC, CTRAP=1)

#### 1.4. HORIZONTAL CHROMA PROCESSING

A simplified block diagram for the horizontal chroma processing unit is shown in Figure 17.

Figure 17. Horizontal Chroma Processing Unit

The KS0127B supports chroma input in NTSC, PAL, SECAM and component formats. The color standard is automatically detected and the various chroma processing blocks are enabled as required for the given chroma standard. Details of the various chroma processing blocks follow.

# 1.4.1. IF Compensation

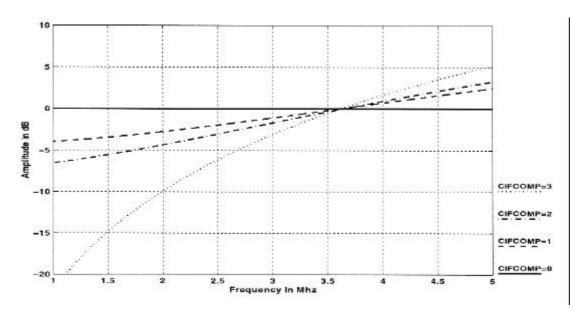

For improved chroma demodulation when the input video is from a mis-tuned IF source, an IF compensation filter is included that has variable gain for the upper chroma side band. This is controlled by the **CIFCMP**[1:0] bits at location **CDEM**. The frequency response is shown in Figure 18. For convenience, all plots are normalized to the NTSC modulation frequency.

Figure 18. Chroma IF Compensation Frequency Response

#### 1.4.2. Demodulation Gain

The demodulation gain block is controlled by feedback from the gain tracking block. For NTSC and PAL type inputs, the gain constant is derived from a programmable reference compared against the U component of the input video. This reference is controlled by the **SAT** register. The default value '0" is the correct gain (saturation for nominal output). For SECAM type input, the feedback is calculated such that proper frequency demodulation is obtained. When external calibration is desired, the gain feed back loop can be 'opened" by setting **TSTCGN**=1. The **SAT** then controls bits 8 through 1 of a 10 bit multiplier.

For standard auto tracking applications, it is recommended that the **SAT** register be used as an end user saturation control. This register is 2's compliment.

# 1.4.3. Demodulation Low Pass Filter

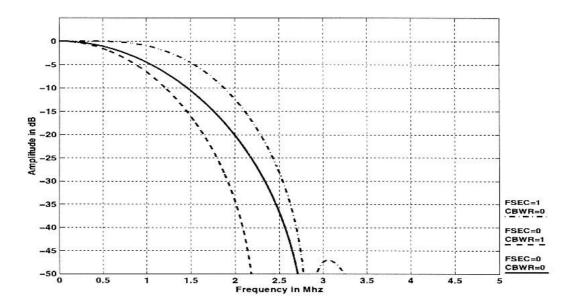

The demodulation circuit also contains a programmable low pass filter and a coring function for noise reduction. The chroma low pass filter frequency response for the demodulation circuit for the various video standards are shown in Figure 19

Figure 19. Chroma Low Pass Filter Frequency Response

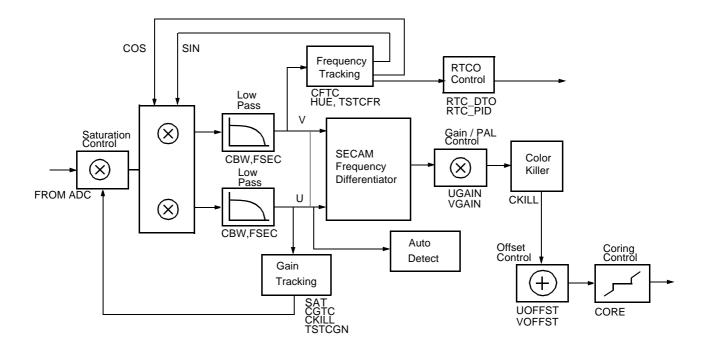

# 1.4.4. SECAM Demodulation

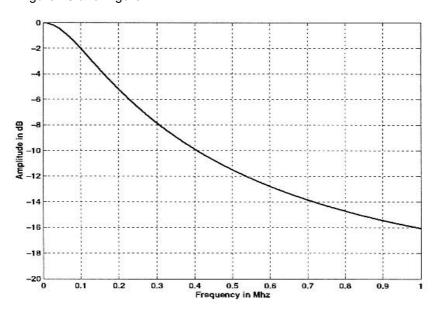

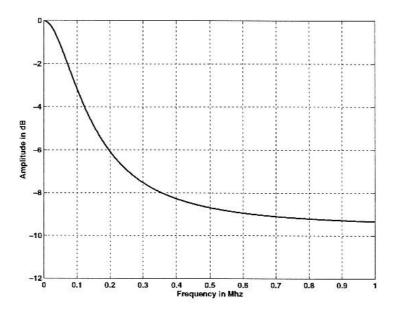

SECAM processing includes a frequency differentiator, a Cloche and a de-emphasis filter. Frequency response for the filters are shown in Figure 20 and Figure 21.

Figure 20. Cloche Filter Frequency Characteristic

Figure 21. De-emphasis Filter Frequency Response

#### 1.4.5. Additional Chroma Functions

KS0127B has many built in auto detection circuits. These allow KS0127B to track any type of video standard input automatically.

For analog component video input, the demodulation function is not enabled. The low pass filter provides a group delay for Cb and Cr alignment. This enables the two components to be sampled by one ADC.

An RTCO serial output is provided that encodes the current chroma and pixel frequency of the decoder. This information can be used by an Encoder running off of the decoder clock to produce proper color output. The horizontal position of the serial signal is controlled by the **HS2** location. The phasing of the DTO and the Encoder can be reset using the **RTC DTO** bit. For PAL mode, the PID polarity can be controlled with the **RTC PID** bit.

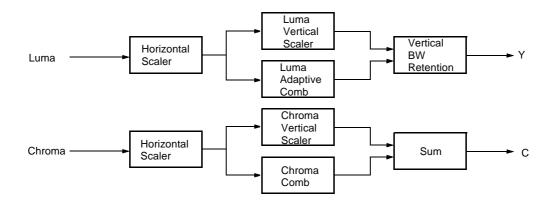

# 1.5. COMB FILTER

Comb filters provide superior Y/C separation for composite NTSC and PAL than simple chroma trap filter. The KS0127B contains on-chip separate 2-line stored luma and chroma comb filters. An internal signal COMB controls for what lines the comb function is enabled. This signal is available through the PORTB pin. Combing is part of the vertical processing which also includes vertical scaling, which is discussed in Section 1.6. A block diagram for the vertical processing section is shown in Figure 22.

Figure 22. Vertical Processing

#### 1.5.1. Luma Comb Filter

The luma comb filter reduces high frequency chroma leakage into the luminance path. The KS0127B uses 2-line stored luma data for combing. Filter coefficients for different video input standards are provided and can be selected automatically based on the video input. Filter coefficients may also be set manually.

An optional active comb is employed for NTSC video. Selection of luma comb coefficients is based on line-to-line chroma correlation.

Provision is made to disable luma comb for S-video, component, or digital video input. This is achieved by programming the luma comb control register **MNYCMB** to "1", and by choosing the value 3 or 4 for **YCMBCO[2:0]**. This will result either a 1-line or 2-line luma delay. Care must be exercised when disabling the luma comb so that luma line delay matches the chroma path line delay.

Special filtering is applied to ensure that high vertical bandwidth is retained for the luma path.

# 1.5.2. Chroma Comb Filter

The chroma comb filter provides further color separation from the composite video. Filter coefficients can be automatically selected based on the input video standard or manually set using **NMCCMB** and **CCMBCO[2:0]**.

#### 1.6. SCALING

The KS0127B includes a high quality down scaler. The video images can be down scaled in both horizontal and vertical direction to an arbitrary size.

#### 1.6.1. Horizontal Scaler

The horizontal scaler uses a 5-tap 32-phase interpolation filter for luma, and a 3-tap 8-phase interpolation filter for chroma. Scaled pixel data are stored in an on-chip FIFO so they can be sent out in a continuous stream.

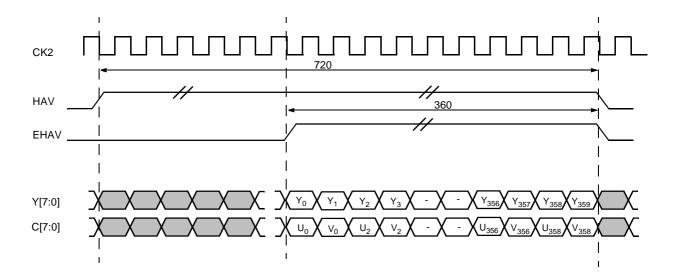

Horizontal scaling ratio is programmed via the 15-bit register **HSCL**. The timing signal EHAV is used to indicate when scaled pixel data is available at the video output port. EHAV can be programmed so that it is active for every line regardless of vertical cropping and scaling. Or it can be programmed to be active only for valid video lines. For example, Figure 23 shows the timing for CIF output assuming HAV is programmed to be active for 720 pixels. The **HSCL** register is programmed with the value 4000 (hex). The trailing edge of EHAV is either aligned with the trailing edge of HAV if the total number of scaled pixels is even, or is one pixel clock earlier if the number is odd.

Figure 23. Horizontal Scaler Timing for CIF Output (CCIR 601 Pixel Rate)

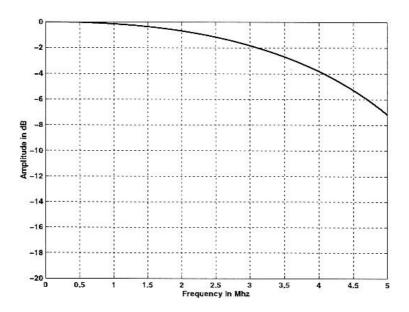

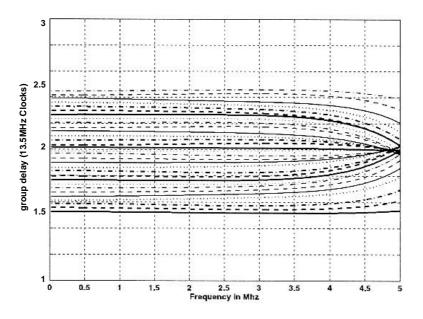

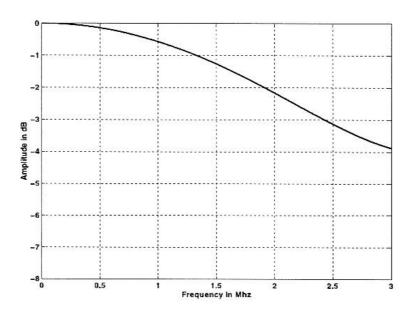

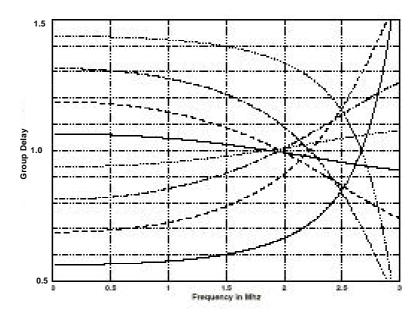

Frequency response and group delay for the luma scaler are shown in Figure 24 and Figure 25, respectively. The luma interpolation filter is designed to achieve relatively flat frequency response and minimal group delay up to the normal video bandwidth. A flat full data path frequency response may be obtained with the help of the luma peaking control register **HYPK[1:0]**. The high quality filter ensures minimal artifacts for any scaling ratio.

Figure 24. Horizontal Luma Scaler Interpolation Filter Frequency Response

Figure 25. Horizontal Luma Scaler Interpolation Filter Group Delay

Because of the limited bandwidth of the chroma data, a simpler interpolation filter is used for the horizontal chroma scaler. The frequency response and group delay for this filter are shown in Figure 26 and Figure 27, respectively.

Figure 26. Horizontal Chroma Scaler Interpolation Filter Frequency Response

Figure 27. Horizontal Chroma Scaler Interpolation Filter Group Delay

# 1.6.2. Luma Vertical Scaler

Vertical luma scaling uses either a 3-tap or 5-tap 8-phase interpolation filter depending on the horizontal scaling

ratio.

Vertical scaling ratio is programmed via the 14-bit register **VSCL**. A valid scaled line is indicated by the timing signal EVAV being active. The EVAV can be programmed to be internally gated by the VAV signal so it can only be valid within the vertically cropped region.

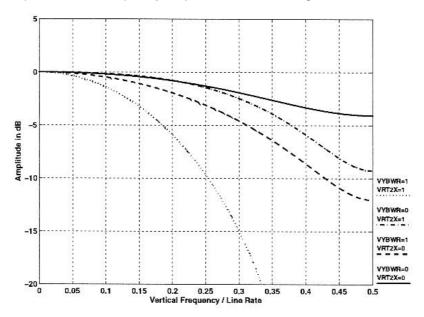

Luma horizontal scaling can use either a 3-tap or a 5-tap interpolation filter depending on the horizontal scaling ration. If the scaled horizontal line has less than or equal to 384 pixels, the 5-tap luma interpolation filter can be turned on by programming the VRT2X bit to a "1". Otherwise, the VRT2X bit should be set to "0" and the 3-tap filter be used.

The **VYBW** bit provides additional vertical bandwidth control for vertical scaling. Typically, when the vertical scaling ratio is less than 1/2, this bit should be set to "1" to eliminate any aliasing effect.

Luma vertical scaler interpolation filter frequency response is shown in Figure 28.

Figure 28. Luma Vertical Scaler Interpolation Filter Frequency Response

In vertical scaling, the start of signal VAV controls the phase of the vertical scaler interpolation filter. If **VAVB**, **VAVDO**, **VAVEVO**, and **VSCL** are programmed such that the vertical interpolation filter has the same phase and scaling ratio as that of a memory controller (most memory controller has simple line dropping vertical scaling), it is possible to interface the KS0127B to the memory controller without using EVAV.

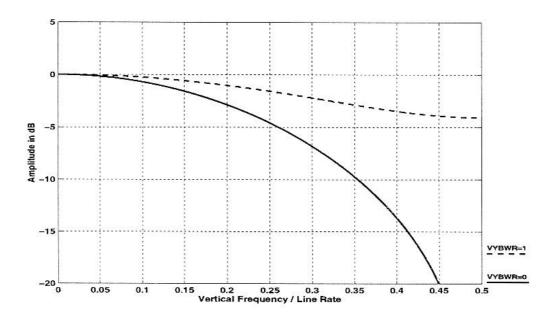

# 1.6.3. Chroma Vertical Scaling

Chroma vertical scaling uses different algorithms depending on video input standard and horizontal scaling ratio. If horizontal scaling results in line with less than or equal to 384 pixels, and the **VRT2X** is set to a "1", a 5-tap interpolation filter will be used for all video inputs. Otherwise, for NTSC, a 3-tap interpolation filter will be used for NTSC input, and decimation (line dropping without filtering) will be used for PAL and SECAM. Filter characteristics for the 3-tap and 5-tap filters are shown in Figure 29.

Figure 29. Chroma Vertical Scaler Interpolation Filter Frequency Response

#### 1.7. VBI DATA PROCESSING

The KS0127B VBI data processing is very flexible in that it supports VBI data formats of:

- Closed Caption Line 21 Data Service (EIA-608)

- 525 line / 60Hz Teletext systems B,C,D (ITU-R BT.653-2)

- 625 line / 50Hz Teletext systems A,B,C,D (ITU-R BT.653-2)

- Copy Generation Management System (EIA/IS-702)

- Wide Screen Signalling (WSS ETS 300 294).

Note that the SMPTE data slicing is removed for the KS0127B and replaced with the WSS / CGMS processing. This data can be accessed from the part via four different methods:

- Enabling the 'Raw un-processed 27MHz" Y ADC samples to be output for the appropriate lines in place of the normal YUV data.

- Slicing the data (creating a clock and comparing the data to a threshold at the clock) and bursting this data out on Y output.

- Reading the sliced data from two internal registers via the IIC bus.

- Via 2 external pins that output the sliced VBI data and the time at which the slice is valid.

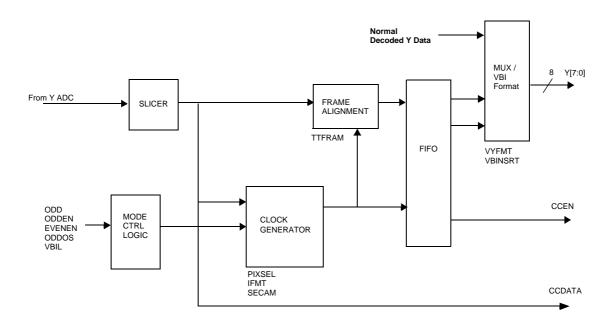

A simplified block diagram for the VBI section is shown in Figure 30.

Figure 30. VBI Decoder Block Diagram

Table 7 lists all the video standards that the VBI data slicer supports. Some of these modes are auto detected based on the current video input standard,

Table 7: Video Standards Supported by VBI Decoder

|                                           | Value of Chip<br>Detection Bits |       | Required Values of<br>Registers to enable<br>Standard |        | Characteristics of the<br>Standard |                           |

|-------------------------------------------|---------------------------------|-------|-------------------------------------------------------|--------|------------------------------------|---------------------------|

| Mode                                      | Format                          | SECAM | VBIL0-15                                              | TT_SYS | Data Rate<br>(MHz)                 | Number of<br>Bits (bytes) |

| 60Hz Teletext system C (NTSC / Intercast) | 1                               | 0     | 2                                                     | 0      | 5.727272                           | 272 (34)                  |

| 50Hz Teletext system B (PAL)              | 0                               | 0     | 2                                                     | 0      | 6.9375                             | 344 (43)                  |

| 50Hz Teletext system A (SECAM)            | 0                               | 1     | 2                                                     | 0      | 6.203125                           | 304 (38)                  |

| 60Hz Teletext system B                    | 0                               | 1     | 2                                                     | 1      | 5.727272                           | 280 (35)                  |

| 50Hz Teletext system C                    | 0                               | 1     | 2                                                     | 2      | 5.734375                           | 272 (34)                  |

| 50Hz Teletext system D                    | 0                               | 1     | 2                                                     | 3      | 5.6457875                          | 280 (35)                  |

| 60Hz Teletext system D                    | 0                               | 1     | 2                                                     | 3      | 5.727272                           | 280 (35)                  |

| Closed Caption NTSC 601                   | N/A                             | N/A   | 1                                                     | N/A    | 0.5035                             | 16 (2)                    |

| CGMS (NTSC 60Hz)                          | 1                               | N/A   | 3                                                     | N/A    | 0.447443                           | 20 (3)                    |

| WSS (PAL 50Hz)                            | 0                               | N/A   | 3                                                     | N/A    | 5.0000                             | 84                        |

Configuring the VBI processing consists of many different steps which are individually explained below.

# 1.7.1. Enabling the VBI Processor

The VBI processor can be enabled independently for the ODD or EVEN fields with the **ODDEN** and **EVENEN** bits. Some VBI data is only present on line in 1 of the 2 fields, These independent field enables allow control of the total VBI data output from the chip. These controls apply to all VBI Lines, Thus it is not possible to enable Closed caption line 21 for the Even field and line 19 Teletext for both the odd and even field.

# 1.7.2. Selecting the Type of Output Data

As previously mentioned, there are 4 different ways the VBI data can be extracted. Three of these are selected as shown in the table, the fourth method (CCEN and CCDAT pins) is always available if VBI processing is enabled.

Table 8: VBI Data Output Mode (VBILn != 0)

| VBCVBS | VBINSRT | Output Mode                                                                                                                                                                                                                 |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0       | The VBI data is available via the internal registers <b>CCDAT1</b> and <b>CCDAT2</b> . Only the last 2 extracted bytes are stored in these registers. Thus, this mode is only useful for extraction of Closed Caption data. |

| 0      | 1       | This mode enables output of the sliced VBI data.                                                                                                                                                                            |

| 1      | 0       | This mode enables output of direct data from the ADC.                                                                                                                                                                       |

| 1      | 1       | This mode is invalid.                                                                                                                                                                                                       |

The KS0127B adds an additional output mode and flexibility to vary the modes from line to line. If **VBCVBS**=0 and **VBINSRT**=1 KS0127B will output sliced data on enabled lines. By setting **VBIMID** to 1, any line for which **VBIL**=3 will output raw ADC data instead of WSS or CGMS. This mode allows a mixture of sliced and raw data. This can be used to output raw data from a teletext line and sliced data from a closed caption line.

# 1.7.3. Select Individual Lines Enabled for VBI Processing

The KS0127B allows programmable selection of processing for the various video lines. For example Teletext/Intercast data can be sliced for lines 14 - 17, and closed caption for line 21.

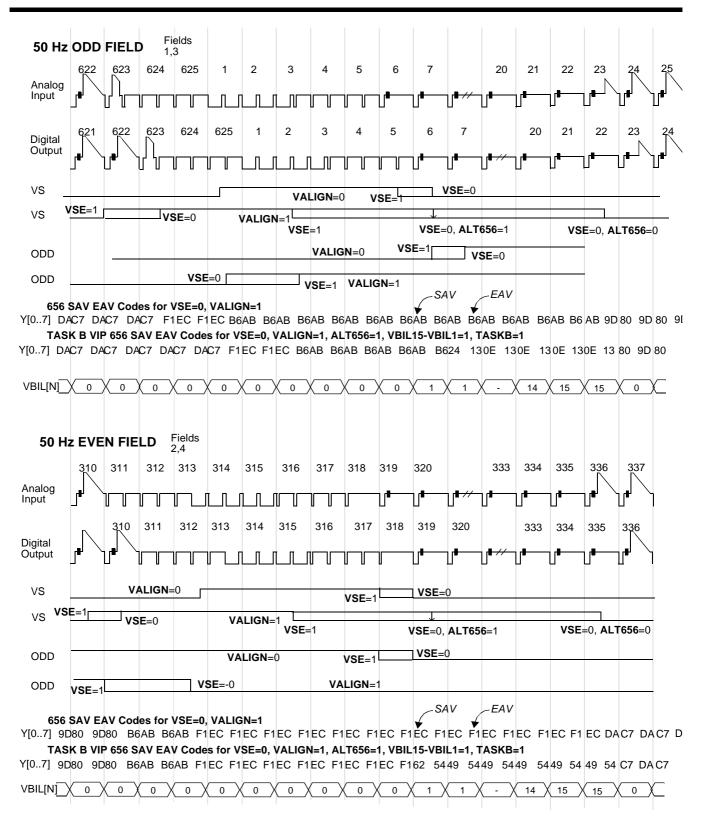

Each 2-bit register **VBIL0** through **VBIL15** defines how a specific VBI line is processed. As can be seen in Figure 36 for 60 Hz and Figure 37 for 50 Hz video, the following alignments exist:

Table 9: VBI Line(s) Selection

| VBIL   | Line Number That the VBIL Processing command applies to (Assuming ODDOS=1) |                                |                          |                               |  |

|--------|----------------------------------------------------------------------------|--------------------------------|--------------------------|-------------------------------|--|

| number | Odd Field<br>60 Hz                                                         | Even Field<br>60 Hz            | Odd Field<br>50 Hz       | Even Field<br>50Hz            |  |

| VBIL0  | All Lines<br>Except 10-24                                                  | All Lines<br>Except<br>273-287 | All lines<br>Except 7-21 | All lines Except<br>320 - 334 |  |

| VBIL1  | 9&10                                                                       | 272&273                        | 6&7                      | 319&320                       |  |

| VBIL2  | 11                                                                         | 274                            | 8                        | 321                           |  |

| VBIL3  | 12                                                                         | 275                            | 9                        | 322                           |  |

| VBIL4  | 13                                                                         | 276                            | 10                       | 323                           |  |

| VBIL5  | 14                                                                         | 277                            | 11                       | 324                           |  |

| VBIL6  | 15                                                                         | 278                            | 12                       | 325                           |  |

| VBIL7  | 16                                                                         | 279                            | 13                       | 326                           |  |

| VBIL8  | 17                                                                         | 280                            | 14                       | 327                           |  |

| VBIL9  | 18                                                                         | 281                            | 15                       | 328                           |  |

| VBIL10 | 19                                                                         | 282                            | 16                       | 329                           |  |

| VBIL11 | 20                                                                         | 283                            | 17                       | 330                           |  |

| VBIL12 | 21                                                                         | 284                            | 18                       | 331                           |  |

| VBIL13 | 22                                                                         | 285                            | 19                       | 332                           |  |

| VBIL14 | 23                                                                         | 286                            | 20                       | 333                           |  |

| VBIL15 | 24&25                                                                      | 287&288                        | 21&22                    | 334&335                       |  |

The **ODDOS[1:0**] bits allow offset between the odd and even fields. Thus VBIL9 can be lines 17,18 or 19 for ODD fields while VBIL9 is still line 281 for EVEN fields. This extra controls account for variations of VBI data locations from ODD and EVEN fields.

When Intercast or Teletext data is selected, an 8-bit user programmable register (TTFRAM) is provided for the framing byte. The frame alignment processor uses this information to properly locate the first data bit on each line

#### 1.7.4. Raw CVBS Data Output Format

When raw ADC data is selected as output in place of the normal YUV or RGB data. The following rules apply:

- For 656 type 8 bit outputs, The ADC data outputs with successive data points in place of the Cb, Y, Cr, Y data stream.

- For 16 bit or 24 bit outputs, The ADC data is output on the Y[7:0] and C[7:0] output pins. At any CK2 clock 2 bytes of ADC data are output. The Y[7:0] bus represents data N while C[7:0] is data N+1.

- ADC data is only output during the region that HAV is active.

- All ADC outputs are limited to the range 1-254, thus a 0 or 255 value will not be output.

For the line selected mode described above using **VBCVBS** and **VBIL**, data is from the luma ADC only. If C ADC data or the entire video line is required, configure **OFMT** bits.

#### 1.7.5. Sliced Data Output Formats

While sliced data is available for many of the output formats, the target application is 656 output format. The description of data format is limited to this mode. The KS0127B allows this data to be output during active video.

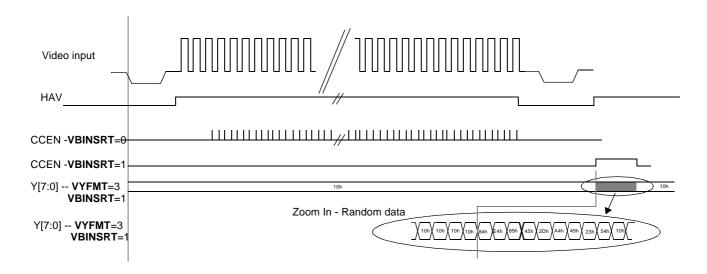

Figure 31 shows the timing diagram for **VYFMT[1:0]**=3.

Figure 31. VBI Insertion Timing for VYFMT[1:0]=3

Digitized CVBS data can also be output on the video output port (except for output format 1, 5 and 7). CVBS is always digitized at the CK clock rate. CVBS data is available when HAV is active. Raw CVBS data is output in a

similar fashion as decoded video. For 8-bit output format, data is output at CK rate using the same 8-bit port as the decoded video. For 16-bit and 24-bit output format, data is output at CK2 rate using Y and C ports. The sequence of data output is CVBS<sub>2n</sub> on Y, and CVBS<sub>2n+1</sub> on C (note that EXV port is not used in 24-bit format for outputting raw CVBS data).

For Closed Caption data, two read-only registers, **CCDAT1** and **CCDAT2**, are provided so the Closed Caption data can be read via the host interface. The **VBIFLG** bit can be polled to see if data captured in the two registers can be safely read.

## 1.8. COLOR SPACE CONVERTER

The color space converter processes the video data as YCbCr 4:4:4 when converting to RGB. A programmable limiter (YCRANG) can be imposed on the Y/C data to limit the ranges. One can choose to limit the Y/C to 1 - 254, or Y to 16 - 235 and C to 16 - 240.

When selected, YCbCr 4:4:4 is converted to 24 bit RGB according to the following equations:

$$R = C_Y + 1.375C_R$$

$G = C_Y - 0.703C_R - 0.328C_B$

$B = C_Y + 1.734C_B$

For 16-bit RGB output, truncation with dithering is used to convert the data from 24 bit to 16 bit.

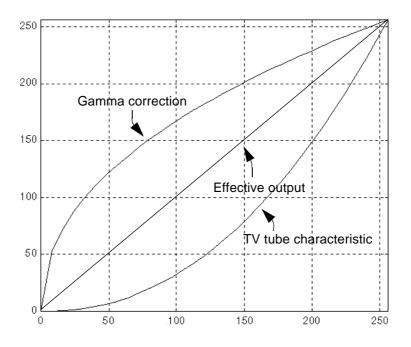

# 1.9. GAMMA CORRECTION

The KS0127B programmable gamma tables allows the customer to apply many different type of corrections. These corrections can be a standard 2.2 factor for NTSC or 2.8 for PAL. These factors can be applied in the RGB or YUV domains.

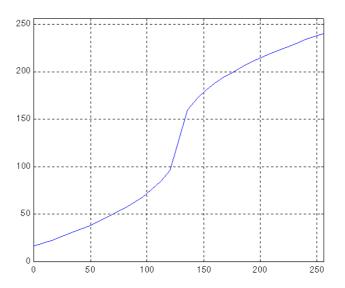

A basic standard gamma equation of

$$R = R'^{2.2}$$

when applied to the R, G, or B signals, generates the response shown as the upper curve below. It is the inverse of the monitor response and thus compensates to produce a linear response.

Figure 32. RGB Gamma Correction

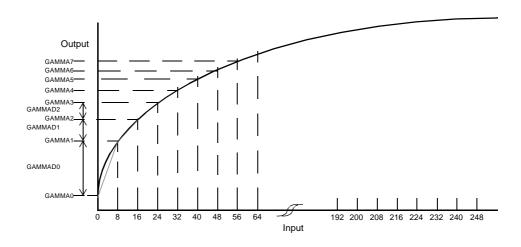

# 1.9.1. Programming the KS0127B

The previous response is easily programmed into the KS0127B loading the 0, 8, 16, 24 etc. values into the GAMMA0,1,2,3 locations. Thus every 8th value is stored. The KS0127B will use linear interpolation to generate the values between every 8th points. This is shown in the following figure.

Figure 33. Gamma LUT Programming

For ease of design, the difference between adjacent points must also be loaded. The complete data values for the previous gamma factor of 1/2.2 is shown in the table below.

Table 10: RGB Gamma LUT Values

| Offset | GAMMA<br>program at index Offset+40h | GAMMAD<br>program at index Offset+60h |

|--------|--------------------------------------|---------------------------------------|

| 0      | 0                                    | 53                                    |

| 1      | 53                                   | 20                                    |

| 2      | 73                                   | 14                                    |

| 3      | 87                                   | 12                                    |

| 4      | 99                                   | 11                                    |

| 5      | 110                                  | 10                                    |

| 6      | 120                                  | 8                                     |

| 7      | 128                                  | 8                                     |

| 8      | 136                                  | 8                                     |

| 9      | 144                                  | 7                                     |

| Α      | 151                                  | 7                                     |

| В      | 158                                  | 6                                     |

| С      | 164                                  | 6                                     |

| D      | 170                                  | 6                                     |

| Е      | 176                                  | 5                                     |

| F      | 181                                  | 6                                     |

| 10     | 187                                  | 5                                     |

| 11     | 192                                  | 5                                     |

| 12     | 197                                  | 5                                     |

| 13     | 202                                  | 5                                     |

| 14     | 207                                  | 4                                     |

| 15     | 211                                  | 5                                     |

| 16     | 216                                  | 4                                     |

| 17     | 220                                  | 5                                     |

| 18     | 225                                  | 4                                     |

| 19     | 229                                  | 4                                     |

| 1A     | 233                                  | 4                                     |

| 1B     | 237                                  | 4                                     |

| 1C     | 241                                  | 4                                     |

| 1D     | 245                                  | 4                                     |

| 1E     | 249                                  | 3                                     |

| 1F     | 252                                  | 4                                     |

The flexibility of this architecture is shown in the following example. Here it is assumed that the KS0127B is operating in a YUV output mode but some form of Gamma correction is required. By converting the RGB gamma correction function back to the YUV color space, the following function can be applied to the U and V signals for improved color performance. This flexibility can be extended in software to produce many type of customer defined transfer functions.

Figure 34. Gamma Correction for Cb and Cr

# 1.10. DIGITAL VIDEO OUTPUT

The KS0127B can output digital video data in various formats, which are tabulated in Table 11. All 8-bit output

**Table 11: Digital Video Output Format**

| Clock |     |            |     |      | (       | CK2 |                |            |            |            |     | C    | K       |    |

|-------|-----|------------|-----|------|---------|-----|----------------|------------|------------|------------|-----|------|---------|----|

| OFMT  | (   | 0          |     | •    | 1       |     | 4              | 5          | 6          | 7          |     | 2    | , 3     |    |

| Туре  |     | bCr<br>2:2 |     | YCbC | r 4:1:1 |     | YCbCr<br>4:4:4 | RGB<br>565 | RGB<br>888 | RGB<br>888 |     | YCbC | r 4:2:2 | ?  |

| Pin   | 2N  | +1         | 4N  | +1   | +2      | +3  | N              | N          | N          | N          | 4N  | +1   | +2      | +3 |

| C0    | Cb0 | Cr0        |     |      |         |     | Cb0            | B0         | В0         | В3         |     |      |         |    |

| C1    | Cb1 | Cr1        |     |      |         |     | Cb1            | B1         | B1         | B4         |     |      |         |    |

| C2    | Cb2 | Cr2        |     |      |         |     | Cb2            | B2         | B2         | B5         |     |      |         |    |

| C3    | Cb3 | Cr3        |     |      |         |     | Cb3            | В3         | В3         | B6         |     |      |         |    |

| C4    | Cb4 | Cr4        | Cr6 | Cr4  | Cr2     | Cr0 | Cb4            | B4         | B4         | B7         |     |      |         |    |

| C5    | Cb5 | Cr5        | Cr7 | Cr5  | Cr3     | Cr1 | Cb5            | G0         | B5         | G2         |     |      |         |    |

| C6    | Cb6 | Cr6        | Cb6 | Cb4  | Cb2     | Cb0 | Cb6            | G1         | B6         | G3         |     |      |         |    |

| C7    | Cb7 | Cr7        | Cb7 | Cb5  | Cb3     | Cb1 | Cb7            | G2         | B7         | G4         |     |      |         |    |

| Y0    | Y0  | Y0         | Y0  | Y0   | Y0      | Y0  | Y0             | G3         | G0         | G5         | Cb0 | Y0   | Cr0     | Y0 |

| Y1    | Y1  | Y1         | Y1  | Y1   | Y1      | Y1  | Y1             | G4         | G1         | G6         | Cb1 | Y1   | Cr1     | Y1 |

| Y2    | Y2  | Y2         | Y2  | Y2   | Y2      | Y2  | Y2             | G5         | G2         | G7         | Cb2 | Y2   | Cr2     | Y2 |

| Y3    | Y3  | Y3         | Y3  | Y3   | Y3      | Y3  | Y3             | R0         | G3         | R3         | Cb3 | Y3   | Cr3     | Y3 |

| Y4    | Y4  | Y4         | Y4  | Y4   | Y4      | Y4  | Y4             | R1         | G4         | R4         | Cb4 | Y4   | Cr4     | Y4 |

| Y5    | Y5  | Y5         | Y5  | Y5   | Y5      | Y5  | Y5             | R2         | G5         | R5         | Cb5 | Y5   | Cr5     | Y5 |

| Y6    | Y6  | Y6         | Y6  | Y6   | Y6      | Y6  | Y6             | R3         | G6         | R6         | Cb6 | Y6   | Cr6     | Y6 |

| Y7    | Y7  | Y7         | Y7  | Y7   | Y7      | Y7  | Y7             | R4         | G7         | R7         | Cb7 | Y7   | Cr7     | Y7 |

| EXV0  |     |            |     |      |         |     | Cr0            |            | R0         | В0         |     |      |         |    |

| EXV1  |     |            |     |      |         |     | Cr1            |            | R1         | B1         |     |      |         |    |

| EXV2  |     |            |     |      |         |     | Cr2            |            | R2         | B2         |     |      |         |    |

| EXV3  |     |            |     |      |         |     | Cr3            |            | R3         | G0         |     |      |         |    |

| EXV4  |     |            |     |      |         |     | Cr4            |            | R4         | G1         |     |      |         |    |

| EXV5  |     |            |     |      |         |     | Cr5            |            | R5         | R0         |     |      |         |    |

| EXV6  |     |            |     |      |         |     | Cr6            |            | R6         | R1         |     |      |         |    |

| EXV7  |     |            |     |      |         |     | Cr7            |            | R7         | R2         |     |      |         |    |

formats use CK as pixel clock; the other formats use CK2 as pixel clock. The first pixel is always aligned to the leading edge of the HAV signal.

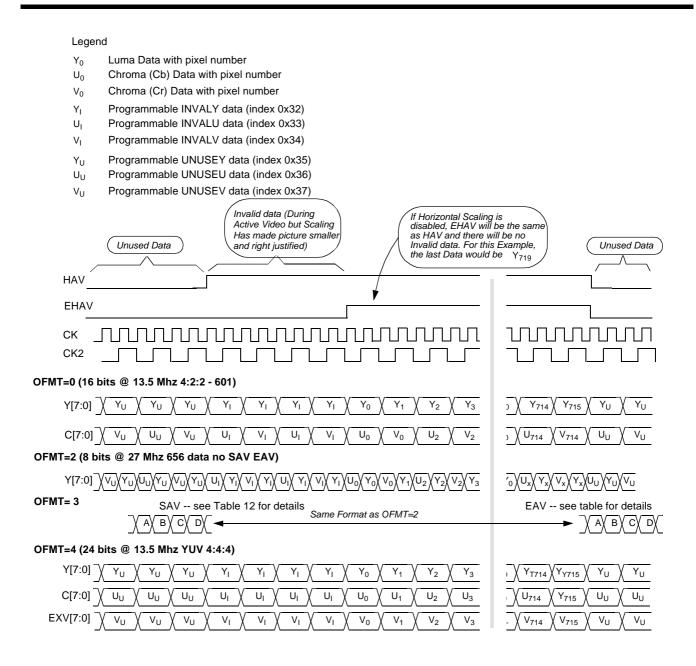

## 1.10.1. Validation Code Insertion

KS0127B inserts validation codes during inactive video (HAV is inactive), and invalid video (HAV is active but EHAV is inactive) to assist in recognition of scaled data and VBI data. Table 12 lists the available codes, when they are inserted, and related programming registers.

**Table 12: Invalid and Unused Code Insertion**

| Code   | Description                                                                                                                                                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INVALY | This user programmed code is inserted in the Y or G output stream in scaling operation when HAV is active while EHAV is inactive. Insertion of this code is independent of the output format. Related register is <b>INVALY</b> . |

| INVALU | This user programmed code is inserted in the U or B output stream in scaling operation when HAV is active while EHAV is inactive. Insertion of this code is independent of the output format. Related register is <b>INVALU</b> . |

| INVALV | This user programmed code is inserted in the V or R output stream in scaling operation when HAV is active while EHAV is inactive. Insertion of this code is independent of the output format. Related register is <b>INVALV</b> . |

| UNUSEY | This user programmed code is inserted in the Y or G output stream when HAV is inactive and no other reference code is inserted. Insertion of this code is independent of the output format. Related register is <b>UNUSEY</b> .   |

| UNUSEU | This user programmed code is inserted in the U or B output stream when HAV is inactive and no other reference code is inserted. Insertion of this code is independent of the output format. Related register is <b>UNUSEU</b> .   |

| UNUSEV | This user programmed code is inserted in the V or R output stream when HAV is inactive and no other reference code is inserted. Insertion of this code is independent of the output format. Related register is <b>UNUSEV</b> .   |

An example timing diagram for some of the programmable modes is shown in Figure 35. In this diagram, The field rate is 60 Hz, A CCIR 601 sampling rate has been selected thus giving 720 active pixels. The horizontal scaling ratio has been selected for an output of 718 out of 720 pixels.

Figure 35. Horizontal Data Timing for Various Output Modes

## 1.10.2. 656 Op Codes

The KS0127B supports timing synchronization through embedded (656) timing reference codes in the output video data stream. This mode is available for output format 3 ( $\mathbf{OFMT}[3:0] = 3$ ). The 656 Op Codes follow the CCIR 656 standard. An optional set of 656 Op Codes can be enabled to identify VBI data using the **TASKB** bit.

The (A,B,C,D) inserted codes for 656 output modes are explained below. Locations in the data stream are shown in Figure 35. The D'data is substituted for the standard codes shown in column D if **TASKB** bit is set and the current line is processing VBI data (sliced or raw ADC data format).

Figure 36. Vertical Timing for 60 Hz Video

Figure 37. Vertical Timing For 50 Hz Video

SAV / EAV Output Sequence --Condition Reference Output timing pic-656 FVH values tures Field D' Vertical Horizontal Α В C D F ν н Field 2 Vertical Blank **End Active Video** FFh 00h 00h F1h 7Fh Start Active Video Field 2 Vertical Blank ECh FFh 00h 00h 62h 1 1 0 End Active Video FFh Field 2 Vertical Active DAh 00h 00h 54h 1 0 1 Field 2 Vertical Active Start Active Video FFh 00h 00h C7h 49h 1 0 0 Field 1 Vertical Blank **End Active Video** FFh 00h 00h B6h 38h 0 1 1 Field 1 Vertical Blank Start Active Video FFh ABh 24h 00h 00h 0 1 0 Field 1 Vertical Active End Active Video FFh 00h 00h 9Dh 13h 0 0 1 FFh Field 1 Vertical Active Start Active Video 00h 80h 0Eh 0 0 00h 0

Table 13: 656 and TASKB 656 Op Codes

## 1.10.3. 656 Op Code Vertical Transitions

The vertical transition locations of the various 656 Op Codes are shown in Figure 36 and Figure 37. Note that for proper transition locations of the SAV and EAV Op Codes **VSE**=0 and **VALIGN**=1.

#### 1.11. HOST INTERFACE

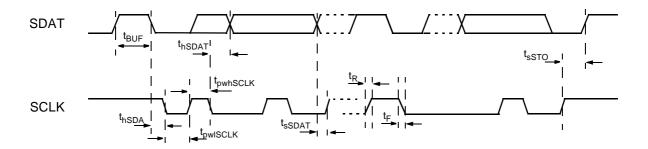

The KS0127B supports the IIC serial interface for programming the chip registers.

#### 1.11.1. IIC Interface

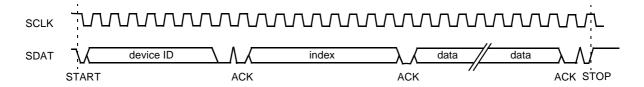

The two wire interface consists of the SCLK and SDAT signals. Data can be written to or read from the KS0127B. For both read and write, each byte is transferred MSB first, and the data bit is valid when the SCLK is high.

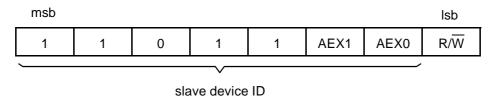

To write to the slave device, the host initiates a transfer cycle with a START signal. The START signal is HIGH to LOW transition on the SDAT while the SCLK is high. The host then sends a byte consisting of the 7-bit slave device ID and a 0 in the R/W bit. The arrangement for the slave device ID and the R/W bit is depicted in Figure 38. AEX1 and AEX0 are configuration pins used to configure the KS0127B to use one of the four addresses. Up to four KS0127Bs can be used in one system each with a unique address.

Figure 38. IIC Slave Device ID and R/W Byte

The second byte the host sends is the base register index. The host then sends the data. The KS0127B increments the index automatically after each byte of data is sent. Therefore, the host can write multiple bytes to the slave if they are in sequential order. The host completes the transfer cycle with a STOP signal which is a LOW to HIGH transition when the SCLK is high.

Each byte transfer consists of 9 clocks. When writing to the KS0127B, an acknowledge signal is asserted by the salve device during the 9th clock.

Figure 39. IIC Data Write

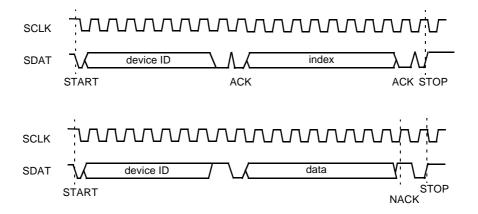

A read cycle takes two START-STOP phases. The first phase is a write to the index register. The second phase is the read from the data register.

The host initiates the first phase by sending the START signal. It then sends the slave device ID along with a 0 in the R/W position. The index is then sent followed by the STOP signal.

The second phase also starts with the START signal. It then sends the slave device ID but with a 1 in the R/W position to indicate data is to be read from the slave device. The host uses the SCLK to shift data out from the KS0127B. A typical second phase in a read transaction is depicted in Figure 40. Auto index increment is supported in Read mode.

Figure 40. IIC Data Read

# 2. CONTROL REGISTER DESCRIPTION