DS4056 - 3.4

# GP2010

# **GLOBAL POSITIONING SYSTEM RECEIVER RF FRONT END**

(Supersedes edition in August 1996 Global Positioning Products Handbook, HB4305-1.0)

The GP2010 is GEC Plessey Semiconductors' second generation RF Front-end for Global Positioning System (GPS) receivers. The GP2010 uses many innovative design techniques and a leading-edge bipolar process to offer a low power, low cost and high reliability RF Front End solution. The GP2010 is designed to operate from either 3 or 5 Volt power supplies.

The input to the device is the L1 (1575.42MHz) Coarse-Acquisition (C/A) code Global Positioning signal from an antenna (via a low-noise pre-amplifier). The output is 2-bit quantised for subsequent signal processing in the digital domain. The GP2010 contains an on-chip synthesiser, mixers, AGC and a quantiser which provides Sign and Magnitude digital outputs. A minimum of external components is required to make a complete GPS front-end.

The device has been designed to operate with the GP2021 12-channel Global Positioning Correlator, and DW9255 SAW filter, both also available from GEC Plessey Semiconductors.

### FEATURES

- Low Voltage Operation (3V 5V)

- Low Power 200mW typ. (3V supply)

- C/A Code Compatible

- On-chip PLL Including Complete VCO

- Triple Conversion Receiver

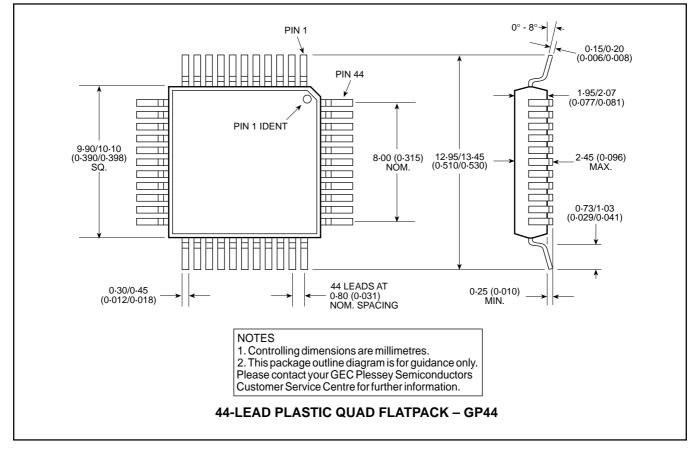

- 44-Lead Surface Mount Quad Flat-Pack Package

- Sign and Magnitude Digital Outputs

- Compatible with GP2021 CMOS Correlator

# APPLICATIONS

- C/A Code Global Positioning by Satellite Receivers

- Time Standards

- Navigation

- Surveying

#### **ORDERING INFORMATION**

The GP2010 is available in 44 pin Quad Flat pack (gullwing formed leads) to Industrial (-40°C to +85°C) grade.

#### **ORDERING CODE**

GP2010 IG GPBR Industrial - Plastic 44-pin PQFP

| 34<br>34<br>35<br>36<br>39<br>39<br>40<br>41<br>42<br>43<br>44<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55<br>55    |                                                                                                                                                                                                                                                                                    |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                                                                                                     | Name                                                                                                                                                                                                                                                                               | Pin                                                                                                                              | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22 | IF Output<br>PLL Filter 1<br>PLL Filter 2<br>$V_{EE}$ (OSC)<br>$V_{CC}$ (OSC)<br>$V_{EE}$ (OSC)<br>$V_{EE}$ (REG)<br>PRef<br>PReset<br>$V_{EE}$ (IO)<br>CLK<br>MAG<br>SIGN<br>OPCIK-<br>OPCIK-<br>OPCIK+<br>$V_{DD}$ (IO)<br>PDN<br>TEST<br>LD<br>$V_{EE}$ (DIG)<br>AGC -<br>AGC + | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44 | $V_{CC} (DIG) \\ REF 2 \\ REF 1 \\ V_{CC} (RF) \\ V_{EE} (RF) \\ V_{EE} (RF) \\ RF Input \\ V_{EE} (RF) \\ V_{CC} (RF) \\ O/P 1- \\ O/P 1- \\ O/P 1+ \\ V_{CC} (2) \\ I/P 2- \\ I/P 2+ \\ V_{EE} (IF) \\ V_{EE} (IF) \\ V_{EE} (IF) \\ O/P 2- \\ O/P 2- \\ O/P 2- \\ O/P 2- \\ O/P 3- \\ I/P 3- \\ I/P 3+ \\ O = 0 \\ O$ |  |  |  |

Fig. 1 Pin connections - top view

#### **RELATED PRODUCTS AND PUBLICATIONS**

| Part         | Description                                       | Data<br>Reference |

|--------------|---------------------------------------------------|-------------------|

| DW9255       | 35.42MHz SAW Filter                               | DS3861            |

| GP2021       | Twelve-Channel Correlator                         | DS4057            |

| GPSBuilder-2 | Twelve-Channel GPS receiver<br>development system | DS4004            |

| GP2010       | Design with the GP2010                            | AN4364            |

| GP2015       | Small RF Format Front End                         | DS4374            |

| GP2015       | Design with the GP2015                            | AN4533            |

#### ABSOLUTE MAXIMUM RATINGS (Non-simultaneous)

| (NOII-SIIIIuitaneous)                    |                                           |

|------------------------------------------|-------------------------------------------|

| Max. Supply Voltage                      | 7V                                        |

| Max. RF Input                            | +15dBm                                    |

| Max. voltage on any pin                  | $V_{CC}/V_{DD} + 0.5V$                    |

| except LD (pin 19) and PReset (pin 9), v | vhich are 5.5V                            |

| Min. voltage on any pin                  | V <sub>EE</sub> - 0.5V<br>-65°C to +150°C |

| Storage Temperature                      | -65°C to +150°C                           |

| Operation Junction Temperature           | -40°C to +150°C                           |

| 10MHz Reference Input                    | 1.5V pk -pk                               |

|                                          |                                           |

# **ESD PROTECTION**

The GP2010 device is static sensitive. The most sensitive pins withstand a 750V test by the human body model. Therefore, ESD handling precautions are essential to avoid degradation of performance or permanent damage to this device.

# **PRODUCT DESCRIPTION**

The GP2010 receives the 1575.42MHz signal transmitted by GPS satellites and converts it to a 4.309MHz IF, using a triple down-conversion. The 4.309MHz IF is sampled to produce a 2-bit digital output. If the GP2010 is used in conjunction with the GP2021 correlator, then the GP2021 provides a sampling clock of 5.714MHz. This converts the IF to a 1.405MHz 2-bit digital output at TTL levels.

The GP2010 can operate from a single supply from +3V (nominal) to +5V (nominal).

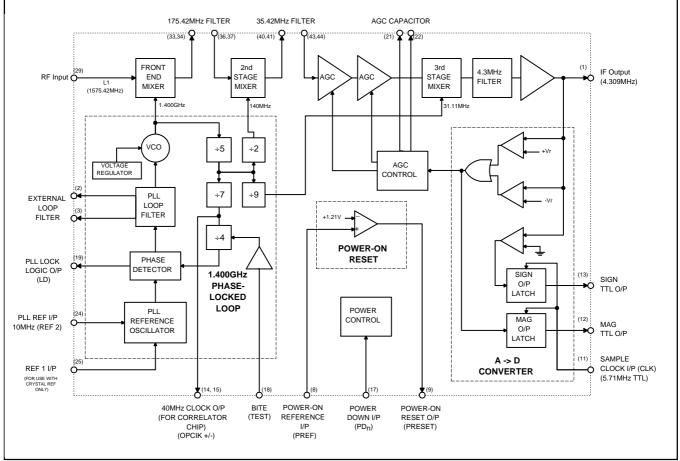

A block diagram of the circuit is shown in figure 2.

#### IF STRIP

The input signal to the GP2010 is the GPS L1 signal received via an antenna and a suitable LNA. The L1 input is a spread spectrum signal at 1575.42MHz with 1.023Mbps BPSK modulation. The signal level at the antenna is about -130dBm, spread over a 2.046MHz bandwidth, so the wanted signal is actually buried in noise. The high RF input compression point of the GP2010 means that with subsequent IF filtering it is possible to reject large out of band jamming signals, in particular 900MHz as used by mobile telephones. The on-chip PLL generates the first local-oscillator frequency at 1400MHz. The output of the front-end mixer (Stage 1) at 175.42 MHz can then be filtered before being applied to the second stage. The double-balanced stage 1 mixer outputs are open-collectors, and require external dc bias to  $V_{CC}$ .

The second stage contains further gain and a mixer with a local oscillator signal at 140 MHz giving a second IF at 35.42 MHz. The second stage mixer is also double-balanced with open-collector outputs requiring external dc bias to  $V_{CC}$ .

The signal from stage 2 is passed through an external filter with a 1dB bandwidth of 1.9MHz. The performance of this filter is critical to system performance and it is recommended that a SAW filter is used (part number DW9255, also available from GEC Plessey Semiconductors). The output of the filter then feeds the main IF amplifier. This includes 2 AGC amplifiers and a third mixer with a local oscillator signal at 31.111 MHz giving a final IF at 4.309 MHz. There is an on-chip filter after the third mixer which provides filtering centred on 4.309 MHz. The IF output, which has  $1k\Omega$  output impedance, is provided for test purposes. All of the signals within the IF amplifier are differential including the filter inputs and outputs, except the IF output (pin 1), to reduce any common mode interference.

Fig. 2 Block diagram of GP2010

The IF output is fed to a 2-bit quantiser which provides sign and magnitude (MSB and LSB) outputs. The magnitude data controls the AGC loop, such that on average the magnitude bit is set (high) 30% of the time. The AGC time constant is set by an external capacitor.

The sign and magnitude data, SIGN (pin 13) and MAG (pin 12), are latched by the rising edge of the sample clock, CLK (pin 11), which is normally derived from the correlator; the GP2021 provides a 5.714MHz (=40/7) clock, giving a sampled IF centred on 1.405MHz.

The Digital Interface circuits use a separate power-supply,  $V_{\text{DD}}(\text{IO})$ , which would normally be shared with the correlator to minimise crosstalk between the analog and digital sections of the device.

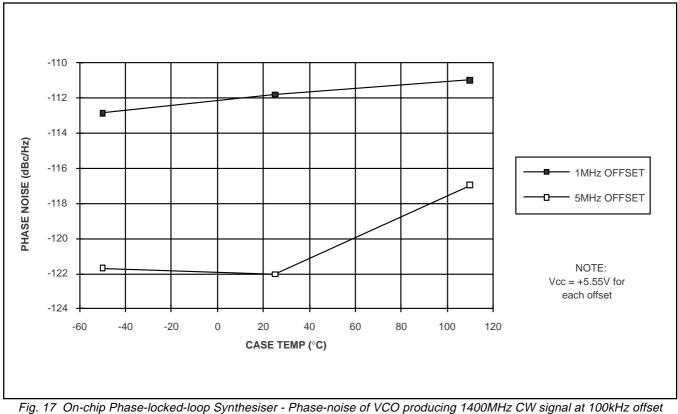

#### **ON-CHIP PHASE-LOCKED LOOP SYNTHESISER**

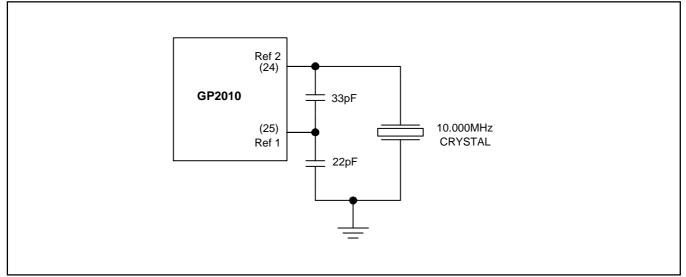

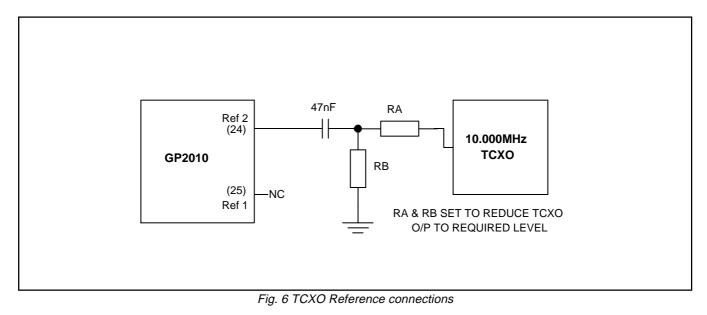

All of the local oscillator signals are derived from an on chip phase locked loop synthesiser. This includes a 1400MHz VCO complete with on-chip tank circuit, dividers and phase detector, with external loop filter components. A 10.000MHz reference frequency is required for the PLL. This can be achieved by attaching an external 10.000MHz crystal to the on-chip PLL reference oscillator (see figure 5). However in most applications the user will need an external source, such as a TCXO, to provide greater frequency stability (see figure 6). An external reference should be ac coupled to REF2 (pin 24); REF 1 (pin 25) should be left open circuit.

The three local oscillator signals 1400MHz, 140.0MHz and 31.11MHz are derived from the 1400MHz synthesiser output. The synthesiser also provides a 40 MHz balanced differential output clock (pins 14 & 15) which can be used to clock the GP2021 correlator. The clock is a low level differential signal which helps minimise interference with the analog areas of the circuit. A PLL lock-detect output, LD (pin 19), is also provided, which is logic high when the PLL is phaselocked to the 10.000MHz reference signal.

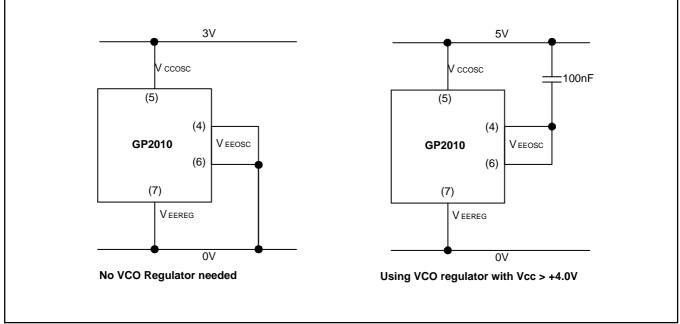

The VCO power-supply incorporates an on-chip regulator to improve the noise-immunity of the PLL. This feature is only available when operating with a 5 volt (nominal) supply which is regulated to 3.3 volts internally. This internal regulated supply is referenced to  $V_{CC}(OSC)$  (pin 5). Figure 7 shows the required connections for both 3 volt and 5 volt operation.

A further feature of the circuit is the TEST input (pin 18). When this input is held high the PLL is unlocked with the VCO at its maximum frequency.

#### **POWER-DOWN CAPABILITY**

A power down function is provided on the GP2010, to limit power consumption. This powers down the majority of the circuit except the "power-on reset" function (see below).

If the power down feature is not required, the Powerdown input,  $PD_n$  (pin 17), should be connected to 0V dc (=Vee/Ground).

#### **POWER-ON RESET FUNCTION**

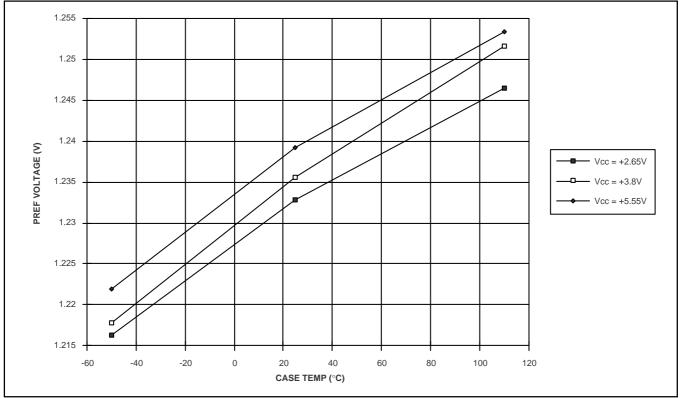

The GP2010 includes a voltage detector which operates from the digital interface supply. This circuit is used to produce a TTL logic low output while the GPS receiver power supply is switching on, and produces a logic high output when the power supply voltage has achieved a nominal value. This output can be used to disable the GP2021 correlator while the power supply is switching on. An internal bandgap reference of approximately +1.21V is compared with the voltage on a sense pin, PRef (pin 8); when the voltage on this pin exceeds the reference, a TTL logic high level appears at the Power-on Reset output, PReset (pin 9). Thus, if the sense input voltage is derived from an external resistive divider from the Digital Interface supply, V<sub>DD</sub>(IO) (pin 16), such that the sense voltage at nominal  $V_{CC}$  is  $V_S$ , then the supply threshold, Vcc(thresh), at which the PReset output goes to logic high is:-

$$V_{\rm S} = \frac{V_{\rm CC} \text{ (nom) x 1.21}}{V_{\rm CC} \text{ (thresh)}}$$

For a V\_{CC} (nom) of 5.0V, V\_{CC} (thresh) may be set to approx. 4.0V, giving V\_S of 1.5V.

For a  $V_{CC}$  (nom) of 3.0V,  $V_{CC}$  (thresh) may be set to approx. 2.4V, giving  $V_S$  of 1.5V.

#### ADDITIONAL INFORMATION

All the digital inputs and outputs can use a separate power supply to help prevent digital switching transitions interacting with the analog sections of the device, and as an additional precaution, the digital inputs and outputs are on the opposite side of the device to the critical analog pins.

# **ELECTRICAL CHARACTERISTICS**

The Electrical Characteristics are guaranteed over the following range of operating conditions (see Fig. 3 for test circuit):

Industrial (I) grade:  $T_{AMB} = -40^{\circ}C$  to  $+85^{\circ}C$ Supply voltage:  $V_{CC}$  and  $V_{DD} = +2.7V$  to +5.5VTest conditions (unless otherwise stated):

$V_{CC}$  = +2.7V and +5.5V,  $V_{DD}$  = +2.7V and +5.5V Industrial (I) grade product: +25°C Supply voltages: Test temperature:

|                                                                                                                                                                                                                                                            | Value                         |                                                  |                             |                                                              |                                                                                                                                                                                                                                                                                                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------|-----------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristic                                                                                                                                                                                                                                             | Min.                          | Тур.                                             | Max.                        | Units                                                        | Conditions                                                                                                                                                                                                                                                                                                                          |  |

| SUPPLY CURRENT<br>Normal mode - Analog interface<br>- Digital interface<br>Power down mode - Analog interface<br>- Digital interface<br>Power Supply Differential<br>Power down Response time                                                              |                               | 55<br>9<br>3<br>3<br>3                           | 77<br>14.5<br>6<br>5<br>100 | mA<br>mA<br>mA<br>mV<br>μs                                   | Pins 5, 23, 26, 32, 35, 42<br>Pin 16<br>Pins 5, 23, 26, 32, 35, 42<br>Pin 16<br>Between any $V_{CC}/V_{DD}$ pins (Note 7)<br>(Note 7)                                                                                                                                                                                               |  |

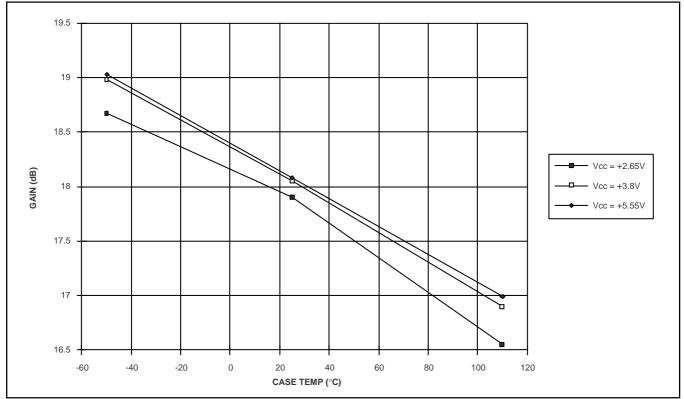

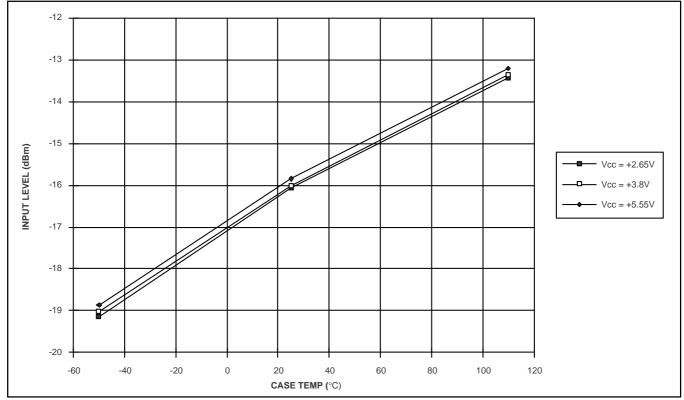

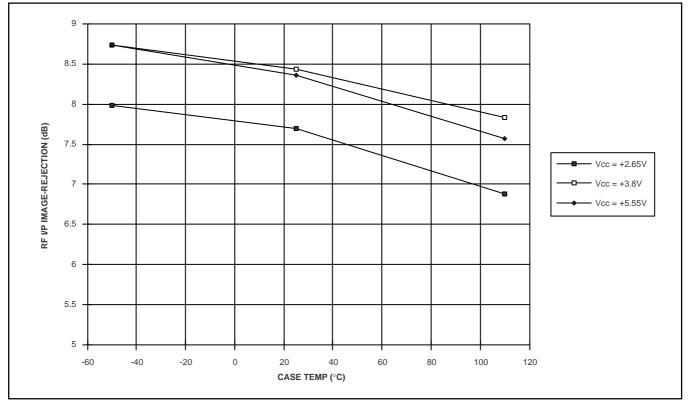

| IF STRIP<br>Front End/Mixer 1<br>Conversion Gain (G1)<br>Noise Figure<br>Input Compression (1dB)<br>Input Impedance<br>Differential Output Impedance<br>RF Input Image Rejection                                                                           | 11<br>-22                     | 18<br>9<br>-16<br>15<br>3.6<br>700<br>8          | 25                          | dB<br>dBm<br>Ω<br>nH<br>Ω<br>dB                              | $\begin{split} R_{O} &= 600\Omega \; (\text{Note 2}) \\ F_{\text{IN}} &= \; 1575.42 \text{MHz} \\ Z_{S} &= \; 50\Omega \; (\text{Note 7}) \\ \text{Pin 29} \; (\text{Notes 1 and 7}) \\ (\text{Notes 1 and 7}) \\ \text{Pins 33 \& 34} \; (\text{Note 8}) \\ F_{\text{IN}} &= \; 1224.58 \text{MHz} \; (\text{Note 7}) \end{split}$ |  |

| <b>Stage 2/Mixer 2</b><br>Conversion Gain (G2)<br>Input Compression (1dB)<br>Differential Input Impedance<br>Differential Output Impedance                                                                                                                 | 22<br>5                       | 27<br>14<br>700<br>500                           | 33                          | dB<br>mV rms<br>Ω<br>Ω                                       | F <sub>IN</sub> = 175.42MHz<br>Pins 36 & 37 (Note 8)<br>Pins 40 & 41 (Note 8)                                                                                                                                                                                                                                                       |  |

| Stage 3<br>High Gain (In terms of total strip)<br>High Gain (G3)<br>Gain Control Range<br>Differential Input Impedance<br>IF Output amplitude<br>IF Output impedance<br>4.3MHz Filter Response<br>Flatness $4.3 \pm 1MHz$<br>Rejection @ 0.5MHz<br>@ 50MHz | 106-G1-G2<br>60<br>-1.5<br>45 | 75<br>60<br>1<br>85<br>1<br>14<br>70             | 120<br>+1.0                 | dB<br>dB<br>dB<br>kΩ<br>mV rms<br>kΩ<br>dB<br>dB<br>dB<br>dB | (Note 6)<br>$F_{IN} = 35.42MHz$<br>(Note 3)<br>Pins 43 & 44 (Note 8)<br>CW input (Note 3)<br>Pin 1(Note 8)<br>(Note 7 and 9)                                                                                                                                                                                                        |  |

| 2 BIT QUANTISER<br>Sign Duty Cycle<br>Mag Duty Cycle<br>AGC Time Constant                                                                                                                                                                                  | 40<br>20                      | 50<br>30<br>2                                    | 60<br>40                    | %<br>%<br>ms                                                 | } (Note 10)<br>C <sub>AGC</sub> = 100nF                                                                                                                                                                                                                                                                                             |  |

| ON-CHIP PLL SYNTHESISER<br>Phase Noise<br>± 1kHz<br>± 10kHz<br>± 10kHz<br>± 100kHz<br>± 1MHz<br>± 50MHz<br>PLL Spurs                                                                                                                                       |                               | -68<br>-75<br>-88<br>-110<br>-120<br>-120<br>-50 |                             | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz     | 15kHz Loop Bandwidth (Note 7) (Note 7)                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                  | Value                 |                                                         |                              |                                   |                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------|------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------|--|

| Characteristic                                                                                                                                                                   | Min.                  | Тур.                                                    | Max.                         | Units                             | Conditions                                                                                   |  |

| VCO Maximum Lock Frequency<br>VCO Minimum Lock Frequency<br>VCO regulator output voltage<br>VCO Gain<br>Phase Detector Gain                                                      | 1414<br>3<br>50       | 3.3<br>150<br>5.3                                       | 1386<br>3.5<br>240           | MHz<br>MHz<br>V<br>MHz/V<br>V/rad | (Note 4)<br>(Note 7)                                                                         |  |

| 10MHz Reference Input<br>10MHz Reference Input Impedance                                                                                                                         | 0.1                   | 0.6<br>5                                                | 1.2                          | V pk-pk<br>kΩ                     | Pin 24<br>(Note 11)                                                                          |  |

| PLL Lockup Time<br>PLL Loop Gain                                                                                                                                                 |                       | 6<br>150                                                |                              | ms<br>dB                          | From Power up (Note 7)<br>(Note 7)                                                           |  |

| DIGITAL INTERFACES<br>Sample Clock, Power Down,<br>Test Inputs.<br>V <sub>IH</sub><br>V <sub>IL</sub><br>Input Current High I <sub>IH</sub><br>Input Current Low I <sub>IL</sub> | 2<br>0<br>-300        |                                                         | V <sub>DD</sub><br>0.5<br>10 | ν<br>ν<br>μΑ<br>μΑ                | Pins 11, 17, 18<br>$V_{IH} = V_{DD}$<br>$V_{IL} = V_{EE}$                                    |  |

| Sign/Mag Outputs<br>V <sub>OH</sub><br>V <sub>OL</sub>                                                                                                                           | V <sub>DD</sub> -1    |                                                         | 0.5                          | V<br>V                            | Pins 13, 12<br>$I_0 = -0.5mA$<br>$I_0 = 0.5mA$                                               |  |

| Sample Clock to Sign/Mag Delay                                                                                                                                                   |                       | 20                                                      |                              | ns                                | $CL = 15pF, RL = 15k\Omega$ (Note 7)                                                         |  |

| <b>40MHz Clock Output</b><br>High Level (V <sub>OH</sub> )<br>Low Level (V <sub>OL</sub> )<br>Output (differential)<br>Duty Cycle                                                | V <sub>DD</sub> -1.25 | V <sub>DD</sub> -1<br>V <sub>OH</sub> -0.1<br>220<br>43 | V <sub>DD</sub> -0.8         | V<br>V<br>mV p-p<br>%             | Pins 14 & 15<br>(Note 5)<br>CL = 15pF (GND) (Note 7)<br>CL = 5pF (Diff) (Note 7)<br>(Note 7) |  |

| LD (PLL Lock)/PReset Outputs<br>Low Level (V <sub>OL</sub> )<br>High Level (V <sub>OH</sub> )                                                                                    | V <sub>DD</sub> -1    | 0.2<br>V <sub>DD</sub>                                  | 0.5                          | V<br>V<br>V                       | Pins 19 and 9<br>$I_0 = 0.5mA$<br>$I_0 = -10\mu A$                                           |  |

| <b>Power-on Reset comparator input</b><br>Power Reset Reference Level<br>Power Reset Reference Input Current                                                                     | 1.1<br>-10            |                                                         | 1.35<br>10                   | V<br>μA                           | Pin 8                                                                                        |  |

Notes On Electrical Characteristics:- All RF measurements are made with appropriate matching to the input or output impedances, such as balun transformers, and levels refer to matched 50ohm ports (see figure 3 for test circuit)

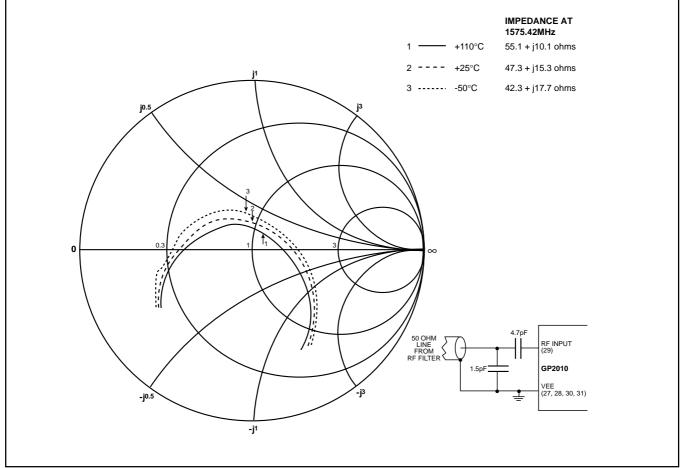

- 1. RF input impedance (series) without input matching components connected expressed as Real impedance with reactive inductor value. Measured at 1575.42MHz.

- 2. Input matched to 50ohm, output loaded with 600ohms differential

- 3. Maximum Stage 3 input signal amplitude for correct AGC operation = 20mV rms.

- 4. VCO regulator voltage measured with respect to Vcc (OSC) pin 5.

- 5. OPCLK outputs are differential and are referenced to V<sub>DD</sub>.

- 6. Minimum gain requirement expressions:

-7dBm < -174dBm/Hz + 19dB + G1 + G2 + G3 - 21dB + 63dB

where -7dBm = typical IF Output level with AGC active (equivalent to 100mV rms)

- -174dBm/Hz = background noise level at RF input

- 19dB = sum of LNA gain and noise figure

- -21dB = total loss in 175MHz and 35MHz filters

- 63dB = summation of noise over a 2MHz bandwidth

Rearranging the above expression gives G1 + G2 + G3 > 106dB.

- 7. This parameter is not production tested.

- 8. This impedance is toleranced at +/-30% and is not production tested.

- 9. Roll off occurs in on-chip capacitive coupling IF Output to input of ADC circuit. Not measurable at IF Output.

- 10. CW input on pins 43 & 44 of 35.42MHz at 7mV rms.

- 11. This input impedance applies to the typical input level. The impedance is level dependent and is not tested or guaranteed.

5

PIN DESCRIPTIONS All V<sub>EE</sub> and V<sub>CC</sub>/V<sub>DD</sub> pins should be connected to ensure reliable operation

| Pin No. | Signal Name           | Input/Output | Description                                                                                                                                                                                                                               |

|---------|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IFOutput              | Output       | IF Test output.<br>Connected to output of Stage 3 prior to the A to D converter.<br>A series $1k\Omega$ resistor is incorporated for buffering purposes.                                                                                  |

| 2       | PLL Filt1             | Output       | PLL Filter 1.<br>Connected to the bias network within the on-chip VCO. An<br>external PLL loop filter network should be connected between<br>this pin and PLL Filt 2 (see below).                                                         |

| 3       | PLL Filt2             | Output       | PLL Filter 2.<br>Connected to the varactor diodes within the on-chip VCO. An<br>external PLL loop filter network should be connected between<br>this pin and PLL Filt 1 (see above).                                                      |

| 4,6     | V <sub>EE</sub> (OSC) | Input        | Negative supply to the on-chip VCO. (See Note 1)                                                                                                                                                                                          |

| 5       | V <sub>CC</sub> (OSC) | Input        | Positive supply to the on-chip VCO.                                                                                                                                                                                                       |

| 7       | V <sub>EE</sub> (REG) | Input        | Negative supply to the VCO regulator.<br>This must be connected to GND.                                                                                                                                                                   |

| 8       | PRef                  | Input        | Power-on Reset Reference input.<br>An on-chip comparator produces a logic HI when the PRef<br>input voltage exceeds +1.21V. (Nom) (See Page 3).                                                                                           |

| 9       | PReset                | Output       | Power-on Reset Output.<br>A TTL compatible output controlled by the Power-on reset<br>comparator (See above). This output remains active even<br>when the chip is powered down. (See pin 17 - PDn).                                       |

| 10      | V <sub>EE</sub> (IO)  | Input        | Negative supply to the Digital Interface. (See Note 2)                                                                                                                                                                                    |

| 11      | CLK                   | Input        | Sample Clock input from the correlator chip.<br>A TTL compatible input (which operates at 5.714MHz if used<br>with GP2021 correlator device) used to clock the MAG & SIGN<br>output latches, on the <b>rising</b> edge of the CLK signal. |

| 12      | MAG                   | Output       | Magnitude bit data output.<br>A TTL compatible signal, representing the <i>magnitude</i> of the<br>mixed down IF signal. Derived from the on-chip 2-bit A to D<br>converter, synchronised to the CLK input clock signal.                  |

| 13      | SIGN                  | Output       | Sign bit data output.<br>A TTL compatible signal, representing the <i>polarity</i> of the mixed<br>down IF signal. Derived from the on-chip 2-bit A to D converter,<br>synchronised to the CLK input clock signal.                        |

| 14      | OPCIk-                | Output       | 40MHz Clock output - inverse phase.<br>One side of a balanced differential output clock, with opposite<br>polarity to Pin 15 - OPClk+. Used to drive a master-clock signal<br>within the correlator chip.                                 |

| 15      | OPClk+                | Output       | 40MHz Clock output - true phase.<br>Other side of a balanced differential output clock set, with<br>opposite polarity to Pin 14 - OPCIk Used to drive a master-<br>clock signal within the correlator chip.                               |

| 16      | V <sub>DD</sub> (IO)  | Input        | Positive supply to the Digital Interface. (See Note 2)                                                                                                                                                                                    |

| Pin No.           | Signal Name           | Input/Output | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                | PDn                   | Input        | Power-Down control input.<br>A TTL compatible input, which when set to logic high, will disable ALL of the GP2010 functions, except the power-on reset block. Useful to reduce the total power consumption of the GP2010. If this feature is not required, the pin should be connected to 0V ( $V_{EE}$ /GND).                                                                                      |

| 18                | TEST                  | Input        | Test control input - Disable PLL.<br>A TTL compatible input, which when set to logic high, will<br>disable the on-chip PLL, by disconnecting the divided-down<br>VCO signal to the phase-detector. The VCO will free run at its<br>upper range of frequency operation. If this feature is not<br>required, the pin should be connected to 0V ( $V_{EE}$ /GND).                                      |

| 19                | LD                    | Output       | PLL Lock Detect output.<br>A TTL compatible output, which indicates if the PLL is phase-<br>locked to the PLL reference oscillator. Will become logic high<br>only when phase-lock is achieved.                                                                                                                                                                                                     |

| 20                | V <sub>EE</sub> (DIG) | Input        | Negative supply to the PLL and A to D converter.                                                                                                                                                                                                                                                                                                                                                    |

| 21                | AGC-                  | Output       | AGC Capacitor output - inverse phase.<br>One side of a balanced output from the AGC block within IF<br>Stage 3, to which an external capacitor is connected to set the<br>AGC time-constant.                                                                                                                                                                                                        |

| 22                | AGC+                  | Output       | AGC Capacitor output - true phase.<br>One side of a balanced output from the AGC block within IF<br>Stage 3, to which an external capacitor is connected to set the<br>AGC time-constant.                                                                                                                                                                                                           |

| 23                | V <sub>CC</sub> (DIG) | Input        | Positive supply to the PLL and A to D converter.                                                                                                                                                                                                                                                                                                                                                    |

| 24                | REF 2                 | Input        | 10.000MHz PLL Reference signal input .<br>Input to which an externally generated 10.000MHz PLL<br>reference signal should be ac coupled, if an external PLL<br>reference frequency source (e.g TCXO) is used (see fig. 6).<br>If no external reference is used, this pin forms part of the on-<br>chip PLL reference oscillator, in conjunction with an external<br>10.000MHz crystal (see fig. 5). |

| 25                | REF 1                 | Input        | PLL reference oscillator auxillary connection.<br>Used in conjunction with Pin 24 (REF 2) to allow a 10.000MHz<br>external crystal to provide the PLL reference signal if no<br>external PLL reference frequency source (e.g TCXO) is used.<br>This pin should NOT be connected if an external TCXO is<br>being used (see fig. 5).                                                                  |

| 26, 32            | V <sub>CC</sub> (RF)  | Input        | Positive supply to the RF input and Stage 1 IF mixer.<br>Both pins 26 & 32 ( $V_{CC}$ (RF)) are connected internally, but<br>must both be connected to $V_{CC}$ externally, to keep series<br>inductance to a minimum.                                                                                                                                                                              |

| 27, 28,<br>30, 31 | V <sub>EE</sub> (RF)  | Input        | Negative supply to the RF input and Stage 1 IF mixer.<br>Pins 27, 28, 30 & 31 are all connected internally, but must ALL<br>be connected to 0V ( $V_{EE}$ /GND) externally, to keep series<br>inductance to a minimum.                                                                                                                                                                              |

| Pin No. | Signal Name          | Input/Output | Description                                                                                                                                                                                                                                                                                                                                 |  |

|---------|----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29      | RF Input             | Input        | RF input.<br>The GPS RF input signal @ 1575.42MHz from an external<br>antenna with LNA and filter is connected to this pin via an<br>input-matching network (see fig.4).                                                                                                                                                                    |  |

| 33      | O/P 1-               | Output       | Stage 1 mixer output @ 175.42MHz - inverse phase.<br>One of a balanced output from first stage IF mixer, to which<br>one input of an external balanced 175MHz bandpass filter is<br>connected. External dc biasing is required via an inductor<br>connected to $V_{CC}(RF)$ - the value of which is dependent on the<br>filter used.        |  |

| 34      | O/P 1+               | Output       | Stage 1 mixer output @ 175.42MHz - true phase.<br>Second of a balanced output from first stage IF mixer, to which<br>the second input of an external balanced 175MHz bandpass<br>filter is connected. External dc biasing is required via an<br>inductor connected to $V_{CC}(RF)$ - the value of which is dependent<br>on the filter used. |  |

| 35      | V <sub>CC</sub> (2)  | Input        | Positive supply to the Stage 2 IF mixer.                                                                                                                                                                                                                                                                                                    |  |

| 36      | I/P 2-               | Input        | Stage 2 mixer input @ 175.42MHz - inverse phase.<br>One of a balanced input to the second stage IF mixer, to which<br>one of the balanced signal outputs from the external 175MHz<br>bandpass filter is connected.                                                                                                                          |  |

| 37      | I/P 2+               | Input        | Stage 2 mixer input @ 175.42MHz - true phase.<br>Second of a balanced input to the second stage IF mixer, to<br>which the second of the balanced signal outputs from the<br>external 175MHz bandpass filter is connected.                                                                                                                   |  |

| 38,39   | V <sub>EE</sub> (IF) | Input        | Negative supply to the Stage 2 IF mixer, and Stage 3 IF block.                                                                                                                                                                                                                                                                              |  |

| 40      | O/P 2-               | Output       | Stage 2 mixer output @ $35.42$ MHz - inverse phase.<br>One of a balanced output from second stage IF mixer, to which<br>one input of an external balanced $35.42$ MHz bandpass filter is<br>connected. External dc biasing is required via an Inductor<br>connected to V <sub>CC</sub> . (See Note 3)                                       |  |

| 41      | O/P 2+               | Output       | Stage 2 mixer output @ $35.42$ MHz - true phase.<br>Second of a balanced output from second stage IF mixer, to<br>which the second input of an external balanced $35.42$ MHz<br>bandpass filter is connected. External dc biasing is required<br>via an Inductor connected to V <sub>CC</sub> . (See Note 3)                                |  |

| 42      | V <sub>CC</sub> (3)  | Input        | Positive supply to the Stage 3 IF mixer.                                                                                                                                                                                                                                                                                                    |  |

| 43      | I/P 3-               | Input        | Stage 3 mixer input @ 35.42MHz - inverse phase.<br>One of a balanced input to the third stage IF mixer, to which<br>one of the balanced signal outputs from the external 35.42MHz<br>bandpass filter is connected. (See Note 3)                                                                                                             |  |

| 44      | I/P 3+               | Input        | Stage 3 mixer input @ 35.42MHz - true phase.<br>Second of a balanced input to the third stage IF mixer, to which<br>the second of the balanced signal outputs from the external<br>35.42MHz bandpass filter is connected. (See Note 3)                                                                                                      |  |

#### **Notes on Pin Descriptions**

- 1). Both pins 4 & 6 ( $V_{EE}$  (OSC)) are connected internally. If the VCO regulator is used ( $V_{CC}$  = +5.00V nominal) then both pins 4 & 6 must be left floating, with either pin de-coupled to  $V_{CC}$  (OSC) with a 100nF capacitor. In this configuration, the dc output level of the regulator can be monitored from  $V_{EE}$  (OSC), with respect to  $V_{CC}$  (OSC) NOT 0V ( $V_{EE}$ /GND). For operation at  $V_{CC}$  <+4.0V, the VCO regulator cannot be used, and both  $V_{EE}$  (OSC) pins must be shorted to  $V_{EE}$  (REG) (Pin 7) see Fig. 7.

- 2). The Digital Interface supply is independent from all the other supply pins, allowing supply separation to reduce the likelihood of undesirable digital signals interfering with the IF strip. (Note the maximum allowable Power Supply Differential in the Electrical Characteristics page 4).

- 3). The 35.42MHz Bandpass filter should have a bandwidth of approx 2.0MHz. Ideally, this should be a DW9255 SAW filter.

#### **CONTROL SIGNALS**

|            | L                | Н            |

|------------|------------------|--------------|

| Power Down | Normal Operation | Powered Down |

| TEST       | Normal Operation | Test         |

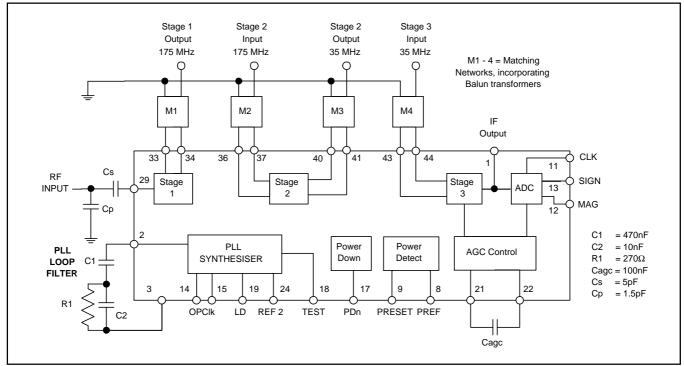

Fig. 3 GP2010 test circuit

#### **OPERATING NOTES**

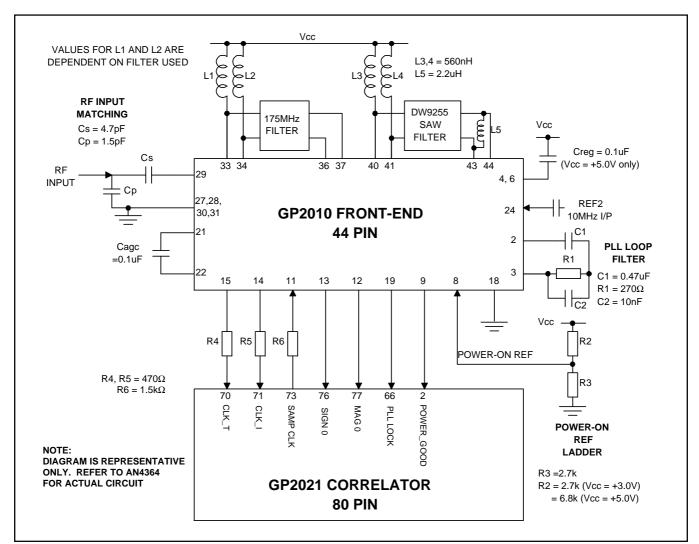

A typical application circuit is shown in figure 4 with the GP2010 front-end interfaced to the GP2021 12 channel correlator integrated circuit. The RF input has an unmatched input impedance (see page 4). The RF input matching components Cs and Cp should be mounted as close to the RF input as possible: also the Vee(RF) tracks must be kept as short as possible. A SAW may be used as a 175.42MHz filter, but this can be replaced by a simpler coupled-tuned LC filter if there is no critical out-of band jamming immunity requirement. The DC bias to mixer 1 is provided via inductors L1 and L2, which may form part of the 175.42MHz filter. The output of mixer 2 requires an external dc bias, achieved with inductors L3 and L4, which also serve to tune out the input capacitance of the DW9255 SAW filter. The output of the SAW is tuned with inductor L5. The AGC capacitor (Cagc) determines the AGC time-constant. The PLL loop filter components are selected to give a PLL loop bandwidth of approx. 10kHz. The IF Output is normally used for test-purposes only, but is available to the user if required. Typically a low noise preamplifier (gain >+15dB) is used, and may be located with a remote antenna.

#### QUALITY AND RELIABILITY

At GEC Plessey Semiconductors, quality and reliability are built into products by rigorous control of all processing operations, and by minimising random, uncontrolled effects in all manufacturing operations. Process management involves full documentation of procedures, recording of batch-bybatch data, using traceability procedures, and the provision of appropriate equipment and facilities to perform sample screening and conformance testing on finished product.

A common information management system is used to monitor the manufacturing on GEC Plessey Semiconductors CMOS and Bipolar processes. All products benefit from the use of an integrated monitoring system throughout all manufacturing operations, leading to high quality standards for all technologies.

Further information is contained in the Quality Brochure, available from GEC Plessey Semiconductors' Sales Offices.

Fig. 4 GP2010 typical application

Fig. 5 Crystal Reference connections

Fig. 7 VCO power-supply connections

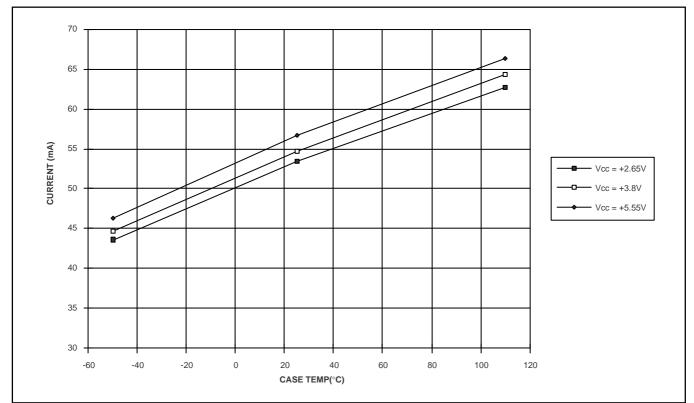

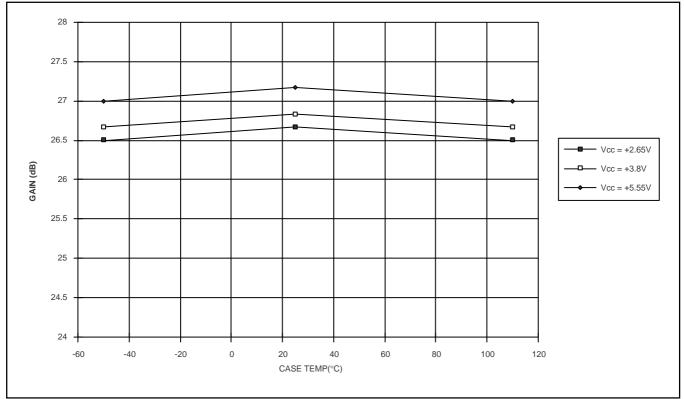

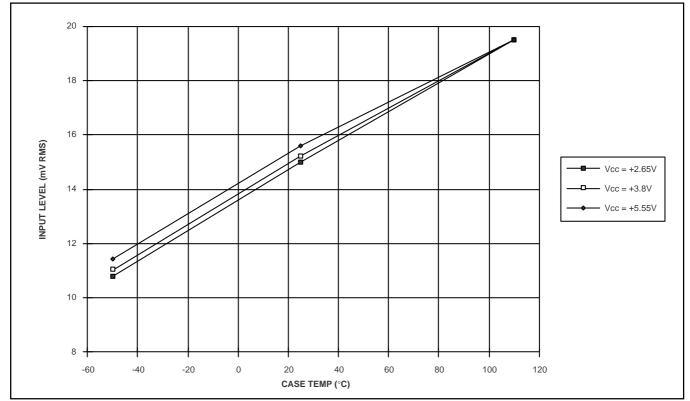

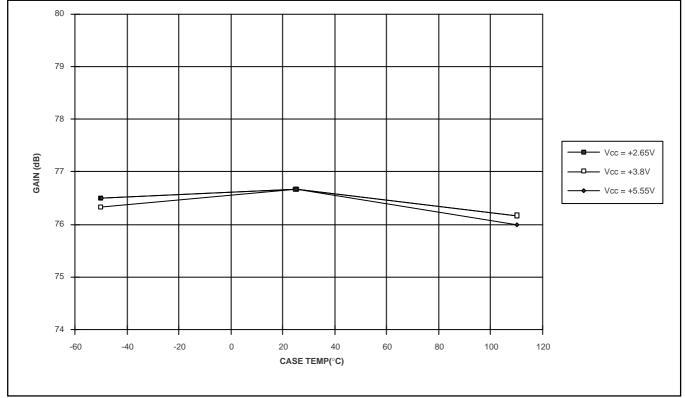

# TYPICAL CHARACTERISTICS OF THE GP2010 GPS RECEIVER RF FRONT-END

The GP2010 has been characterised to guarantee reliable operation over the Industrial Temperature range (-40°C -> +85°C ambient). This was achieved by setting the device case temperature to extremes of +110°C and -50°C. The following charts show the typical variation of key parameters across the extended case temperature range.

NOTE:- ALL Measurements at Vcc = +2.65V made with VCO voltage-regulator DISABLED.

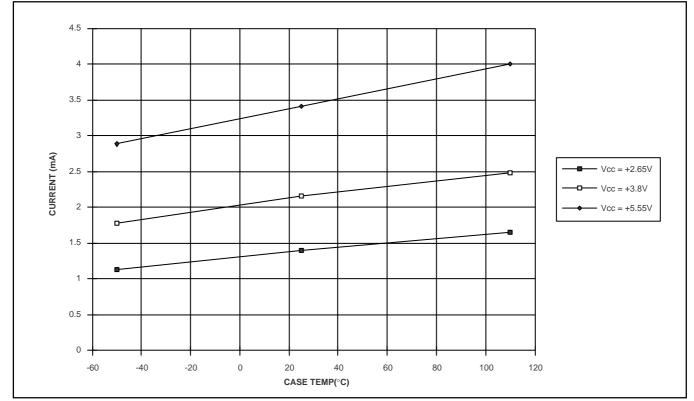

Fig. 9 Supply Current - Analog interface - power-down mode

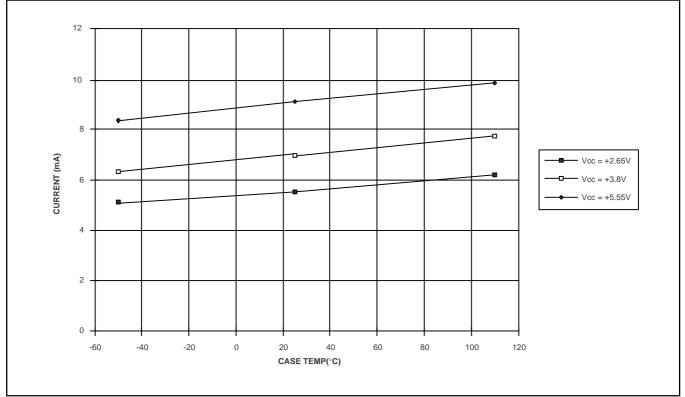

Fig. 10 Supply Current - Digital interface - normal mode

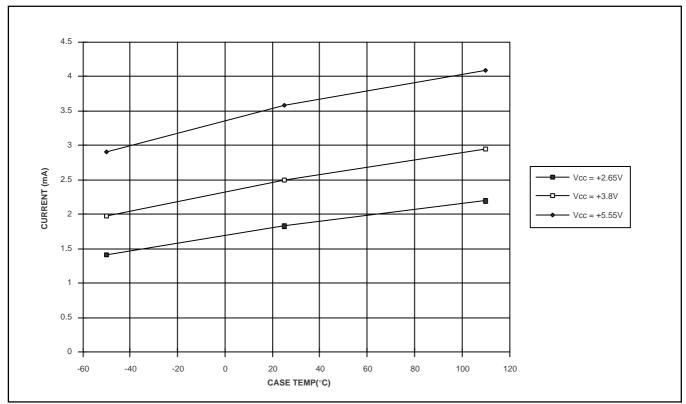

Fig. 11 Supply Current - Digital interface - power-down mode

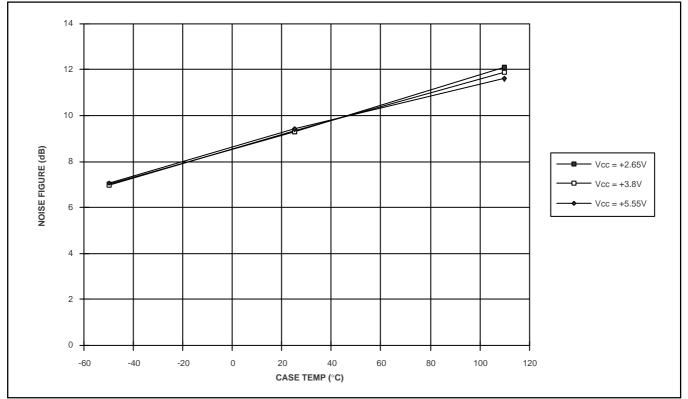

Fig. 12 Noise figure of IF chain in a typical application circuit

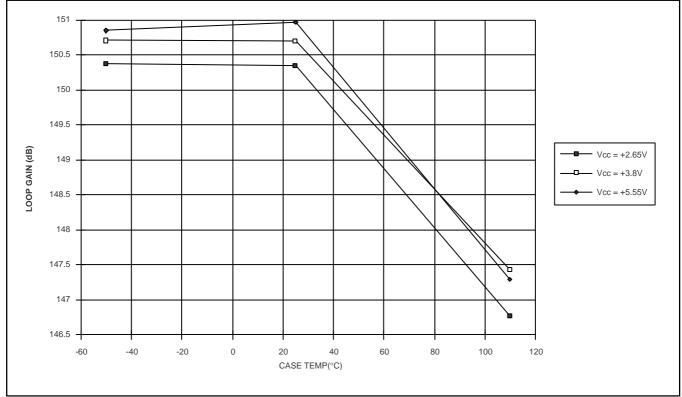

Fig. 13 On-chip Phase-locked-loop Synthesiser Loop gain

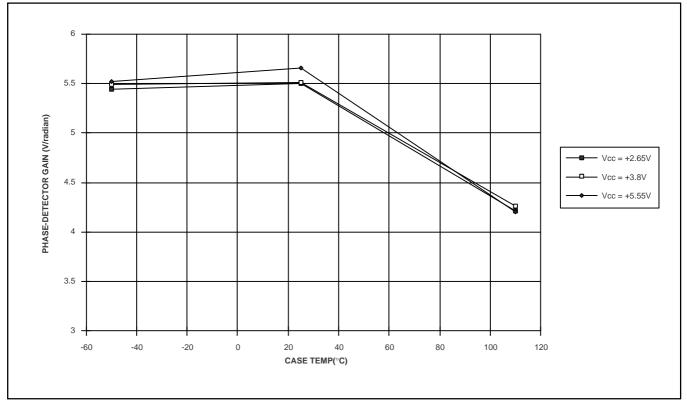

Fig. 14 On-chip Phase-locked-loop Synthesiser Phase-detector gain

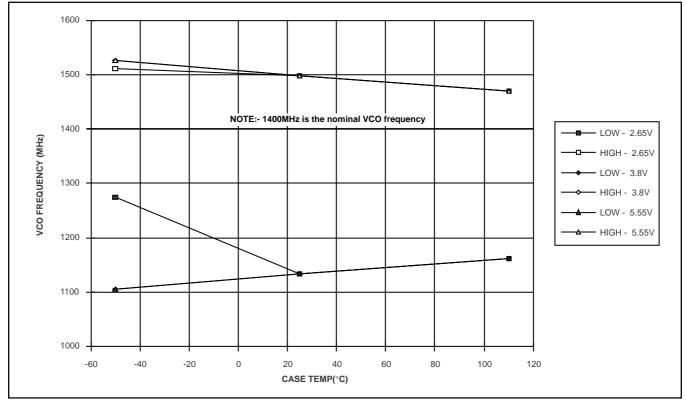

Fig. 15 On-chip Phase-locked-loop Synthesiser - LOW and HIGH limits of VCO frequency for PLL to be locked (Note that this a **typical** characteristic and **cannot** be guaranteed)

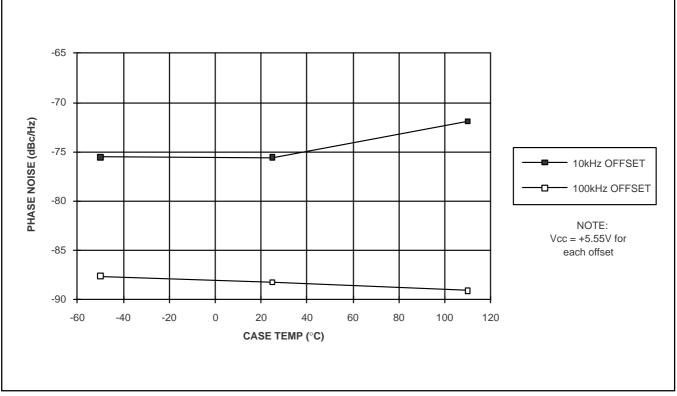

Fig. 16 On-chip Phase-locked-loop Synthesiser - Phase-noise of VCO producing 1400MHz CW signal at 10kHz offset (15kHz PLL loop bandwidth)

(15kHz PLL loop bandwidth)

Fig. 18 Frontend/Mixer 1 Small-signal Conversion Gain - RF I/P frequency at 1575.42MHz

Fig. 19 Frontend/Mixer 1 Input level for 1dB Conversion Gain-compression - RF I/P frequency at 1575.42MHz

Fig. 20 Frontend/Mixer 1 Image rejection - RF I/P frequency at 1224.58MHz

Fig. 21 Stage 2/Mixer 2 Small-signal Conversion Gain - Stage 2 I/P frequency at 175.42MHz

Fig. 22 Stage 2/Mixer 2 Input level for 1dB Conversion Gain-compression - Stage 2 I/P frequency at 175.42MHz

Fig. 23 Stage 3 MAXIMUM Small-signal Conversion Gain - Stage 3 I/P frequency at 35.42MHz

Fig. 24 Power-on Reset Threshold level

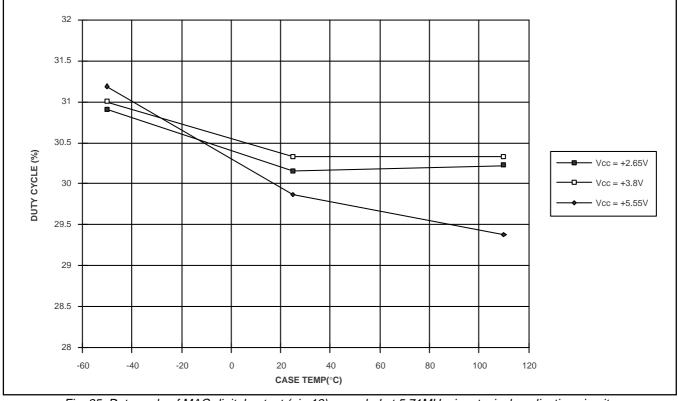

Fig. 25 Duty-cycle of MAG digital output (pin 12), sampled at 5.71MHz in a typical application circuit -RF I/P signal = 1575.42MHz CW, -85dBm - equivalent to 26dB excess noise from a typical GPS antenna

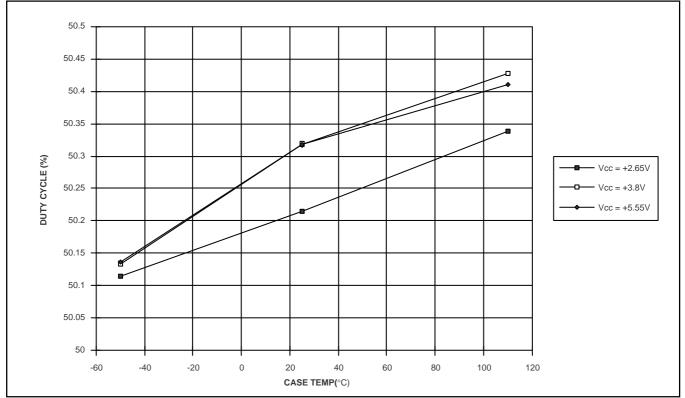

Fig. 26 Duty-cycle of SIGN digital output (pin 13), sampled at 5.71MHz in a typical application circuit - RF I/P signal = 1575.42MHz CW, -85dBm - equivalent to 26dB excess noise from a typical GPS antenna

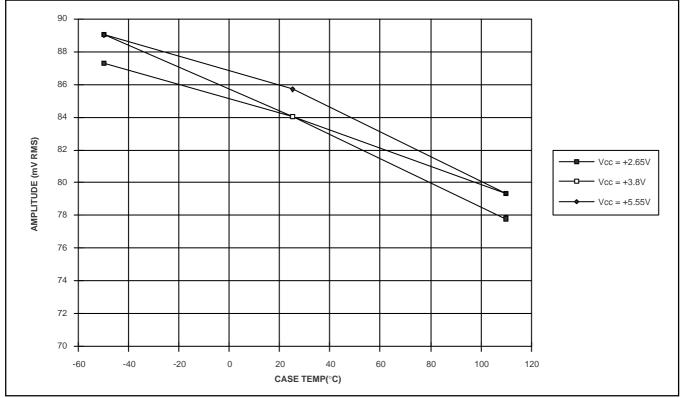

Fig. 27 Amplitude of IFOUT (pin 1) at 4.3MHz (±1.0MHz) in a typical application circuit - RF I/P signal = 1575.42MHz CW, -85dBm - equivalent to 26dB excess noise from a typical GPS antenna

Fig. 28 Typical Matched RF I/P Impedance between 1000MHz and 2000MHz RF I/P level @ -40dBm

# **PACKAGE DETAILS**

Dimensions are shown thus: mm (in)

#### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (01793) 518000 Fax: (01793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017 1500 Green Hills Road. Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 69 18 90 00 Fax : (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- **NORTH AMERICA** Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023. **SOUTH EAST ASIA** Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260. Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

- Swindon Tel: (01793) 726666 Fax : (01793) 518582

These are supported by Agents and Distributors in major countries world-wide. © GEC Plessey Semiconductors 1996 Publication No. DS4056 Issue No. 3.4 October 1996 TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request