## 4MEGABIT (512K $\times$ 8/ 256K $\times$ 16) 5VOLT SECTOR ERASE CMOS FLASH MEMORY

### **GENERAL DESCRIPTION**

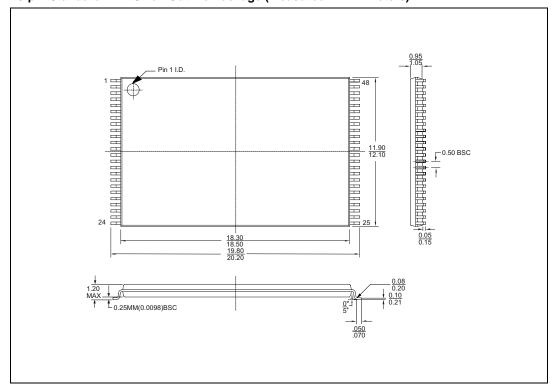

The BM29F400 is an 4 Megabit, 5.0 volt-only CMOS Flash memory device organized as a 512 Kbytes of 8-bits each, or 256 Kbytes of 16 bits each. The device is offered in standard 48-pin TSOP package. It is designed to be programmed and erased in-system with a 5.0 volt power-supply and can also be reprogrammed in standard EPROM programmers.

With access times of 90 nS, 120 nS, and 150 nS, the BM29F400 has separate chip enable CE, write enable  $\overline{\text{WE}}$ , and output enable  $\overline{\text{OE}}$  controls. BMI's memory devices reliably store memory data even after 100,000 program and erase cycles.

The BM29F400 is entirely pin and command set compatible with the JEDEC standard for 4 Megabit Flash memory devices. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations.

The BM29F400 is programmed by executing the program command sequence. This will start the internal byte/word programming algorithm that automatically times the program pulse width and also verifies the proper cell margin. Erase is accomplished by executing either the sector erase or chip erase command sequence. This will start the internal erasing algorithm that automatically times the erase pulse width and also verifies the proper cell margin. No preprogramming is required prior to execution of the internal erase algorithm. Sectors of the BM29F400 Flash memory array are electrically erased via Fowler-Nordheim tunneling. Bytes/words are programmed one byte/word at a time using a hot electron injection mechanism.

The BM29F400 features a sector erase architecture. The device memory array is divided into one 16 Kbytes, two 8 Kbytes, one 32 Kbytes, and seven 64 Kbytes. Sectors can be erased individually or in groups without affecting the data in other sectors. Multiple sector erase and full chip erase capabilities add flexibility to altering the data in the device. To protect this data from accidental program and erase, the device also has a sector protect function. This function hardware write protects the selected sector(s). The sector protect and sector unprotect features can be enabled in a PROM programmer.

For read, program and erase operation, the BM29F400 needs a single 5.0 volt power-supply. Internally generated and well regulated voltages are provided for the program and erase operation. A low Vcc detector inhibits write operations on loss of power. End of program or erase is detected by the Ready/Busy status pin, Data Polling of DQ7, or by the Toggle Bit I feature on DQ6. Once the program or erase cycle has been successfully completed, the device internally resets to the Read mode.

The BM29F400 also has a hardware RESET pin. Driving the RESET pin low during execution of an Internal Programming or Erase command will terminate the operation and reset the device to the Read mode. The RESET pin may be tied to the system reset circuitry, so that the system will have access to boot code upon completion of system reset, even if the Flash device is in the process of an Internal Programming or Erase operation. If the device is reset using the RESET pin during an Internal Programming or Erase operation, data in the address locations on which the internal state

## BM29F400T/BM29F400B

machine is operating will be erroneous. Thus, these address locations will need rewriting after the device is reset.

#### **FEATURES**

- 5.0V +/- 10% Program and Erase

- Minimizes system-level power requirements

High performance

- 90 nS access time

- Compatible with JEDEC-standard Commands

- Uses software commands, pinouts, and packages following industry standards for single power supply Flash memory

- Typically 100,000 Program/Erase Cycles

- · Sector Erase Architecture

- One 16 Kbytes, two 8 Kbytes, one 32 Kbytes, and seven 64 Kbytes

- Any combination of sectors can be erased concurrently; also supports full chip erase

- Erase Suspend/Resume

- Suspend a sector erase operation to allow a data read in a sector not being erased within the same device

- · Ready/Busy

- RY/BY output pin for detection of programming or erase cycle completion

#### RESET

- Hardware pin resets the internal state machine to the read mode

- · Internal Erase Algorithms

- Automatically erases a sector, any combination of sectors, or the entire chip

- Internal Programming Algorithms

- Automatically programs and verifies data at a specified address

- Low Power Consumption

- 20 mA typical active read current for Byte Mode

- 28 mA typical active read current for Word Mode

- 30 mA typical write/erase current

- Sector Protection

- Hardware method disables any combination of sectors from a program or erase operation

- Boot Code Sector Architecture

| FAMILY PART NO.          | -90 | -120 | -150 |

|--------------------------|-----|------|------|

| Maximum Access Time (nS) | 90  | 120  | 150  |

| CE (E) Access time (nS)  | 90  | 120  | 150  |

| OE (G) Access time (nS)  | 35  | 50   | 60   |

<sup>\*</sup>This speed is available with Vcc = 5V +/- 5% variation

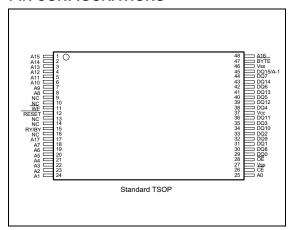

## **PIN CONFIGURATIONS**

## **PIN DESCRIPTION**

| A0-A17   | Address Inputs               |

|----------|------------------------------|

| DQ0-DQ14 | Data Input/Output            |

| DQ15/A-1 | Data Input/Output, Address   |

|          | Max.                         |

| CE       | Chip Enable                  |

| ŌĒ       | Output Enable                |

| WE       | Write Enable                 |

| Vss      | Device Ground                |

| RESET    | Hardware RESET Pin,          |

|          | Active Low                   |

| RY/BY    | Ready/Busy Status Output     |

| Vcc      | Device Power Supply          |

| BYTE     | Selects 8-bit or 16-bit Mode |

| NC       | Not Internally Connected     |

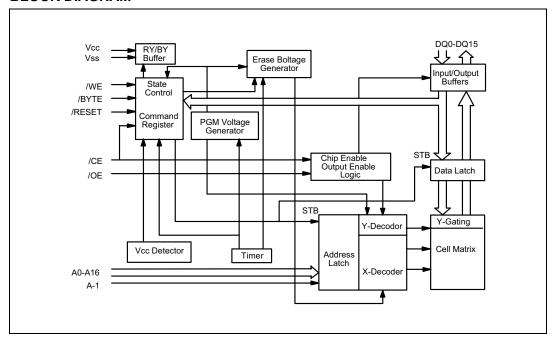

## **BLOCK DIAGRAM**

## **BUS OPERATION**

Table 1. Bus Operations ( $\overline{\text{BYTE}} = \text{ViH}$ )(1)

| OPERATION                                 | CE | OE | WE | A0 | A1 | A6 | A9  | DQ0-DQ15 | RESET |

|-------------------------------------------|----|----|----|----|----|----|-----|----------|-------|

| Electronic ID Manufacturer <sup>(2)</sup> | L  | L  | Н  | L  | L  | L  | VID | Code     | Н     |

| Electronic ID Device(2)                   | L  | L  | Н  | Н  | L  | L  | VID | Code     | Н     |

| Read <sup>(3)</sup>                       | L  | L  | Н  | A0 | A1 | A6 | A9  | Dout     | Н     |

| Standby                                   | Н  | Х  | Х  | Х  | Х  | Х  | Х   | High Z   | Н     |

| Hardware Reset                            | Х  | Х  | Х  | Х  | Х  | Х  | Х   | High Z   | L     |

| Output Disable                            | L  | Н  | Н  | Х  | Χ  | Χ  | Х   | High Z   | X     |

| Write                                     | L  | Н  | L  | A0 | A1 | A6 | A9  | DIN(4)   | Н     |

| Verify Sector Protect <sup>(2)</sup>      | L  | L  | Н  | L  | Н  | L  | VID | Code     | Н     |

| Temporary Sector Unprotect                | Х  | Х  | Х  | Х  | Х  | Х  | Х   | X        | VID   |

#### Notes:

- 1. L = V<sub>I</sub>L, H = V<sub>I</sub>H, X = Don't Care. See DC Characteristics for voltage levels.

- 2. Manufacturer and device codes may also be accessed via a command register sequence. Refer to Table 6.

- 3.  $\overline{\text{WE}}$  can be V<sub>IL</sub> if  $\overline{\text{CE}}$  is V<sub>IL</sub>,  $\overline{\text{OE}}$  at V<sub>IH</sub> initiates the write operations.

- 4. Refer to Table 6 for valid  $\ensuremath{D_{\mbox{\footnotesize IN}}}$  during a write operation.

Table 2. Bus Operations ( $\overline{BYTE} = VIL$ )(1)

| OPERATION                                 | CE | ŌE | WE | A0 | <b>A</b> 1 | A6 | A9  | DQ0-DQ7            | DQ8-DQ15 | RESET |

|-------------------------------------------|----|----|----|----|------------|----|-----|--------------------|----------|-------|

| Electronic ID Manufacturer <sup>(2)</sup> | L  | L  | Н  | L  | L          | L  | VID | Code               | High Z   | Н     |

| Electronic ID Device <sup>(2)</sup>       | L  | L  | Н  | Н  | L          | L  | VID | Code               | High Z   | Н     |

| Read <sup>(3)</sup>                       | L  | L  | Н  | A0 | A1         | A6 | A9  | Douт               | High Z   | Н     |

| Standby                                   | Н  | Х  | Х  | Х  | Х          | Х  | Х   | High Z             | High Z   | Н     |

| Hardware Reset                            | Х  | Х  | Х  | Х  | Х          | Х  | Х   | High Z             | High Z   | L     |

| Output Disable                            | L  | Н  | Н  | Х  | Х          | Х  | Х   | High Z             | High Z   | Н     |

| Write                                     | L  | Н  | L  | A0 | A1         | A6 | A9  | DIN <sup>(4)</sup> | High Z   | Н     |

| Verify Sector Protect <sup>(2)</sup>      | L  | L  | Н  | L  | Н          | L  | VID | Code               | High Z   | Н     |

| Temporary Sector Unprotect                | Х  | Х  | Х  | Х  | Х          | Х  | Х   | Х                  | High Z   | VID   |

- 1. L = V<sub>IL</sub>, H = V<sub>I</sub>H, X = Don't Care. See DC Characteristics for voltage levels.

- 2. Manufacturer and device codes may also be accessed via a command register sequence. Refer to Table 6.

- 3.  $\overline{\text{WE}}$  can be V<sub>IL</sub> if  $\overline{\text{CE}}$  is V<sub>IL</sub>,  $\overline{\text{OE}}$  at V<sub>IH</sub> initiates the write operations.

- 4. Refer to Table 6 for valid DIN during a write operation.

**Table 3. Sector Protection Verify Electronic ID Codes**

|        | TYPE              |      |                | A6  | A1  | A0  | Code (Hex) |

|--------|-------------------|------|----------------|-----|-----|-----|------------|

| Ma     | Manufacturer Code |      | Х              | VIL | VIL | VIL | ADH        |

|        | 29F400T           | Byte | X              | VIL | VIL | VIH | 23H        |

| 29F400 |                   | Word |                |     |     |     | 22,23H     |

|        | 29F400B           | Byte | X              | VIL | VIL | VIH | ABH        |

|        |                   | Word |                |     |     |     | 22 ABH     |

| S      | ector Protection  |      | Sector Address | VIL | VIH | VIL | 01H(1)     |

Note: Outputs 01H at protected sector addresses, and outputs 00H at unprotected addresses.

Table 4. Sector Address Tables (BM29F400T)

|      | A17 | A16 | A15 | A14 | A13 | A12 | (x8) Address Range | (x16) Address Range |

|------|-----|-----|-----|-----|-----|-----|--------------------|---------------------|

| SA0  | 0   | 0   | 0   | Х   | Х   | Х   | 00000H-0FFFFH      | 00000H-07FFFH       |

| SA1  | 0   | 0   | 1   | Х   | Х   | Х   | 10000H-1FFFFH      | 08000H-0FFFFH       |

| SA2  | 0   | 1   | 0   | Х   | Х   | Х   | 20000H-2FFFFH      | 10000H-17FFFH       |

| SA3  | 0   | 1   | 1   | Х   | Х   | Х   | 30000H-3FFFFH      | 18000H-1FFFFH       |

| SA4  | 1   | 0   | 0   | Х   | Х   | Х   | 40000H-4FFFFH      | 20000H-27FFFH       |

| SA5  | 1   | 0   | 1   | X   | X   | Х   | 50000H-5FFFFH      | 28000H-2FFFFH       |

| SA6  | 1   | 1   | 0   | Х   | Х   | Х   | 60000H-6FFFFH      | 30000H-37FFFH       |

| SA7  | 1   | 1   | 1   | 0   | X   | Х   | 70000H-77FFFH      | 38000H-3BFFFH       |

| SA8  | 1   | 1   | 1   | 1   | 0   | 0   | 78000H-79FFFH      | 3C000H-3CFFFH       |

| SA9  | 1   | 1   | 1   | 1   | 0   | 1   | 7A000H-7BFFFH      | 3D000H-3DFFFH       |

| SA10 | 1   | 1   | 1   | 1   | 1   | Х   | 7C000H-7FFFFH      | 3E000H-3FFFFH       |

Notes:

Table 5. Sector Address Tables (BM29F400B)

|      | A17 | A16 | A15 | A14 | A13 | A12 | (x8) Address Range | x16) Address Range |

|------|-----|-----|-----|-----|-----|-----|--------------------|--------------------|

| SA0  | 0   | 0   | 0   | 0   | 0   | X   | 00000H-03FFFH      | 00000H-01FFFH      |

| SA1  | 0   | 0   | 0   | 0   | 1   | 0   | 04000H-05FFFH      | 02000H-02FFFH      |

| SA2  | 0   | 0   | 0   | 0   | 1   | 1   | 06000H-07FFFH      | 03000H-03FFFH      |

| SA3  | 0   | 0   | 0   | 1   | Х   | X   | 08000H-0FFFFH      | 04000H-07FFFH      |

| SA4  | 0   | 0   | 1   | Х   | Х   | X   | 10000H-1FFFFH      | 08000H-0FFFFH      |

| SA5  | 0   | 1   | 0   | Х   | Х   | X   | 20000H-2FFFFH      | 10000H-17FFFH      |

| SA6  | 0   | 1   | 1   | Х   | Х   | X   | 30000H-3FFFFH      | 18000H-1FFFFH      |

| SA7  | 1   | 0   | 0   | Х   | Х   | X   | 40000H-4FFFFH      | 20000H-27FFFH      |

| SA8  | 1   | 0   | 1   | Х   | Х   | X   | 50000H-5FFFFH      | 28000H-2FFFFH      |

| SA9  | 1   | 1   | 0   | Х   | X   | X   | 60000H-6FFFFH      | 30000H-37FFFH      |

| SA10 | 1   | 1   | 1   | Χ   | Χ   | Х   | 70000H-7FFFFH      | 38000H-3FFFFH      |

<sup>1.</sup> The address range is A17:A-1 if in byte mode ( $\overline{\text{BYTE}} = \text{V}_{\text{IL}}$ ).

<sup>2.</sup> The address range is A17:A0, if in word mode ( $\overline{BYTE} = VIH$ ).

<sup>1.</sup> The address range is A17:A-1 if in byte mode ( $\overline{\text{BYTE}} = \text{V}_{\text{IL}}$ ).

<sup>2.</sup> The address range is A17:A0, if in word mode (  $\overline{\text{BYTE}} = \text{V}_{\text{IH}}$ ).

## BRIGHT Microelectronics Inc

#### **Electronic ID Mode**

The Electronic ID mode allows the reading out of a binary code from the device and will identify its manufacturer and device type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional over the entire temperature range of the device.

To activate this mode, the programming equipment must force VID (11.5V to 12.5V) on address pin A9. Two identifier bytes may then be sequenced from the device outputs by toggling address A0 from VIL to VIH. All addresses are don't cares except A0, A1, and A6 (see Table 3).

Manufacturer and device codes may also be read via the command register; for instance, when the BM29F400 is erased or programmed in a system without access to high voltage on the A9 pin. The command sequence is illustrated in Table 6 (refer to Electronic ID Command section).

Byte 0 (A0 = VIL) represents the manufacturer's code (Bright Microelectronics = ADH) and byte 1 (A0 = VIH) the device identifier code (BM29F400T = 23H and BM29F400B = ABH for 8-bit mode; BM29F400T = 2223H and BM29F400B = 22ABH for 16-bit mode). These two byte words are given in Table 3. To read the proper device codes when executing the Electronic ID, all identifiers for manufacturer and device will exhibit odd parity with the MSB (DQ7) defined as the parity bit. A1 must be VIL (see Table 3).

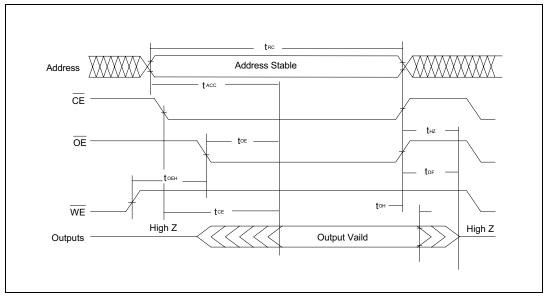

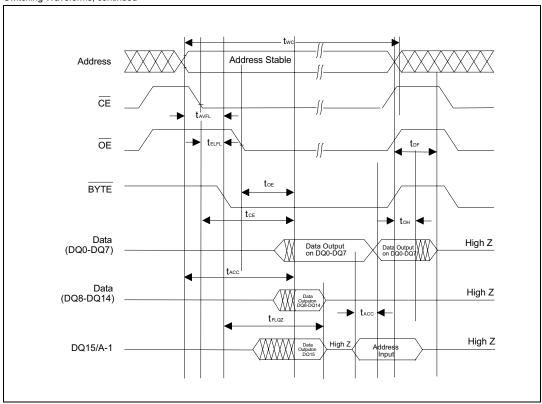

#### Read Mode

The BM29F400 has three control functions which must be satisfied in order to obtain data at the outputs.  $\overline{CE}$  is the power control and should be used for device selection.  $\overline{OE}$  is the output control and should be used to gate data to the output pins if a device is selected. As shown in Table 1,  $\overline{WE}$  should be held at VIH, except in Write mode and Enable Sector Protect mode.

Address access time ( $t_{ACC}$ ) is equal to the delay from stable addresses to valid output data. Chip enable access time ( $t_{CE}$ ) is the delay from stable addresses and stable  $\overline{CE}$  to valid data at the output pins. Output enable access time is the delay from the falling edge of  $\overline{OE}$  to valid data at the output pins (assuming the addresses have been stable for at least  $t_{ACC}$ – $t_{OE}$  time).

## Standby Mode and Hardware RESET Standby Mode

The BM29F400 has two methods for implementing standby mode. The first method requires use of both the  $\overline{\text{CE}}$  pin and the  $\overline{\text{RESET}}$  pin. The second method only requires use of the  $\overline{\text{RESET}}$  pin.

When using both pins, a CMOS standby mode is achieved when both  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  are held at Vcc  $\pm 0.5$ V. In this condition, the current consumed is typically less than 100  $\mu$ A. A TTL standby mode is achieved with both  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  held at ViH. In this condition, the typical current required is reduced to 200  $\mu$ A. The device can be read with standard access time (t<sub>CE</sub>) from either of these two standby modes.

When using the  $\overline{\text{RESET}}$  pin only, a CMOS standby mode is achieved with  $\overline{\text{RESET}}$  held at Vss  $\pm 0.5$ V. In this condition, the current consumed is typically less than 100  $\mu$ A. A TTL standby mode is achieved with  $\overline{\text{RESET}}$  held at VIL. In this condition, the typical current required is reduced to 1 mA. Once the  $\overline{\text{RESET}}$  pin is taken high, the device requires 500 nS of wake-up time before outputs are valid for a read access.

## BM29F400T/BM29F400B

If the device is deselected during programming or erase, the device will draw active current until the programming or erase operation is completed. In the standby mode the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

#### **Output Disable Mode**

With the  $\overline{OE}$  input at a logic high level (VIH), output from the device is disabled. This will cause the output pins to be in a high impedance state. It is shown in Table 1 that  $\overline{CE} = VIL$  and  $\overline{WE} = VIH$  for Output Disable. This is to differentiate Output Disable mode from Write mode and to prevent inadvertent writes during Output Disable.

### **Program and Erase Modes**

Device programming and erase are accomplished via the command register. Contents of the register serve as inputs to the internal state machine. Outputs of the state machine dictate the function of the device.

The command register itself does not occupy any addressable memory locations. The register is a latch used to store the commands along with the addresses and data information needed to execute the command. The command register is written by bringing  $\overline{WE}$  to VIL, while  $\overline{CE}$  is at VIL and  $\overline{OE}$  is at VIH. Addresses are latched on the falling edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever happens later, while data is latched on the rising edge of  $\overline{WE}$  or  $\overline{CE}$ , whichever happens first. Standard microprocessor write timings are used. Refer to AC Characteristics for Programming/Erase and their respective Timing Waveforms for specific timing parameters.

## **Enable Sector Protect and Verify Sector Protect Modes**

The BM29F400 has a hardware Sector Protect mode that disables both Programming and Erase operation to the protected sector(s). There are total of 11 sectors in this device. The sector protect feature is enabled using the programming equipment at the user's site. The device is shipped from the BMI factory with all sectors unprotected.

To verify programming of the protection circuitry, the programming equipment must force VID on the address pin A9 with  $\overline{CE}$  and  $\overline{OE}$  at VIL and  $\overline{WE}$  at VIH. As shown in Table 2, scanning the sector addresses while (A6, A1 and A0) = (0, 1, 0) will produce a 01H code at the device output pins for a protected sector. In the Verify Sector Protect mode, the device will read 00H for an unprotected sector. In this mode, the lower order addresses, except for A0, A1 and A6, are don't care. Address locations with A1 = VIL are reserved for Electronic ID manufacturer and device codes. It is also possible to determine if a sector is protected in-system by writing the Electronic ID command (described in the Electronic ID command section below.)

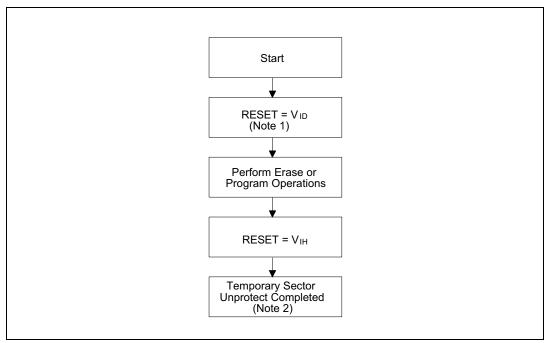

#### **Temporary Sector Unprotect Mode**

The BM29F400 has a Temporary Sector Unprotect feature that allows the protect feature to be temporarily suspended to change data in a protected sector in-system. The Temporary Sector Unprotect mode is activated by setting the RESET pin to VID (11.5V–12.5V).

In this mode, protected sectors can be programmed or erased by selecting the sector addresses. Once VID is removed from the RESET pin, all previously protected sectors will be protected. Refer to the Temporary Sector Unprotect algorithm and timing waveforms.

## BRIGHT Microelectronics Inc

#### Read RESET Command

The read or RESET operation is initiated by writing the Read/Reset command sequence in to the command register. Microprocessor read cycles retrieve the data from the memory. The device remains enable for reads until the command register contents are changed.

The device will automatically power-up in the Read/Reset mode. In this case, a command sequence is not needed to read the memory data. This default power-up to Read mode ensures that no spurious changes of the data can take place during the power transitions. Refer to the AC Characteristics for Read-Only Operation and the respective Timing Waveforms for the specific timing parameters.

#### **Electronic ID Command**

The BM29F400 contains an Electronic ID command to supplement the traditional PROM programming method described in the Electronic ID Mode section. The operation is initiated by writing the Electronic ID command sequence into the command register. Following command write, a read cycle from address XX00H retrieves manufacturer code of ADH. A read cycle from address XX01H returns the device code (BM29F400T = 23H and BM29F400B = ABH for 8-bit mode; BM29F400T = 2223H and BM29F400B = 22ABH for 16-bit mode) (see Table 3). All manufacturer and device codes exhibit odd parity with the MSB (DQ7) defined as the parity bit.

The Electronic ID command can also be used to identify protected sectors. After writing the Electronic ID command sequence, the CPU can scan the sector addresses (see Table 4 and Table 5) while (A6, A1, A0) = (0, 1, 0). Protected sectors will return 01H on the data outputs and unprotected sectors will return 00H. To terminate the operation, it is necessary to write the Read/Reset command sequence into the command register.

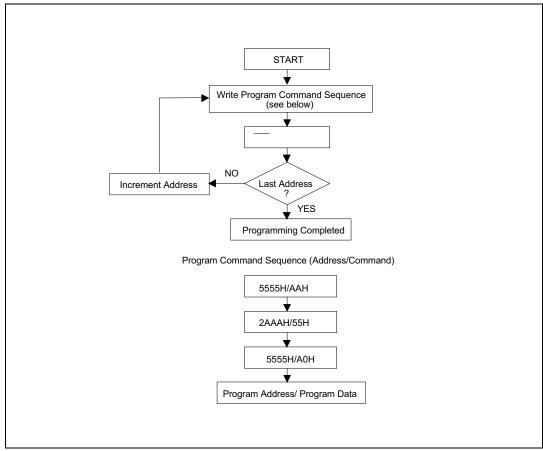

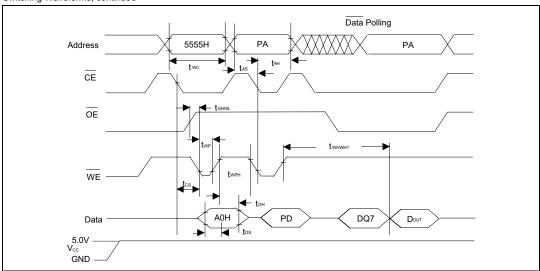

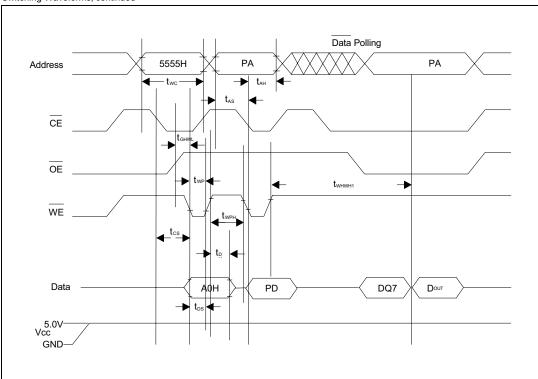

### **Byte/Word Programming Command**

The device is programmed on a byte-by-byte (or word-by-word) basis. Programming is a four bus cycle operation (see Table 6). There are two "unlock" write cycles. These are followed by the program set-up command and data write cycles. Addresses are latched on the falling edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever happens later, and program data (PD) is latched on the rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever happens first. The rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever happens first, begins programming using the Embedded Program Algorithm.

Upon executing the algorithm, the system is not required to provide further controls or timings. The device will automatically provide adequate internally generated program pulses and verify the programmed cell margin.

The automatic programming operation is completed when the data on DQ7 (also used as  $\overline{\text{Data}}$  Polling) is equivalent to the data written to this bit at which time the device returns to the read mode and addresses are no longer latched (see Table 7, Write Operation Status Flags). Therefore, the device requires that a valid address to the device be supplied by the system at this particular instance of time for  $\overline{\text{Data}}$  Polling operations.  $\overline{\text{Data}}$  Polling must be performed at the memory location which is being programmed.

Any commands written to the chip during the Internal Program Algorithm will be ignored. If a hardware RESET occurs during the programming operation, the data at that particular location will be corrupted.

## BM29F400T/BM29F400B

Byte/Word programming is allowed in any sequence, and across sector boundaries. However, remember that a data "0" cannot be programmed to a data "1". Only erase operations can convert a logical "0" to a logical "1". Attempting to program data from "0" to "1" may cause the device to exceed time limits, or even worse, result in an apparent success according to the Data Polling algorithm. In the later case, however, a subsequent read of this bit will show that the data is still a logical "0".

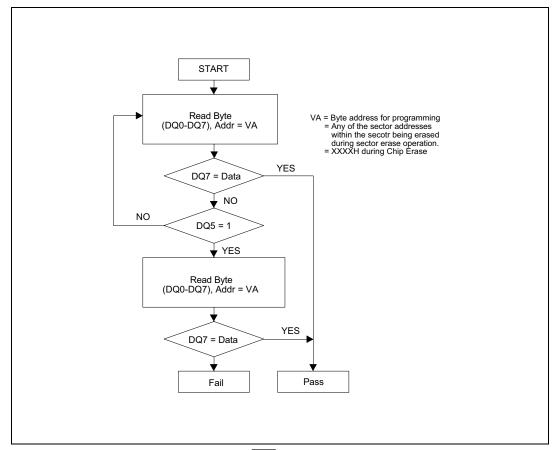

Figure 1 illustrates the Byte/Word Programming Algorithm using typical command strings and bus operations.

The device will ignore any commands written to the chip during execution of the internal Byte/Word Programming Algorithm. If a hardware RESET occurs during the Byte/Word Programming operation, the data at that particular address location will be corrupted.

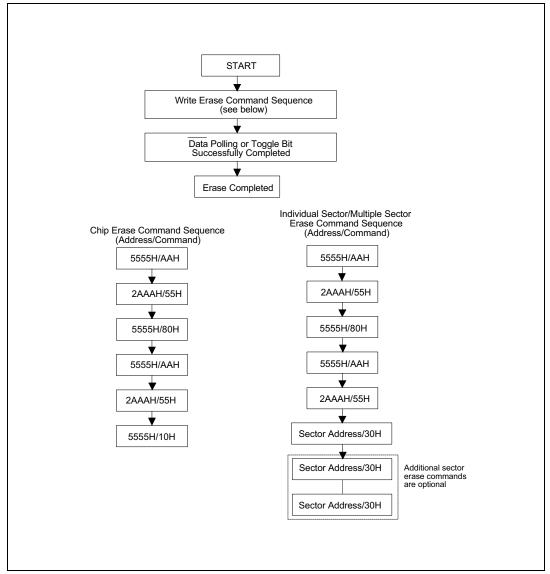

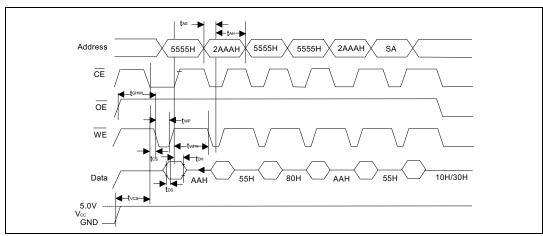

## **Chip Erase Command**

Chip erase is a six bus cycle operation (see Table 6). The chip erase begins on the rising edge of the last  $\overline{\text{WE}}$  pulse in the command sequence.

Upon executing the Chip Erase command sequence, the device's internal state machine executes an internal erase algorithm. The system is not required to provide further controls or timings. The device will automatically provide adequate internally generated erase pulses and verify chip erase within the proper cell margins. During chip erase, all sectors of the device are erased except protected sectors.

During Chip Erase, data bit DQ7 shows a logical "0". This operation is known as Data Polling. The erase operation is completed when the data on DQ7 is a logical "1" (see Write Operation Status section). Upon completion of the Chip Erase operation, the device returns to read mode. At this time, the address pins are no longer latched. Note that Data Polling must be performed at a sector address within any of the sectors being erased and not a protected sector to ensure that DQ7 returns a logical "1" upon completion of the Chip Erase operation.

Figure 2 illustrates the Chip Erase Algorithm using typical command strings and bus operations.

The device will ignore any commands written to the chip during execution of the internal Chip Erase algorithm. If a hardware  $\overline{\mathsf{RESET}}$  occurs during the Chip Erase operation, the data in the device will be corrupted.

#### **Sector Erase Command**

Sector erase is a six bus cycle operation (see Table 6). The sector address (any address location within the desired sector) is latched on the falling edge of  $\overline{WE}$ , while the command data is latched on the rising edge of  $\overline{WE}$ . An internal device timer will initiate the Sector Erase operation 100  $\mu$ S  $\pm$ 20% (80  $\mu$ S to 120  $\mu$ S) from the rising edge of the  $\overline{WE}$  pulse for the last Sector Erase command entered on the device.

Upon executing the Sector Erase command sequence, the device's internal state machine executes an internal erase algorithm. The system is not required to provide further controls or timings. The device automatically provides adequate internally generated erase pulses and verify sector erase within the proper cell margins. Protected sectors of the device will not be erased, even if they are selected with the Sector Erase command.

Revision A2

## BM29F400T/BM29F400B

Multiple sectors can be erased simultaneously by writing the sixth bus cycle command of the Sector Erase command for each sector to be erased. The time between initiation of the next Sector Erase command must be less than 80  $\mu S$  to guarantee acceptance of the command by the internal state machine. The time-out window can be monitored via the write operation status pin DQ3 (refer to the Write Operation Status section for Sector Erase Timer operation). It is recommended that CPU interrupts be disabled during this time to ensure that the subsequent Sector Erase commands can be initiated within the 100  $\mu S$  window. The interrupts can be re-enabled after the last Sector Erase command is written. As mentioned above, an internal device timer will initiate the Sector Erase operation 100  $\mu S$  ±20% (80  $\mu S$  to 120  $\mu S$ ) from the rising edge of the last  $\overline{WE}$  pulse. Sector Erase Timer Write Operation Status pin (DQ3) can be used to monitor time out window. If another falling edge of the  $\overline{WE}$  occurs within the 100 mS time-out window, the internal device timer is reset. Loading the sector erase buffer may be done in any sequence and with any number of sectors.

Any command other than Sector Erase or Erase Suspend during this period and afterwards will  $\overline{\text{RESET}}$  the device to read mode, ignoring the previous command string. Resetting the device with a hardware  $\overline{\text{RESET}}$  after it has begun execution of a Sector Erase operation will result in the data in the operated sectors being undefined and may be unrecoverable. In this case, restart the Sector Erase operation on those sectors and attempt to allow them to complete the Erase operation.

#### **Command Definitions**

Device operations are selected by writing specific address and data sequences in to the Command register. Writing incorrect addresses and data values or writing them in the improper sequence will RESET the device to Read mode. Table 5 defines the valid register command sequences. Either of the two Read/Reset commands will RESET the device (when applicable).

During Sector Erase operation, data bit DQ7 shows a logical "0". This operation is known as Data Polling. Sector Erase operation is complete when data on DQ7 is a logical "1" (see Write Operation Status section) at which time the device returns to read mode. At this time, the address pins are no longer latched. Note that Data Polling must be performed at a sector address within any of the sectors being erased and not a protected sector to ensure that DQ7 returns a logical "1" upon completion of the Sector Erase operation.

Figure 2 illustrates the Sector Erase Algorithm using typical command strings and bus operations.

During execution of the Sector Erase command, only the Erase Suspend and Erase Resume commands are allowed. All other commands will RESET the device to read mode.

Note: Do not attempt to write an invalid command sequence during the sector erase operation. Doing so will terminate the sector erase operation and the device will /RESET to the read mode.

#### **Table 6. Command Definitions**

|            | mand<br>ience | Bus Write<br>Cycles |       | us Write |       | nd Bus<br>Cycle |       | d Bus<br>Cycle |                    | Bus Write<br>Cycle                               |       | lus Write<br>ycle |       | sus Write<br>ycle |

|------------|---------------|---------------------|-------|----------|-------|-----------------|-------|----------------|--------------------|--------------------------------------------------|-------|-------------------|-------|-------------------|

| Reset      | /Read         | Required            | Addr. | Data     | Addr. | Data            | Addr. | Data           | Addr.              | Data                                             | Addr. | Data              | Addr. | Data              |

| Reset      | t/Read        | 1                   | XXXXH | F0H      |       |                 |       |                |                    |                                                  |       |                   |       |                   |

| Reset      | Word          | 4                   | 5555H | AAH      | 2AAAH | 55H             | 5555H | F0H            | RA                 | RD                                               |       |                   |       |                   |

| /Read      | Byte          |                     | AAAAH |          | 5555H |                 | AAAAH |                |                    |                                                  |       |                   |       |                   |

| Electronic | Word          | 4                   | 5555H | AAH      | 2AAAH | 55H             | 5555H | 90H            | 01H <sup>(7)</sup> | 2223H<br>(T Device ID)<br>22ABH<br>(B Device ID) |       |                   |       |                   |

| ID         | Byte          |                     | AAAAH |          | 5555H |                 | AAAAH |                |                    | 23H<br>(T Device ID)<br>ABH<br>(B Device ID)     |       |                   |       |                   |

| Program    | Word          | 4                   | 5555H | AAH      | 2AAAH | 55H             | 5555H | A0H            | PA                 | PD                                               |       |                   |       |                   |

|            | Byte          |                     | AAAAH |          | 5555H |                 | AAAAH |                |                    |                                                  |       |                   |       |                   |

| Chip       | Word          | 6                   | 5555H | AAH      | 2AAAH | 55H             | 5555H | 80H            | 5555H              | AAH                                              | 2AAAH | 55H               | 5555H | 10H               |

| Erase      | Byte          |                     | AAAAH |          | 5555H |                 | AAAAH |                | AAAAH              |                                                  | 5555H |                   | AAAAH |                   |

| Sector     | Word          | 6                   | 5555H | AAH      | 2AAAH | 55H             | 5555H | 80H            | 5555H              | AAH                                              | 2AAAH | 55H               | SA    | 30H               |

| Erase      | Byte          |                     | AAAAH |          | 5555H |                 | AAAAH |                | AAAAH              |                                                  | 5555H |                   |       |                   |

| Erase      | Word          | 1                   | XXXXH | вон      |       |                 |       |                |                    |                                                  |       |                   |       |                   |

| Suspend    | Byte          |                     |       |          |       |                 |       |                |                    |                                                  |       |                   |       |                   |

| Erase      | Word          | 1                   | XXXXH | 30H      |       |                 |       |                |                    |                                                  |       |                   |       |                   |

| Resume     | Byte          |                     |       |          |       |                 |       |                |                    |                                                  |       |                   |       |                   |

#### Notes

- 1. Bus operations are defined in Tables 1 and 2.

- 2. For a Command Sequence, address bit A15 = X = Don't Care for all address commands except for Program Address (PA) and Sector Address (SA).

- 3. RA = Address of the memory location to be read.

- RD = Data read from location RA during read operation.

- PA = Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE pulse.

- PD = Data to be programmed at location PA. Data is latched on the rising edge of WE.

- SA = Address of sector to be erased. (See Table 4 for top boot and Table 5 for bottom boot.)

- 4. The Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress.

- 5. Reading from, and programming to, non-erasing sectors is allowed in the Erase Suspend mode.

- 6. The System should generate the following address patterns: Word Mode: 5555H or 2AAAH to addresses A0–A14. Byte Mode: AAAAH or 5555H to addresses A-1–A14.

- 7. Address 00H returns the manufacturer's ID code (Bright Microelectronics ADH), address 01H returns the device ID code.

#### Erase Suspend/Erase Resume Commands

The Erase Suspend command allows the user to interrupt a Sector Erase operation and read data from or to a sector that is not being erased. The Erase Suspend command is applicable only during Sector Erase operation, including, but not limited to, sector erase time-out period after any Sector Erase commands (30H) have been initiated.

## BM29F400T/BM29F400B

Writing the Erase Suspend command during the time-out will result in immediate termination of the time-out period. Any subsequent writes of the Sector Erase command will be taken as the Erase Resume command (30H). Note that any other commands during the time-out will  $\overline{\text{RESET}}$  the device to the Read mode. The address pins are "don't cares" when writing the Erase Suspend or Erase Resume commands.

When the Erase Suspend command is written during a Sector Erase operation, the chip will take between 1  $\mu$ S and 230  $\mu$ S to suspend the erase operation and go into Erase Suspended mode. During this time, the system can monitor the  $\overline{Data}$  Polling or Toggle Bit write operation status flags to determine when the device has entered erase suspend mode (see Write Operation Status section.) The system must use an address of an erasing sector to monitor  $\overline{Data}$  Polling or Toggle Bit to determine if the Sector Erase operation has been suspended.

In Erase Suspend mode, the system can read data from any sector that is not being erased. A read from a sector being erased will result in write operation status data. After the system writes the Erase Suspend command and waits until the Toggle Bit stops toggling, data reads from the device may then be performed (see Write Operation Status section). Any further writes of the Erase Suspend command at this time will be ignored.

To resume operation of Sector Erase, the Erase Resume command (30H) should be written. Any further writes of the Erase Resume command at this point will be ignored. Another Erase Suspend command can be written after the chip has resumed Sector Erase operation.

## DQ7

## Data Polling

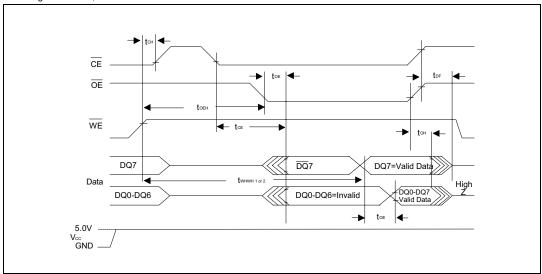

The BM29F400 device features Data Polling as a method to indicate to the host the status of the Byte/Word Programming, Chip Erase, and Sector Erase operations. When the Byte/Word Programming operation is in progress, an attempt to read the device will produce the compliment of the data last written to DQ7. Upon completion of the Byte/Word Programming operation, an attempt to read the device will produce the true data last written to DQ7. When the Chip Erase or Sector Erase operation is in progress, an attempt to read the device will produce a logical "0" at the DQ7 output. Upon completion of the Chip Erase or Sector Erase operation, an attempt to read the device will produce a logical "1" at the DQ7 output. The flowchart for Data Polling (DQ7) is shown in Figure 3.

For Chip Erase, the  $\overline{\text{Data}}$  Polling is valid after the rising edge of the sixth  $\overline{\text{WE}}$  pulse in the six write pulse sequence. For Sector Erase, the  $\overline{\text{Data}}$  Polling is valid after the last rising edge of the sector erase  $\overline{\text{WE}}$  pulse. For both Chip Erase and Sector Erase,  $\overline{\text{Data}}$  Polling must be performed at sector address within any of the sectors being erased and not a protected sector. Otherwise, the  $\overline{\text{Data}}$  Polling status may not be valid. Once the Internal Algorithm operation is close to being completed, the BM29F400 data pins (DQ7) may change asynchronously while the output enable ( $\overline{\text{OE}}$ ) is asserted low. This means that the device is driving status information on DQ7 at one instant and valid data at the next instant of time. Depending on when the system samples the DQ7 output, it may read status or valid data. Even if the device has completed the Internal Algorithm operation and DQ7 has a valid data, data outputs on DQ0-DQ6 may be still invalid. Valid data on DQ0-DQ7 will be read on the successive read attempts.

## BM29F400T/BM29F400B

The Data Polling feature is only active during the Byte/Word Programming operation, Chip Erase operation, Sector Erase Operation, or Sector Erase time-out window (see Table 7).

#### DQ6

## **Toggle Bit**

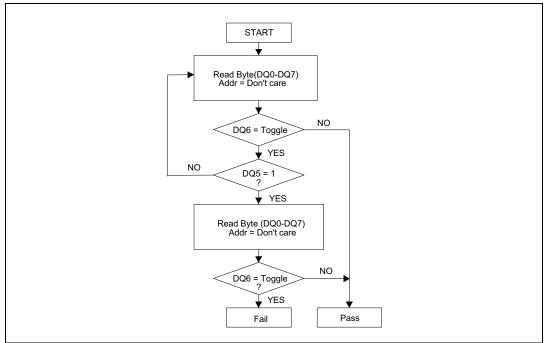

The BM29F400 also features the "Toggle Bit" as a method to indicate to the host system the status of the Internal Programming and Erase Algorithms (see Figure 4 for Toggle Bit (DQ6) flowchart.

During an Internal Programming or Erase Algorithm cycle, successive attempts to read ( $\overline{OE}$  toggling) data from the device will result in DQ6 toggling between one and zero. Once Internal Programming or Erase operation is completed, DQ6 will stop toggling and valid data will be read on the next successive attempts. During  $\overline{BYTE}$  Programming, Toggle Bit is valid after the rising edge of the fourth  $\overline{WE}$  pulse in the four write pulse sequence. For Chip Erase, Toggle Bit is valid after the rising edge of the sixth  $\overline{WE}$  pulse in the six write pulse sequence. For Sector Erase, Toggle Bit is valid after the last rising edge of the sector erase  $\overline{WE}$  pulse. Toggle Bit is also active during sector erase time-out window.

In Byte/Word Programming, if the sector being written to is protected, the Toggle Bit will toggle for about 300 nS and then stop toggling without the data having changed. In Chip Erase or Sector Erase, the device will erase all the selected sectors except for the ones that are protected. If all selected sectors are protected, the chip will toggle the Toggle Bit for about 300 nS and then drop back into read mode, having changed none of the data. Either  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  toggling will cause the DQ6 Toggle Bit I to toggle.

### DQ5

#### **Exceeded Timing Limits**

DQ5 will indicate if the Byte/Word Programming, Chip Erase, or Sector Erase time has exceeded the specified limits (internal pulse count) of the device. Under these conditions DQ5 will produce a logical "1". This is a failure condition which indicates that the program or erase cycle was not successfully completed.  $\overline{\text{Data}}$  Polling is the only operating function of the device under this condition. The  $\overline{\text{OE}}$  and  $\overline{\text{WE}}$  pins will control the output disable functions as described in Table 1.

If this failure condition occurs during Sector Erase operation, it specifies that particular sector is bad and it may not be reused. However, other sectors are still functional and may continue to be used for the program or erase operation. The device must be  $\overline{\text{RESET}}$  to the Read mode to use other sectors of the device. Write the Read/Reset command sequence to the device, and then execute the Byte/Word Programming or Sector Erase command sequence. This allows the system to continue to use the other active sectors in the device.

If this failure condition occurs during Chip Erase operation, it specifies that the entire chip is bad or combination of sectors are bad. In so, the chip should not be reused.

If this failure condition occurs during Byte/Word Programming operation, it indicates the entire sector containing that  $\overline{\text{BYTE}}$  is bad and this sector may not be reused (other sectors are still functional and can be reused.)

The DQ5 failure condition may also appear if a user tries to program a non blank location without erasing. In this case, the device may exceed time limits and not complete the Internal Algorithm operation. Hence, the system never reads a valid data on DQ7 bit and DQ6 never stops toggling. Once the device has exceeded timing limits, the DQ5 bit will indicate a "1".

#### DQ3

#### **Sector Erase Timer**

After the completion of the initial Sector Erase command sequence, the sector erase time-out window will begin. DQ3 will remain low until the time-out window is closed. Data Polling and Toggle Bit are valid after the initial Sector Erase command sequence.

If Data Polling or the Toggle Bit indicates the device has been written with a valid erase command, DQ3 maybe used to determine if the Sector Erase time-out window is still open. If DQ3 is a logical "1", the internally controlled erase cycle has begun. Attempts to write subsequent command to the device will be ignored until the erase operation is completed as indicated by Data Polling or Toggle Bit. If DQ3 is a logical "0", the device will accept additional Sector Erase commands. To ensure the command has been accepted, the system software should check the status of DQ3 prior to and following each subsequent Sector Erase command. If DQ3 were high on the second status check, the command may not have been accepted. Refer to Table 7: Write Operation Status Flags.

### **Write Operations Status**

|             | STATUS                                             | DQ7  | DQ6    | DQ5  | DQ3  |

|-------------|----------------------------------------------------|------|--------|------|------|

| In          | Byte/Word Programming Operation                    | DQ7  | Toggle | 0    | N/A  |

| Progress    | Chip or Sector Erase Operation                     | 0    | Toggle | 0    | 1    |

|             | Erase Suspend Mode<br>(Non-Erase Suspended Sector) | Data | Data   | Data | Data |

| Exceeded    | Byte/Word Programming Operation                    | DQ7  | Toggle | 1    | 0    |

| Time Limits | Chip or Sector Erase Operation                     | 0    | Toggle | 1    | 1    |

Table 7. Write Operation Status Flags<sup>(1)</sup>

Notes: DQ0, DQ1, DQ4 are reserve pins for future use.

## RY/BY

## Ready/Busy Status

The BM29F400 provides a RY/BY open-drain output pin as a way to indicate to the host system that an Internal Programming or Erase operation is either in progress or has been completed. If the RY/BY output is low, the device is busy with either a Programming or Erase operation. If the RY/BY output is high, the device is ready to accept a Read, Programming, or Erase command. When the RY/BY pin is low, the device will not accept any additional Programming or Erase commands with the exception of the Erase Suspend command. If the BM29F400 is placed in an Erase Suspend mode, the RY/BY output will be high.

## BM29F400T/BM29F400B

During a programming operation, the RY/BY pin is driven low after the rising edge of the fourth  $\overline{\text{WE}}$  pulse. During an erase operation, the RY/BY pin is driven low after the rising edge of the sixth  $\overline{\text{WE}}$  pulse. The RY/BY pin will indicate a busy condition during the  $\overline{\text{RESET}}$  pulse. Refer to the timing waveforms for the RY/BY status pin for further clarification. The RY/BY pin is high in the Standby mode.

Since this is an open-drain output, several RY/BY pins can be tied together with a pull-up resistor to Vcc.

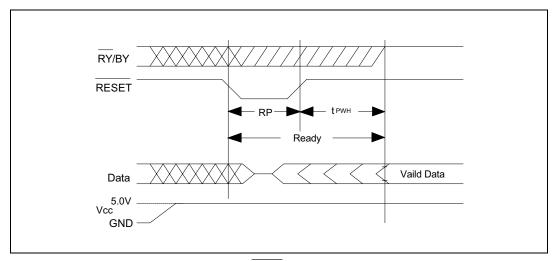

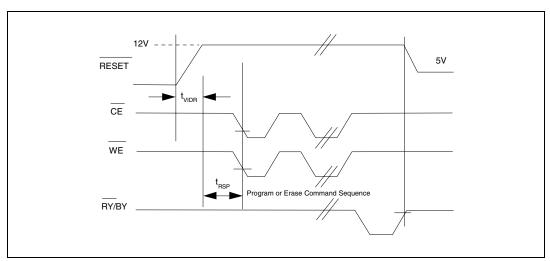

#### **RESET Hardware Reset**

The BM29F400 device may be  $\overline{\text{RESET}}$  by driving the  $\overline{\text{RESET}}$  pin to VIL. The  $\overline{\text{RESET}}$  pin must be kept low (VIL) for at least 500 nS. Pulling the  $\overline{\text{RESET}}$  pin low will terminate any operation in progress. The internal state machine will be  $\overline{\text{RESET}}$  to the read mode 1 mS to 230 mS after the  $\overline{\text{RESET}}$  pin is driven low. If a hardware  $\overline{\text{RESET}}$  occurs during a Programming or Erase operation, the data at that particular location will be indeterminate.

When the RESET pin is low and the internal RESET is complete, the device goes to Standby mode and cannot be accessed. Also, note that all the data output pins are tri-stated for the duration of the RESET pulse. Once the RESET pin is taken high, the device requires 500 nS of wake up time until outputs are valid for a read access.

The RESET pin may be tied to the system RESET input. Therefore, if a system  $\frac{RESET}{RESET}$  occurs during an Internal Programming or Erase operation, the device will be automatically  $\frac{RESET}{RESET}$  to read mode. This will enable the system's microprocessor to read the boot-up firmware from the Flag's memory.

#### **Data Protection**

The BM29F400 is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transitions. During power-up the device automatically resets the internal state machine in the Read mode. Also, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific multi-bus cycle command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from Vcc power-up and power-down transitions or system noise.

#### Low Vcc Write Inhibit

To avoid initiation of a write cycle during Vcc power-up and power-down, a write cycle is locked out for Vcc less than 3.2V (typically 3.7V). If Vcc < VLKO, the command register is disabled and all internal programming/erase circuits are disabled. Under this condition the device will  $\overline{\text{RESET}}$  to the Read mode. Subsequent writes will be ignored until the Vcc level is greater than VLKO. It is the users responsibility to ensure that the control pins are logically correct to prevent unintentional writes when Vcc is above 3.2V.

### Write Pulse "Glitch" Protection

Noise pulses of less than 5 nS (typical) on  $\overline{OE}$ ,  $\overline{CE}$  or  $\overline{WE}$  will not initiate a write cycle.

## **Logical Inhibit**

Writing is inhibited by holding any one of  $\overline{OE} = VIL$ ,  $\overline{CE} = VIH$ , or  $\overline{WE} = VIH$ . To initiate a write cycle  $\overline{CE}$  and  $\overline{WE}$  must be a logical "0" while  $\overline{OE}$  is a logical "1".

## **Power-up Write Inhibit**

Power-up of the device with  $\overline{WE} = \overline{CE} = VIL$  and  $\overline{OE} = VIH$  will not accept commands on the rising edge of  $\overline{WE}$ . The internal state machine is automatically  $\overline{RESET}$  to the Read mode on power-up.

## **Sector Unprotect**

The BM29F400 also features a sector unprotect mode, so that protected sectors may be unprotected to incorporate any changes in the code. Protecting all sectors is necessary before unprotecting any sector(s). Sector unprotection is accomplished in a PROM programmer.

Figure 1. Internal Programming Algorithm

Figure 2. Internal Erase Algorithm

Figure 3. Data Polling Algorithm

Notes: DQ7 is rechecked even if DQ5 = logical "1" because DQ7 may change simultaneously with DQ5.

Figure 4. Toggle Bit Algorithm

Note: DQ6 is rechecked even if DQ5 = logical "1" because DQ6 may stop toggling at the same time as DQ5 changing to a logical "1".

## **Absolute Maximum Ratings**

| PARAMETER                             | RATING      | UNIT |

|---------------------------------------|-------------|------|

| Storage Temperature                   | -65 to +125 | °C   |

| Plastic Packages                      |             |      |

| Ambient Temperature                   | -55 to +125 | °C   |

| With Power Applied                    |             |      |

| Voltages with Respect to Ground       | -2 to +7    |      |

| All pins except A9 (Note 1)           | -2 to +7    | V    |

| Vcc (Note 1); A9 (Note 2)             | -2 to +14   |      |

| Output Short Circuit Current (Note 4) | 200         | mA   |

- Minimum DC voltage on input or I/O pins is -0.5V.

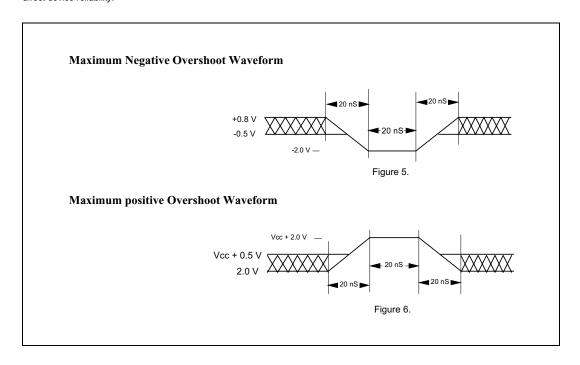

During voltage transitions, inputs may overshoot Vss to -2.0V for periods of up to 20 nS. Maximum DC voltage on output and I/O pins is Vcc +0.5V. During Voltage transitions, outputs may overshoot to Vcc +2.0V for periods up to 20 nS.

- 2. Minimum DC input voltage on A9 pin is -0.5V. During voltage transitions, A9 may overshoot Vss to -2.0V for periods of up to 20 nS. Maximum DC input voltage on A9 is +12.5V which may overshoot to 14.0V for periods of up to 20 nS.

- 3. No more than one output shorted at a time. Duration of the short circuit should not be greater than one second.

## **Operating Ranges**

| PARAMETER              | RATING      | UNIT |

|------------------------|-------------|------|

| Commercial (C) Devices | 0 to +70    | °C   |

| Extended (I) Devices   | -55 to +125 | °C   |

| Vcc Supply Voltage     | +4.5 to 5.5 | V    |

| Vcc for BM29F400-90    |             |      |

Note: Operating ranges define those limits between which the functionality of the device is guaranteed.

\*NoticeStresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC CHARACTERISTICS**

## **TTL/NMOS Compatible**

| PARAMETER                           | SYM.        | TEST CONDITIONS                      |        | MIN. | MAX.     | UNIT |

|-------------------------------------|-------------|--------------------------------------|--------|------|----------|------|

| Input Load Current                  | <b> </b> LI | VIN = Vss to VCC,<br>VCC = VCC Max.  |        |      | ±1.0     | μΑ   |

| A9 Input Load Current               | ILIT        | Vcc = Vcc Max.,<br>A9 = 12.5 V       |        |      | ±1.0     | μΑ   |

| Output Leakage Current              | llo         | VOUT = Vss to VCC,<br>VCC = VCC Max. |        |      | ±1.0     | μΑ   |

| Vcc Active Current <sup>(1)</sup>   | ICC1        | CE = VIL, OE = VIH                   | Byte   |      | 40       | mA   |

|                                     |             |                                      | Word   |      | 50       | mA   |

| VCC Active Current <sup>(2,3)</sup> | ICC2        | CE = VIL, OE = VIH                   |        |      | 60       | mA   |

| VCC Standby Current                 | ICC3        | Vcc = Vcc Max.,<br>CE = RESET = ViH  |        |      | 1.0      | mA   |

| Vcc Standby Current (RESET)         | ICC4        | Vcc = Vcc Max.,<br>RESET = VIL       |        |      | 1.0      | mA   |

| Input Low Level                     | VIL         |                                      |        | -0.5 | 0.8      | V    |

| Input High Level                    | VIH         |                                      |        | 2.0  | Vcc +0.5 | V    |

| Voltage for Electronic              | VID         | Vcc = 5.0V                           | 11.5   | 12.5 | V        |      |

| Output Low Voltage                  | Vol         | IOL = 5.8 mA, VCC = VCC              | Min.   |      | 0.45     | V    |

| Output High Voltage                 | Voн         | IOH = -2.5 mA, VCC = VCC             | C Min. | 2.4  |          | V    |

<sup>1.</sup> The Icc current listed includes both the DC operating current and the frequency dependent component (at 6 MHz).

The frequency component typically is less than 2 mA/MHz, with  $\overline{OE}$  at Viii.

<sup>2.</sup> Icc active while Internal Algorithm (program or erase) is in progress.

<sup>3.</sup> Not 100% tested.

## BM29F400T/BM29F400B

DC Characteristics, continued

## **CMOS Compatible**

| PARAMETER                                    | SYM.             | TEST CONDITIONS                      | MIN.               | MAX.     | UNIT |

|----------------------------------------------|------------------|--------------------------------------|--------------------|----------|------|

| Input Load Current                           | ILI              | VIN = Vss to Vcc, Vcc = Vcc Max.     |                    | ±1.0     | μΑ   |

| A9 Input Load Current                        | <b>I</b> LIT     | Vcc = Vcc Max., A9 = 12.5 V          |                    | ±1.0     | μΑ   |

| Output Leakage Current                       | llo              | VOUT = Vss to Vcc, Vcc = Vcc Max.    |                    | ±1.0     | μΑ   |

| Vcc Active Current <sup>(1)</sup>            | ICC1             | CE = VIL, OE = VIH                   | Byte               | 40       | mA   |

|                                              |                  |                                      | Word               | 50       | mA   |

| Vcc Active Current <sup>(2,3)</sup>          | ICC2             | CE = VIL, OE = VIH                   |                    | 60       | mA   |

| Vcc Standby Current                          | ICC3             |                                      |                    | 100      | μΑ   |

| Vcc Standby Current (RESET)                  | ICC4             | Vcc = Vcc Max.,<br>RESET = Vss ±0.5V |                    | 100      | μΑ   |

| Input Low Level                              | VIL              |                                      | -0.5               | 0.8      | V    |

| Input High Level                             | VIH              |                                      | 0.7 × Vcc          | Vcc +0.3 | V    |

| Voltage for Electronic ID and Sector Protect | VID              | Vcc = 5.0 V                          | 11.5               | 12.5     | V    |

| Output Low Voltage                           | Vol              | IOL = 5.8 mA, VCC = VCC Min.         |                    | 0.45     | V    |

| Output High Voltage                          | Vo <sub>H1</sub> | IOH = -2.5 mA, Vcc = Vcc Min.        | $0.85 \times V$ IH |          | V    |

|                                              | Vo <sub>H2</sub> | Іон = -100 mA, Vcc = Vcc Min.        | Vcc -0.4           | V        |      |

| Low Vcc Lock-out Voltage                     | VLKO             |                                      | 3.2                | 4.2      | V    |

- 2. Icc active while Internal Algorithm (program or erase) is in progress.

- 3. Not 100% tested.

<sup>1.</sup> The Icc current listed includes both the DC operating current and the frequency dependent component (at 6 MHz).

The frequency component typically is less than 2 mA/MHz, with OE at ViH.

## **AC CHARACTERISTICS**

## **Read-only Operations**

| PARAME<br>SYM.    | TER                | DESCRIPTION                                                                                        | TEST SETUR           | TEST SETUP |    | -120 | -150 | UNIT |

|-------------------|--------------------|----------------------------------------------------------------------------------------------------|----------------------|------------|----|------|------|------|

| JEDEC             | Standard           |                                                                                                    |                      |            |    |      |      |      |

| tAVAV             | tRC                | Read Cycle Time(2)                                                                                 |                      | Min.       | 90 | 120  | 150  | nS   |

| <sup>t</sup> AVQV | tACC               | Address to Output Delay                                                                            | CE = VIL<br>OE = VIL | Max.       | 90 | 120  | 150  | nS   |

| t <sub>ELQV</sub> | tCE                | Chip Enable to Output Delay                                                                        | OE = VIL             | Max.       | 90 | 120  | 150  | nS   |

| tGLQV             | tOE                | Output Enable to Output Delay                                                                      |                      | Max.       | 35 | 50   | 55   | nS   |

| <sup>t</sup> EHQZ | tHZ                | Chip Enable to Output High Z <sup>(3,4)</sup>                                                      |                      | Max.       | 20 | 30   | 35   | nS   |

| tGHQZ             | tDF                | Output Enable to Output High Z <sup>(2,3)</sup>                                                    |                      |            | 20 | 30   | 35   | nS   |

| tAXQX             | tОН                | Output Hold Time from<br>Addresses, $\overline{CE}$ or $\overline{OE}$ ,<br>Whichever Occurs First |                      | Min.       | 0  | 0    | 0    | nS   |

|                   | <sup>t</sup> READY | RESET Pin Low to Read Mode <sup>(4)</sup>                                                          |                      | Max.       | 20 | 20   | 20   | mS   |

|                   | tELFL<br>tELFH     | CE to BYTE Switching Low or High                                                                   |                      | Max.       | 5  | 5    | 5    | nS   |

### Notes:

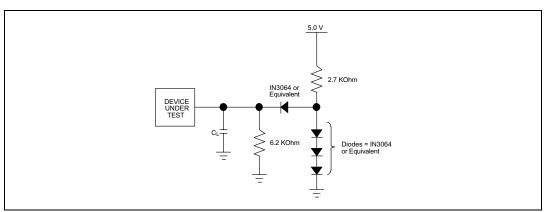

- 1. Test Conditions: Output Load: 1 TTL gate and 100 pF Input rise and fall times: 20 nS; Input pulse levels: 0V to 3 V

- Timing measurement reference level Input/Output: 1.5V

- 3. Output driver disable time.

- 4. Not 100% tested.

Figure 7. Test Condition

Note: CL = 100 pF including jig capacitance.

Publication Release Date: December 1999 Revision A2

## AC CHARACTERISTICS

## **Programming/Erase Operations**

| PARAMETER         | SYM.              | DESCRIPTION                                           |                           |              | -90        | -120       | -150       | UNIT     |

|-------------------|-------------------|-------------------------------------------------------|---------------------------|--------------|------------|------------|------------|----------|

| JEDEC             | Standard          |                                                       |                           |              |            |            |            |          |

| <sup>t</sup> AVAV | tWC               | Write Cycle Time <sup>(1)</sup>                       |                           | Min.         | 90         | 120        | 150        | nS       |

| <sup>t</sup> AVWL | tAS               | Address Setup Ti                                      | me                        | Min.         | 0          | 0          | 0          | nS       |

| <sup>t</sup> WLAX | <sup>t</sup> AH   | Address Hold Tim                                      | ne                        | Min.         | 45         | 50         | 50         | nS       |

| <sup>t</sup> DVWH | tDS               | Data Setup Time                                       |                           | Min.         | 45         | 50         | 50         | nS       |

| <sup>t</sup> WHDX | <sup>t</sup> DH   | Data Hold Time                                        |                           | Min.         | 0          | 0          | 0          | nS       |

|                   | tOES              | Output Enable Se                                      | etup Time                 | Min.         | 0          | 0          | 0          | nS       |

|                   | <sup>t</sup> OEH  | Output Enable                                         | Read <sup>(1)</sup>       | Min.         | 0          | 0          | 0          | nS       |

|                   |                   | Hold Time                                             | Toggle & Data Polling(1)  | Min.         | 10         | 10         | 10         | nS       |

| <sup>t</sup> GHWL | <sup>t</sup> GHWL | Read Recover Tir                                      | ne Before Write           | Min.         | 0          | 0          | 0          | nS       |

| tELWL             | tcs               | CE Setup Time                                         |                           | Min.         | 0          | 0          | 0          | nS       |

| tWHEH             | <sup>t</sup> CH   | CE Hold Time                                          | CE Hold Time              |              | 0          | 0          | 0          | nS       |

| tWLWH             | tWP               | Write Pulse Widtl                                     | Write Pulse Width         |              | 45         | 50         | 50         | nS       |

| twhwl             | twph              | Write Pulse Width High                                |                           | Min.         | 20         | 20         | 20         | nS       |

| tWHWH1            | tWHWH1            | Byte Programming Operation                            |                           | Typ.<br>Max. | 16<br>400  | 16<br>400  | 16<br>400  | μS<br>μS |

| tWHWH2            | tWHWH2            | Sector Erase Ope                                      | Sector Erase Operation(2) |              | 0.26<br>12 | 0.26<br>12 | 0.26<br>12 | sec      |

| tWHWH3            | tWHWH3            | Chip Erase Opera                                      | ation(2)                  | Typ.<br>Max. | 2.0<br>90  | 2.0<br>90  | 2.0<br>90  | sec      |

|                   | t <sub>VCS</sub>  | Vcc Setup Time(1                                      | 1)                        | Min.         | 50         | 50         | 50         | mS       |

|                   | tVIDR             | Rise Time to VID(                                     | 1,3)                      | Min.         | 500        | 500        | 500        | nS       |

|                   | tOESP             | OE Setup Time                                         | to WE Active(1, 3, 4)     | Min.         | 4          | 4          | 4          | mS       |

|                   | t <sub>RP</sub>   | RESET Pulse W                                         | RESET Pulse Width         |              | 500        | 500        | 500        | nS       |

|                   | tRSP              | RESET Setup Time(3)                                   |                           | Min.         | 4          | 4          | 4          | μS       |

|                   | tBUSY             | Programming/Erase Valid to RY/BY Delay <sup>(1)</sup> |                           | Min.         | 40         | 50         | 60         | nS       |

|                   | t∨LHT             | Voltage Transition Time(1, 4)                         |                           | Min.         | 4          | 4          | 4          | mS       |

|                   | tWPP1             | Sector Protect W                                      | rite Pulse Width(4)       | Min.         | 100        | 100        | 100        | mS       |

|                   | tWPP2             | Sector Unprotect                                      | Write Pulse Width(4)      | Min.         | 350        | 350        | 350        | mS       |

|                   | t <sub>CSP</sub>  | CE Setup Time                                         | to WE Active(1, 4)        | Min.         | 4          | 4          | 4          | nS       |

- 1. Not 100% tested.

- 2. Does not include pre-programming time.

- This timing is for Temporary Sector Unprotect operation.

These timings are for Sector Protect and/or Sector Unprotect operations.

## **SWITCHING WAVEFORMS**

| WAVEFORM | INPUT                                  | OUTPUT                                        |

|----------|----------------------------------------|-----------------------------------------------|

|          | Must Be Steady                         | Will Be Steady                                |

|          | May Change<br>from H to L              | Will Be Change<br>from H to L                 |

|          | May Change<br>from L to H              | Will Be Change<br>from L to H                 |

|          | Don't Care,<br>Any Change<br>Permitted | Change,<br>State Unknown                      |

|          | Does Not<br>Apply                      | Center Line is<br>High impedance<br>Off State |

Figure 8. AC Waveforms for Read Operations

## Switching Waveforms, continued

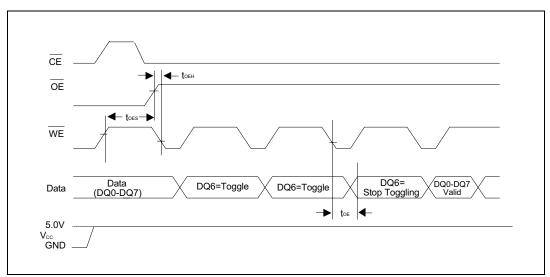

Figure 9. AC Waveforms Program Operations

- 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at BYTE address.

- 3.  $\overline{\mbox{DQ7}}$  is the output of the complement of the data written to the device.

- 4. Dout is the output of the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

6. These waveforms are for 16-bit mode.

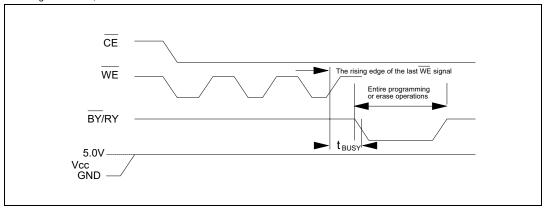

Figure 10. AC Waveforms Chip/Sector Erase Operations

- 1. SA is the sector address for Sector Erase. Address = X = Don't Care for Chip Erase.

- 2. These waveforms are for 16-bit mode.

Switching Waveforms, continued

Figure 11. AC Waveforms for Data Polling during Internal Algorithm Operations

Note: DQ7 = Valid Data (The device has completed the internal program or erase operation.)

Figure 12 AC Waveforms for Toggle Bit during Internal Algorithm Operation

Note: DQ6 stops toggling (The device has completed the internal program or erase operation.)

Switching Waveforms, continued

Figure 13. RY/BY Timing Diagram During Program/Erase Operation

Figure 14. RESET Timing Diagram

Inc.

Switching Waveforms, continued

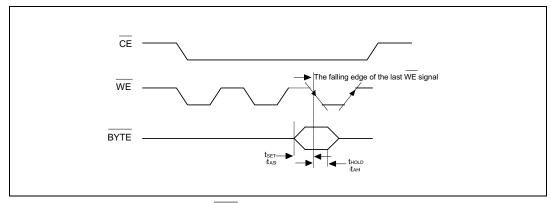

Figure 15. BYTE Timing Diagram for Read Operation

Figure 16. BYTE Timing Diagram for Write Operation

Figure 17. Temporary Sector Unprotect Algorithm

- 1. All protected sector groups unprotected.

- 2. All previously protected sector groups are protected again.

Figure 18. Temporary Unprotect Timing Diagram

## **AC CHARACTERISTICS**

## **Programming/Erase Operations**

| PARAMETER         | SYM.            |                                                 | DESCRIPTION                                       |      |      |      |      |      |

|-------------------|-----------------|-------------------------------------------------|---------------------------------------------------|------|------|------|------|------|

| JEDEC             | Standard        |                                                 |                                                   |      | -90  | -120 | -150 | Unit |

| tAVAV             | twc             | Write Cycle Time                                | (1)                                               | Min. | 90   | 120  | 150  | nS   |

| <sup>t</sup> AVEL | t <sub>AS</sub> | Address Setup T                                 | ime                                               | Min. | 0    | 0    | 0    | nS   |

| <sup>t</sup> ELAX | t <sub>AH</sub> | Address Hold Tir                                | ne                                                | Min. | 45   | 50   | 50   | nS   |

| <sup>t</sup> DVEH | t <sub>DS</sub> | Data Setup Time                                 |                                                   | Min. | 45   | 50   | 50   | nS   |

| <sup>t</sup> EHDX | <sup>t</sup> DH | Data Hold Time                                  |                                                   | Min. | 0    | 0    | 0    | nS   |

|                   | toes            | Output Enable S                                 | etup Time <sup>(1)</sup>                          | Min. | 0    | 0    | 0    | nS   |

|                   | tOEH            | Output Enable                                   | Read(1)                                           | Min. | 0    | 0    | 0    | nS   |

|                   |                 | Hold Time                                       | Toggle and Data Polling(1)                        | Min. | 10   | 10   | 10   | nS   |

| <sup>t</sup> GHWL | tGHWL           | Read Recover Ti                                 | me Before Write                                   | Min. | 0    | 0    | 0    | nS   |

| tWLEL             | tws             | WE Setup Time                                   | WE Setup Time                                     |      | 0    | 0    | 0    | nS   |

| tEHWH             | tWH             | WE Hold Time                                    |                                                   | Min. | 0    | 0    | 0    | nS   |

| <sup>t</sup> ELEH | tCP             | CE Pulse Width                                  |                                                   | Min. | 45   | 50   | 50   | nS   |

| tEHEL             | tCPH            | CE Pulse Width                                  | CE Pulse Width High                               |      | 20   | 20   | 20   | nS   |

| twhwh1            | twhwh1          | Byte Programmir                                 | g Operation                                       | Тур. | 16   | 16   | 16   | mS   |

|                   |                 |                                                 |                                                   | Max. | 400  | 400  | 400  | mS   |

| tWHWH2            | tWHWH2          | Sector Erase Ope                                | eration(2)                                        | Тур. | 0.26 | 0.26 | 0.26 | sec  |

|                   |                 |                                                 |                                                   | Max. | 12   | 12   | 12   | sec  |

| twhwh3            | twhwh3          | Chip Erase Oper                                 | ation(2)                                          | Тур. | 2.0  | 2.0  | 2.0  | sec  |

|                   |                 |                                                 |                                                   | Max. | 90   | 90   | 90   | sec  |

|                   | tvcs            | Vcc Setup Time(                                 | 1,3)                                              | Min. | 50   | 50   | 50   | mS   |

|                   | tVIDR           | Rise Time to V <sub>ID</sub> (1,3)              |                                                   | Min. | 500  | 500  | 500  | nS   |

|                   | tVLHT           | Voltage Transition Time(1,3)                    |                                                   | Min. | 4    | 4    | 4    | mS   |

|                   | twPP1           | Sector Protect Write Pulse Width <sup>(4)</sup> |                                                   | Min. | 100  | 100  | 100  | mS   |

|                   | tWPP2           | Sector Unprotect                                | Sector Unprotect Write Pulse Width <sup>(4)</sup> |      | 10   | 10   | 10   | mS   |

|                   | tOESP           | OE Setup Time                                   | to WE Active(1, 3)                                | Min. | 4    | 4    | 4    | mS   |

|                   | tCSP            | OE Setup Time                                   | to WE Active(1, 4)                                | Min. | 4    | 4    | 4    | nS   |

- 1. Not 100% tested.

- 2. Does not include pre-programming time.

- 3. This timing is for Sector Unprotect operation.

- 4. Output Driver Disable Time.

## Switching Waveforms, continued

Figure 19. Alternate  $\overline{\text{CE}}$  Controlled Program Operation Timings

- 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at BYTE address.

- 3. DQ7 is the output of the complement of the data written to the device.

- 4. Dout is the output of the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

- 6. These waveforms are for the x16 mode.

## BM29F400T/BM29F400B

## **Erase and Programming Performance**

| PARAMETER             |        |         |      |        |

|-----------------------|--------|---------|------|--------|

|                       | MIN.   | TYP.    | MAX. | UNIT   |

| Sector Erase Time     |        | 0.33    | 15   | sec    |

| Chip Erase Time       |        | 2.4     | 120  | sec    |

| Byte Programming Time |        | 16      | 400  | μS     |

| Chip Programming Time |        | 8       | 200  | sec    |

| Erase/Program Cycles  | 10,000 | 100,000 |      | cycles |

## **Latch Up Characteristics**

| PARAMETER                                         | MIN.    | MAX.       |

|---------------------------------------------------|---------|------------|

| Input Voltage with respect to Vss on all I/O pins | -1.0V   | Vcc + 1.0V |

| Vcc Current                                       | -100 mA | + 100 mA   |

Note: Includes all pins except Vcc. Test conditions: Vcc = 5.0V, one pin at a time.

## **CAPACITANCE**

## **TSOP Pin**

| PARAMETER               | SYMBOL | TEST SETUP | TYP. | MAX. | UNIT |

|-------------------------|--------|------------|------|------|------|

| Input Capacitance       | CIN    | VIN = 0    | 6    | 7.5  | pF   |

| Output Capacitance      | Соит   | Vout = 0   | 8.5  | 12   | pF   |

| Control Pin Capacitance | CIN2   | VIN = 0    | 8    | 10   | pF   |

#### Notes:

- 1. Sampled, not 100% tested.

- 2. Test conditions  $T_A = 25^{\circ}$ , f = 1.0 MHz.

## **Data Retention**

| PARAMETER                           | TEST CONDITIONS | MIN. | UNIT  |

|-------------------------------------|-----------------|------|-------|

| Minimum Pattern Data Retention Time | 150°            | 10   | Years |

| Minimum Pattern Data Retention Time | 125°            | 20   | Years |

## BM29F400T/BM29F400B

## **ORDERING INFORMATION**

| PART NO.     | ACCESS<br>TIME<br>(nS) | POWER<br>SUPPLY<br>CURRENT<br>MAX. (mA) | BOOT<br>BLOCK | PACKAGE     | CYCLING<br>(MIN.) | TEMPERATURE<br>RANGE |

|--------------|------------------------|-----------------------------------------|---------------|-------------|-------------------|----------------------|