#### **Features**

- Incorporates the ARM7TDMI<sup>™</sup> ARM<sup>®</sup> Thumb<sup>®</sup> Processor Core

- High-performance 32-bit RISC Architecture

- High-density 16-bit Instruction Set

- Leader in MIPS/Watt

- Embedded ICE (In-Circuit Emulation)

- 8K Bytes On-chip SRAM

- 32-bit Data Bus

- Single-clock Cycle Access

- Fully Programmable External Bus Interface (EBI)

- Maximum External Address Space of 64M Bytes

- Up to 8 Chip Selects

- Software Programmable 8/16-bit External Data Bus

- 8-level Priority, Individually Maskable, Vectored Interrupt Controller

- 4 External Interrupts, Including a High-priority Low-latency Interrupt Request

- 32 Programmable I/O Lines

- 3-channel 16-bit Timer/Counter

- 3 External Clock Inputs

- 2 Multi-purpose I/O Pins per Channel

- 2 USARTs

- 2 Dedicated Peripheral Data Controller (PDC) Channels per USART

- Programmable Watchdog Timer

- Advanced Power-saving Features

- CPU and Peripheral Can be Deactivated Individually

- Fully Static Operation:

- 0 Hz to 16 MHz at 1.8V

- 0 Hz to 33 MHz at 2.7V

- 0 Hz to 40 MHz at 3.0V

- 1.8V to 3.6V Operating Range

- Available in a 100-lead TQFP Package

## **Description**

The AT91M40800 microcontroller is a member of the Atmel AT91 16/32-bit microcontroller family, which is based on the ARM7TDMI processor core. This processor has a high-performance 32-bit RISC architecture with a high-density 16-bit instruction set and very low power consumption. In addition, a large number of internally banked registers result in very fast exception handling, making the device ideal for real-time control applications.

The AT91M40800 microcontroller features a direct connection to off-chip memory, including Flash, through the fully-programmable External Bus Interface (EBI). An eight-level priority vectored interrupt controller, in conjunction with the Peripheral Data Controller, significantly improves the real-time performance of the device.

The device is manufactured using Atmel's high-density CMOS technology. By combining the ARM7TDMI processor core with an on-chip high-speed memory and a wide range of peripheral functions on a monolithic chip, the AT91M40800 is a powerful microcontroller that offers a flexible, cost-effective solution to many compute-intensive embedded control applications.

# AT91 ARM® Thumb® Microcontrollers

# AT91M40800 Electrical Characteristics

# **Absolute Maximum Ratings\***

| Operating Temperature (Industrial)40°C to +85°C              |

|--------------------------------------------------------------|

| Voltage on Any Input Pin with Respect to Ground0.5V to +4.0V |

| Maximum Operating Voltage4.6V                                |

| DC Output Current6 mA                                        |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC Characteristics**

| Symbol            | Parameter             | Condition                                                                     | Min                   | Тур | Max                   | Units |

|-------------------|-----------------------|-------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| V <sub>DD</sub>   | DC Supply             |                                                                               | 1.8                   |     | 3.6                   | V     |

| T <sub>A</sub>    | Ambient Temperature   |                                                                               | -40                   |     | 85                    | °C    |

| V <sub>IL</sub>   | Input Low Voltage     | V <sub>DD</sub> = 1.8V to 3.6V                                                | -0.5                  |     | 0.3 x V <sub>DD</sub> | V     |

| V <sub>IH</sub>   | Input High Voltage    | $V_{DD} = 1.8V \text{ to } 3.6V$                                              | 0.7 x V <sub>DD</sub> |     | 3.6                   | V     |

| V <sub>OL</sub>   | Output Low Voltage    | $I_{OL} = 0.8 \text{ mA}, V_{DD} = 3.0 \text{V}$                              |                       |     | 0.1                   | V     |

| V <sub>OH</sub>   | Output High Voltage   | $I_{OH} = 0.8 \text{ mA}, V_{DD} = 3.0 \text{V}$                              | V <sub>DD</sub> - 0.1 |     |                       | V     |

| I <sub>LEAK</sub> | Input Leakage Current |                                                                               |                       |     | 390                   | nA    |

| I <sub>PULL</sub> | Input Pull-up Current | V <sub>DD</sub> = 3.6V                                                        |                       |     | 350                   | μΑ    |

| I <sub>CAP</sub>  | Input Capacitance     |                                                                               |                       |     | 6                     | pF    |

| 1                 | Shakia Currant        | $V_{DD} = 3.6V - MCKI = 0 Hz$<br>All inputs driven<br>TMS, TDI, TCK, NRST = 1 |                       | TBD |                       |       |

| I <sub>SC</sub>   | Static Current        | $V_{DD} = 1.8V - MCKI = 0 Hz$<br>All inputs driven<br>TMS, TDI, TCK, NRST = 1 |                       | TBD |                       | μΑ    |

# **Power Consumption**

The values in the following tables are measured values in the operating conditions indicated (i.e.,  $V_{DD} = 3.3V$  or 2.0V,  $T = 25^{\circ}$ ) on the AT91EB40 Evaluation Board.

Table 1. Power Consumption

|        |                                                                          | $V_{DD}$ |      |        |

|--------|--------------------------------------------------------------------------|----------|------|--------|

| Mode   | Conditions                                                               | 2.0V     | 3.3V | Unit   |

| Reset  |                                                                          | 0.06     | 0.16 |        |

| Normal | Fetch in ARM mode out of internal SRAM All peripheral clocks activated   | 1.38     |      |        |

| Normal | Fetch in ARM mode out of internal SRAM All peripheral clocks deactivated | 1.04     | 2.84 | mW/MHz |

| Idlo   | All peripheral clocks activated                                          | 0.61     | 1.66 |        |

| Idle   | All peripheral clocks deactivated                                        | 0.19     | 0.52 |        |

Table 2. Power Consumption per Peripheral

|                                  | V    | DD   |          |

|----------------------------------|------|------|----------|

| Peripheral                       | 2.0V | 3.3V | Unit     |

| PIO Controller                   | 0.01 | 0.03 |          |

| Timer/Counter Channel            | 0.01 | 0.02 | m\\/\\\\ |

| Timer/Counter Block (3 Channels) | 0.02 | 0.07 | mW/MHz   |

| USART                            | 0.03 | 0.08 |          |

## **Conditions**

#### **Environment Constraints**

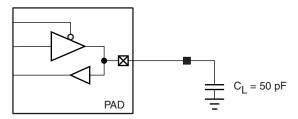

The output delays are valid for a capacitive load of 50 pF, as shown in Figure 1.

Figure 1. Output/Bidirectional Pad Capacitive Load

## **Timing Results**

The output delays are for a capacitive load of 50 pF, as shown in Figure 1.

In order to obtain the timing for other capacitance values, the following equation should be used.

$$t = t_{datasheet} + factor \times (C_{load} - 50pF)$$

Table 3. Derating Factor Due to Capacitive Load Variation

| Parameter | Industrial | Units |

|-----------|------------|-------|

| Factor    | 0.04       | ns/pF |

## **Voltage Ranges**

Timings are provided for the three operating conditions defined. The core voltage is supplied from 1.8V to 3.6V, but the three following operating conditions have been characterized for timing purposes.

**Table 4.** Voltage Ranges for Timing Characterization

|                      | V       | V <sub>DD</sub> |                                |  |  |

|----------------------|---------|-----------------|--------------------------------|--|--|

| Operating Conditions | Minimum | Maximum         | Maximum Operating<br>Frequency |  |  |

| 33 MHz at 2.7V       | 2.7V    | 3.6V            | 33 MHz                         |  |  |

| 40 MHz at 3.0V       | 3.0V    | 3.6V            | 40 MHz                         |  |  |

| 16 MHz at 1.8V       | 1.8V    | 3.6V            | 16 MHz                         |  |  |

# **Clock Waveforms**

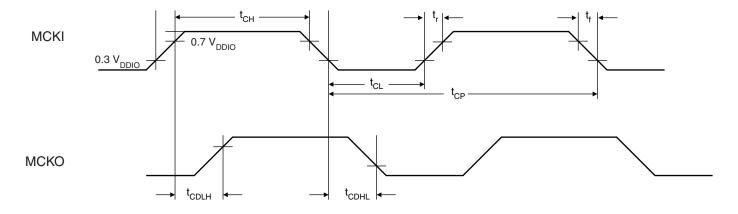

Table 5. Clock Waveform Parameters

|                      |                      |                   | Minimum           |                   |                   | Maximum           |                   |       |  |

|----------------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|--|

| Symbol               | Parameter            | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |  |

| 1/(t <sub>CP</sub> ) | Oscillator Frequency |                   |                   |                   | 33                | 40                | 16                | MHz   |  |

| t <sub>CP</sub>      | Main Clock Period    | 33                | 25                | 62                |                   |                   |                   |       |  |

| t <sub>CH</sub>      | High Time            | 12                | 11                | 22                |                   |                   |                   |       |  |

| t <sub>CL</sub>      | Low Time             | 12                | 11                | 22                |                   |                   |                   | ns    |  |

| t <sub>r</sub>       | Rising Edge          |                   |                   |                   | 2                 | 2                 | 2                 |       |  |

| t <sub>f</sub>       | Falling Edge         |                   |                   |                   | 2                 | 2                 | 2                 |       |  |

Table 6. Clock Propagation Times

|                   |                               |                   | Minimum           |                   |                   | Maximum           |                   |       |  |

|-------------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|--|

| Symbol            | Parameter                     | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |  |

| t <sub>CDLH</sub> | Rising Edge Propagation Time  | 5                 | 5                 | 10                | 12                | 11                | 22                | 20    |  |

| t <sub>CDHL</sub> | Falling Edge Propagation Time | 6                 | 6                 | 12                | 13                | 12                | 24                | ns    |  |

Figure 2. Clock Waveform

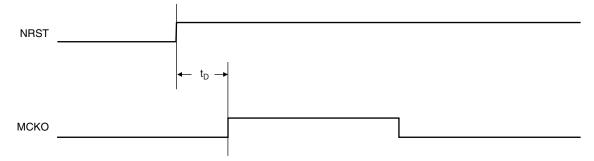

**Table 7.** NRST to MCKO

|                |                                     |                       | Minimum               |                       |                       | Maximum               |                       |       |  |

|----------------|-------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|--|

| Symbol         | Parameter                           | 33 MHz<br>at 2.7V     | 40 MHz<br>at 3.0V     | 16 MHz<br>at 1.8V     | 33 MHz<br>at 2.7V     | 40 MHz<br>at 3.0V     | 16 MHz<br>at 1.8V     | Units |  |

| t <sub>D</sub> | NRST Rising Edge to MCKO Valid Time | 3(t <sub>CP</sub> /2) | 3(t <sub>CP</sub> /2) | 3(t <sub>CP</sub> /2) | 7(t <sub>CP</sub> /2) | 7(t <sub>CP</sub> /2) | 7(t <sub>CP</sub> /2) | ns    |  |

Figure 3. MCKO Relative to NRST

# **AC Characteristics**

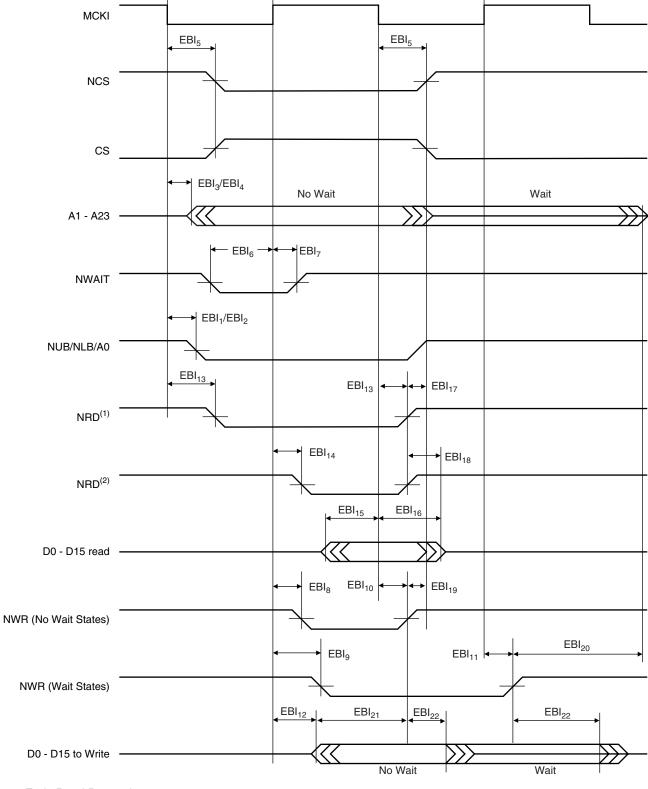

# **EBI Signals Relative to MCKI**

The following tables show timings relative to operating condition limits defined in Table 4. See Figure 4.

Table 8. General-purpose EBI Signals

|                  |                                | Minimum           |                   |                   |                   |                   |                   |       |

|------------------|--------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Symbol           | Parameter                      | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |

| EBI <sub>1</sub> | MCKI Falling to NUB Valid      | 3                 | 3                 | 6                 | 16                | 14                | 28                |       |

| EBI <sub>2</sub> | MCKI Falling to NLB/A0 Valid   | 5                 | 5                 | 10                | 14                | 12                | 24                |       |

| EBI <sub>3</sub> | MCKI Falling to A7 - A1 Valid  | 5                 | 5                 | 10                | 14                | 12                | 24                |       |

| EBI <sub>4</sub> | MCKI Falling to A23 - A8 Valid | 5                 | 5                 | 10                | 14                | 12                | 24                | ns    |

| EBI <sub>5</sub> | MCKI Falling to Chip Select    | 6                 | 6                 | 12                | 20                | 17                | 34                |       |

| EBI <sub>6</sub> | NWAIT Setup before MCKI Rising |                   |                   |                   | 8                 | 7                 | 14                |       |

| EBI <sub>7</sub> | NWAIT Hold after MCKI Rising   | 2                 | 1                 | 2                 |                   |                   |                   |       |

Table 9. EBI Write Signals

|                   |                                                                    |                    | Minimum            |                    |                   | Maximum           |                   |       |

|-------------------|--------------------------------------------------------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------|

| Symbol            | Parameter                                                          | 33 MHz<br>at 2.7V  | 40 MHz<br>at 3.0V  | 16 MHz<br>at 1.8V  | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |

| EBI <sub>8</sub>  | MCKI Rising to NWR Active (No Wait States)                         | 5                  | 5                  | 10                 | 15                | 13                | 26                |       |

| EBI <sub>9</sub>  | MCKI Rising to NWR Active (Wait States)                            | 5                  | 5                  | 10                 | 15                | 13                | 26                |       |

| EBI <sub>10</sub> | MCKI Falling to NWR Inactive (No Wait States)                      | 6                  | 6                  | 12                 | 15                | 13                | 26                |       |

| EBI <sub>11</sub> | MCKI Rising to NWR Inactive (Wait States)                          | 6                  | 6                  | 12                 | 15                | 13                | 26                | ns    |

| EBI <sub>12</sub> | MCKI Rising to D0 - D15 Out Valid                                  | 5                  | 4                  | 8                  | 16                | 14                | 28                | 110   |

| EBI <sub>19</sub> | NWR High to A23 - A1, NUB/NLB/A0, NCS, CS changes (No Wait States) | 2                  | 1                  | 2                  |                   |                   |                   |       |

| EBI <sub>20</sub> | NWR High to A23 - A1, NCS, CS<br>Changes (Wait States)             | t <sub>CP</sub> /2 | t <sub>CP</sub> /2 | t <sub>CP</sub> /2 |                   |                   |                   |       |

| EBI <sub>21</sub> | Data Out Valid before NWR High                                     | 15                 | 14                 | 28                 |                   |                   |                   |       |

| EBI <sub>22</sub> | Data Out Valid after NWR High                                      | 1                  | 1                  | 2                  |                   |                   |                   |       |

Table 10. EBI Read Signals

|                   |                                          | Minimum           |                   |                   |                   |                   |                   |       |

|-------------------|------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Symbol            | Parameter                                | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |

| EBI <sub>13</sub> | MCKI Falling to NRD Valid <sup>(1)</sup> | 6                 | 6                 | 12                | 13                | 15                | 30                |       |

| EBI <sub>14</sub> | MCKI Rising to NRD Valid <sup>(2)</sup>  | 5                 | 5                 | 10                | 14                | 12                | 24                |       |

| EBI <sub>15</sub> | D0 - D15 in Setup before MCKI Falling    |                   |                   |                   | 6                 | 6                 | 12                |       |

| EBI <sub>16</sub> | D0 - D15 in Hold after MCKI Falling      | 4                 | 4                 | 8                 |                   |                   |                   | ns    |

| EBI <sub>17</sub> | NRD High to A23 - A1, NCS, CS<br>Changes | 0                 | 0                 | 0                 |                   |                   |                   |       |

| EBI <sub>18</sub> | Data Hold after NRD High                 | 0                 | 0                 | 0                 |                   |                   |                   |       |

Notes: 1. Early Read Protocol 2. Standard Read Protocol

Figure 4. EBI Signals Relative to MCKI

Notes: 1. Early Read Protocol

2. Standard Read Protocol

## **Peripheral Signals**

## **USART Signals**

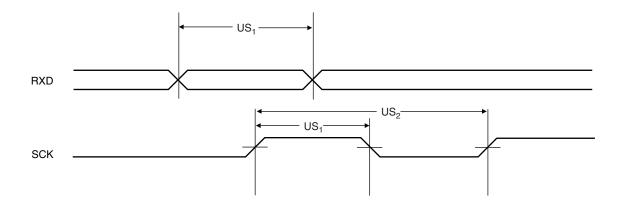

The inputs have to meet the minimum pulse width and period constraints shown in Table 11 and Table 12, and represented in Figure 5.

Table 11. USART Input Minimum Pulse Width

| Symbol          | Parameter                   | Minimum Pulse Width   | Units |

|-----------------|-----------------------------|-----------------------|-------|

| US <sub>1</sub> | SCK/RXD Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

Table 12. USART Minimum Input Period

| Symbol          | Parameter                | Minimum Input Period  | Units |

|-----------------|--------------------------|-----------------------|-------|

| US <sub>2</sub> | SCK Minimum Input Period | 5(t <sub>CP</sub> /2) | ns    |

Figure 5. USART Signals

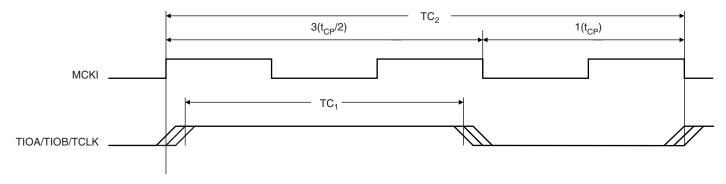

#### **Timer/Counter Signals**

Due to internal synchronization of input signals, there is a delay between an input event and a corresponding output event. This delay is  $3(t_{CP})$  in Waveform Event Detection mode and  $4(t_{CP})$  in Waveform Total Count Detection mode. The inputs have to meet the minimum pulse width and minimum input period shown in Tables 13 and 14, and as represented in Figure 6.

Table 13. Timer Input Minimum Pulse Width

| Symbol          | Parameter                          | Minimum Pulse Width   | Units |

|-----------------|------------------------------------|-----------------------|-------|

| TC <sub>1</sub> | TCLK/TIOA/TIOB Minimum Pulse-width | 3(t <sub>CP</sub> /2) | ns    |

Table 14. Timer Input Minimum Period

| Symbol          | Parameter                           | Minimum Input Period  | Units |

|-----------------|-------------------------------------|-----------------------|-------|

| TC <sub>2</sub> | TCLK/TIOA/TIOB Minimum Input Period | 5(t <sub>CP</sub> /2) | ns    |

Figure 6. Timer Input

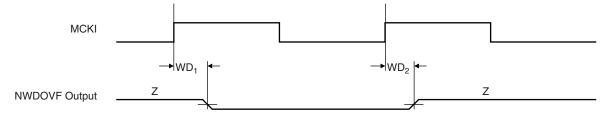

## **Watchdog Timer Signals**

Table 15. Watchdog Timer Outputs

|                 |                               | Minimum           |                   | Maximum           |                   |                   |                   |       |

|-----------------|-------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Symbol          | Parameter                     | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |

| WD <sub>1</sub> | MCKI Rising to NWDOVF Rising  | 3                 | 3                 | 6                 | 14                | 12                | 24                |       |

| WD <sub>2</sub> | MCKI Rising to NWDOVF Falling | 3                 | 3                 | 6                 | 14                | 12                | 24                | ns    |

Figure 7. Watchdog Signals Relative to MCKI

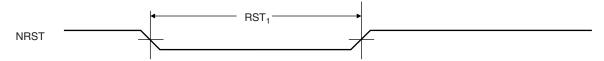

## **Reset Signals**

A minimum pulse width is necessary, as shown in Table 16 and as represented in Figure 8.

Table 16. Reset Minimum Pulse Width

| Symbol           | Parameter                | Minimum Pulse-width  | Units |

|------------------|--------------------------|----------------------|-------|

| RST <sub>1</sub> | NRST Minimum Pulse Width | 10(t <sub>CP</sub> ) | ns    |

Figure 8. Reset Signal

Only the NRST rising edge is synchronized with MCKI. The falling edge is asynchronous.

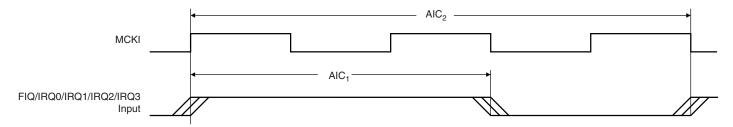

## **Advanced Interrupt Controller Signals**

Inputs have to meet the minimum pulse width and mimimum input period shown in Table 17 and Table 18 and represented in Figure 9.

Table 17. AIC Input Minimum Pulse Width

| Symbol           | Parameter                                   | Minimum Pulse Width   | Units |

|------------------|---------------------------------------------|-----------------------|-------|

| AIC <sub>1</sub> | FIQ/IRQ0/IRQ1/IRQ2/IRQ3 Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

Table 18. AIC Input Minimum Period

| Symbol           | Parameter                | Minimum Input Period  | Units |

|------------------|--------------------------|-----------------------|-------|

| AIC <sub>2</sub> | AIC Minimum Input Period | 5(t <sub>CP</sub> /2) | ns    |

Figure 9. AIC Signals

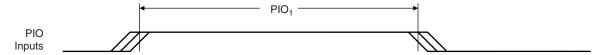

## Parallel I/O Signals

The inputs have to meet the minimum pulse width shown in Table 19 and represented in Figure 10.

Table 19. PIO Input Minimum Pulse Width

| Symbol Parameter |                               | Minimum Pulse Width   | Units |

|------------------|-------------------------------|-----------------------|-------|

| PIO <sub>1</sub> | PIO Input Minimum Pulse Width | 3(t <sub>CP</sub> /2) | ns    |

Figure 10. PIO Signal

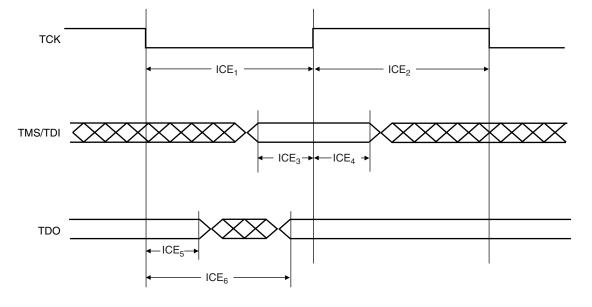

## **ICE Interface Signals**

Table 20. ICE Interface Timing Specifications

|                  |                        |                   | Minimum           |                   | Maximum           |                   |                   |       |

|------------------|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Symbol           | Parameter              | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | 33 MHz<br>at 2.7V | 40 MHz<br>at 3.0V | 16 MHz<br>at 1.8V | Units |

| ICE <sub>1</sub> | TCK Low Period         | 50                | 50                | 50                |                   |                   |                   |       |

| ICE <sub>2</sub> | TCK High Period        | 50                | 50                | 50                |                   |                   |                   |       |

| ICE <sub>3</sub> | TDI, TMS Setup to TCK  |                   |                   |                   | 2                 | 1                 | 2                 |       |

| ICE <sub>4</sub> | TDI, TMS Hold from TCK | 3                 | 2                 | 4                 |                   |                   |                   | ns    |

| ICE <sub>5</sub> | TDO Hold Time          | 3                 | 3                 | 6                 |                   |                   |                   |       |

| ICE <sub>6</sub> | TCK to TDO Valid       | 3                 | 3                 | 6                 | 20                | 17                | 34                |       |

Figure 11. ICE Interface Signal

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel U.K., Ltd.

Coliseum Business Centre

Riverside Way

Camberley, Surrey GU15 3YL

England

TEL (44) 1276-686-677

FAX (44) 1276-686-697

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Iapan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

> Fax-on-Demand North America: 1-(800) 292-8635 International: 1-(408) 441-0732

e-mail literature@atmel.com

Web Site http://www.atmel.com

*BBS* 1-(408) 436-4309

#### © Atmel Corporation 2000.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ARM, Thumb and ARM Powered are registered trademarks of ARM Limited. ARM7TDMI is a trademark of ARM Limited.