# **Features**

- AVR® Microcontroller

- Clock Generator Provides CPU Rates up to 24 MHz

- Programmable UART with 16-byte FIFOs at the Receiver Side (1), with a Maximum Rate of 921K Baud

- Programmable SPI Interface

- Full-speed USB Function Controller

- 2K Bytes of SRAM for Data, Stack and Program Variables

- . 2K Bytes of Dual-port RAM, Shared among the USB, UART and AVR

- 8K x 16-bit SRAM for Program Execution

- Internal ROM for the Bootstrap Loader

- One USB Control Endpoint

- Six USB Programmable Endpoints (up to 64 Bytes) with Double-buffered FIFOs for Back-to-back Transfers

- One 8-bit Timer/Counter

- One 16-bit Timer/Counter

- External and Internal Interrupt Sources

- Programmable Watchdog Timer

- Independent UART BRG Oscillator

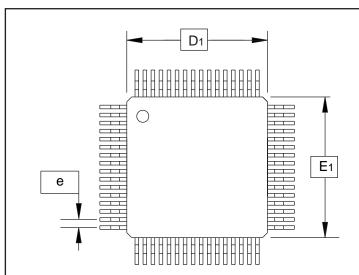

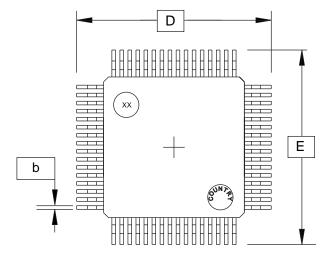

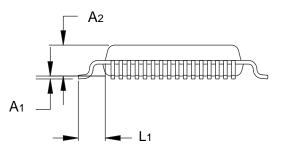

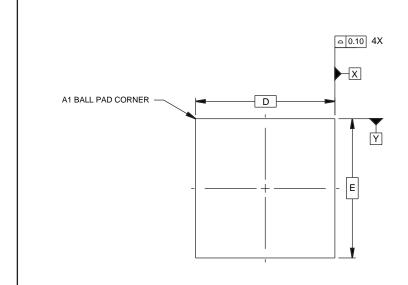

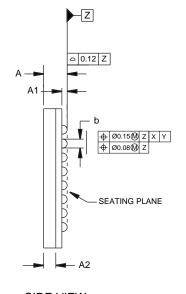

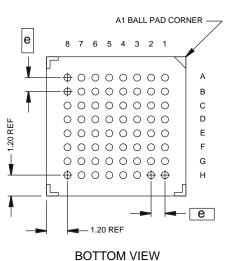

- 64-lead TQFP Package and BGA Package

- 3.3V Operation

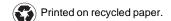

# **Pin Configuration (TQFP)**

AVR®-based

Bridge between

Full-speed USB

and Fast Serial

Asynchronous

Interfaces

AT76C711

# **Description**

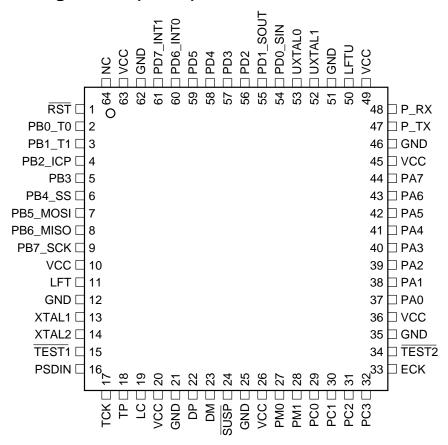

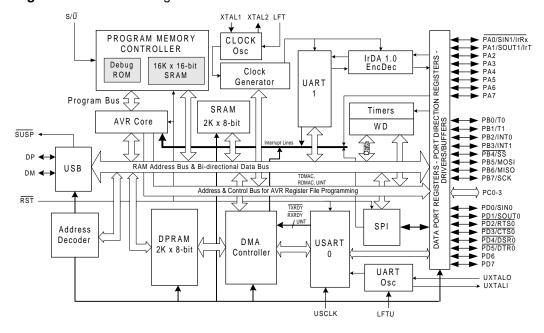

The Atmel AT76C711 is a compound USB device designed to provide a high-speed USB interface to devices that need to communicate with a host through fast serial links, like UARTs and IrDA interfaces. It is based on the AVR-enhanced RISC architecture and consists of a USB function interface with a devoted DMA controller for fast data transfers between the buffers of the USB endpoints and a shared DPRAM of 2K bytes, 2K bytes SRAM for data, stack and program variables, a Synchronous Peripheral Interface (SPI), a UART supporting a maximum rate of 921K baud with DMA channels for data transfers to/from the DPRAM and an 8K x 16-bit SRAM for microcode execution. An IrDA controller is also provided, attached to a second UART module, and is able to communicate with an IrDA transceiver with a maximum rate of 1.2 Mbps. An internal ROM contains the bootstrap loader which reads the instructions from an external serial DataFlash® of Atmel AT45 Series and stores them into the on-chip program SRAM. Alternatively, microcode can be stored in the program SRAM using the slave program mode while the chip is in the reset state.

The USB Hardware block consists of a USB transceiver, the SIE, endpoint controllers and an interface to the microcontroller. The USB Hardware interfaces to the USB host at the packet level. The microcontroller firmware handles the higher-level USB protocol layers that are not processed by the USB Hardware and in addition, it performs the peripheral control functions.

The device is suitable for applications where minimization of power dissipation is required, since there are no power-consumable transactions with external parallel devices.

# **Block Diagram**

# **Applications**

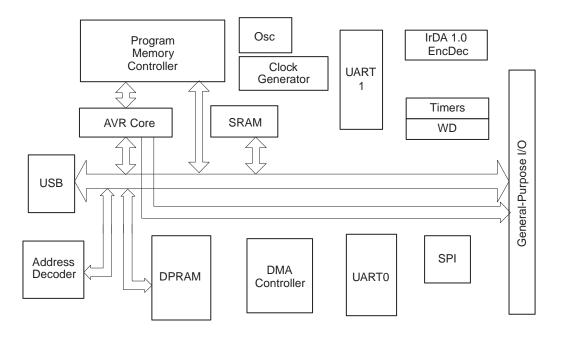

The AT76C711 can be used in applications where peripherals supporting fast serial asynchronous or synchronous transfer of data have to communicate with a host or other peripherals through a high-speed serial link, like USB. A typical application of AT76C711 and its functional diagram are shown in Figures 1 and 2.

Typical areas of AT76C711 usage are:

- Connection of Network Interface Cards (NICs) to a host system

- Wireless communications

- Bridging of microcontrollers with different types of serial interfaces

- USB to UART bridge

- USB to IrDA bridge

- IrDA to UART bridge

- Packet adaptation of network protocol packets to USB requirements

Figure 1. Typical AT76C711 Application

Figure 2. Functional Diagram

# Pin Summary - Pin Assignment in Alphabetical Order

I = Input, O = Output, OD = Output, Open Drain, B = Bi-directional, V = Power Supply, Ground Type:

| 1) po: 1 = 111 par, 0 = 0 arpar, 0 2 |             |        |      |

|--------------------------------------|-------------|--------|------|

| Pin #<br>TQFP                        | Pin#<br>BGA | Signal | Туре |

| 23                                   | H4          | DM     | В    |

| 22                                   | НЗ          | DP     | В    |

| 33                                   | H8          | ECK    | I    |

| 19                                   | F3          | LC     | I    |

| 14                                   | E2          | LFT    | I    |

| 50                                   | A7          | LFTU   | I    |

| *                                    | ***         | GND    | V    |

| 64                                   | B2          | NC     |      |

| 48                                   | B7          | P_IRX  | I    |

| 47                                   | B8          | P_ITX  | 0    |

| 37                                   | E7          | PA0    | В    |

| 38                                   | F8          | PA1    | В    |

| 39                                   | E8          | PA2    | В    |

| 40                                   | E5          | PA3    | В    |

| 41                                   | D8          | PA4    | В    |

| 42                                   | E6          | PA5    | В    |

| 43                                   | D7          | PA6    | В    |

| Pin# | Pin# |          |      |

|------|------|----------|------|

| TQFP | BGA  | Signal   | Туре |

| 44   | D6   | PA7      | В    |

| 2    | B1   | PB0_T0   | В    |

| 3    | C3   | PB1_T1   | В    |

| 4    | C2   | PB2_ICP  | В    |

| 5    | D2   | PB3      | В    |

| 6    | C1   | PB4_SS   | В    |

| 7    | D1   | PB5_MOSI | В    |

| 8    | D4   | PB6_MISO | В    |

| 9    | E1   | PB7_SCK  | В    |

| 29   | H6   | PC0      | В    |

| 30   | G6   | PC1      | В    |

| 31   | H7   | PC2      | В    |

| 32   | G7   | PC3      | В    |

| 54   | A6   | PD0_SIN  | В    |

| 55   | A5   | PD1_SOUT | В    |

| 56   | D5   | PD2      | В    |

| 57   | A4   | PD3      | В    |

|      |      |          |      |

| Pin # | Pin# |          |      |

|-------|------|----------|------|

| TQFP  | BGA  | Signal   | Туре |

| 58    | C5   | PD4      | В    |

| 59    | B4   | PD5      | В    |

| 60    | C4   | PD6_INT0 | В    |

| 61    | A3   | PD7_INT1 | В    |

| 16    | G2   | PSDIN    | I    |

| 1     | A1   | RST      | I    |

| 27,   | G5,  | PM0, PM1 | I    |

| 28    | F5   |          |      |

| 24    | E4   | SUSP     | 0    |

| 17    | H1   | TCK      | I    |

| 15    | G1   | TEST1    | I    |

| 34    | G8   | TEST2    | I    |

| 18    | H2   | TP       | I    |

| **    | **** | VCC      | V    |

| 51    | B6   | UXTALI   | I    |

| 52    | B5   | UXTALO   | 0    |

| 11    | F1   | XTAL1    | I    |

| 12    | F2   | XTAL2    | 0    |

- Notes: 1. (\*) GND TGFP: 12, 21, 25, 35, 46, 51, 62.

- 2. (\*\*) VCC TQFP: 10, 20, 24, 36, 45, 49, 63.

- 3. (\*\*\*) GND BGA: B3, C6, C7, E3, F6, H5, G4

- 4. (\*\*\*\*) VCC BGA: A2, A8, C8, F7, F4, G3, D3

# Pin Summary – Pin Assignment in Numerical Order

|               |       |          | _    |

|---------------|-------|----------|------|

| Pin #<br>TQFP | Pin # | Signal   | Typo |

|               | BGA   | Signal   | Туре |

| 1             | A1    | RST      | I    |

| 2             | B1    | PB0_T0   | В    |

| 3             | C3    | PB1_T1   | В    |

| 4             | C2    | PB2_ICP  | В    |

| 5             | D2    | PB3      | В    |

| 6             | C1    | PB4_SS   | В    |

| 7             | D1    | PB5_MOSI | В    |

| 8             | D4    | PB6_MISO | В    |

| 9             | E1    | PB7_SCK  | В    |

| 10            | D3    | VCC      | V    |

| 11            | E2    | LFT      | I    |

| 12            | E3    | GND      | V    |

| 13            | F1    | XTAL1    | I    |

| 14            | F2    | XTAL2    | 0    |

| 15            | G1    | TEST1    | I    |

| 16            | G2    | PSDIN    | I    |

| 17            | H1    | TCK      | I    |

| 18            | H2    | TP       | I    |

| 19            | F3    | LC       | I    |

| 20            | G3    | VCC      | V    |

| 21            | G4    | GND      | V    |

| 22            | НЗ    | DP       | В    |

| Pin #<br>TQFP | Pin #<br>BGA | Signal | Туре |

|---------------|--------------|--------|------|

| 23            | H4           | DM     | В    |

| 24            | E4           | SUSP   | 0    |

| 25            | H5           | GND    | V    |

| 26            | F4           | VCC    | V    |

| 27            | G5           | PM0    | I    |

| 28            | F5           | PM1    | I    |

| 29            | H6           | PC0    | В    |

| 30            | G6           | PC1    | В    |

| 31            | H7           | PC2    | В    |

| 32            | G7           | PC3    | В    |

| 33            | H8           | ECK    | I    |

| 34            | G8           | TEST2  | I    |

| 35            | F6           | GND    | V    |

| 36            | F7           | VCC    | V    |

| 37            | E7           | PA0    | В    |

| 38            | F8           | PA1    | В    |

| 39            | E8           | PA2    | В    |

| 40            | E5           | PA3    | В    |

| 41            | D8           | PA4    | В    |

| 42            | E6           | PA5    | В    |

| 43            | D7           | PA6    | В    |

| 44            | D6           | PA7    | В    |

| Pin # | Pin # | Simus!   | Tune |

|-------|-------|----------|------|

| TQFP  | BGA   | Signal   | Туре |

| 45    | C8    | VCC      | V    |

| 46    | C7    | GND      | V    |

| 47    | B8    | P_ITX    | 0    |

| 48    | В7    | P_IRX    | I    |

| 49    | A8    | VCC      | V    |

| 50    | A7    | LFTU     | I    |

| 51    | C6    | GND      | V    |

| 52    | В6    | UXTALI   | I    |

| 53    | B5    | UXTALO   | 0    |

| 54    | A6    | PD0_SIN  | В    |

| 55    | A5    | PD1_SOUT | В    |

| 56    | D5    | PD2      | В    |

| 57    | A4    | PD3      | В    |

| 58    | C5    | PD4      | В    |

| 59    | B4    | PD5      | В    |

| 60    | C4    | PD6_INT0 | В    |

| 61    | A3    | PD7_INT1 | В    |

| 62    | В3    | GND      | V    |

| 63    | A2    | VCC      | V    |

| 64    | B2    | NC       | V    |

# Signal Description (1)

Type: I = Input, O = Output, OD = Output, Open Drain, B = Bi-directional, V = Power Supply, Ground

| Name                    | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Memory (        | Controller Sig | nals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PM0, PM1                | I              | Configuration pins – See Figure 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

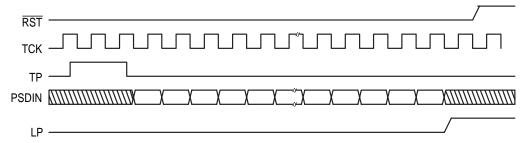

| PSDIN                   | I              | Program Serial Data-In: In slave program mode, this signal carries the serial program data that are samples with the positive edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TP                      | I              | When RST is active (low), a high level of this signal, for at least two TCK pulses, forces the program address generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| LC                      | 1              | Load Complete: A transition from low to high denotes the completion of program data transfer from the external device. The AVR will start executing instructions from the internal SRAM as soon as the $\overline{\text{RST}}$ goes high.                                                                                                                                                                                                                                                                                                                                                                         |

| TCK                     | 1              | A clock signal for sampling PSDIN input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Port Signals            | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PA[0:7]                 | В              | Port A, PA0 through PA7 – 8-bit bi-directional port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PA[0:7] PC[0:3] PD[0:7] | B<br>B         | Port B, PB0 through PB7 – 8-bit bi-directional port. PB0, PB1, PB2, PB4 through PB7 are dual- function as shown below:  Port Alternate Function  PB0 Timer/Counter0 clock input  PB1 Timer/Counter1 clock input  PB2 (ICP) Input Capture Pin for Timer/Counter1  PB4 (\$\overline{SS}\$) SPI slave port select input  PB5 (MOSI) SPI slave port select input  PB6 (MISO) SPI master data-in, slave data-out  PB7 (SCK) SPI master clock out, slave clock in  Port C, PC0 through PC3 – 4-bit output port.  Port D, PD0 through PD7 – 8-bit bi-directional I/O port. PD0, PD1 also serve as the data lines for     |

| PD[0:7]                 | В              | the asynchronous serial port as listed below:  Port Alternate Function  PD0 (SIN) Serial Data-In (I): This pin provides the serial receive data input to 16550 UART. The SIN signal will be a logic "1" during reset, idle (no data). During the local loopback mode, the SIN input pin is disabled and SOUT data is internally connected to the UART SIN input.  PD1 (SOUT) Serial Data Out (O): This pin provides the serial transmit data from the 16550 UART. The SOUT signal will be a logic "1" during reset, idle (no data).  PD6 (INT0) External Interrupt0 source  PD7 (INT1) External Interrupt1 source |

| USB Serial Interfac     | e              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DP                      | В              | Upstream Plus USB I/O – DP and DM form the differential signal pin pair connected to the host controller or an upstream hub.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DM                      | В              | Upstream Minus USB I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SUSP                    | 0              | Suspend: This output pin is deactivated (high) during normal operation. It is used to signal the host microcontroller that AT76C711 has received USB suspend signaling. This pin will stay asserted while AT76C711 is in the suspend mode. This pin is deactivated whenever a USB resume signaling is detected on DP and DM.                                                                                                                                                                                                                                                                                      |

# Signal Description (Continued)<sup>(1)</sup>

Type: I = Input, O = Output, OD = Output, Open Drain, B = Bi-directional, V = Power Supply, Ground

| Name           | Туре | Description                                                                                                                                                                                                      |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Signals   |      |                                                                                                                                                                                                                  |

| TEST1          | I    | Test signal for clocks (used in production phase only – normally tied to high)                                                                                                                                   |

| TEST2          | I    | Test signal for monitoring internal signal levels using the four data ports (used in production phase only – normally tied to high)                                                                              |

| ECK            | ı    | Clock pulse for activating various test modes when TEST2 is active                                                                                                                                               |

| IrDA Interface |      |                                                                                                                                                                                                                  |

| P_ITX          | 0    | Infrared Data Out: This pin provides the serial transmit data from the IrDA codec to external IR Data Transceiver. This function is activated when the IrDA interface is enabled from PERIPHEN I/O Register.     |

| P_IRX          | I    | Infrared Data-In: This pin provides the serial receive data input from the external IR Data Transceiver to IrDA codec. This function is activated when the IrDA interface is enabled from PERIPHEN I/O Register. |

| Other Signals  |      |                                                                                                                                                                                                                  |

| GND            | V    | Ground                                                                                                                                                                                                           |

| VCC            | V    | 3.3V power supply                                                                                                                                                                                                |

| RST            | ı    | Reset: A low on this pin for two machine cycles, while the oscillator is running, resets the device.                                                                                                             |

| XTAL1          | I    | Oscillator Input: Input to the inverting oscillating amplifier. A 12 MHz clock oscillator should be applied.                                                                                                     |

| XTAL2          | 0    | Oscillator Output: Output of the inverting oscillator amplifier.                                                                                                                                                 |

| LFT            | I    | Master clock PLL LFT pin                                                                                                                                                                                         |

| UXTALI         | I    | UART BRG Oscillator Input. Input to the UART oscillator amplifier.                                                                                                                                               |

| UXTALO         | 0    | UART BRG Oscillator Output. Output of the UART oscillator amplifier.                                                                                                                                             |

| LFTU           | I    | UART clock PLL LFT pin                                                                                                                                                                                           |

Note: 1. Any signal with an OVERLINE indicates that it is an active low signal.

# Functional Description

# Bootstrap ROM and Program Modes

The AT76C711 offers a variety of program modes that allow the user not only to upload the microcode to internal program SRAM but also to upgrade the system firmware that is contained in a serial AT45DB011 (or larger) Flash. AT76C711 supports one slave and three master program modes.

# **Slave Program Mode**

The chip enters the slave program mode while in the reset state (RST active low) when it detects a positive edge transition of TP signal. The timing diagram of the procedure is depicted in Figure 3.

Figure 3. Slave Program Mode Timing Diagram

# **Master Program Modes**

On power-up or after a system reset, the bootstrap code traces the value of the PM0, PM1 signals and executes the respective task according to Figure 3. After the execution of any of the following tasks, the chip enters the normal mode and starts running the code loaded in the internal program SRAM.

| PM0 | PM1 | Task                                                                                                                                                                   |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | х   | SPI program mode: The internal program SRAM is loaded from the external serial Flash through the SPI.                                                                  |

| 0   | 0   | USB program mode: The host downloads the code to the internal program SRAM using the DFU protocol. <sup>(1)</sup>                                                      |

| 0   | 1   | USB program mode with firmware upgrade: The host downloads pages of code to the internal program SRAM, which are then stored to the external SPI Flash. <sup>(1)</sup> |

Note: 1. This mode is not supported in the current version of the chip.

# **USB Hardware Block**

# **USB Function Interface**

The USB function interface consists of a Serial Interface Engine (SIE), a Serial Bus Controller (SBC) and a System Interface (SI). The SIE performs the clock/data separation, NRZI encoding and decoding, bit insertion and deletion, CRC generation and checking and the serial-parallel data conversion. The SBC consists of a protocol engine and a USB device with one control endpoint (EP0), four programmable endpoints, each with one 2 x 64-byte dedicated double-buffered FIFO and one programmable endpoint with one 2 x 16-byte double-buffered FIFO. Each EP can be programmed as isochronous, bulk or interrupt and can be configured either as IN or OUT. A pair endpoint address scheme is also supported for the first four programmable endpoints. According to this scheme, two endpoints may have the same address, provided one of them has been configured as IN and the other as OUT. The SBC manages the device address, monitors the status of the transactions, manages the FIFOs and communicates to the microcontroller through a set of status and control registers. The SI connects the SBC to the microcontroller and provides a DMA mechanism for transferring data between the DPRAM and the endpoint buffers.

# **USB Function Controller**

The function controller is implemented in the microcontroller's firmware.

# **USB Interrupt Handling**

All interrupt signals from the USB functions are consolidated into a single interrupt line, which is input to the interrupt controller of the AVR. The following sections describe all the interrupt sources of the USB controller.

All interrupts are masked through the interrupt enable registers that exist in the USB controller. The External Resume and Received Resume interrupts are cleared when the firmware clears the interrupt bit (the Suspend Interrupt is automatically cleared when activity is detected). All other interrupts are cleared when the processor sets a corresponding bit in an interrupt acknowledge register in the USB macro cell. There is only one bit for each interrupt source.

| Interrupt              | Description                                                                                                                                                                                                                                                                                                                                      |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function EP0 Interrupt | See "Control Transfers at Function EP0" for details.                                                                                                                                                                                                                                                                                             |

| Function EP1 Interrupt | For an OUT endpoint, it indicates that Function Endpoint1 has received a valid OUT packet and that the data is in the FIFO. For an IN endpoint, it means that the endpoint has received an IN token, sent out the data stored in the FIFO and received an ACK from the host. The FIFO is now ready to be written by new data from the processor. |

| Function EP2 Interrupt | See Function EP1 Interrupt                                                                                                                                                                                                                                                                                                                       |

| Function EP3 Interrupt | See Function EP1 Interrupt                                                                                                                                                                                                                                                                                                                       |

| Function EP4 Interrupt | See Function EP1 Interrupt                                                                                                                                                                                                                                                                                                                       |

| Function EP5 Interrupt | See Function EP1 Interrupt                                                                                                                                                                                                                                                                                                                       |

| Function EP6 Interrupt | See Function EP1 Interrupt                                                                                                                                                                                                                                                                                                                       |

| SOF Received           | Whenever USB Hardware decodes a valid Start of Frame                                                                                                                                                                                                                                                                                             |

| EXT RSM                | The USB Hardware has received a remote wake-up request.                                                                                                                                                                                                                                                                                          |

| RCVD RSM               | The USB Hardware has received resume signaling. The processor's firmware should take the function out of the suspended state.                                                                                                                                                                                                                    |

| SUSP                   | The USB Hardware has detected a suspend condition and is preparing to enter the suspend mode. The processor's firmware should place the embedded function in the suspend mode.                                                                                                                                                                   |

# **Interrupt Priority**

The USB macro interrupt priority is defined below.

| Priority Level            | Interrupt Name      |

|---------------------------|---------------------|

| 2 (High level)            | SOF Received        |

| 1: Same level (Low level) | Function EP0 to EP6 |

# **Endpoint Interrupt**

Endpoint interrupts are triggered by setting or clearing one or more bits in the Control and Status registers of an endpoint. These interrupts are caused by events during packet transactions and are different for control and non-control endpoints. The interrupts are described below, with respect to the Control and Status register bit definitions. Please refer to the "Endpoint Control and Status Register" definition on page 59.

# Interrupt for Non-control Endpoints

| 1. | RX OUT Packet   | set   | (0 -> 1) |

|----|-----------------|-------|----------|

| 2. | TX Packet Ready | clear | (1 -> 0) |

# Interrupt for Control Endpoints

| 1. | RX OUT Packet   | set   | (0 -> 1) |

|----|-----------------|-------|----------|

| 2. | RX SETUP        | set   | (0 -> 1) |

| 3. | TX Packet Ready | clear | (1 -> 0) |

| 4. | TX Complete     | set   | (0 -> 1) |

# **Serial Interface Engine**

The SIE performs the following functions:

- NRZI data encoding and decoding

- Bit stuffing and unstuffing

- CRC generation and checking

- ACKs and NACKs

- Identifying the type of a token

- Address checking

- Clock generation (via DPLL)

#### **Function Interface Unit**

The Function Interface Unit (FIU) provides the interface between the processor and the SIE. It manages transactions at the packet level with minimal intervention from the processor and contains the endpoints' buffers.

The FIU is designed to operate in single-packet mode and to manage the USB packet protocol layer. To operate the FIU, the firmware must first enable the endpoints of the FIU, and select direction and ping-pong capability. After being enabled, the endpoints are in receive mode by default. The FIU notifies the processor when a valid token has been received. The data contained in the data packet will be supplied in the FIFO.

The processor transfers the data to and from the host by interacting with each endpoint's FIFO and Control and Status registers.

For example, when transmitting an IN packet, the FIU assembles the data of the endpoint's FIFO in a USB packet, transmits the packet and will signal the processor after the host receives and acknowledges the packet. The FIU performs automatic data packet retransmission and DATA0/DATA1 PID toggling.

For SETUP tokens, the processor must parse the device request and then respond appropriately. After a SETUP token, there may be zero (0) or more DATA IN or DATA OUT packets for which the processor must either supply or receive the data.

# **Control Transfers at Function EP0**

Legend: DATA1/DATA0 = Data packet with DATA1 or DATA0 PID

DATA 1 (0) = Zero length DATA1 packet

| Host                               | USB Macro                          | Microcontroller                                                                                                                                                                                                                                                               |

|------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SETUP Stage                        |                                    |                                                                                                                                                                                                                                                                               |

| 1. [SYNC]-[SETUP]                  |                                    |                                                                                                                                                                                                                                                                               |

| 2. [SYNC]-[DATA0]                  |                                    |                                                                                                                                                                                                                                                                               |

|                                    | 3. Data are put in FIFO            |                                                                                                                                                                                                                                                                               |

|                                    | 4. If CRC OK,<br>Send [SYNC]-[ACK] |                                                                                                                                                                                                                                                                               |

|                                    | 5. If CRC OK,<br>Set RX_SETUP bit  |                                                                                                                                                                                                                                                                               |

|                                    |                                    | 6. INTERRUPT                                                                                                                                                                                                                                                                  |

|                                    |                                    | 7. Read UISR (bit 0 is set)                                                                                                                                                                                                                                                   |

|                                    |                                    | 8. Read FCSR0 (RX_SETUP bit)                                                                                                                                                                                                                                                  |

|                                    |                                    | 9. Read FBYTE_CNT0                                                                                                                                                                                                                                                            |

|                                    |                                    | 10. Read FIFO0                                                                                                                                                                                                                                                                |

|                                    |                                    | If Set Control Direction Fill FIFO with data Set TX_Packet_Ready If Control Write Phase: Clear Control Direction If No Data Stage Phase: Clear Control Direction Set Data_End bit If Unsupported Command: Set FORCE_STALL bit  12. Clear RX_SETUP bit 13. SET UIAR (EP0 INTA) |

| Status Stage, No DATA Stag         | е                                  |                                                                                                                                                                                                                                                                               |

| 1. [SYNC]-[IN]                     | 2. Send DATA1(0)                   |                                                                                                                                                                                                                                                                               |

| 3. If CRC OK,<br>Send [SYNC]-[ACK] |                                    |                                                                                                                                                                                                                                                                               |

|                                    | 4. Set TX_Complete bit             |                                                                                                                                                                                                                                                                               |

|                                    |                                    | 5. INTERRUPT                                                                                                                                                                                                                                                                  |

|                                    |                                    | 6. Read UISR                                                                                                                                                                                                                                                                  |

|                                    |                                    | 7. Read CSR                                                                                                                                                                                                                                                                   |

|                                    |                                    | 8. If SET_ADDRESS, write to FADDR                                                                                                                                                                                                                                             |

|                                    |                                    | 9. Clear TX_Complete bit                                                                                                                                                                                                                                                      |

# **Control Transfers at Function EP0 (Continued)**

Legend: DATA1/DATA0 = Data packet with DATA1 or DATA0 PID

DATA 1 (0) = Zero length DATA1 packet

| Host                               | USB Macro                                                                                              | Microcontroller                                                                   |

|------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|                                    |                                                                                                        | 10. Clear Data_End bit                                                            |

|                                    |                                                                                                        | 11. Set FORCE_STALL bit                                                           |

|                                    |                                                                                                        | 12. SET UIAR (EP0 INTA)                                                           |

| DATA Stage, Control READ           |                                                                                                        |                                                                                   |

| 1. [SYNC]-[IN]                     |                                                                                                        |                                                                                   |

|                                    | <ol> <li>If TX_Packet_Ready = 1</li> <li>Send DATA0/DATA1</li> <li>else</li> <li>Send STALL</li> </ol> |                                                                                   |

| 3. If CRC OK,<br>Send [SYNC]-[ACK] |                                                                                                        |                                                                                   |

|                                    | 4. Clear TX_Packet_Ready                                                                               |                                                                                   |

|                                    | 5. Set TX_Complete bit                                                                                 |                                                                                   |

|                                    |                                                                                                        | 6. INTERRUPT                                                                      |

|                                    |                                                                                                        | 7. Read UISR                                                                      |

|                                    |                                                                                                        | 8. Read CSR                                                                       |

|                                    |                                                                                                        | 9. Clear TX_Complete bit                                                          |

|                                    |                                                                                                        | 10. If more data Fill FIFO with data Set TX_Packet_Ready else Set SET_FORCE_STALL |

|                                    |                                                                                                        | 11. SET UIAR (EP0 INTA)                                                           |

| STATUS/Early STATUS Stag           | e with READ DATA Stage                                                                                 |                                                                                   |

| 1. [SYNC]-[OUT]                    |                                                                                                        |                                                                                   |

| 2. [SYNC]-[DATA1(0)]               |                                                                                                        |                                                                                   |

|                                    | 3. If TX_Complete = 0 Send [SYNC]-[ACK] Set RX_OUT else Send [SYNC]-[NACK]                             |                                                                                   |

|                                    |                                                                                                        | 4. INTERRUPT                                                                      |

|                                    |                                                                                                        | 5. Read UISR                                                                      |

|                                    |                                                                                                        | 6. Read CSR                                                                       |

|                                    |                                                                                                        | 7. Clear RX_OUT                                                                   |

|                                    |                                                                                                        | 8. Set Data_End                                                                   |

# **Control Transfers at Function EP0 (Continued)**

Legend: DATA1/DATA0 = Data packet with DATA1 or DATA0 PID

DATA 1 (0) = Zero length DATA1 packet

| Host                               | USB Macro                       | Microcontroller                                                                                                           |

|------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                                    |                                 | 9. Set FORCE_STALL  COMMENT: A SETUP token will clear Data End.  Not cleared by firware in case host retries 1 through 3. |

|                                    |                                 | 10. SET UIAR (EP0 INTA)                                                                                                   |

| DATA Stage, Control WRI            | TE                              |                                                                                                                           |

| 1. [SYNC]-[OUT]                    |                                 |                                                                                                                           |

| 2. [SYNC]-[DATA1/DATA0]            |                                 |                                                                                                                           |

|                                    | 3. Data are put in FIFO         |                                                                                                                           |

|                                    | 4. If CRC OK, send [SYNC]-[ACK] |                                                                                                                           |

|                                    | 5. If CRC OK, set RX_OUT        |                                                                                                                           |

|                                    |                                 | 6. INTERRUPT                                                                                                              |

|                                    |                                 | 7. Read UISR                                                                                                              |

|                                    |                                 | 8. Read CSR                                                                                                               |

|                                    |                                 | 9. Read FIFO                                                                                                              |

|                                    |                                 | 10. Clear RX_OUT                                                                                                          |

|                                    |                                 | If last packet, Set Data_End Set FORCE_STALL                                                                              |

|                                    |                                 | 11. SET UIAR (EPO INTA)                                                                                                   |

| STATUS Stage with WRIT             | E DATA Stage                    |                                                                                                                           |

| 1. [SYNC]-[IN]                     |                                 |                                                                                                                           |

|                                    | 2. Send DATA1(0)                |                                                                                                                           |

| 3. If CRC OK,<br>Send [SYNC]-[ACK] |                                 |                                                                                                                           |

|                                    | 4. Set TX_Complete bit          |                                                                                                                           |

|                                    |                                 | 5. INTERRUPT                                                                                                              |

|                                    |                                 | 6. Read UISR                                                                                                              |

|                                    |                                 | 7. Read CSR                                                                                                               |

|                                    |                                 | 8. Clear TX_Complete bit                                                                                                  |

|                                    |                                 | 9. Clear Data_End bit                                                                                                     |

|                                    |                                 | 10. Set FORCE_STALL bit                                                                                                   |

|                                    |                                 | 11. SET UIAR (EP0 INTA)                                                                                                   |

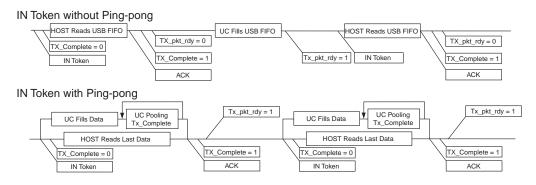

# Interrupt and Bulk IN Transfers

- 1. The USB Hardware automatically starts the endpoint in receive mode and NAKs all IN tokens as long as bit CSR[TX Packet Ready] is cleared.

- The processor checks bit CSR[TX Packet Ready]. If it is "0", writes the data into the FIFO, then sets CSR[TX Packet Ready].

- 3. At the next IN token, the USB Hardware sends the packet out and waits for an ACK. Until an ACK is received, the USB Hardware will retransmit the packet.

After receiving an ACK, the USB Hardware clears bit CSR[TX Packet Ready], signaling a successful completion to the processor.

Figure 4. IN Token with and without Ping-pong

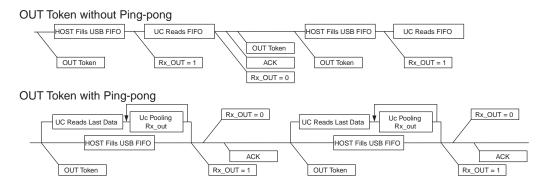

# Interrupt and Bulk OUT Transfers

The USB Hardware automatically starts the endpoint in receive mode. When an OUT token is received and if CSR[RX OUT Packet] is cleared, it stores the data in the FIFO. It ACKs the host if the data received are not corrupted, and then interrupts the processor. If CSR[RX OUT Packet] is set, the USB Hardware responds with a NAK to the incoming OUT token: The processor checks CSR[RX OUT Packet] and if it is "1", it reads the data from the FIFO and clears CSR[RX OUT Packet Ready].

Figure 5. OUT Token with and without Ping-pong

# Interrupt and Isochronous Transfers

Isochronous transfers use the same protocol with bulk transfers except that error correction and data packet retransmission are not supported:

- No ACK token

- No NAK token

- Data PID is always zero

# Interrupt and Interrupt IN Transfers

Interrupt transfers use the same protocol with bulk IN transfers (Interrupt OUT is not supported in USB Spec 1.0).

# Suspend

A USB device enters the suspend mode only when requested by the USB host through bus inactivity for at least 3 ms. The USB Hardware detects this request, sets the SUSP bit of the Suspend/Resume Register (SPRSR), and interrupts the processor if the interrupt is enabled. The processor should shutdown any peripheral activity, enter powerdown mode and signal the USB Hardware that it can now enter the suspend mode by writing "1" to the "sleep mode" USB\_Macro input pin. At this moment, the "Suspend2SIE" output pin is activated and the oscillator, PLL and other peripherals should be disabled.

# Resume

Resume is signaled by a J- to K-state transition at the USB port. The USB Hardware enables the oscillator/PLL and sets the RSM bit of the SPRSR, which generates an interrupt. The processor starts executing where it left off and services the interrupt. Then the firmware clears the RCVD RSM bit.

# Remote Wake-up

While the USB peripheral is in suspend mode, resuming is also possible through the remote wake-up feature. Remote wake-up is invoked due to an external event (such as the detection of a key pressing in a keyboard) and is denoted by the "Ext\_int" USB\_Macro pins (active high). This action, in turn, enables the oscillator and the USB Hardware. The USB Hardware sets the associated flag of UISR and the EXT RSM bit of SPRSR. These generate two interrupts to the processor: Ext\_int and RSM\_int. The processor starts executing where it left off and services the interrupt. Then the firmware clears the EXT RSM bit and EXT[0-3] bit.

If the remote wake-up feature is enabled and the USB bus remains idle for a period of 5 ms (already 3 ms in the suspend mode), the resume signal is sent to the host during the next 10 ms and the RSMINPR bit of the Global State Register is set.

# **AVR Microcontroller**

The AT76C711 is based on the AVR architecture and includes many of the features of the AVR AT90S8515 microcontroller. All peripherals, apart from SPI and timers, are memory mapped to the data address space.

# **Interrupt Handling**

The interrupt vector table of AT76C711 is shown below.

Table 1. AT76C711 Interrupt Vectors

| Vector # | Program<br>Address | Source       | Interrupt Definition            |

|----------|--------------------|--------------|---------------------------------|

| 1        | \$0000             | RESET        | Hardware Pin and Watchdog Reset |

| 2        | \$0002             | SUSP/RESM    | USB Suspend and Resume          |

| 3        | \$0004             | INT0         | External Interrupt Request 0    |

| 4        | \$0006             | TIMER1 CAPT  | Timer/Counter1 Capture Event    |

| 5        | \$0008             | TIMER1 COMPA | Timer/Counter1 Compare Match A  |

| 6        | \$000A             | TIMER1 COMPB | Timer/Counter1 Compare Match B  |

| 7        | \$000C             | TIMER1 OVF   | Timer/Counter1 Overflow         |

| 8        | \$000E             | TIMER0 OVF   | Timer/Counter0 Overflow         |

| 9        | \$0010             | SPI, STC     | SPI Serial Transfer Complete    |

| 10       | \$0012             | TDMAC        | Tx DMA Termination              |

| 11       | \$0014             | UARTO INT    | UART0 Interrupt Request         |

| 12       | \$0016             | RDMAC        | Rx DMA Termination              |

| 13       | \$0018             | USB Hardware | USB Hardware Interrupt          |

| 14       | \$001A             | UART1 INT    | UART1 Interrupt Request         |

| 15       | \$001C             | INT1         | External Interrupt Request 1    |

# Oscillator and Clock Generator

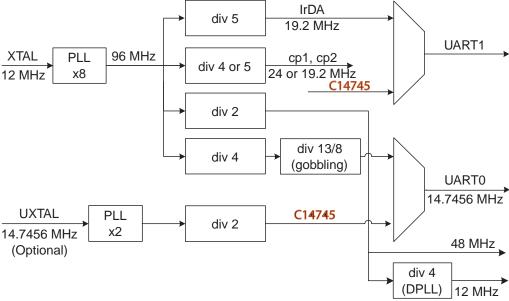

AT76C711 has two on-chip crystal oscillators. The first one is the main oscillator and is used to generate the clocks of the AVR CPU and the 48 MHz clock of the USB core. The nominal value of this oscillator should be 12 MHz. After the initial reset, the default CPU rate is 24 MHz. Dividing the 48 MHz clock appropriately, an internal clock of 14.746 MHz is produced, which can be used for generating standard modem baud rates with a deviation of 1.6 percent.

Alternatively, if a strict baud rate is required, a dedicated oscillator for the UART block is provided. The Clock Tree Circuit is shown in Figure 6. The output pins of the crystal oscillators are not designed to drive any external circuits. Instead of using crystals, either oscillator's input pin can also be driven by an external clock signal.

Figure 6. Clock Tree Circuit

# **UARTO**

The main features of UART0 are:

- Programmable Baud Rate Generator

- 16-byte FIFO at the Receiver Side

- Parity, Framing and Overrun Error Detection

- Line Break Generation and Detection

- Automatic Echo, Local Loopback and Remote Loopback Channel Modes

- Interrupt Generation

- Two Dedicated Controller Channels

- 5-, 6-, 7- and 8-bit Character Length

- Maximum Rate 921.6K Baud

- Interface to a DMA Controller for Fast Data Transfers to/from the DPRAM

The input to the baud rate generator is selectable between a 14.746 MHz clock (derived from the internal clock generator) or the dedicated UART oscillator. Both the DMA controller and the AVR processor can have access to the UART registers. The arbitration of the UART memory bus is implemented internally to the DMA controller.

# Receiver

The UART detects the start of a received character by sampling the RxD signal until it detects a valid start bit. A low level (space) on RxD is interpreted as a valid start bit if it is detected for more than 7 cycles of the sampling clock, which is 16 times the baud rate. Hence a space that is longer than 7/16 of the bit period is detected as a valid start bit. A space that is 7/16 of a bit period or shorter is ignored and the receiver continues to wait for a valid start bit. When a valid start bit has been detected, the receiver samples the RxD at the theoretical midpoint of each bit. It is assumed that each bit lasts 16 cycles of the sampling clock (1 bit period) so the sampling point is 8 cycles (0.5 bit periods) after the beginning of the bit. Therefore, the first sampling point is sampled 24 cycles (1.5 bit periods) after the falling edge of the start bit was detected. Each subsequent bit is sampled 16 cycles (1 bit period) after the previous one.

# **Receive FIFO Operation**

The 16-byte receive data FIFO is enabled by the (US\_FCR) bit 0. The user can set the receiver trigger level. The receiver FIFO section includes a timeout function to ensure data is delivered to the external CPU. An interrupt is generated whenever the Receive Holding Register (US\_RHR) has not been read after the loading of a character or if the trigger level has been reached.

# **Timeout**

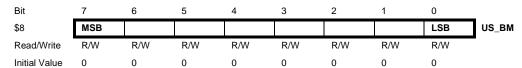

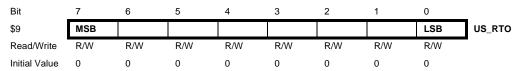

This function allows an idle condition on the RxD line to be detected. The maximum delay for which the UART should wait for a new character to arrive while the RxD line is inactive (high level) is programmed in US\_RTO (Receiver Timeout). When this register is set to "0", no timeout is detected. Otherwise, the receiver waits for a first character and then initializes a counter, which decrements at each bit period and is reloaded at each byte reception. When the counter reaches "0", the timeout bit (bit 6) in US\_CSR is set. The user can restart waiting for a first character by setting the start timeout bit (bit 4) of US\_CR Register. The timeout duration is:

Duration = Value x \_ 4 \_ x \_ Bit Period

# **Receive Break**

The break condition is detected by the receiver when all data, parity and stop bits are low. At the moment of the low stop bit detection, the receiver asserts receive break (bit 2) in US\_CSR. The end of receive break is detected by a high level for at least 2/16 of the bit period. Receive break (bit 2) is also set after the end of break has been detected.

# **Transmitter**

The start bit, data bits, parity bit and stop bits are serially shifted, with the least significant bit first, on the falling edge of the serial clock. The number of data bits is selected in the character length field, (bits 7 and 6) in US\_PMR. The parity bit is set according to the parity type bit 1 field in US\_PMR. The number of stop bits is selected in the number of stop (bits 4, 5) field in US\_MR. When a character is written to US\_THR (Transmit Holding), it is transferred to the Shift Register as soon as it is empty. When the transfer occurs, the transmit ready (bit 1) in US\_CSR is set until a new character is written to US\_THR. If the Transmit Shift Register and US\_THR are both empty, the transmitter empty (bit 7) in US\_CSR is set.

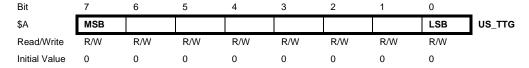

# Time-guard

The time-guard function allows the transmitter to insert an idle state on the TxD line between two characters. The duration of the idle state is programmed in US \_TTG (Transmitter Time-guard). When this register is set to "0", no time-guard is generated. Otherwise, the transmitter holds a high level on TxD after each transmitted byte during the number of bit periods programmed in US\_TTG.

# **Transmit Break**

The transmitter can generate a break condition on the TxD line when the Start Break command (bit 0) is set in US\_CR (Control Register). In this case, the characters present in US\_THR and in the Transmit Shift Register are completed before the line is held low. To remove this break condition on the TxD line, the Stop Break command (bit 1) in US\_CR must be set. The UART generates minimum break duration of one character length. The TxD line then returns to high level (idle state) for at least 12-bit periods to ensure that the end of break is correctly detected. Then the transmitter resumes normal operation.

# **Interrupt Generation**

Each status bit in US\_CSR has a corresponding bit in US\_IER (Interrupt Enable) that controls the generation of interrupts by asserting the UART interrupt line. Any of the Parity, Framing or overrun Error condition generate a line? Error Interrupt. Interrupt sources are given in the register description section.

# **Channel Modes**

The UART can be programmed to operate in three different test modes using the field Channel Mode (bits 6 and 7) in US\_MR. Automatic echo mode allows bit-by-bit retransmission. When a bit is received on the RxD line, it is sent to the TxD line. Programming the transmitter has no effect.

The local loopback mode allows the transmitted characters to be received. TxD and RxD pins are not used and the output of the transmitter is internally connected to the input of the receiver. The RxD pin level has no effect and the TxD pin is held high, as in the idle state.

The remote loopback mode directly connects the RxD pin to the TxD pin. The transmitter and the receiver are disabled and have no effect. This mode allows bit-by-bit retransmission.

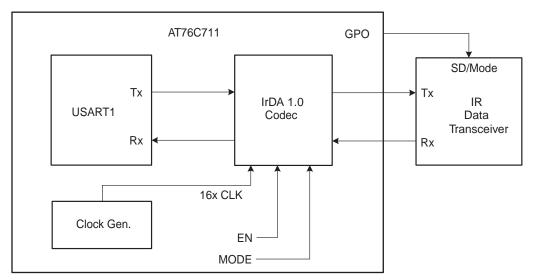

#### UART1 - IrDA Codec

The IrDA codec provides an IrDA 1.0 standard interface. It is connected to the SIN and SOUT of UART1. The IRDAMOD Register of the I/O register set selects the operation mode of the IrDA codec.

The EN bit activates the module. When it is deactivated, the UART signals are connected directly to the external interface, bypassing the IrDA codec block. Otherwise, it encodes the outgoing and decodes the incoming data from and to the UART1 respectively, according to the IrDA 1.0 standard (3/16 modulation).

The MODE bit gives the user the capability to change the modulation scheme from 3/16 pulse width to 4/16.

The UART settings should be half-duplex to avoid signal interference. The UART1 register set is similar to that of UART0: its base address is 2030/hex.

The IrDA codec transmits a 3/16 pulse width on zeros (0) and nothing on ones (1). In receive operations, it extends the incoming zeros to 16/16 pulse and feeds them reversed to the UART1 SIN (see "IrDA Serial Infrared Physical Layer Specification" at www.irda.org/standards).

An internally generated clock of 19.2 MHz makes it possible to use the IrDA module for up to 1.2 Mbps transfer rates (much higher than the typical 115.2 Kbps). This capability offers a simple solution for high-speed infrared communications.

The input to the baud rate generator of UART1 is selectable between the 19.2 MHz clock and the clock of the dedicated oscillator for standard modem rates.

A typical application of the AT76C711 connection to an external IR Data Transceiver when the IrDA module is enabled is shown in Figure 7. The GPO is a general-purpose output (can be provided from the data ports).

Figure 7. AT76C711 Connection to External IR Data Transceiver, IrDA Module Enabled

# **DMA Controller**

The DMA controller is able, under firmware control, to transfer data between the DPRAM and the UART, without the intervention of the processor. The DMA controller will interrupt the processor as soon as it transfers the processor-preprogrammed number of bytes. During data transfers from the DMA controller, the Transmit and Receive DMA Status registers are updated with possible errors indicated by the UART. These status registers can be read by the processor, after the DMA controller's interrupt at the end of a block transfer, to report if the block transfer was error free or not.

The DMA controller is programmed by the processor to transfer blocks of data between the DPRAM and the UART core. In addition, the UART can be accessed by the processor only through the DMA controller module. Thus, data transfers between the processor and other memory devices are not interrupted when DMA transfers occur.

Segmentation and reassembly of the transmitted/received packets through the UART are also executed with the aid of the DMA controller, under firmware control. Reassembly of network packets is implemented by storing the USB packets from a certain endpoint in successive address spaces. The DMA controller is then programmed to consecutively transfer the bytes of the reassembled packet that has been formed. On the other hand, during packet reception from the UART, the processor can program the DMA controller to read a certain number of bytes from the UART's FIFO and store them at a given target address, depending on the packet header. After the end of the DMA transfer, an interrupt is issued by the DMA controller to signal the processor to check for possible errors during this transfer and forward the packet to the EPs of the USB interface.

The DMA controller is programmed with the characteristics of a DMA transfer before it is enabled. The only information that is required is the DPRAM target address and the packet length, because it is already aware of the segment boundaries in order to perform wraparound inside the corresponding segment. In addition, status registers provide information related to errors encountered during a DMA transfer. Two of the above sets of registers are implemented, one for each direction.

Transmit and receive DMAs are performed by polling the TXRDY and RXRDY signals of the UART. A DMA operation consists of reading the UART status registers and accessing the Data Hold Register. Transmit and receive DMA operations can take place simultaneously.

Whenever a receive DMA operation is terminated, either normally or by a Receive Character Timeout Interrupt from the UART or forced by the firmware, an internal RDMAC interrupt signal from DMA is issued to the processor. After that, the firmware should read RXTPLL and RXTPLM to be informed about the exact number of the received bytes, possible errors during DMA and the reason for the DMA termination.

After a transmit DMA termination, either normally or forced by firmware, an internal TDMAC interrupt signal from the DMA is issued to the processor. After that, the firmware should read TXTPLL and TXTPLM to be informed about the exact number of the transmitted bytes and the reason for DMA termination.

# **DPRAM Organization**

DPRAM organization is related to the length of the packets transferred through UART. The programmer can define segments in the DPRAM address space from DPORG Register of the DMA controller. Memory segmentation facilitates wraparound during DMA transfers. According to the number of segments, the DMA controller can determine the END and START address of each segment so it doesn't need to be informed about the segment boundaries each time a transfer is enabled. The default state is the DPRAM being unsegmented. Details of the possible DPRAM segmentation schemes are given at the description of the DPORG Register of the DMA controller.

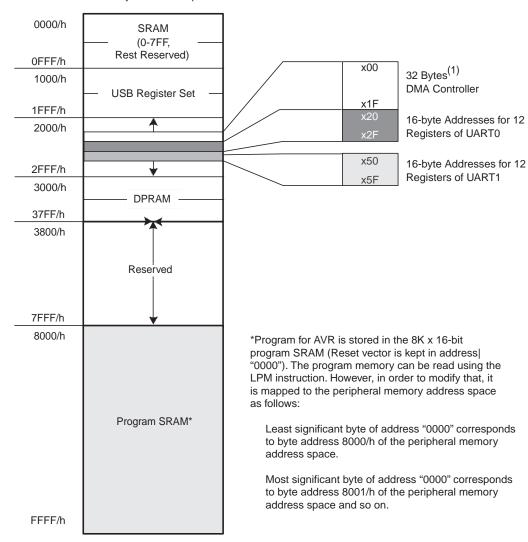

# **Mapping Allocations**

The AVR uses a 16-bit address bus to have access to 64-Kbyte memory locations. In AT76C711 design this memory is shared among the various peripherals as shown in Figure 8.

| Address Space | Size        | Module                                  |

|---------------|-------------|-----------------------------------------|

| 0000 - 07FF   | 2048 bytes  | SRAM                                    |

| 0800 - 0FFF   | 2048 bytes  | Reserved                                |

| 1000 - 1FFF   | 4096 bytes  | USB (not all of the locations are used) |

| 2000 - 201F   | 32 bytes    | DMA controller                          |

| 2020 - 202F   | 16 bytes    | UART0                                   |

| 2030 - 203F   | 16 bytes    | UART1                                   |

| 2040          | 1 byte      | Program Memory Control bit              |

| 2041 - 2FFF   | 4031 bytes  | Reserved                                |

| 3000 - 37FF   | 2048 bytes  | DPRAM                                   |

| 3800 - 7FFF   | 18432 bytes | Reserved                                |

| 8000 - 7FFF   | 16384 bytes | Program SRAM                            |

| 7FFF - FFFF   | 16384 bytes | Reserved                                |

Figure 8. Memory Allocation for On-chip Resources

64-Kbyte Address Space

Note: 1. These register blocks are mapped to any 256-byte boundary (x00) in address space 2000 - 2FFF/h.

# **I/O Memory**

The I/O space definition of AT76C711 is shown in Table 2. This space is defined in the area \$00 - \$3F and can be directly accessed by IN and OUT instructions or by ordinary SRAM accesses in the area \$20 - \$5F. The notation used will be followed in the rest of this document. A more detailed description of the I/O memory space is given in the sections that follow.

Table 2. AT76C711 I/O Space

| I/O Address<br>(SRAM Address) | Name    | Function                                   |  |  |

|-------------------------------|---------|--------------------------------------------|--|--|

| \$3F(\$5F)                    | SREG    | Status Register                            |  |  |

| \$3E(\$5E)                    | SPH     | Stack Pointer High                         |  |  |

| \$3D(\$5D)                    | SPL     | Stack Pointer Low                          |  |  |

| \$39(\$59)                    | EIMSK   | External Interrupt Mask Register           |  |  |

| \$37(\$57)                    | TIMSK   | Timer Interrupt Mask Register              |  |  |

| \$36(\$56)                    | TIFR    | Timer Interrupt Flag Register              |  |  |