### High Performance 128K×8 5V CMOS Flash EEPROM

## $128K \times 8$ CMOS Flash EEPROM

#### Features

- Organization:128K × 8 bits

- Sector Erase architecture

- Four  $32K \times 8$  sectors

- Single  $5.0\pm0.5V$  power supply for read/write operations

- High speed 120/150 ns address access time

- Low power consumption:

- 30 mA maximum read current

- 50 mA maximum program current

- 1.5 mA maximum standby current

- 1 mA maximum standby current (low power)

- 10,000 write/erase cycle endurance

- JEDEC standard write cycle commands - protects data from accidental changes

- Program/erase cycle end signals:

- Data polling

- DQ6 toggle

- $\bullet$  Low  $V_{CC}$  write lock-out below 3.2V

- JEDEC standard packages and pinouts:

- 32-pin DIP

- 32-pin PLCC

- 32-pin TSOP

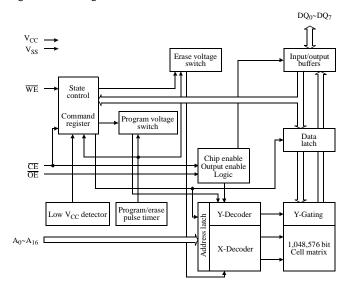

#### Logic block diagram

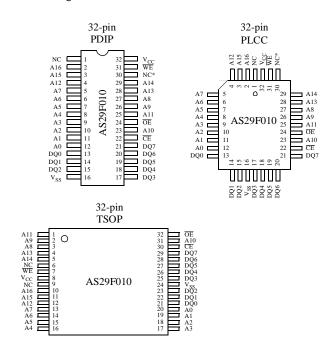

### Pin arrangement

## Selection guide

|                           |                 | 29F010-120 | 29F010-150 | Unit |

|---------------------------|-----------------|------------|------------|------|

| Maximum access time       | t <sub>AA</sub> | 120        | 150        | ns   |

| Chip enable access time   | t <sub>CE</sub> | 120        | 150        | ns   |

| Output enable access time | t <sub>OE</sub> | 50         | 50         | ns   |

# ALLIANCE SEMICONDUCTOR

#### Functional description

The AS29F010 is a high performance 1 megabit 5 volt-only Flash memory organized as 128K bytes of 8 bits each. It is divided into four sectors of 32K bytes each. Each sector is separately erased and programmed without affecting data in the other sectors. All program, erase, and verify operations are 5-volt only, and require no external 12V supply pin. All required features for in-system programmability are provided.

The AS29F010 provides high performance with a maximum access time of 120, or 150 ns. Chip Enable ( $\overline{\text{CE}}$ ), Output Enable ( $\overline{\text{OE}}$ ), and Write Enable ( $\overline{\text{WE}}$ ) pins allow easy interface with the system bus.

Program, erase, and verify operations are controlled with an on-chip command register using a JEDEC standard Write State Machine approach to enter commands. Each command requires four write cycles to be executed. Address and data are latched internally during all write, erase, and verify operations, and an internal timer terminates each command. The chip has a typical timer period of 200 µs for all commands but Erase, which has a typical period of 800 ms. Under nominal conditions, a sector can be completely programmed and verified in less than 12 seconds. To program, erase, and verify a sector typically takes less than 18 seconds.

Data protection is provided by a low- $V_{CC}$  lockout and by error checking in the Write State Machine. DATA polling and Toggle Bit modes are used to show that the chip is executing a command when the AS29F010 is read during a write or erase operation. After Erase or Program commands, Verify-1 and Verify-0 command modes ensure sufficient margin for reliable operation. (See command summary on page 5.)

The AS29F010 is packaged in 32-pin DIP, PLCC and TSOP packages with JEDEC standard pinouts for one megabit Flash memories.

#### Array architecture and data polarity

The array consists of 128K (131,072) bytes divided into four sectors of 32K bytes each. Addresses A15 and A16 select the four sectors:

| Sector | Address range | Address pins | Function                    |

|--------|---------------|--------------|-----------------------------|

| 0      | 00000h-07FFFh | A0-A5        | CA: Column addresses 00-3Fh |

| 1      | 08000h–0FFFh  | A6-A14       | RA: Row addresses 000–1FFh  |

| 2      | 10000h-17FFFh | A15-A16      | SA: Sector addresses 0-3h   |

| 3      | 18000h–1FFFFh |              |                             |

The AS29F010 is shipped in the erased state with all bits set to 1. Programmed bits are set to 0. Data is programmed into the array one byte at a time. All programmed bits remain set to 0 until the sector is erased and verified using the Sector Erase and Verify algorithm. Erase returns all bytes in a 32K sector to the erased state FFh, or all bits set to 1. Each sector is erased individually with no effect on the other sectors.

## Operating modes

The AS29F010 is controlled by a Write State Machine (WSM) that interprets and executes commands. At power-up the WSM is reset to normal read mode. Once a command is initiated by writing data into the DQ pins with the  $\overline{WE}$  pin, the WSM enters the command mode and keeps the chip powered up until the command is finished. After the command is terminated by the internal timer, the WSM returns to the normal read mode.

#### Mode table

| Mode           | CE | ŌĒ | WE | A0 | A9 | DQ               |

|----------------|----|----|----|----|----|------------------|

| Read           | L  | L  | Н  | A0 | A9 | D <sub>OUT</sub> |

| Output disable | L  | Н  | Н  | Х  | Х  | High Z           |

| Standby        | Н  | Н  | Н  | Х  | Х  | High Z           |

| Mfr. code      | L  | L  | Н  | L  | Vh | 52h              |

| Device code    | L  | L  | Н  | Н  | Vh | 04h              |

| Write command  | L  | Н  | L  | A0 | A9 | D <sub>IN</sub>  |

<sup>†</sup>**Key:** L =Low ( $\langle V_{IL}$ ); H = High ( $\rangle V_{IH}$ ); Vh = 11.5–12.5V; X =Don't care

**Read mode**: Selected with  $\overline{CE}$  and  $\overline{OE}$  low,  $\overline{WE}$  high. Data is valid  $t_{AA}$  after addresses are stable,  $t_{CE}$  after  $\overline{CE}$  is low and  $t_{OE}$  after  $\overline{OE}$  is low.

Output disable: Part remains powered up; but outputs disabled with OE pulled high.

Standby: Part is powered down, and I<sub>CC</sub> reduced to 1.5 mA for TTL input levels (<1.0 mA for CMOS input levels).

**Mfr.** (manufacturer) **code**, **Device code**: Selected by A9 = 11.5–12.5V. When  $\overline{CE}$  and  $\overline{OE}$  are pulled low the outputs are enabled and a data byte is read out. When A0 is pulled low the output data = 52h, a unique Mfr. code for Alliance Semiconductor Flash products. When A0 is high  $D_{OUT} = 04h$ , the Alliance device code for the AS29F010.

**Write command:** Selected by  $\overline{CE}$  and  $\overline{WE}$  pulled low,  $\overline{OE}$  pulled high. Initiates command mode in the WSM and latches addresses and data into the chip. Once a write command starts, the WSM stays in command mode until the command is completed or it times out. Addresses are latched on the falling edge of  $\overline{WE}$  and  $\overline{CE}$ , whichever occurs later; data is latched on the rising edge of  $\overline{WE}$  and  $\overline{CE}$ , whichever occurs first. The  $\overline{WE}$  signal is filtered to prevent spurious events from being detected as write commands.

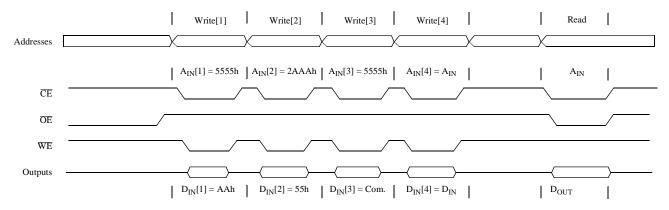

#### Command format

All commands require four bus write cycles to execute. After four write cycles the command is executed until terminated by the internal timer. For verify commands a read operation after  $Write_{[4]}$  in a write command bus cycle reads out the data from the array. For manufacturer and device code commands the ID code is read out. For other operations a read operation reads out a status byte on the outputs.

|                          | Address in | Data in          |

|--------------------------|------------|------------------|

| Bus write <sub>[1]</sub> | 5555h      | AAh              |

| Bus write <sub>[2]</sub> | 2AAAh      | 55h              |

| Bus write <sub>[3]</sub> | 5555h      | Command code     |

| Bus write <sub>[4]</sub> | Address in | Data in          |

| Bus read                 | Address in | D <sub>OUT</sub> |

**Command timeout**: For each operation the address and data are latched at bus  $Write_{[4]}$  and held until the operation completes and times-out. After time-out the WSM returns the AS29F010 to normal mode. Each individual operation requires the 4-cycle write command sequence to execute. The AS29F010 does not remain in command mode after time-out. When a command times-out only the error flag is not reset.

Errors and timeout: Any of the following conditions sets the error flag.

- Any write command which does not match the sequence above for Write [1]. Write [2], and Write [3].

- Any write cycle that follows more than 150 µs after the previous write cycle.

- The command Data<sub>[3]</sub> in Write<sub>[3]</sub> has more than one bit set high. This indicates conflicting commands.

- +  $V_{CC}$  drops below  $V_{LKO}$  during command execution.

Once the error flag is set, the AS29F010 times out and returns to normal Readmode. The error flag remains until it is cleared by a reset command. The error flag can be read by executing a status command and reading the status byte.

#### Command codes and time out

The Command Code table displays the bus cycles required for each command mode. Read delay is the minimum delay after  $Write_{[4]}$  during a write command bus cycle before a valid read may be executed. Timeout indicates the maximum delay before the WSM returns the AS29F010 to normal mode. Erase has a longer timeout than the other modes. Status byte can be read almost immediately after a  $Write_{[4]}$ , but the verify commands require a 25 µs delay to read valid data.

## Command code table

| Mode            | D <sub>IN[3]</sub><br>Write <sub>[3]</sub> data | A <sub>IN[4]</sub><br>Write <sub>[4]</sub> address | D <sub>IN[4]</sub> data | Read address    | Read data                |            | Read delay       | Maximum time out |

|-----------------|-------------------------------------------------|----------------------------------------------------|-------------------------|-----------------|--------------------------|------------|------------------|------------------|

| Reset           | 00h                                             | Х                                                  | х                       | 0000h           | Status                   |            | 100 ns           | 250 μs           |

| Status          | 01h                                             | Х                                                  | X                       | 0000h           | Status                   |            | 100 ns           | 250 µs           |

| ID Read<br>code | 02h                                             | 0000h<br>0001h                                     | x<br>x                  | 0000h<br>0001h  | Mfr. code<br>Device code | 52h<br>04h | 100 ns<br>100 ns | 250 µs           |

| Verify-0        | 04h                                             | A <sub>IN</sub>                                    | Х                       | A <sub>IN</sub> | D <sub>OUT</sub>         |            | 25 µs            | 250 μs           |

| Verify-1        | 08h                                             | A <sub>IN</sub>                                    | х                       | A <sub>IN</sub> | D <sub>OUT</sub>         |            | 25 µs            | 250 µs           |

| Converge        | 10h                                             | A <sub>IN</sub>                                    | 00h                     | A <sub>IN</sub> | Status                   |            | 100 ns           | 250 µs           |

| Program         | 40h                                             | A <sub>IN</sub>                                    | $D_{IN}$                | A <sub>IN</sub> | Status                   |            | 100 ns           | 250 µs           |

| Erase           | 80h                                             | A <sub>IN</sub>                                    | FFh                     | $A_{IN}$        | Status                   |            | 100 ns           | 1000 µs          |

## Command algorithms

Individual write commands are used together in eight program and erase algorithms to guarantee the 29F010 operating margins for the life of the part. Refer to the AS29F010 Programming Specification for details on the algorithms for program and erase operations.

| Recommended operating conditions |                 |      |     | $(T_a = 0^{\circ}C to$ | o +70°C) |

|----------------------------------|-----------------|------|-----|------------------------|----------|

| Parameter                        | Symbol          | Min  | Тур | Max                    | Unit     |

|                                  | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                    | V        |

| Supply voltage                   | V <sub>SS</sub> | 0    | 0   | 0                      | V        |

| T                                | V <sub>IH</sub> | 2.0  | -   | $V_{CC} + 1.0$         | V        |

| Input voltage                    | V <sub>IL</sub> | -0.5 | -   | 0.8                    | V        |

## Absolute maximum ratings

| Parameter                       | Symbol           | Min  | Max            | Unit |

|---------------------------------|------------------|------|----------------|------|

| Input voltage (Input or DQ pin) | V <sub>IN</sub>  | -1.0 | $V_{CC} + 1.0$ | V    |

| Input voltage (A9 pin)          | V <sub>IN</sub>  | -1.0 | +13.0          | V    |

| Output voltage                  | V <sub>OUT</sub> | -1.0 | $V_{CC} + 1.0$ | V    |

| Power supply voltage            | V <sub>CC</sub>  | +4.5 | +5.5           | V    |

| Operating temperature           | T <sub>OPR</sub> | -55  | +125           | °C   |

| Storage temperature (plastic)   | T <sub>STG</sub> | -65  | +125           | °C   |

| Short circuit output current    | I <sub>OUT</sub> | -    | 100            | mA   |

| Latch-up current                | I <sub>IN</sub>  | -    | ±100           | mA   |

Stresses greater than those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

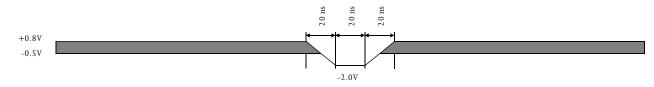

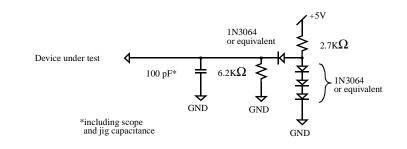

Maximum negative overshoot waveform

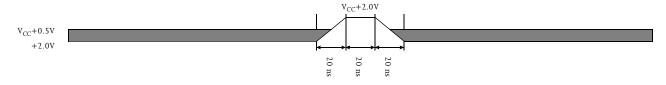

## Maximum positive overshoot waveform

| DC electrical characteristics        |                         | $(V_{CC} = 5)$                                                                               | $.0\pm0.5$ V, $V_{SS} =$ | $0V, T_a = 0^{\circ}C$ | to +70°C) |

|--------------------------------------|-------------------------|----------------------------------------------------------------------------------------------|--------------------------|------------------------|-----------|

| Parameter                            | Symbol                  | Test conditions                                                                              | Min                      | Max                    | Unit      |

| Input load current                   | $I_{LI}$                | $V_{IN} = V_{SS}$ to $V_{CC}$ , $V_{SS} = V_{MAX}$                                           | -                        | ±1                     | μΑ        |

| Output leakage current               | I <sub>LO</sub>         | $V_{OUT} = V_{SS}$ to $V_{CC}$ , $V_{SS} = V_{MAX}$                                          | -                        | ±1                     | μΑ        |

| Output short circuit current         | I <sub>OS</sub>         | $V_{OUT} = 0.5V$                                                                             | -                        | 100                    | mA        |

| Active current, read @ 6MHz          | I <sub>CC</sub>         | $\overline{\text{CE}} = \text{V}_{\text{IL}}, \ \overline{\text{OE}} = \text{V}_{\text{IH}}$ | -                        | 30                     | mA        |

| Active current, program/erase        | I <sub>CCPRG</sub>      | $\overline{\text{CE}} = \text{V}_{\text{IL}}, \ \overline{\text{OE}} = \text{V}_{\text{IH}}$ | -                        | 50                     | mA        |

|                                      | $I_{SB1}$ (TTL)         | $\overline{\text{CE}} = \text{V}_{\text{IH}}$                                                | -                        | 1.5                    | mA        |

| Standby current                      | I <sub>SB2</sub> (CMOS) | $\overline{\text{CE}} = \text{V}_{\text{CC}}$                                                | -                        | 1.0                    | mA        |

|                                      | I <sub>CCPD</sub>       | $\overline{RP} = 0V$                                                                         | -                        | 2                      | μΑ        |

| Input: low level                     | V <sub>IL</sub>         |                                                                                              | 0.5                      | 0.8                    | V         |

| Input: high level                    | V <sub>IH</sub>         |                                                                                              | 2.0                      | $V_{SS} + 0.3$         | V         |

| Output low voltage                   | V <sub>OL</sub>         | $I_{OL} = 12mA$                                                                              | -                        | 0.45                   | V         |

| Output high loval                    | V <sub>OH1</sub>        | $I_{OH} = -2.5 \text{ mA}$                                                                   | 2.4                      | -                      | V         |

| Output high level                    | V <sub>OH2</sub>        | $I_{OH} = -100 \ \mu A$                                                                      | V <sub>CC</sub> - 0.4    | -                      | V         |

| Low V <sub>CC</sub> lock out voltage | V <sub>LKO</sub>        |                                                                                              | 3.2                      | 4.2                    | V         |

| Input HV select voltage              | V <sub>ID</sub>         |                                                                                              | 11.5                     | 12.5                   | V         |

#### Notes

1 Not more than one output tested simultaneously. Duration of the short circuit must not be >1 second. V<sub>OUT</sub> = 0.5V was selected to avoid test problems caused by tester ground degradation. (This parameter is sampled and not 100% tested, but guaranteed by characterization.)

2 The I<sub>CC</sub> current listed includes both the DC operating current and the frequency dependent component (@ 6 MHz). The frequency component typically is less than 2 mA/MHz with  $\overline{\text{OE}}$  at V<sub>IH</sub>.

3  $I_{CC}$  active while program or erase operations are in progress.

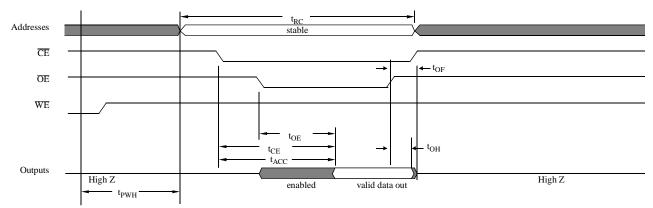

# AC parameters — read cycle

$(V_{CC} = 5.0 \pm 0.5 V, V_{SS} = 0 V, T_a = 0^{\circ}C \text{ to } +70^{\circ}C)$

|                   |                  |                                                                                                       | - 1 | 20  | -1  | 50  |      |

|-------------------|------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|

| JEDEC symbol      | Std symbol       | Parameter                                                                                             | Min | Max | Min | Max | Unit |

| t <sub>AVAV</sub> | t <sub>RC</sub>  | Read cycle time                                                                                       | 120 | -   | 150 | -   | ns   |

| t <sub>AVQV</sub> | t <sub>ACC</sub> | Address to output delay                                                                               | -   | 120 | -   | 150 | ns   |

| t <sub>ELQV</sub> | t <sub>CE</sub>  | Chip enable to output                                                                                 | -   | 120 | -   | 150 | ns   |

| t <sub>GLQV</sub> | t <sub>OE</sub>  | Output enable to output                                                                               | -   | 50  | -   | 50  | ns   |

| t <sub>EHQZ</sub> | t <sub>DF</sub>  | Chip enable to output High Z                                                                          | -   | 30  | -   | 30  | ns   |

| t <sub>GHQZ</sub> | t <sub>DF</sub>  | Output enable to output High Z                                                                        | -   | 30  | -   | 30  | ns   |

| t <sub>AXQX</sub> | t <sub>OH</sub>  | Output hold time from addresses, first occurrence of $\overline{\text{CE}}$ or $\overline{\text{OE}}$ | 0   | _   | 0   | -   | ns   |

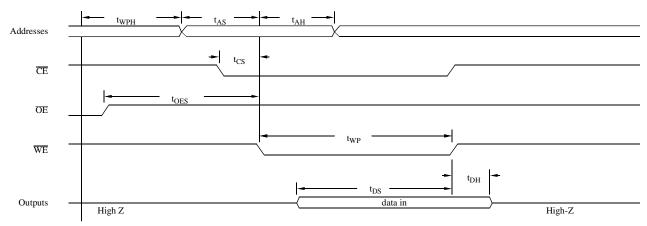

# AC parameters — write cycle

$(V_{CC} = 5.0 \pm 0.5 V, V_{SS} = 0V, T_a = 0^{\circ}C \text{ to } +70^{\circ}C)$

| -                  |                    | ,                                                   |      |      |      |      |      |

|--------------------|--------------------|-----------------------------------------------------|------|------|------|------|------|

|                    |                    |                                                     |      | -120 |      | -150 |      |

| JEDEC symbol       | Std symbol         | Parameter                                           | Min  | Max  | Min  | Max  | Unit |

| t <sub>AVAV</sub>  | t <sub>WC</sub>    | Write cycle time                                    | 120  | -    | 150  | -    | ns   |

| t <sub>AVWL</sub>  | t <sub>AS</sub>    | Address setup time                                  | 0    | -    | 0    | -    | ns   |

| t <sub>WLAX</sub>  | t <sub>AH</sub>    | Address hold time                                   | 50   | -    | 50   | -    | ns   |

| t <sub>DVWH</sub>  | t <sub>DS</sub>    | Data setup time                                     | 50   | -    | 50   | -    | ns   |

| t <sub>WHDX</sub>  | t <sub>DH</sub>    | Data hold time                                      | 0    | -    | 0    | -    | ns   |

|                    | t <sub>OES</sub>   | Output enable setup time                            | 0    | -    | 0    | -    | ns   |

|                    |                    | Output enable hold time: Read                       | 0    | -    | 0    | -    | ns   |

|                    | t <sub>OEH</sub>   | Output enable hold time:<br>Toggle and DATA polling | 10   | -    | 10   | -    | ns   |

| t <sub>GHWL</sub>  | t <sub>GHWL</sub>  | Read recover time before write                      | 0    | -    | 0    | -    | ns   |

| t <sub>ELWL</sub>  | t <sub>CS</sub>    | CE setup time                                       | 0    | -    | 0    | -    | ns   |

| t <sub>WHEH</sub>  | t <sub>CH</sub>    | CE hold time                                        | 0    | -    | 0    | -    | ns   |

| t <sub>WLWH</sub>  | t <sub>WP</sub>    | Write pulse width                                   | 80   | -    | 80   | -    | ns   |

| t <sub>WHWL</sub>  | t <sub>WPH</sub>   | Write pulse width high                              | 20   | -    | 20   | -    | ns   |

| t <sub>WHWH1</sub> | t <sub>WHWH1</sub> | Programming pulse time                              | 250  | -    | 250  | -    | μs   |

| t <sub>WHWH2</sub> | t <sub>WHWH2</sub> | Erase pulse time                                    | 1000 | -    | 1000 | -    | μs   |

|                    | t <sub>VCS</sub>   | V <sub>CC</sub> setup time                          | 2    | -    | 2    | -    | μs   |

|                    |                    |                                                     |      |      |      |      |      |

#### Read waveform

#### Write command waveform

#### Write command bus waveform

For all waveforms,  $A_{IN[4:1]}$ , and  $D_{IN[4:1]}$  = Address and Data for write cycles 1–4;  $D_{IN}$  = Data to be programmed at address  $A_{IN}$ ; Com. = Command byte input on the DQ pins during Write<sub>[3]</sub>;  $D_{OUT}$  = Status byte, Manufacturer ID code, or array data for verify.

# Latchup tolerance

| Parameter                                                                | Min  | Max                  | Unit |

|--------------------------------------------------------------------------|------|----------------------|------|

| Input voltage with respect to $V_{SS}$ on pin A9                         | -1.0 | +13.5                | V    |

| Input voltage with respect to $V_{\mbox{\scriptsize SS}}$ on all DQ pins | -1.0 | V <sub>CC</sub> +1.0 | V    |

| Current                                                                  | -100 | +100                 | mA   |

Includes all pins except  $V_{CC}.$  Test conditions:  $V_{CC}$  = 5.0V, one pin at a time.

| TSOP pin cap     | (f = 1 M)               | $(f = 1 \text{ MHz}, T_a = 25^{\circ}\text{C})$ |         |     |      |

|------------------|-------------------------|-------------------------------------------------|---------|-----|------|

| Symbol           | Parameter               | Test setup                                      | Typical | Max | Unit |

| C <sub>IN</sub>  | Input capacitance       | $V_{\rm IN}=0$                                  | 6       | 7.5 | pF   |

| C <sub>OUT</sub> | Output capacitance      | $V_{OUT} = 0$                                   | 8.5     | 12  | pF   |

| C <sub>IN2</sub> | Control pin capacitance | $V_{IN} = 0$                                    | 7.5     | 9   | μF   |

| C <sub>IN2</sub> | Control pin capacitance | $v_{\rm IN} \equiv 0$                           | 7.5     | 9   | μr   |

| PLCC and PDIP pin capacitance $(f = 1 \text{ MHz}, T_a = 25^{\circ})$ |                         |                |         | $(Hz, T_a = 25^{\circ}C)$ |      |

|-----------------------------------------------------------------------|-------------------------|----------------|---------|---------------------------|------|

| Symbol                                                                | Parameter               | Test setup     | Typical | Max                       | Unit |

| CIN                                                                   | Input capacitance       | $V_{\rm IN}=0$ | 4       | 6                         | pF   |

| C <sub>OUT</sub>                                                      | Output capacitance      | $V_{OUT} = 0$  | 8       | 12                        | pF   |

| C <sub>IN2</sub>                                                      | Control pin capacitance | $V_{IN} = 0$   | 8       | 12                        | μF   |

# Erase and programming performance

| (f = 1  MHz, T) | = room temperature, | $V_{CC} = 5V \pm 10\%$ |

|-----------------|---------------------|------------------------|

|-----------------|---------------------|------------------------|

|                                                                          |     | Limits  |     |        |

|--------------------------------------------------------------------------|-----|---------|-----|--------|

| Parameter                                                                | Min | Typical | Max | Unit   |

| Sector erase and Verify-1 time (excludes 00h programming prior to erase) | -   | 6.0     | 8.2 | sec    |

| Sector programming time                                                  | -   | -       | 8.2 | sec    |

| Chip programming time                                                    | -   | 48      | 80  | sec    |

| Erase program cycles                                                     | -   | 10,000  | -   | cycles |

| Byte program time                                                        | -   | 200     | 250 | μs     |

| Byte verify-0 time                                                       | -   | 200     | 250 | μs     |

## Data retention

| Parameter                           | Temperature | Min | Unit  |

|-------------------------------------|-------------|-----|-------|

|                                     | 150°        | 10  | years |

| Minimum pattern data retention time | 125°        | 20  | years |

# AS29F010 ordering information

| Package ∖ Access time        | 120 ns         | 150 ns         |

|------------------------------|----------------|----------------|

| Plastic DIP, 600 mil, 32-pin | AS29F010-120PC | AS29F010-150PC |

| PLCC, 0.53 × 0.45" 32-pin    | AS29F010-120LC | AS29F010-150LC |

| TSOP, 8×20 mm, 32-pin        | AS29F010-120TC | AS29F010-150TC |

# AS29F010 part numbering system

| AS29F               | 010           | -XXX                | Х                                         | С                                             |

|---------------------|---------------|---------------------|-------------------------------------------|-----------------------------------------------|

| Flash EEPROM prefix | Device number | Address access time | Package: P = PDIP<br>L = PLCC<br>T = TSOP | Commercial temperature range,<br>0°C to 70 °C |