## 12–Bit, 80 / 105 MSPS IF Sampler A/D Converter

# **Advanced Technical Data**

1/7/00

## AD9433

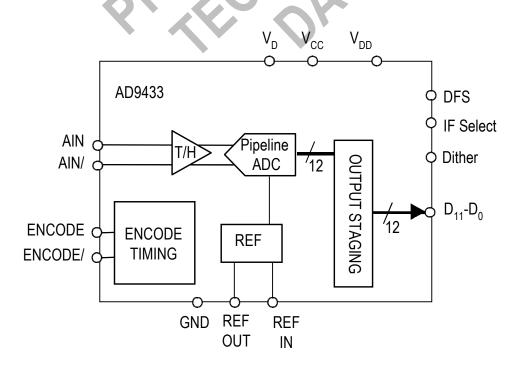

The AD9433 is an 12-bit monolithic sampling analog-to-digital converter with an on-chip track-and-hold circuit and is optimized for low cost, low power, small size and ease of use. The product operates up to 105 Msps conversion rate and is optimized for outstanding dynamic performance in wideband and high IF carrier systems.

The ADC requires a +5V and a +3.3V power supply and a flexible clock duty differential encode clock for full performance operation. No external reference or driver components are required for many applications. The digital outputs are TTL/CMOS compatible and a separate output power supply pin supports interfacing with 3.3V or 2.5V logic.

A user selectable on-chip dithering allows minimum SFDR performance of –90dBc from DC to 250MHz. An IF band select allows optimized SINAD vs SFDR for a particular carrier frequency.

The encode clock supports either differential or single-ended and is PECL compatible. Immunity to clock duty cycle variations and an output data format select option of two's complement or offset binary are also supported.

Fabricated on an advanced BiCMOS process, the AD9433 is available in a 52 pin surface mount plastic package (52 LQFP) specified over the industrial temperature range (-40°C to +85°C) and is pin compatible with the AD9432.

### FEATURES

IF Sampling up to 350MHz IF band select for optimized SINAD and SFDR On-chip reference and track/hold Scalable voltage reference Selectable on-chip dither for improved SFDR & THD Excellent Linearity: - DNL = +/- 0.3 lsb (typ)

- DNL = +/- 0.6 Isb (typ) - INL = +/- 0.6 Isb (typ) 700 MHz Full Power Analog Bandwidth SNR = 69dB @ Fin up to Nyquist SFDR = -90dBc @ Fin up to 250 MHz THD = -90dBc @ Fin up to 250 MHz Power dissipation = 900mW typical at 105Msps Input voltage range of 1Vp-p and 2Vp-p Two's complement or Straight binary data format +5.0V and +3.3V Supply Operation +2.5V to 3.3V TTL/CMOS outputs Clock Duty Cycle Stablizer.

#### **APPLICATIONS**

Wireless and Wired Broadband Communications - Wideband carrier frequency systems Communications Test Equipment "IF Sampling" schemes Radar and Satellite sub-systems

#### **REV 0.1**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. © Analog Devices, Inc., 1999

One Technology Way, P.O Box 9106, Norwood, MA 02062–9106, USA Tel: 617/329–4700 Fax: 617–326–8703

# **AD9433—TARGET SPECIFICATIONS**

### ELECTRICAL CHARACTERISTICS (VDD = 3.0V, VCc = 5.0V; external reference; ENCODE = 105 Msps, unless otherwise noted)

| Parameter                                  | Temp  | Test<br>Level | AD9433BST-105         |            |      |        |

|--------------------------------------------|-------|---------------|-----------------------|------------|------|--------|

|                                            |       |               | Min                   | Typical    | Max  | Units  |

| RESOLUTION                                 |       |               |                       | 12         |      | bits   |

| DC ACCURACY                                |       |               |                       |            |      |        |

| Differential Nonlinearity                  | +25°C | Ι             | -0.6                  | ±0.3       | +0.6 | LSB    |

|                                            | Full  | VI            |                       |            |      | LSB    |

| Integral Nonlinearity                      | +25°C | Ι             |                       | ±0.75      |      | LSB    |

|                                            | Full  | VI            |                       |            |      | LSB    |

| No Missing Codes                           | Full  | VI            |                       | Guaranteed | 1    |        |

| Gain Error <sup>1</sup>                    | +25°C | Ι             |                       | ±1         |      | % FS   |

|                                            | Full  | VI            |                       |            |      | % FS   |

| Gain Tempco <sup>1</sup>                   | Full  | V             |                       | 150        |      | ppm/°C |

| ANALOG INPUT                               |       |               |                       |            |      |        |

| Input Voltage Range                        | Full  | V             |                       | ±1.0       |      | V p–р  |

| (with respect to AIN\)                     |       |               |                       |            |      |        |

| Common Mode Voltage                        | Full  | V             |                       | 3.0        |      | V      |

| Input Offset Voltage                       | Full  | VI            |                       | $\pm 0$    |      | mV     |

| Input Capacitance                          | +25°C | V             |                       | 4          |      | pF     |

| Input Resistance                           | Full  | VI            | 2                     | 3          | 3    | kΩ     |

| Analog Bandwidth, Full Power               | +25°C | V             |                       | 500        |      | MHz    |

| ANALOG REFERECE                            |       |               |                       |            |      |        |

| Reference Voltage                          | Full  | VI            | 2.4                   | 2.5        | 2.6  | V      |

| Тетрсо                                     | Full  | V             |                       | 50         |      | ppm/°C |

| Input Bias Current                         | Full  | VI            |                       | 15         |      | μA     |

| SWITCHING PERFORMANCE                      |       |               |                       |            |      |        |

| Maximum Conversion Rate                    | Full  | VI            | 105                   |            |      | Msps   |

| Minimum Conversion Rate                    | Full  | IV            |                       |            | 10   | Msps   |

| Encode Pulse Width High (t <sub>EH</sub> ) | +25°C | IV            | 4.5                   | 5.0        |      | ns     |

| Encode Pulse Width Low (t <sub>EL</sub> )  | +25°C | IV            | 4.5                   | 5.0        |      | ns     |

| Aperture Delay $(t_A)$                     | +25°C | V             |                       | 2.0        |      | ns     |

| Aperture Uncertainty (Jitter)              | +25°C | V             |                       | 0.3        |      | ps rms |

| Output Valid Time $(t_V)^2$                | Full  | VI            |                       | 6.0        |      | ns     |

| Output Propagation Delay $(t_{PD})^2$      | Full  | VI            | 4.5                   | 8.0        | 9.0  | ns     |

| Output Rise Time $(t_R)^2$                 | Full  | VI            |                       | 2.1        |      | ns     |

| Output Fall Time $(t_F)$                   | Full  | VI            |                       | 1.9        |      | ns     |

| Output Fall Time (t <sub>F</sub> )         |       |               |                       |            |      |        |

| Output Fall Time (t <sub>F</sub> )         |       |               |                       |            |      |        |

| DIGITAL INPUTS                             |       |               |                       |            |      |        |

| Encode Input Common Mode                   | Full  | V             | 1.2                   | 1.6        | 2.0  | V      |

| Differential Input (Enc,Enc\)              | Full  | V v           |                       | 750        |      | mV     |

| Single Ended                               |       |               |                       |            |      |        |

| Logic "1" Voltage                          | Full  | IV            | 0                     |            |      | V      |

| Logic "0" Voltage                          | Full  | IV            |                       |            | 0.9  | V      |

| Input Resistance                           | Full  | VI            |                       | 5          |      | kΩ     |

| Input Capacitance                          | +25°C | V             |                       | 4.5        |      | PF     |

| DIGITAL OUTPUTS                            |       |               |                       |            |      |        |

| Logic "1" Voltage ( $V_{DD} = +3.3V$ )     | Full  | VI            | V <sub>DD</sub> -0.05 | 5          |      | V      |

| Logic "0" Voltage ( $V_{DD} = +3.3V$ )     | Full  | VI            | 55                    |            | 0.05 | V      |

| Output Coding                              |       |               | Two's c               | complement |      |        |

| POWER SUPPLY                               |       |               |                       | 1          |      | 1      |

| Power Dissipation <sup>3</sup>             | Full  | VI            |                       | 900        |      | mW     |

|                                            |       |               | 1                     | 200        |      |        |

| Power Supply Rejection Ratio               | +25°C | Ι             |                       | ±5         |      | mV/V   |

|                                                       |       | Test  | AD9433BST-105   |      |  | x Units |

|-------------------------------------------------------|-------|-------|-----------------|------|--|---------|

| Parameter                                             | Тетр  | Level | Min Typical Max |      |  |         |

| DYNAMIC PERFORMANCE <sup>4</sup>                      |       |       |                 |      |  |         |

| Signal-to-Noise Ratio (SNR)                           |       |       |                 |      |  |         |

| (Without Harmonics)                                   |       |       |                 |      |  |         |

| $\hat{f}_{IN} = 10 \text{ MHz}$                       | +25°C | Ι     |                 | 69   |  | dB      |

| $f_{IN} = 49 \text{ MHz}$                             | +25°C | Ι     |                 | 69   |  | dB      |

| $f_{IN} = 70 \text{ MHz}$                             | +25°C | Ι     |                 | 69   |  | dB      |

| $f_{IN} = 150 \text{ MHz}$                            | +25°C | Ι     |                 | 68.8 |  | dB      |

| $f_{IN} = 250 \text{ MHz}$                            | +25°C | Ι     |                 | 68.8 |  | dB      |

| Signal-to-Noise Ratio (SINAD)                         |       |       |                 |      |  |         |

| (With Harmonics)                                      |       |       |                 |      |  |         |

| $f_{IN} = 10 \text{ MHz}$                             | +25°C | Ι     |                 | 68   |  | dB      |

| $f_{IN} = 49 \text{ MHz}$                             | +25°C | Ι     |                 | 68   |  | dB      |

| $f_{IN} = 70 \text{ MHz}$                             | +25°C | Ι     |                 | 68   |  | dB      |

| $f_{IN} = 150 \text{ MHz}$                            | +25°C | Ι     |                 | 67.8 |  | dB      |

| $f_{IN} = 250 \text{ MHz}$                            | +25°C | Ι     |                 | 67.8 |  | dB      |

| Effective Number of Bits                              |       |       |                 |      |  |         |

| $f_{IN} = 10 \text{ MHz}$                             | +25°C | I     |                 | 11.2 |  | bits    |

| $f_{IN} = 49 \text{ MHz}$                             | +25°C | I     |                 | 11.2 |  | bits    |

| $f_{IN} = 70 \text{ MHz}$                             | +25°C | I     |                 | 11.2 |  | bits    |

| $f_{IN} = 150 \text{ MHz}$                            | +25°C | I.    |                 | 11.0 |  | bits    |

| $f_{IN} = 250 \text{ MHz}$                            | +25°C | I     |                 | 11.0 |  | bits    |

| 2 <sup>nd</sup> & 3 <sup>rd</sup> Harmonic Distortion |       |       |                 |      |  |         |

| $f_{IN} = 10 \text{ MHz}$                             | +25°C | I     |                 | -90  |  | dBc     |

| $f_{IN} = 49 \text{ MHz}$                             | +25°C | I     |                 | -90  |  | dBc     |

| $f_{IN} = 70 \text{ MHz}$                             | +25°C |       |                 | -90  |  | dBc     |

| $f_{IN} = 150 \text{ MHz}$                            | +25°C | I     |                 | -90  |  | dBc     |

| $f_{IN} = 250 \text{ MHz}$                            | +25°C | I     |                 | -90  |  | dBc     |

| 4 <sup>th</sup> or higher Harmonic Distortion         |       |       |                 |      |  |         |

| $f_{IN} = 10 \text{ MHz}$                             | +25°C | I     |                 | -87  |  | dBc     |

| $f_{IN} = 49 \text{ MHz}$                             | +25°C | Ι     |                 | -87  |  | dBc     |

| $f_{IN} = 70 \text{ MHz}$                             | +25°C | Ι     |                 | -85  |  | dBc     |

| $f_{IN} = 150 \text{ MHz}$                            | +25°C | Ι     |                 | -85  |  | dBc     |

| $f_{IN} = 250 \text{ MHz}$                            | +25°C | Ι     |                 | -85  |  | dBc     |

| Two–Tone Intermod Distortion (IMD)                    |       |       |                 |      |  |         |

| $f_{IN} = 10 \text{ MHz}$                             | +25°C | V     |                 | Tbf  |  | dBc     |

| $f_{IN} = 20 \text{ MHz}$                             | +25°C | V     |                 | Tbf  |  | dBc     |

| $f_{IN} = 47 \text{ MHz}$                             | +25°C | V     |                 | Tbf  |  | dBc     |

NOTES

1.

Gain error and gain temperature coefficients are based on the ADC only (with a fixed 2.5V external reference and 2Vp-p differential input.).  $t_V$  and  $t_{PD}$  are measured from a 1.5V level of the ENCODE input to the 50%/50% levels of the digital outputs swing. The digital output load during test is not to exceed an ac load of 10pF or a dc current of +/-40  $\mu$ A. 2.

3.

Power dissipation measured with encode at rated speed and a dc analog input. SNR/harmonics based on an analog input voltage of -0.5dBFS referenced to a 2V full-scale input range. 4.