#### Preliminary Rev. A 8/10/01

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 ©Analog Devices, Inc., 2001

# PRELIMINARY TECHNICAL DATA

### **FEATURES**

Very Flat AC Response to 400MHz, ±.5dB Digital Variable Gain, from -5dB to +40dB  $(R_L=1k\Omega)$ 3dB Step Size Parallel or Serial 4-bit Interface **Differential Input and Output 200**Ω Differential Input **200**Ω Differential Output **High-Efficiency Output Stage** Operation from Supply Voltages from 3.0 - 5.5 V Rapid Power-Down to less than 300 µA max

**APPLICATIONS IF Sampling Receivers Cellular/PCS Base Stations**

### **PRODUCT DESCRIPTION**

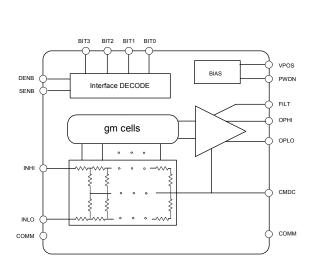

The AD8369 is a high-performance digitally controlled variable gain amplifier for use from very low frequencies to 550MHz, with a -3dB frequency of 700MHz at full gain (40dB, Rload=1k) and essentially constant response at all gains. The AD8369 delivers excellent distortion performance, two-tone intermodulation distortion is 63dBc at 150MHz for 10MHz spacing. Digital control of the AD8369 is achieved using a 4-bit serial or parallel interface. The mode of digital control is selected by connecting a single pin to ground or the positive supply.

Variable gain is achieved via two methods. Six dB gain steps are implemented using the X-AMP approach, where the input signal is scaled by a differential R-2R ladder network. The ladder also sets the input impedance at 200 ohms differential. Three dB steps are implemented at the output of the amp via a signal subtraction method. The output impedance is set via on chip resistors across the differential output pins. Consequently the load that is presented to the part will affect the overall gain of the amplifier.

Standard CMOS levels can drive the digital interface. Control pins (SENB and DENB) when left open are pulled to levels that put the part in the parallel transparent mode. The Data pins are pulled low if left unconnected. In serial mode, Bit0 is the serial data input and Bit1 is clock. The DENB has the same function in both the serial and parallel modes. Data is latched while the DENB pin is low and transparent when DENB is high. The AD8369 may be powered on or off by a voltage applied to the ENBL pin. When this voltage is at logic LO, the total dissipation drops to the microwatt range. For a logic HI, the chip powers-up rapidly to its nominal quiescent current of 34mA at 25° C.

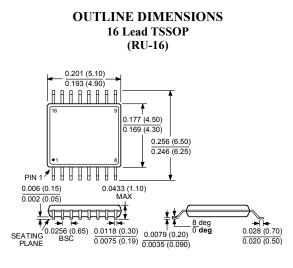

The AD8369 is fabricated on Analog Devices proprietary, high performance 25GHz silicon Bipolar IC process. The AD8369 is available in a 16pin TSSOP package for the industrial temperature range of -40°C to +85°C. A device populated evaluation board is available

Patents Pending

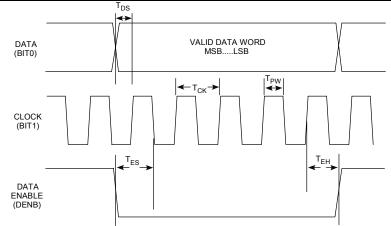

# **AD8369**

45-dB Digital VGA

LF to 500MHz

# **ANALOG DEVICES**

# AD8369

### **AD8369-SPECIFICATIONS** (V<sub>s</sub>=5V, T=25°C, Z<sub>O</sub> = 200Ω, Frequency = 70MHz unless otherwise noted)

| Parameters                      | Conditions                                  | Min    | Тур | Max | Units         |

|---------------------------------|---------------------------------------------|--------|-----|-----|---------------|

| OVERALL FUNCTION                |                                             |        |     |     |               |

| Frequency Range                 | $V_{s}$ =5V, T=25°C, $Z_{O}$ = 200 $\Omega$ | Note 1 |     | 550 | MHz           |

| INPUT STAGE                     |                                             |        |     |     |               |

| Maximum Input                   | Maximum Peak Input Voltage                  |        |     | TBD | Vp-p          |

| Input Resistance// Capacitance  | From INHI to INLO, Freq = 70 MHz            |        | 200 |     | $\Omega //pF$ |

| Input Noise Spectral Density    | At max gain                                 |        | TBD |     | nV/√H:        |

| GAIN CONTROL                    |                                             |        |     |     |               |

| INTERFACE                       |                                             |        |     |     |               |

| Gain Range                      |                                             |        | 45  |     | dB            |

| Maximum Gain                    | Gain Code F (1111)                          |        | 40  |     | dB            |

| Minimum Gain                    | Gain Code 0 (0000)                          |        | -5  |     | dB            |

| Gain Step Size                  |                                             |        | 3   |     | dB            |

| Gain Step Accuracy              |                                             |        | TBD |     | dB            |

| Gain Step Response              | Gain Code 0 (0000) to Gain Code 1 (0001)    |        | TBD |     | μs            |

| OUTPUT STAGE                    |                                             |        |     |     |               |

| Maximum Output Voltage          | $R_L \ge 1k\Omega$                          |        | TBD |     | Vpp           |

| Output Resistance// Capacitance | From OPHI to OPLO                           |        | 200 |     | $\Omega//pF$  |

| f = 70 MHz                      |                                             |        |     |     |               |

| Gain                            | Gain Code F (1111)                          |        | 35  |     | dB            |

| Noise Figure                    | At Max Gain                                 |        | 6.8 |     | dB            |

| Output IP3                      | fl = 69.5 MHz, f2 = 70.5MHz, At Max Gain    |        | 22  |     | dBm           |

| Output 1dB Compression Point    | At Max Gain                                 |        | -1  |     | dBm           |

| f = 140 MHz                     |                                             |        |     |     |               |

| Gain                            | All bits high (1111)                        |        | 35  |     | dB            |

| Noise Figure                    | At Max Gain                                 |        | 6.8 |     | dB            |

| Output IP3                      | f1 = 139.5 MHz, f2 = 140.5MHz, At Max Gain  |        | 18  |     | dBm           |

| Output 1dB Compression Point    | At Max Gain                                 |        | TBD |     | dBm           |

| f = 190 MHz                     |                                             |        |     |     | 1             |

| Gain                            | All bits high (1111)                        |        | 35  |     | dB            |

| Noise Figure                    | At Max Gain                                 |        | 6.9 |     | dB            |

| Output IP3                      | f1 = 189.5 MHz, f2 = 190.5MHz, At Max Gain  |        | 17  |     | dBm           |

| Output 1dB Compression Point    | At Max Gain                                 |        | TBD |     | dBm           |

| f = 240 MHz                     |                                             |        |     |     |               |

| Gain                            | All bits high (1111)                        |        | 35  |     | dB            |

| Noise Figure                    | At Max Gain                                 |        | 6.9 |     | dB            |

| Output IP3                      | f1 = 239.5MHz, f2 = 240.5MHz, At Max Gain   |        | 15  |     | dBm           |

| Output 1dB Compression Point    | At Max Gain                                 |        | TBD |     | dBm           |

### AD8369-SPECIFICATIONS

(Vs=5V, T=25°C, Z\_O = 200 $\Omega$ , Frequency = 70MHz unless otherwise noted)

| POWER INTERFACE      |                                                                                  |                    |     |    |

|----------------------|----------------------------------------------------------------------------------|--------------------|-----|----|

| Supply Voltage       |                                                                                  | 3.0                | 5.5 | V  |

| Quiescent Current    | PWDN high                                                                        | 34                 |     | mA |

| vs. Temperature      | $-30^{\circ}C \le T_A \le 85^{\circ}C$                                           |                    |     | mA |

| Disable Current      | PWDN low                                                                         | 750                |     | μΑ |

| vs. Temperature      | $-30^{\circ}C \le T_A \le 85^{\circ}C$                                           |                    |     | uA |

| MODE CONTROL         |                                                                                  |                    |     |    |

| INTERFACE            |                                                                                  |                    |     |    |

| Mode LO Threshold    | Device in parallel mode of operation                                             | V <sub>S</sub> / 2 |     | V  |

| Mode HI Threshold    | Device in serial mode of operation                                               | $V_{\rm S}/2$      |     | V  |

| POWER DOWN INTERFACE |                                                                                  |                    |     |    |

| Threshold            |                                                                                  | 1.7                |     | V  |

| Response Time        | Time delay following LO to HI transition until device meets full specifications. | TBD                |     | μs |

| Input Bias Current   | PWDN = 5 V                                                                       | 170                |     | μΑ |

Notes

1) The lowest frequency of operation is determined by the capacitor on pin FILT.

2) See applications section for reactive matching networks

# AD8369

### TIMING REQUIREMENTS (Vs=5V, T=25°C, F<sub>CLK</sub> = 8MHz unless otherwise noted)

| ¥=1.                                                |     |     |     |       |

|-----------------------------------------------------|-----|-----|-----|-------|

| Parameter                                           |     | Тур | Max | Units |

| Clock Pulse Width (T <sub>PW</sub> )                | TBD |     |     | ns    |

| Clock Period (T <sub>CK</sub> )                     | TBD |     |     | ns    |

| Setup Time Data vs. Clock (T <sub>DS</sub> )        | TBD |     |     | ns    |

| Setup Time Data Enable vs. Clock (T <sub>ES</sub> ) | TBD |     |     | ns    |

| Hold Time Data Enable vs. Clock (T <sub>EH</sub> )  | TBD |     |     | ns    |

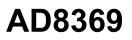

Figure 1. Serial Interface Timing Diagram

| Desired<br>Gain<br>(dB) | Equivalent<br>Gain<br>(V <sub>OUT</sub> /V <sub>IN</sub> ) | BIT3<br>(MSB) | BIT2 | BIT1 | BIT0<br>(LSB) |

|-------------------------|------------------------------------------------------------|---------------|------|------|---------------|

| -5                      | 0.562341                                                   | 0             | 0    | 0    | 0             |

| -2                      | 0.794328                                                   | 0             | 0    | 0    | 1             |

| +1                      | 1.122018                                                   | 0             | 0    | 1    | 0             |

| +4                      | 1.584893                                                   | 0             | 0    | 1    | 1             |

| +7                      | 2.238721                                                   | 0             | 1    | 0    | 0             |

| +10                     | 3.162278                                                   | 0             | 1    | 0    | 1             |

| +13                     | 4.466836                                                   | 0             | 1    | 1    | 0             |

| +16                     | 6.309573                                                   | 0             | 1    | 1    | 1             |

| +19                     | 8.912509                                                   | 1             | 0    | 0    | 0             |

| +22                     | 12.58925                                                   | 1             | 0    | 0    | 1             |

| +25                     | 17.78279                                                   | 1             | 0    | 1    | 0             |

| +28                     | 25.11886                                                   | 1             | 0    | 1    | 1             |

| +31                     | 35.48134                                                   | 1             | 1    | 0    | 0             |

| +34                     | 50.11872                                                   | 1             | 1    | 0    | 1             |

| +37                     | 70.79458                                                   | 1             | 1    | 1    | 0             |

| +40                     | 100                                                        | 1             | 1    | 1    | 1             |

Table 1. Gain for Multiple Values of Gain Code for  $1k\Omega$ Load.

# AD8369

### AD8369

| ABSOLUTE MAXIMUM | I RATINGS* |

|------------------|------------|

|------------------|------------|

| Supply Voltage VPOS<br>PWDN Voltage             |                     |

|-------------------------------------------------|---------------------|

| SENB Select Voltage                             | $\dots V_{S} + xV$  |

| Input Volage, INHI - INLO                       | xV                  |

| Internal Power Dissipation                      | TBD                 |

| $\theta_{JA}$                                   | 150 °C/W            |

| Maximum Junction Temperature                    | +125° C             |

| Operating Temperature Range40° C                | C to +85° C         |

| Storage Temperature Range $\dots -65^{\circ} C$ | to $+150^{\circ}$ C |

| Lead Temperature Range (Soldering 60 se         | c)+300° C           |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

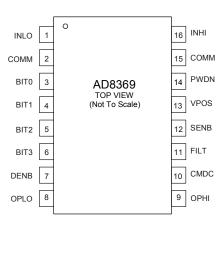

### **PIN CONFIGURATION**

| PIN FUNCTION DESCRIPTIONS |                                                                                      |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Name                      | Function                                                                             |  |  |  |

| INLO                      | Balanced Differential Input. Internally                                              |  |  |  |

|                           | biased, should be AC coupled.                                                        |  |  |  |

| COMM                      | Device Common. Connect to low                                                        |  |  |  |

|                           | impedance ground.                                                                    |  |  |  |

| BIT0                      | Gain Selection Least Significant Bit. Used as                                        |  |  |  |

|                           | DATA input signal when in serial mode of                                             |  |  |  |

| BIT1                      | operation.<br>Gain Selection Control Bit. Used as CLOCK                              |  |  |  |

| DITI                      | input pin when in serial mode of operation.                                          |  |  |  |

| BIT2                      | Gain Selection Control Bit. Inactive when in                                         |  |  |  |

|                           | serial mode of operation.                                                            |  |  |  |

| BIT3                      | Gain Selection Most Significant Bit. Inactive                                        |  |  |  |

|                           | when in serial mode of operation.                                                    |  |  |  |

| DENB                      | Data Enable Pin. Data writes to register when                                        |  |  |  |

|                           | low. Data is latched during low to high transition. See Figure 1 for timing diagram. |  |  |  |

| OPLO                      | Balanced Differential Output. Biased to mid                                          |  |  |  |

|                           | supply, should be AC coupled                                                         |  |  |  |

| OPHI                      | Balanced Differential Output. Biased to mid                                          |  |  |  |

|                           | supply, should be AC coupled                                                         |  |  |  |

| CMDC                      | Common Mode Decoupling Pin. Connect bypass                                           |  |  |  |

|                           | capacitor to ground for additional common mode                                       |  |  |  |

|                           | supply decoupling.                                                                   |  |  |  |

| FILT                      | High Pass Filter Connection. Used to set high pass corner frequency.                 |  |  |  |

| SENB                      | Serial or Parallel Interface Select. Connect SENB                                    |  |  |  |

| DEND                      | to VPOS for serial operation. Connect SENB to                                        |  |  |  |

|                           | COMM for parallel operation.                                                         |  |  |  |

| VPOS                      | Positive Supply Voltage, V <sub>S</sub> .+ 3V to +5.5V.                              |  |  |  |

| PWDN                      | Power Down Pin. Device is active when high,                                          |  |  |  |

|                           | pull pin low to disable device.                                                      |  |  |  |

| COMM                      | Device Common. Connect to low                                                        |  |  |  |

|                           | impedance ground.                                                                    |  |  |  |

| INHI                      | Balanced Differential Input. Internally                                              |  |  |  |

|                           | biased, should be AC coupled.                                                        |  |  |  |

CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8369 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy [>250 V HBM] electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **ORDERING GUIDE**

Pin 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

| Model           | Temp. Range      | Package Description | Package Option |

|-----------------|------------------|---------------------|----------------|

| AD8369ARU       | -40 °C to +85 °C | Tube, 16-Lead TSSOP | RU-16          |

| AD8369ARU-REEL7 |                  | 7" Tape and Reel    |                |

| AD8369-EVAL     |                  | Evaluation Board    |                |

# AD8369

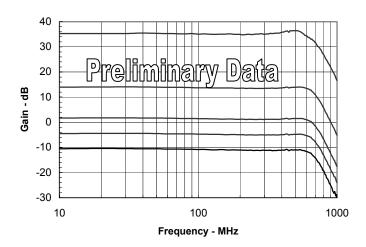

TPC 1. Frequency Response versus Gain Code (ref  $200\Omega$  load)

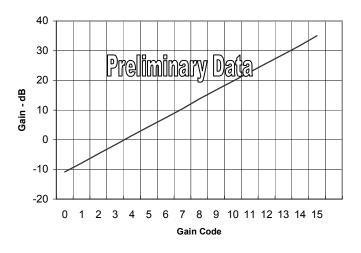

TPC 2. Gain verus Gain Cod e (ref  $200\Omega$  load)

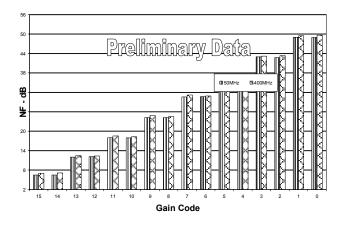

TPC 3. NoiseFigurversus Gain Code (ref  $200\Omega$  load)

Rev. A 8/10/2001

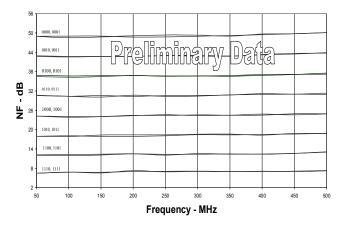

TPC 4. Noise Figure versus Frequency (ref  $200\Omega$  load)

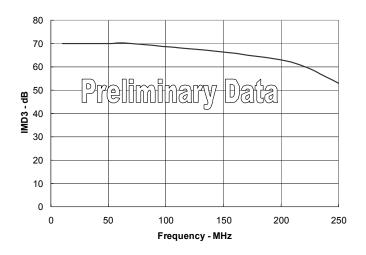

TPC 5. IMD3 versus Frequency at Maximum Gain  $V_{out}=1Vpp$  Composite, Rload=1 k $\Omega$

# AD8369

### **Basic Connections**

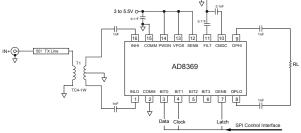

The AD8369 is a digitally controlled variable gain amplifier designed to operate in a 200  $\Omega$  system. The differential 200  $\Omega$  input and output impedances allow for easy impedance matching and gain adjustment in typical high performance intermediate frequency (IF) signal chain designs. *Figure 1. Basic Connections*

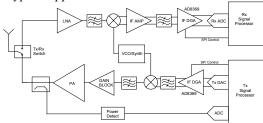

The AD8369 is typically used as an IF VGA in the receive and transmit portions of the signal chain. Figure 1 shows the basic connections for operating the AD8369 and Figure 2 shows a block diagram of a typical application.

Figure 2. Typical Signal Chain Example

A supply voltage of +3.0 V to +5.5 V is required for the AD8369. The supply to the VPOS pin should be decoupled with a low inductance  $0.1\mu$ F surface mount ceramic capacitors, close to the device. Additional supply decoupling may be attained using a small series resistance followed by a shunt capacitor to ground, this should help to ensure clean supply voltage to the AD8369.

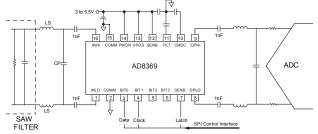

The input to the AD8369 is a 200  $\Omega$  differential resistive ladder network. A broadband 50 $\Omega$  input match can be achieved by using an impedance transformer as shown in figure 1. The impedance transformer not only transforms a 50  $\Omega$  input to a 200  $\Omega$  value, but can also be used to convert a single ended input signal to a balanced differential output. Most applications will only require operation over a narrow band of frequencies. For narrow band applications it may be more efficient to use a reactive matching network as in the example of figure 3. In this example the input signal from the SAW filter is transformed to match step up matching network. Network selection is highly dependent upon the frequency of operation and driving impedance of the preceding stage. For example, if the SAW filter presents a 50 $\Omega$  output impedance at 70MHz, LS = 100 nH and CP = 18 pF will transform the 50 $\Omega$  output to match the 200 $\Omega$ input of the AD8369.

the 200  $\Omega$  input impedance of the AD8369 using a

Figure 3. IF Sampling Receiver Example

### **Evaluation Board**

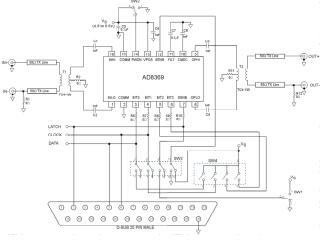

Figure 4. Evaluation Board Schematic

The evaluation board allows for quick testing of the AD8369 using standard  $50\Omega$  test equipment. Transforms T1 and T2 are used to transform  $50\Omega$  source and load terminations to the desired  $200 \Omega$  reference impedance. This allows for broadband operation of the device without a need to pay particular attention to impedance matching.

The evaluation board comes with the AD8369 control software which allows for serial gain control from most computers. By simply adjusting the slider bar in the control software, the gain code is automatically updated to the AD8369. It is necessary to set SW3 to 'SER' for the control software to function normally.

# AD8369

| Component    | Function                                                                                                                                                                                                                                                                          | Default Condition                 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| VPOS, GND    | Supply and Ground Vector Pins                                                                                                                                                                                                                                                     | Not Applicable                    |

| SW1          | Data Enable: Set to position A for pass through mode of                                                                                                                                                                                                                           | Not Applicable                    |

| SW2          | operation. Ser to position B to latch the gain setting.<br><b>Device Enable:</b> When in the PWDN position, the PWDN pin will be connected to ground and the AD8369 will be disabled. The device is enabled when the switch is in the PWUP position, connecting PWDN pin to VPOS. | Not Applicable                    |

| SW3, R5      | Serial/Parallel Selection : The device will respond to                                                                                                                                                                                                                            | Not Applicable                    |

| 2            | serial control inputs from connector P1 when the switch is<br>in the SER position. Parallel operation is achieved when in<br>PAR position. Device can be hardwired for parallel mode of<br>operation by placing $0\Omega$ resistor in position R5.                                | R5 = open (Size 0603)             |

| SW4          | <b>Parallel Interface Control:</b> Used to hardwire BIT0 through BIT3 to desired gain code when in parallel mode of operation. The switch functions as a hexadecimal to binary encoder (Gain Code $0 = 0000$ , Gain Code $F = 1111$ ).                                            | Not Applicable                    |

| C1, C2, C3,  | AC Coupling Capacitors: Provides AC coupling of the                                                                                                                                                                                                                               | C1 = C2 = 1nF (Size 0603)         |

| C4           | input and output signals.                                                                                                                                                                                                                                                         | C3 = C4 = 1nF (Size 0603)         |

| T1, T2       | <b>Impedance Transformers:</b> Used to transform the $200\Omega$                                                                                                                                                                                                                  | T1 = T2 = TC4-1W                  |

|              | input and output impedance to $50\Omega$ .                                                                                                                                                                                                                                        | (MiniCircuits)                    |

| R1, R2, R11, | Single Ended or Differential: R2 and R11 are used to                                                                                                                                                                                                                              | $R1 = R2 = 0\Omega$ (Size 0603)   |

| R12          | ground the center tap of the secondary windings on<br>transformers T1 and T2. R1 and R12 should be used to<br>ground J2 and J7 when used in single ended applications.                                                                                                            | $R11 = R12 = 0\Omega$ (Size 0603) |

| R6, R7, R8,  | <b>Control Interface Resistors:</b> Simple series resistors for                                                                                                                                                                                                                   | $R6 = R7 = 0\Omega$ (Size 0603)   |

| R9, R10      | each control interface signal. May be replaced with jumpers                                                                                                                                                                                                                       | $R8 = R9 = 0\Omega$ (Size 0603)   |

|              | for interface debug.                                                                                                                                                                                                                                                              | $R10 = 0\Omega$ (Size 0603)       |

| C5, C6, C8   | Power Supply Decoupling: Nominal supply decoupling                                                                                                                                                                                                                                | $C5 = 0.1 \mu F$ (Size 0603)      |

|              | consists of a $0.1\mu$ F capacitor followed by a 1nF capacitor to ground as close to the device as possible. C8 provides additional decoupling of the output common mode voltage.                                                                                                 | C6 = C8 = 1nF (Size 0603)         |

| C7           | <b>High Pass Filter Capacitor:</b> Used to set high pass corner frequency of output. See applications section for equations.                                                                                                                                                      | C7 = 1nF (Size 0603)              |

| C9           | <b>Clock Filter Capacitor:</b> May be required with some printer ports to minimize overshoot. The clock waveform may be smoothed using a simple filter network established by R7 and C9. Some experimentation may be necessary to determine optimum values.                       | C9 = open (Size 0603)             |

### **Table II Evaluation Board Configuration Options**

AD8369

Dimensions shown in inches and (mm)

Rev. A 8/10/2001