## **LP3939**

# **Power Amplifier Driver for Dual Band CDMA Handsets**

## **General Description**

Designed specifically for Qualcomm's MSM3xxx and MSM5xxx series, the LP3939 is an integrated device that provides interface to the baseband processor to power-switch two independent power amplifiers in dual band applications. By integrating the discrete components necessary to achieve the same functions, the LP3939 drastically reduces board space and component cost.

### **Features**

■ Power-switch for dual band CDMA power amplifier

## **Key Specifications**

- 0.002 µA Quiescent Current (typ)

- LLP16 Package

### **Applications**

■ Dual-band CDMA phones with MSM3xxx or MSM5xxx platform

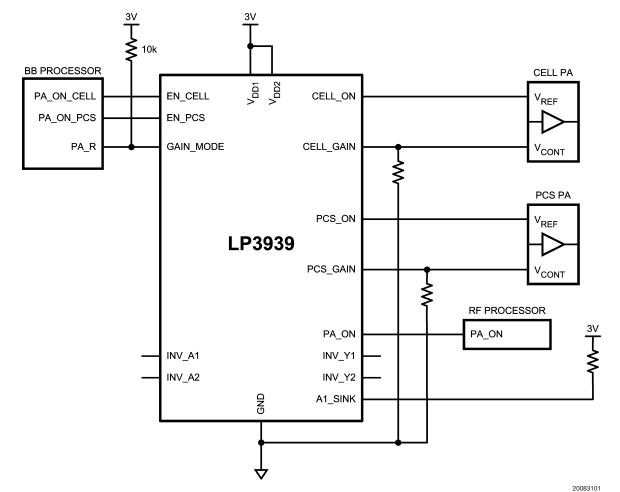

## **LP3939 Application Circuit**

Note: This application circuit shows the connection interface to a typical Skyworks PA. Connections to other PA vendors may vary slightly.

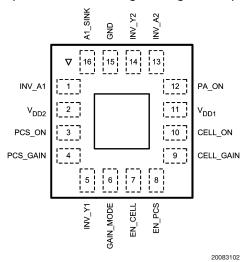

# **Connection Diagram**

### (LLP16: NSC Marketing Drawing LQA16A)

**Top View** See NS Package Number LQA16A

# **Pin Description**

| Pin | Name      | Functional Description                                |  |

|-----|-----------|-------------------------------------------------------|--|

| 1   | INV_A1    | Input                                                 |  |

| 2   | $V_{DD2}$ | Supply. V <sub>DD1</sub> and V <sub>DD2</sub> must be |  |

|     |           | tied together externally.                             |  |

| 3   | PCS_ON    | Output, open drain                                    |  |

| 4   | PCS_GAIN  | Output, open drain                                    |  |

| 5   | INV_Y1    | Output                                                |  |

| 6   | GAIN_MODE | Input                                                 |  |

| 7   | EN_CELL   | Input                                                 |  |

| 8   | EN_PCS    | Input                                                 |  |

| 9   | CELL_GAIN | Output, open drain                                    |  |

| 10  | CELL_ON   | Output, open drain                                    |  |

| 11  | $V_{DD1}$ | Supply. V <sub>DD1</sub> and V <sub>DD2</sub> must be |  |

|     |           | tied together externally.                             |  |

| 12  | PA_ON     | Output                                                |  |

| 13  | INV_A2    | Input                                                 |  |

| 14  | INV_Y2    | Output, open drain                                    |  |

| 15  | GND       | GND                                                   |  |

| 16  | A1_SINK   | Output, open drain                                    |  |

## **Ordering Information**

| LP3939 Supplied as 1k Units, Tape and Reel | LP3939 Supplied as 4.5k Units, Tape and Reel | Package Marking |

|--------------------------------------------|----------------------------------------------|-----------------|

| LP3939ILQ                                  | LP3939ILQX                                   | National Logo   |

|                                            |                                              | UZXYTT          |

|                                            |                                              | LP3939          |

U-wafer fab code Z-assembly plant code XY-date code

TT-die run traceability

## **Absolute Maximum Ratings (Notes 1,**

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{DD1}$ ,  $V_{DD2}$  -0.3V to +6.0V

EN\_CELL, EN\_PCS, GAIN\_MODE, INV\_A1, INV\_A2, PA\_ON, INV\_Y1, CELL\_ON, CELL\_GAIN, PCS\_ON, PCS\_GAIN, INV\_Y2

and A1\_SINK -0.3V to  $(V_{DD} + 0.3V)$ GND to GND SLUG  $\pm 0.3V$ Junction Temperature  $150^{\circ}$ C

Maximum Power Dissipation

(Note 3) 2.0W

Storage Temperature -65°C to +150°C

ESD (Note 4):

Human Body Model 2 kV Machine Model 200V

## Operating Ratings (Notes 1, 2)

$V_{DD1}, V_{DD2}$  1.8V to 5.5V Junction Temperature  $-40^{\circ}$ C to  $+125^{\circ}$ C Operating Temperature  $-40^{\circ}$ C to  $+85^{\circ}$ C Thermal Resistance 39.8°C/W

$\theta_{JA}$  (LLP16)

Maximum Power Dissipation

(Note 5) 1.38W

### **DC Electrical Characteristics**

Unless otherwise noted,  $V_{DD1} = V_{DD2} = 3V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+85^{\circ}C$ . (Note 6)

| Symbol                | Parameter              | Conditions                                                                  | Тур   | Limit           |     | 11    |

|-----------------------|------------------------|-----------------------------------------------------------------------------|-------|-----------------|-----|-------|

|                       |                        |                                                                             |       | Min             | Max | Units |

| I <sub>IN</sub>       | Input Current          | All Input Pins                                                              | 0.05  |                 | 5   | μA    |

| I <sub>Q</sub>        | Quiescent Current      | All inputs tied to V <sub>DD</sub> or ground.  No load at the outputs.      | 0.002 |                 | 5   | μA    |

| I <sub>LEAKAGE</sub>  | Output Leakage Current | CELL_ON, PCS_ON CELL_GAIN, PCS_GAIN                                         |       |                 | 10  | μΑ    |

|                       |                        | A1_SINK                                                                     |       |                 | 5   |       |

| R <sub>DS-ON</sub> MC | MOSFET's ON Resistance | P-Ch, V <sub>DD</sub> = 3V<br>CELL_ON, PCS_ON<br>CELL_GAIN, PCS_GAIN        | 275   |                 | 500 |       |

|                       |                        | P-Ch, V <sub>DD</sub> = 2V<br>CELL_ON, PCS_ON<br>CELL_GAIN, PCS_GAIN        | 430   |                 | 650 | mΩ    |

| V <sub>IH</sub>       | Logic High Input       | $1.8V \le V_{DD} < 2.5V$<br>EN_CELL, EN_PCS, INV_A1,<br>GAIN_MODE, INV_A2   |       | 1.4             |     | V     |

|                       |                        | $2.5V \le V_{DD} \le 3.5V$<br>EN_CELL, EN_PCS, INV_A1,<br>GAIN_MODE, INV_A2 |       | 2.0             |     | V     |

| V <sub>IL</sub>       | Logic Low Input        | $1.8V \le V_{DD} \le 3.5V$<br>EN_CELL, EN_PCS, INV_A1,<br>GAIN_MODE, INV_A2 |       |                 | 0.4 | V     |

| V <sub>OH</sub>       | Logic High Output      | PA_ON, INV_Y1,<br>I <sub>SOURCE</sub> = 1 mA                                | 2.93  | 2.8             |     | V     |

|                       |                        | INV_Y2,<br>I <sub>SOURCE</sub> = 1 mA                                       | 2.74  | 2.74 <b>2.5</b> |     | , v   |

| V <sub>OL</sub>       | Logic Low Output       | PA_ON, INV_Y1, I <sub>SINK</sub> = 1 mA                                     | 80    | 200             |     |       |

|                       |                        | INV_Y2, A1_SINK<br>I <sub>SINK</sub> = 1 mA                                 | 16    |                 | 55  | mV    |

### **AC Electrical Characteristics**

Unless otherwise noted,  $V_{DD1} = V_{DD2} = 3V$ ,  $C_{LOAD} = 50$  pF. Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}$ C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $-40^{\circ}$ C to  $+85^{\circ}$ C. (Note 7)

| Symbol            | Parameter                      | Conditions                                                           | Typ | Limit |     | Units  |

|-------------------|--------------------------------|----------------------------------------------------------------------|-----|-------|-----|--------|

|                   |                                | Conditions                                                           | Тур | Min   | Max | Ullits |

| t <sub>PLH</sub>  | Propagations Delay Low to High | EN_CELL to PA_ON or EN_PCS to PA_ON                                  | 10  |       | 80  | ns     |

|                   |                                | EN_CELL to CELL_ON or EN_PCS to PCS_ON $R_{PD} = 100\Omega$          | 7   |       | 56  | ns     |

|                   |                                | GAIN_MODE to CELL_GAIN or GAIN_MODE to PCS_GAIN $R_{PD} = 100\Omega$ | 7   |       | 56  | ns     |

|                   |                                | INV_A1 to INV_Y1                                                     | 10  |       | 80  | ns     |

|                   |                                | INV_A2 to INV_Y2                                                     | 25  |       | 200 | ns     |

| t <sub>PHL</sub>  | Propagations Delay High to Low | EN_CELL to PA_ON or<br>EN_PCS to PA_ON                               | 10  |       | 80  | ns     |

|                   |                                | EN_CELL to CELL_ON or EN_PCS to PCS_ON $R_{PD} = 100\Omega$          | 25  |       | 200 | ns     |

|                   |                                | GAIN_MODE to CELL_GAIN or GAIN_MODE to PCS_GAIN $R_{PD} = 100\Omega$ | 20  |       | 160 | ns     |

|                   |                                | INV_A1 to INV_Y1                                                     | 10  |       | 80  | ns     |

|                   |                                | INV_A1 to A1_SINK R <sub>PU</sub> = 10 kΩ                            | 5   |       | 40  | ns     |

|                   |                                | INV_A2 to INV_Y2                                                     | 5   |       | 40  | ns     |

| t <sub>RISE</sub> | Rise Time                      | PA_ON                                                                | 15  |       | 120 |        |

|                   |                                | INV_Y2                                                               | 50  |       | 400 | ns     |

|                   |                                | INV_Y1                                                               | 20  |       | 160 |        |

| T <sub>FALL</sub> | Fall Time                      | PA_ON                                                                | 15  |       | 120 |        |

|                   |                                | INV_Y2                                                               | 10  |       | 80  | ns     |

|                   |                                | INV_Y1                                                               | 20  |       | 160 |        |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula:

$$PD = \frac{T_J - T_A}{\theta_{JA}}$$

where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient temperature. The 2.0W rating appearing under Absolute Maximum Ratings results from substituting the Absolute Maximum junction temperature, 150°C for  $T_J$ , 70°C for  $T_A$  and 39.8°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures below 70°C. Less power can be dissipated safely at ambient temperatures above 70°C. The Absolute Maximum power dissipation can be increased by 25 mW for each degree below 70°C, and it must be derated by 25 mW for each degree above 70°C.

Note 4: The human body model is 100 pF discharged through a 1.5 k $\Omega$  resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

Note 5: Like the Absolute Maximum power dissipation, the maximum power dissipation depends on the ambient temperature. The 1.38W rating appearing under Absolute Maximum Ratings results from substituting the Maximum junction temperature, 125°C for  $T_J$ , 70°C for  $T_A$  and 39.8°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures above 70°C. The Absolute Maximum power dissipation can be increased by 25 mW for each degree below 70°C, and it must be derated by 25 mW for each degree above 70°C.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: All AC parameters are guaranteed by design, not production tested.

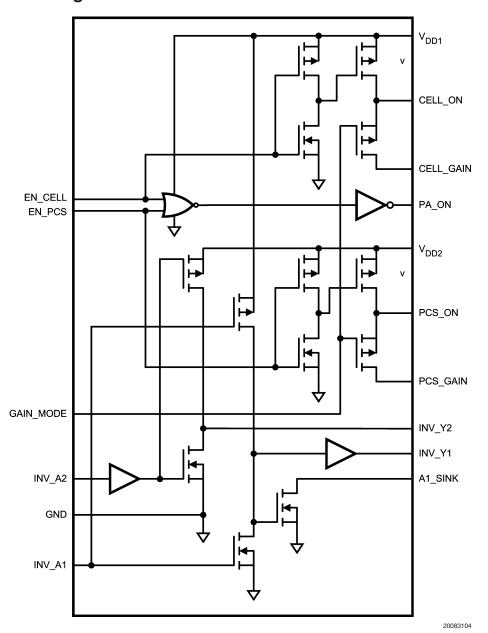

# LP3939 Block Diagram

**Truth Tables**

TABLE 1. PA Enables

| INPUTS  |        | OUTPUTS   |        |       |  |

|---------|--------|-----------|--------|-------|--|

| EN_CELL | EN_PCS | CELL_ON   | PCS_ON | PA_ON |  |

| 0       | 0      | 0         | 0      | 0     |  |

| 1       | 0      | 1         | 0      | 1     |  |

| 0       | 1      | 0         | 1      | 1     |  |

| 1       | 1      | Not Valid |        |       |  |

Note: Measured with a 10  $k\Omega$  pull down resistor on CELL\_ON and PCS\_ON.

# Truth Tables (Continued)

TABLE 2. PA Gain Mode

|           | INPUTS  | OUTPUTS |           |          |  |

|-----------|---------|---------|-----------|----------|--|

| GAIN_MODE | EN_CELL | EN_PCS  | CELL_GAIN | PCS_GAIN |  |

| 0         | 0       | 0       | 0         | 0        |  |

| 0         | 1       | 0       | 1         | 0        |  |

| 1         | 1       | 0       | 0         | 0        |  |

| 0         | 0       | 1       | 0         | 1        |  |

| 1         | 0       | 1       | 0         | 0        |  |

| X         | 1       | 1       | Not Valid |          |  |

Note: Measured with a 10 k $\Omega$  pull down resistor on CELL\_GAIN and PCS\_GAIN.

**TABLE 3. Current Sink Control**

| INPUTS | OUTPUTS |         |  |

|--------|---------|---------|--|

| INV_A1 | INV_Y1  | A1_SINK |  |

| 0      | 1       | 0       |  |

| 1      | 0       | 1       |  |

| INV_A2 | INV_Y2  |         |  |

| 0      | 1       |         |  |

| 1      | 0       |         |  |

Note: Measured with a 10 k $\Omega$  pull up resistor on A1\_SINK.

www.national.com

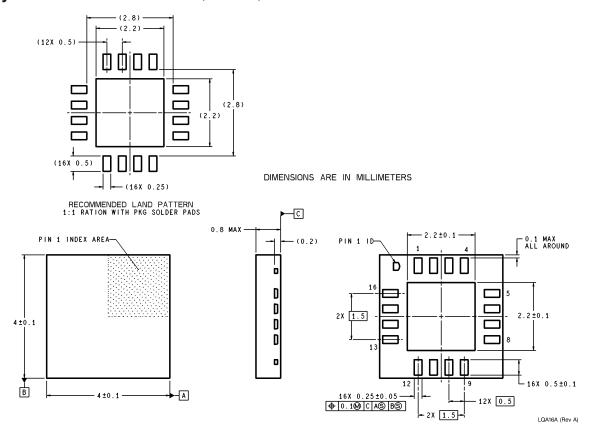

### Physical Dimensions inches (millimeters) unless otherwise noted

NOTES: UNLESS OTHERWISE SPECIFIED

- 1. STANDARD LEAD FINISH TO BE 5.08 MICROMETERS MINIMUM LEAD/TIN (SOLDER) ON COPPER.

- 2. NO JEDEC REGISTRATION AS OF APRIL 2000.

16-Lead Plastic Quad Package

Order Number LP3939ILQ or LP3939ILQX

NS Package Number LQA16A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560