## **LP3927**

# Cellular/PCS System Power Management IC

# **General Description**

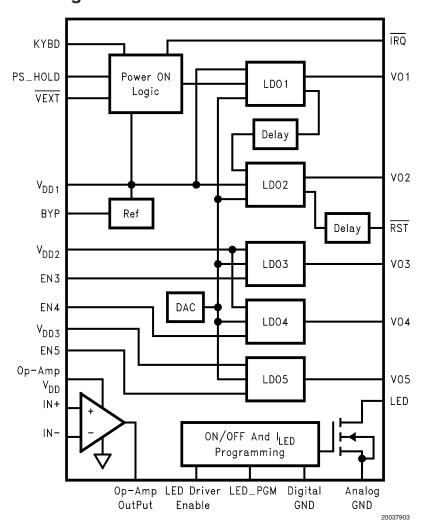

The LP3927 system power management IC is designed for cellular/PCS handsets as well as other portable systems that require intelligent power management. Each device contains five low-dropout linear regulators (LDO's), a reset timer, a power-up control logic, a general-purpose open drain output that can be used to light LEDs, and a CMOS rail-to-rail input/output operational amplifier.

Each linear regulator features an extremely low dropout voltage of 100 mV (typ) at maximum output current. LDO1 and LDO2 are powered on and off by either the KYBD or the VEXT pin. LDO3, LDO4 and LDO5 each have its independent enable pin. LDO1 and LDO4 are rated at 150 mA each, LDO2 and LDO5 are rated at 200 mA each and LDO3 is rated at 100 mA. All LDO's are optimized for low noise and high isolation.

The open drain output current sink can be programmed up to 150 mA by using an external low cost resistor.

A single supply, low voltage operational amplifier has rail to rail input and output with 600 kHz of gain-bandwidth product.

# **Key Specifications**

- 3.0V to 5.5V Input Voltage Range

- Two 200 mA, Two 150 mA and One 100 mA LDO's

- 100 mV typ Dropout Voltage @ I<sub>MAX</sub>

- 150 mA General-Purpose Open-drain programmable current sink for back light LED

- Low Voltage Rail to Rail Input/Output Operational Amplifier

- 28 pin LLP package

# **Applications**

- Cellular/PCS handsets

- PDA's, Palmtops, and portable terminals

- Single-Cell Li+ Systems

- 2- or 3- Cell NiMH, NiCd or Alkaline System

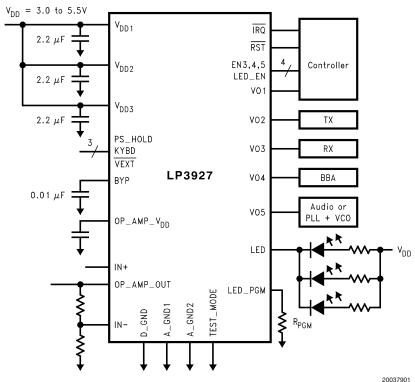

# **Typical Application Circuit**

$V_{\rm DD1},\,V_{\rm DD2}$  and  $V_{\rm DD3}$  must be tied together externally. Collectively called  $V_{\rm DD}.$

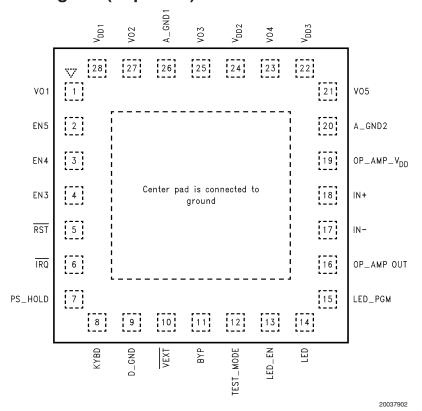

# LP3927 Pin Out Diagram (Top View)

# **Output Current Rating and Voltage Options**

|      | I <sub>MAX</sub> (mA) | Voltage Options (V)      |

|------|-----------------------|--------------------------|

| LDO1 | 150                   | 1.8, 1.9, 2.5, 2.6*, 2.7 |

| LDO2 | 200                   | 1.8, 2.85*, 2.9, 3.0     |

| LDO3 | 100                   | 2.7, 2.8, 2.9*, 3.0      |

| LDO4 | 150                   | 2.7, 2.8, 2.9*, 3.0      |

| LDO5 | 200                   | 2.7, 2.8, 2.9, 3.0*      |

|      | I <sub>MAX</sub> (mA) | Voltage Options (V)       |

|------|-----------------------|---------------------------|

| LDO1 | 150                   | 1.85*, 1.9, 2.5, 2.6, 2.7 |

| LDO2 | 200                   | 1.8, 2.85*, 2.9, 3.0      |

| LDO3 | 100                   | 2.7, 2.85*, 2.9, 3.0      |

| LDO4 | 150                   | 2.6*, 2.85, 2.9, 3.0      |

| LDO5 | 200                   | 2.7, 2.85*, 2.9, 3.0      |

<sup>\*</sup> denotes the voltage options that are available currently. For other options, please contact the National Semiconductor factory sales office/distributors for availability and specifications. Voltage options in the two tables cannot be mixed and matched.

# **Ordering Information**

| LP3927 Supplied as<br>1000 Units, tape and<br>reel | LP3927 Supplied as<br>4500 Units, tape and<br>reel | Standard<br>LDO delay | Optional<br>LDO delay | VO1<br>(V) | VO2<br>(V) | VO3<br>(V) | VO4<br>(V) | VO5<br>(V) | TOP<br>MARKING |

|----------------------------------------------------|----------------------------------------------------|-----------------------|-----------------------|------------|------------|------------|------------|------------|----------------|

| LP3927ILQ-AH                                       | LP3927ILQX-AH                                      |                       | Х                     | 2.6        | 2.85       | 2.9        | 2.9        | 3.0        | 3927AH         |

| LP3927ILQ-AJ                                       | LP3927ILQX-AJ                                      | Х                     |                       | 2.6        | 2.65       | 2.9        | 2.9        | 3.0        | 3927AJ         |

| LP3927ILQ-AP                                       | LP3927ILQX-AP                                      |                       | Х                     | 1.85       | 2.85       | 2.85       | 2.6        | 2.85       | 3927AP         |

For LDO delay options, please refer to Electrical Characteristics Table.

# **Pin Description**

| Pin | Name                   | Functional Description                                                                                                                              |

|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VO1                    | 150 mA, LDO1 output pin.                                                                                                                            |

| 2   | EN5                    | LDO5 enable input.                                                                                                                                  |

| 3   | EN4                    | LDO4 enable input.                                                                                                                                  |

| 4   | EN3                    | LDO3 enable input.                                                                                                                                  |

| 5   | RST                    | Externally pulled high, open drain output to processor/memory reset.                                                                                |

| 6   | ĪRQ                    | Externally pulled high, open drain output to processor interrupt indicating KYBD has gone high.                                                     |

| 7   | PS_HOLD                | Input from the processor to the LP3927. A HIGH indicates a steady supply of power is granted. Refer to "Application Hints" section for more detail. |

| 8   | KYBD                   | An active high input signal indicating the keyboard "On/Off" button has been asserted. Refer to "Application Hints" section for more detail.        |

| 9   | D_GND                  | Digital ground, used primarily for the digital and DAC circuits.                                                                                    |

| 10  | VEXT                   | Active low input indicating a battery charger insertion Refer to "Application Hints" section for more detail.                                       |

| 11  | BYP                    | Reference bypass pin.                                                                                                                               |

| 12  | TEST_MODE              | Pin used for production testing, factory use only. This pin should be grounded in applications.                                                     |

| 13  | LED_EN                 | LED driver enable input.                                                                                                                            |

| 14  | LED                    | LED driver, drain connection of the LED drive MOSFET.                                                                                               |

| 15  | LED_PGM                | LED drive current programming pin.                                                                                                                  |

| 16  | OP_AMP_OUT             | Operational amplifier output pin.                                                                                                                   |

| 17  | IN-                    | - input of the Op-Amp.                                                                                                                              |

| 18  | IN+                    | + input of the Op-Amp.                                                                                                                              |

| 19  | OP_AMP_V <sub>DD</sub> | Power supply pin for Op-Amp.                                                                                                                        |

| 20  | A_GND2                 | Ground for analog.                                                                                                                                  |

| 21  | VO5                    | 200 mA, LDO5 output pin.                                                                                                                            |

| 22  | $V_{DD3}$              | Input power pin for LDO5. $V_{DD1}$ , $V_{DD2}$ and $V_{DD3}$ must be tied together externally.                                                     |

| 23  | VO4                    | 150 mA, LDO4 output pin.                                                                                                                            |

| 24  | $V_{DD2}$              | Input power pin for LDO3 and LDO4. V <sub>DD1</sub> , V <sub>DD2</sub> and V <sub>DD3</sub> must be tied together externally.                       |

| 25  | VO3                    | 100 mA, LDO3 output pin.                                                                                                                            |

| 26  | A_GND1                 | Ground for analog.                                                                                                                                  |

| 27  | VO2                    | 200 mA, LDO2 output pin.                                                                                                                            |

| 28  | $V_{DD1}$              | Input power pin for LDO1 and LDO2. $V_{DD1}$ , $V_{DD2}$ and $V_{DD3}$ must be tied together externally.                                            |

# **Functional Block Diagram**

# **Absolute Maximum Ratings (Notes 1,**

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

All pins except LED\_PGM, BYP, op amp's inputs & output -0.3V to 6.0V OP\_AMP\_OUT, IN-, IN+ -0.3V to 5.5V GND to GND SLUG ±0.3V Junction Temperature 150°C Storage Information -65°C to 150°C

Soldering Temperature

Pad Temperature 235°C Maximum Power Dissipation (Note 3) 2.6W

ESD (Note 4):

KYBD 4 kV 2 kV All other pins

# Operating Ratings (Notes 1, 2)

$V_{DD1}$ ,  $V_{DD2}$ ,  $V_{DD3}$ , KYBD, OP\_AMP\_ $V_{DD}$ 3.0V to 5.5V EN3, EN4, EN5 -0.3V to  $(V_{DD} + 0.3V)$

C<sub>OUT</sub>:

1.0  $\mu F$  to 20.0  $\mu F$ Capacitance  $0.005\Omega$  to  $0.5\Omega$ **ESR** Junction Temperature -40°C to 125°C Operating Temperature -40°C to 85°C

Thermal Resistance (Note 5)

$\theta_{JA}$  (LLP28) 30.8°C/W Maximum Power Dissipation (Note 6) 1.78W

# **Electrical Characteristics, LDO's**

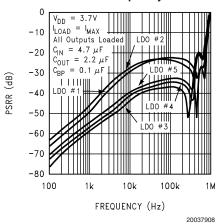

Unless otherwise noted,  $V_{DD} = V_{OUT(target)} + 0.7V$ ,  $C_{IN}$  ( $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{DD3}$ ) = 4.7  $\mu$ F,  $C_{OUT}$  (VO1 to VO5) = 2.2  $\mu$ F,  $C_{byp}$  = 0.1  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40°C to +85°C. (Notes 7, 8)

| Symbol                             | Davamatav                                                  | Conditions                                                                                                           | Turning        | Limit |                   | Halt-                |

|------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------|-------|-------------------|----------------------|

| Symbol                             | Parameter                                                  | Conditions                                                                                                           | Typical        | Min   | Max               | Units                |

| $V_{DD}$                           | Input Voltage Range                                        | $V_{DD1}, V_{DD2}, V_{DD3}, KYBD$                                                                                    | 3.7            | 3     | 5.5               | V                    |

| $\Delta V_{OUT}$                   | Output Voltage Tolerance                                   | $I_{OUT} = I_{MAX}/2,$ $V_{DD} = 3.7V$                                                                               |                | -2    | +2                | %                    |

|                                    | Load Regulation                                            | $I_{OUT}$ = 100 $\mu$ A to $I_{MAX}$ , $V_{DD}$ = 3.7V                                                               |                | -2    | +2                | %                    |

|                                    | Line Regulation                                            | $V_{DD} = V_{OUT(target)} + 0.7V \text{ to } 5.5V$<br>$I_{OUT} = I_{MAX}/2$                                          |                | -40   | +40               | mV                   |

|                                    | Total Accuracy Error                                       |                                                                                                                      |                | -3.5  | +3.5              | %                    |

| V <sub>IN</sub> - V <sub>OUT</sub> | Dropout Voltage                                            | I <sub>OUT</sub> = I <sub>MAX</sub> (Note 9)                                                                         | 100            |       | 170<br><b>200</b> | mV                   |

| e <sub>N</sub>                     | Output Noise Voltage                                       | $I_{OUT} = 100 \mu A,$<br>10 Hz $\leq f \leq 100 \text{ kHz}$                                                        | 27             |       |                   | $\mu V_{rms}$        |

| PSRR                               | Power Supply Ripple<br>Rejection Ratio                     | $C_{IN} = 2.2 \mu F$ , $I_{OUT} = I_{MAX}$ ,<br>f = 100  Hz<br>f = 1  kHz<br>f = 10  kHz                             | 45<br>45<br>30 |       |                   | dB                   |

|                                    |                                                            | f = 100 kHz                                                                                                          | 10             |       |                   |                      |

|                                    | Cross Talk                                                 | (Note 10)                                                                                                            | 30             |       |                   | dB                   |

| I <sub>Q</sub>                     | Quiescent Current                                          | $I_{OUT} = 0$ , PS_HOLD = KYBD = 0<br>$\overline{VEXT} = V_{DD}$                                                     |                |       | 5<br><b>8</b>     | μΑ                   |

| I <sub>GND</sub>                   | Ground Current                                             | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 1 mA,<br>LDO3, LDO4, LDO5 OFF                                                | 100            |       | 200               | μΑ                   |

|                                    |                                                            | I <sub>OUT1</sub> , I <sub>OUT2</sub> , I <sub>OUT3</sub> , I <sub>OUT4</sub> , I <sub>OUT5</sub> = I <sub>MAX</sub> | 400            |       | 950               |                      |

| I <sub>sc</sub>                    | Short Circuit Current Limit                                | $V_{OUT} = 0V$                                                                                                       | 400            |       |                   | % of I <sub>MA</sub> |

| C <sub>OUT</sub>                   | Output Capacitor                                           | Capacitance                                                                                                          |                | 1     | 20                | μF                   |

|                                    |                                                            | ESR                                                                                                                  |                | 5     | 500               | mΩ                   |

| R <sub>SHUNT</sub>                 | V <sub>O2</sub> - V <sub>O5</sub> Output Shunt<br>Resistor |                                                                                                                      | 70             |       | 200               | Ω                    |

# **Electrical Characteristics, Digital Interface**

| Cumbal               | Parameter Conditions  |                                       | Turning | Limit               |                     | Units |  |

|----------------------|-----------------------|---------------------------------------|---------|---------------------|---------------------|-------|--|

| Symbol               | Parameter             | Conditions                            | Typical | Min                 | Max                 | Units |  |

| V <sub>OL</sub>      | Logic Low Output      | RST and IRQ                           |         |                     | 150                 | mV    |  |

|                      |                       | I <sub>LOAD</sub> = 250 μA            |         |                     |                     |       |  |

| V <sub>IH</sub>      | Logic High Input      | KYBD and VEXT                         |         | 0.7 V <sub>DD</sub> |                     | V     |  |

|                      |                       | EN3-5, PS_HOLD                        |         | 1.4                 |                     |       |  |

|                      |                       | LED_EN for AH and AJ options          |         | 0.85V <sub>DD</sub> |                     |       |  |

|                      |                       | LED_EN for AP option                  |         | 2.0                 |                     |       |  |

| V <sub>IL</sub>      | Logic Low Input       | KYBD and VEXT                         |         |                     | 0.2 V <sub>DD</sub> | V     |  |

|                      |                       | EN3-5, PS_HOLD                        |         |                     | 0.4                 |       |  |

|                      |                       | LED_EN for AH and AJ options          |         |                     | 0.2 V <sub>DD</sub> |       |  |

|                      |                       | LED_EN for AP option                  |         |                     | 0.4                 |       |  |

| I <sub>LEAKAGE</sub> | Input Leakage Current | VEXT, PS_HOLD, IRQ,                   |         | -10                 | +10                 | μΑ    |  |

|                      |                       | KYBD, EN3–5, $0V \le V_{DD} \le 5.5V$ |         |                     |                     |       |  |

# **Electrical Characteristics, Error Flag**

| Cumbal               | Parameter               | Conditions                                            | Typical | Limit |      | Units              |

|----------------------|-------------------------|-------------------------------------------------------|---------|-------|------|--------------------|

| Symbol               | Parameter               | Conditions                                            | Typical | Min   | Max  | Offics             |

| $V_{Th	ext{-}H}$     | Error Flag High         | V <sub>o1</sub> and V <sub>o2</sub> Outputs (Note 11) | 95      | 92    | 98   | % V <sub>OUT</sub> |

| $V_{Th	ext{-L}}$     | Error Flag Low          |                                                       | 90      | 89    | 92   |                    |

| t <sub>DELAY-H</sub> |                         | (Note 12)                                             | 6       | 0     | 10   | μs                 |

| t <sub>DELAY-L</sub> |                         |                                                       | 6       | 0     | 10   | μs                 |

|                      | Keyboard Debounce Delay | (Note 13)                                             | 32      | 16    | 64   | ms                 |

|                      | VEXT Debounce Delay     | (Note 13)                                             | 32      | 16    | 64   | ms                 |

| R <sub>DELAY</sub>   | RST Reset Delay         | (Note 14)                                             | 20      | 10    | 40   | ms                 |

| t <sub>DELAY</sub>   | LDO Delay, standard     | (Note 15)                                             | 125     | 0     | 250  | μs                 |

|                      | LDO Delay, optional     |                                                       | 10      | 5     | 20   | ms                 |

| t <sub>Hold-UP</sub> | PS_HOLD Input           | (Note 16)                                             | 500     | 250   | 1000 | ms                 |

# **Electrical Characteristics, Backlight LED Driver**

| Symbol           | Parameter     | Conditions                           | Typical | Li  | Units |        |

|------------------|---------------|--------------------------------------|---------|-----|-------|--------|

| Syllibol         | Parameter     | Conditions                           | Турісаі | Min | Max   | Offics |

| I <sub>LED</sub> | Drive Current | $V_{LED} = 1V, R_{PGM} = 130k\Omega$ | 150     | 125 | 175   | mA     |

# **Electrical Characteristics, Operational Amplifier**

Unless otherwise noted,  $V_{OP\_AMP\_VDD} = 3.3V$ ,  $V_{CM} = V_{OUT} = V_{OP\_AMP\_VDD}/2$  and  $R_{LOAD} > 1$  M $\Omega$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}$ C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}$ C to  $+85^{\circ}$ C. (Note 7)

| Symbol             | Parameter                    | Conditions                                                 | Typical | Limit |     | Units |

|--------------------|------------------------------|------------------------------------------------------------|---------|-------|-----|-------|

| Symbol             | Parameter                    | Conditions                                                 | Typical | Min   | Max | Units |

| $V_{DD}$           | OP_AMP_V <sub>DD</sub>       |                                                            | 3.3     | 3     | 5.5 | V     |

| Vos                | Input Offset Voltage         |                                                            | 1.2     |       | 10  | mV    |

| TC V <sub>os</sub> | Offset Voltage Drift         |                                                            | 10      |       |     | μV/°C |

| I <sub>B</sub>     | Input Bias Current           |                                                            | 0.2     |       |     | nA    |

| Ios                | Input Offset Current         |                                                            | 0.1     |       |     | nA    |

| R <sub>IN</sub>    | Input Resistance             |                                                            | >1      |       |     | GΩ    |

| CMRR               | Common-Mode Rejection Ratio  | $0V \le V_{CM} \le 2.7V$                                   | 70      |       |     | dB    |

| PSRR               | Power Supply Rejection Ratio | $V_{OP\_AMP\_VDD} = 2.7V \text{ to}$ $3.3V$ , $V_{CM} = 0$ | 60      |       |     | dB    |

## **Electrical Characteristics, Operational Amplifier** (Continued)

Unless otherwise noted,  $V_{OP\_AMP\_VDD} = 3.3V$ ,  $V_{CM} = V_{OUT} = V_{OP\_AMP\_VDD}/2$  and  $R_{LOAD} > 1$  M $\Omega$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $-40^{\circ}C$  to  $+85^{\circ}C$ . (Note 7)

| Symbol           | Parameter                   | Conditions                | Typical | Limit |     | Units  |

|------------------|-----------------------------|---------------------------|---------|-------|-----|--------|

|                  | Farameter                   | Conditions                |         | Min   | Max | Ullits |

| C <sub>IN</sub>  | Common-Mode Input Capacitor |                           | 3       |       |     | pF     |

| V <sub>OUT</sub> | Output Swing                | $R_{LOAD} = 2 k\Omega$    |         |       | 0.5 | V      |

|                  |                             |                           |         | 3.1   |     |        |

| Is               | Supply Current              | $V_{OP\_AMP\_VDD} = 3.0V$ | 0.5     |       | 1.4 | mA     |

| SR               | Slew Rate                   |                           | 0.7     |       |     | V/µs   |

| GBW              | Gain-Bandwidth Product      |                           | 0.6     |       |     | MHz    |

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions, see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

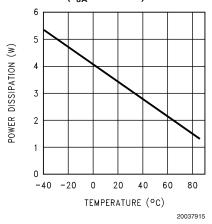

Note 3: The Absolute Maximum power dissipation depends on the ambient temperature and can be calculated using the formula

$$P = (T_J - T_A)/\theta_{JA}, \tag{1}$$

where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance. The 2.6W rating appearing under Absolute Maximum Ratings results from substituting the Absolute Maximum junction temperature, 150°C, for  $T_J$ , 70°C for  $T_A$ , and 30.8°C/W for  $\theta_{JA}$ . More power can be dissipated safely at ambient temperatures above 70°C. The Absolute Maximum power dissipation can be increased by 32.5 mW for each degree below 70°C, and it must be derated by 32.5 mW for each degree above 70°C.

Note 4: The human-body model is used. The human-body model is 100 pF discharged through 1.5 k $\Omega$ .

**Note 5:** This figure is taken from a thermal modeling result. The test board is a 4 layer FR-4 board measuring 101mm x 101mm x 1.6mm with a 3 x 3 array of thermal vias. The ground plane on the board is 50mm x 50mm. Ambient temperature in simulation is 22°C, still air. Power dissipation is 1W.

Note 6: Like the Absolute Maximum power dissipation, the maximum power dissipation for operation depends on the ambient temperature. The 1.78W rating appearing under Operating Ratings results from substituting the maximum junction temperature for operation, 125°C, for  $T_J$ , 70°C for  $T_A$ , and 30.8°C/W for  $\theta_{JA}$  into (1) above. More power can be dissipated at ambient temperatures above 70°C. Less power can be dissipated at ambient temperatures above 70°C. The maximum power dissipation for operation can be increased by 32.5 mW for each degree below 70°C, and it must be derated by 32.5 mW for each degree above 70°C.

Note 7: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are 100% production tested or guaranteed through statistical analysis. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

Note 8: The target output voltage, which is labeled V<sub>OUT(target)</sub>, is the desired or ideal output voltage.

**Note 9:** Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This specification does not apply in cases it implies operation with an input voltage below the 2.5V minimum appearing under Operating Ratings. For example, this specification does not apply for devices having 1.5V outputs because the specification would imply operation with an input voltage at or about 1.5V.

Note 10: Pulsing the load of LDO X from 100µA to Imax and measuring its effects at the output of LDO Y. LDO Y enabled but under no load.

Note 11: The error flags are internal to the chip. There is no external access to the signals. LDO1 error flag and the LDO2 error flag will go HIGH when the respective LDO reaches its  $V_{Th-H}$  value. The error flags will go LOW when the respective LDO reaches its  $V_{Th-H}$  value.

Note 12: The t<sub>DELAY-L</sub> is the delay between LDO1 reaching its V<sub>Th-L</sub> and its error flag going HIGH. The t<sub>DELAY-L</sub> is the delay between LDO1 reaching its V<sub>Th-L</sub> and its error flag going LOW. Same delays apply to LDO2 and its error flag.

Note 13: Refer to Timing Diagram.

Note 14: The delay between LDO2 error flag HIGH and  $\overline{\text{RST}}$  signal HIGH in the power up sequence. In the power down sequence, it is the delay between  $\overline{\text{RST}}$  signal LOW and LDO2 disabled.

Note 15: The delay between LDO1 error flag HIGH and LDO2 enable in power up sequence. In the power down sequence, it is the delay between LDO2 error flag LOW and LDO1 disable. For the optional LDO delay, please contact the factory for availability.

Note 16: Time between RST high and PS\_HOLD going high.

### **PSRR vs Frequency**

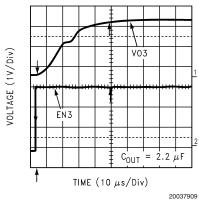

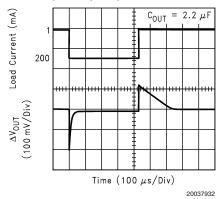

# LDO3 Enable Response (Cout=2.2μF)

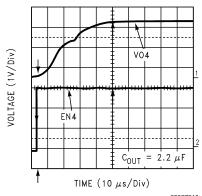

### LDO4 Enable Response (Cout=2.2μF)

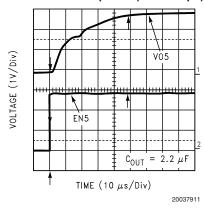

### LDO5 Enable Response (Cout=2.2μF)

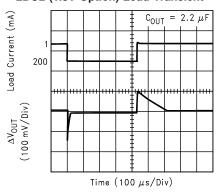

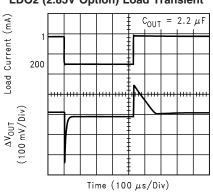

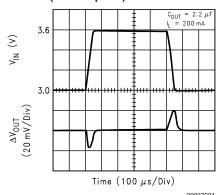

### LDO2 (1.8V Option) Load Transient

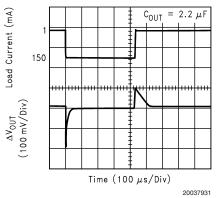

### LDO2 (2.85V Option) Load Transient

20037930

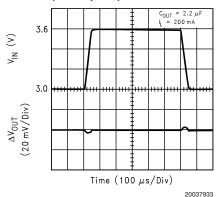

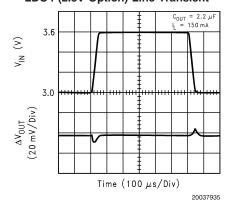

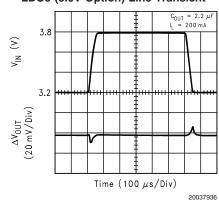

# Typical Performance Characteristics Unless otherwise specified, $C_{IN}$ = 1 $\mu$ F ceramic, $C_{BYP}$ = 0.01 $\mu$ F, $V_{DD}$ = $V_{OUT}$ + 0.2V, $T_A$ = 25°C, Enable pin is tied to $V_{DD}$ . (Continued)

### LDO4 (2.8V Option) Load Transient

### LDO2 (1.8V Option) Line Transient

### LDO4 (2.8V Option) Line Transient

### LDO5 (3.0V Option) Load Transient

### LDO2 (2.85V Option) Line Transient

### LDO5 (3.0V Option) Line Transient

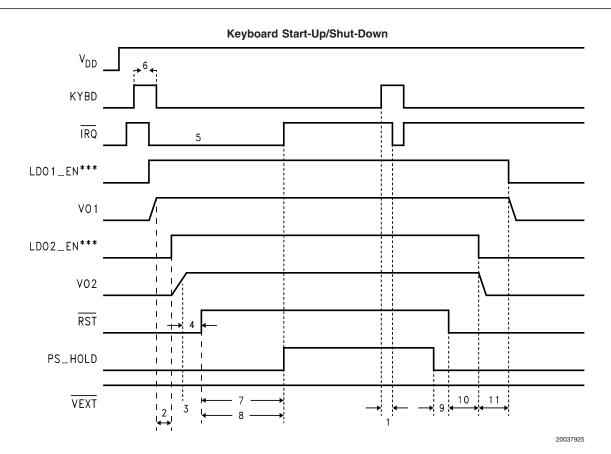

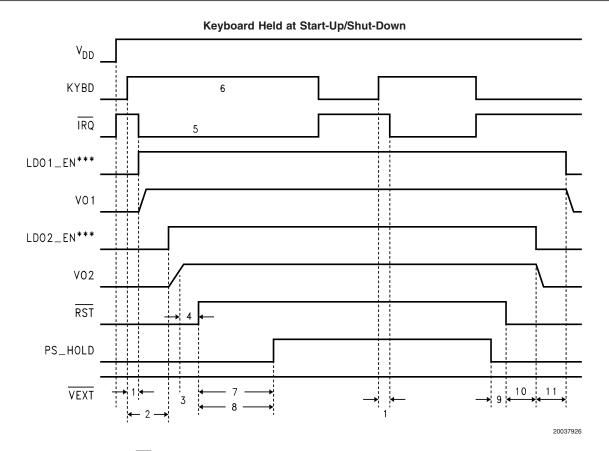

Note: Diagram indicates Open Drain  $\overline{\text{IRQ}}$  tied to  $V_{DD}$ .

\*\*\* = Internal signal

- 1. Keyboard de-bounce delay, 32 msec typ.

- 2. Delay between LDO1 reaching 95% of its output voltage and LDO2 enable, 125 µsec typical.

- 3. Both LDO1 and LDO2 outputs reach 95% of respective output voltage, start  $\overline{\text{RST}}$  timer.

- 4. RST delay, 20 msec typical.

- 5. IRQ is active low.

- 6. Keyboard press must be greater than 32 msec.

- 7. PS\_HOLD timer begins upon  $\overline{\text{RST}}$  going high.

- 8. Maximum of 500 msec period from RST going high to PS\_HOLD going high.

- 9. Response time from PS\_HOLD going low to  $\overline{\text{RST}}$  going low.

- 10. Delay between  $\overline{\text{RST}}$  high-low transition to LDO2 disable.

- 11. Delay between LDO2 disable and LDO1 disable.

Note: Diagram indicates Open Drain  $\overline{IRQ}$  tied to  $V_{DD}$ .

\*\*\* = Internal signal

- 1. Keyboard de-bounce delay, 32msec typ.

- 2. Delay between LDO1 reaching 95% of its output voltage and LDO2 enable.

- 3. Both LDO1 and LDO2 outputs reach 95% of the respective output voltage, start RST timer.

- 4. Reset delay.

- 5. IRQ is active low.

- 6. Keyboard press must be greater than 32 msec.

- 7. PS\_HOLD timer begins upon RST going high.

- 8. Maximum of 500 msec period from RST going high to PS\_HOLD going high.

- 9. Response time from PS\_HOLD going low to  $\overline{\text{RST}}$  going low.

- 10. Delay between  $\overline{\text{RST}}$  high-low transition to LDO2 disable.

- 11. Delay between LDO2 disable and LDO1 disable.

11

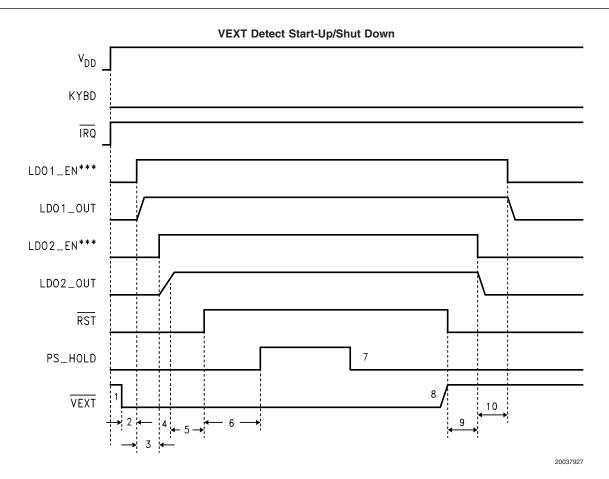

Note: Diagram indicates Open Drain  $\overline{\text{IRQ}}$  tied to  $V_{DD}$ .

\*\*\* = Internal signal

- 1. VEXT goes active low.

- 2. VEXT 32 msec de-bounce period.

- 3. Delay between LDO1 and LDO2 enables.

- 4. Both LDO1 and LDO2 outputs reach 95% of respective output voltage, start Reset timer.

- 5. Reset delay.

- 6. Period between Reset and PS\_HOLD going high is not relevant since  $\overline{\text{VEXT}}$  is low

- 7. PS\_HOLD goes low but LDOs continue to run since  $\overline{\text{VEXT}}$  is low.

- 8. PS\_HOLD is low and VEXT goes high, RST pin goes low.

- 9. Delay between  $\overline{\text{RST}}$  going low and LDO2 disabled.

- 10. Delay between LDO2 and LDO1 disabled.

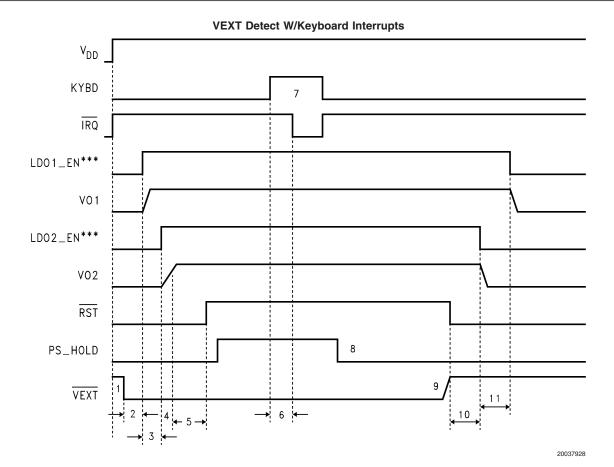

Note: Diagram indicates Open Drain  $\overline{IRQ}$  tied to  $V_{DD}$ .

\*\*\* = Internal signal

- 1. VEXT goes active low.

- 2. VEXT 32 msec de-bounce period.

- 3. Delay between LDO1 and LDO2 enable.

- 4. Both LDO1 and LDO2 outputs reach 95% of respective output voltage, start Reset timer.

- 5. Reset delay.

- 6. Keyboard de-bounce delay.

- 7. Keyboard pulse must be a minimum of 32 msec.

- 8. PS\_HOLD may go low after Key press, but LDOs stay on since VEXT is low.

- 9. VEXT goes high, begin shutdown since PS\_HOLD is low.

- 10. Delay between RST going low and LDO2 disabled.

- 11. Delay between LDO2 disable and LDO1 disabled.

# **Application Hints**

### LP3927 FUNCTION DESCRIPTION

The LP3927 is designed for cellular/PCS handsets. The LDOs power the microprocessor, RF and digital sections of the phone. When a KYBD debounce of longer than 32 ms is detected by the LP3927, the  $\overline{IRQ}$  signal is asserted and sent to the microprocessor. In addition, the KYBD signal turns on LDO1. When LDO1 reaches 95% of its output voltage option, a 125  $\mu s$  delay (standard LDO delay. The optional LDO delay has a 10msec delay) takes place, and LDO2 turns on. When LDO2 reaches 95% of its output voltage option,  $\overline{RST}$  goes high after a 20 ms delay. At this point, the microprocessor comes out of reset and the LP3927 starts the PS\_HOLD timer. If PS\_HOLD goes high before 500 ms,  $\overline{IRQ}$  is de-asserted. If PS\_HOLD stays low for longer than 500 ms,  $\overline{IRQ}$  will still de-assert, but  $\overline{RST}$  will also be asserted, and the part will power down.

The power down sequence is the exact reverse of the power up sequence. PS\_HOLD from the microprocessor goes low, indicating a request to turn the part off. This causes  $\overline{RST}$  to go low. LDO2 will be turned off after a 20 ms delay. When LDO2 drops to 90% of its output voltage option, LDO1 will start to turn off after a 125  $\mu s$  (or a 10msec) delay. Another KYBD debounce after power up does not necessary mean power down.

Whenever LDO1 or LDO2 falls under 90% of the output voltage option,  $\overline{RST}$  immediately goes low to bring PS\_HOLD low in order to turn the part off.

Plugging the charger into the cell phone will cause an external signal VEXT to toggle from high to low. The LP3927 will respond differently to this signal depending on the scenario:

Case 1: If a charger is plugged into the cell phone after the phone is already on, the  $\overline{\text{VEXT}}$  signal go from high to low. The LP3927 will acknowledge this signal but all other signals remain unchanged.

Case 2: If a charger is plugged into the phone while the phone is off,  $\overline{\text{VEXT}}$  signal goes from high to low and the LP3927 will proceed to turn LDO1 on after a 32 ms delay, and the identical power-up sequence follows. This case bypasses the power-up initiated by KYBD and  $\overline{\text{IRQ}}$ . KYBD remains low and  $\overline{\text{IRQ}}$  remains high at all time during power-up.

When the charger is plugged in, the phone cannot be turned off unless both VEXT goes high and PS\_HOLD goes low.

### **LDOs**

The LP3927 contains five LDOs. LDO1 and 2 are powered by the  $V_{\rm DD1}$  line; LDO3 and 4 are powered by the  $V_{\rm DD2}$  line; and LDO5 is powered by the  $V_{\rm DD3}$  line.  $V_{\rm DD1}$ ,  $V_{\rm DD2}$  and  $V_{\rm DD3}$  must be tied together externally. All five LDOs accept an input voltage from 3.0V to 5.5V. This accommodates the full usable range of a single Li-On battery.

LDO1 and 4 each provide 150 mA of current. LDO2 and 5 each provide 200 mA of current. LDO3 provides 100 mA of current. The output of each LDO can be programmed to different voltage levels at the factory. Refer to "Output Current Rating and Voltage Options" Table for more details.

### LDO INPUT CAPACITOR

An input capacitance of  $\approx 2.2~\mu F$  is required between each  $V_{DD}$  input pins and ground. (The amount of the capacitance may be increased without limit).

This capacitor must be located a distance of not more than 1 cm from the input pin and returned to a clean analog ground. Any good quality ceramic, tantalum, or film capacitor may be used at the inputs.

**Important:** Tantalum capacitors can suffer catastrophic failures due to surge current when connected to a low-impedance source of power (like a battery or a very large capacitor). If a tantalum capacitor is used at the input, it must be guaranteed by the manufacturer to have a surge current rating sufficient for the application.

There are no requirements for the ESR on the input capacitor, but tolerance and termperature coefficient must be considered when selecting the capacitor to ensure the capacitance will be  $\approx$  1  $\mu F$  over the entire operating temperature range.

### LDO OUTPUT CAPACITOR

The LDOs are designed specifically to work with very small ceramic output capacitors. A ceramic capacitor (X7R, X5R, Z5U, or Y5V) in 1  $\mu$ F to 20  $\mu$ F range with 5 m $\Omega$  to 500 m $\Omega$  ESR range is suitable in the LP3927 application circuit.

It may also be possible to use tantalum or film capacitors at the output, but these are not as attractive for reasons of size and cost.

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR (Equivalent Series Resistance) value which is within a stable range (5 m $\Omega$  to 500 m $\Omega$ ).

### LED CURRENT DRIVER

The LED pin on the LP3927 is an open-drain output that can provide up to 150 mA to drive backlight LEDs. It is turned on when the LED\_EN pin is pulled high, and off when the LED\_EN pin is pulled low. The external resistor  $R_{PGM}$  connected to the LED\_PGM pin programs the output current of LED. A 130  $k\Omega$  resistor sets the output current to 150 mA. An  $\it approximated$  equation between  $R_{PGM}$  and  $I_{LED}$  is:

$$ILED = \frac{19235}{R_{PCM}}$$

### **OPERATIONAL AMPLIFIER**

The LP3927 has an internal op amp with rail-to-rail input and output and a 600 kHz of gain-bandwidth product.

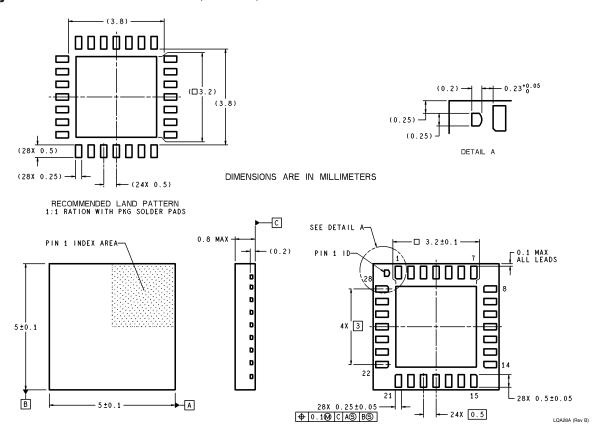

### LEADLESS LEADFRAME PACKAGE (LLP)

The LP3927 is packaged in a 28-lead LLP package for enhanced thermal performance. The 28-lead LLP measures 5 mm x 5 mm x 0.75 mm. Its small size and low profile is ideal for handset applications and other portable applications that require power management.

### THERMAL PERFORMANCE

The LLP package is designed for enhanced thermal performance because of the exposed die attach pad at the bottom center of the package. It brings advantage to thermal performance by creating a very direct path for thermal dissipation. Compared to the traditional leaded packages where the die attach pad is embedded inside the mold compound, the LLP reduces a layer in the thermal path.

The thermal advantage of the LLP package is fully realized only when the exposed die attach pad is soldered down to a thermal land on the PCB board and thermal vias are planted underneath the thermal land. Based on a LLP thermal mea-

# Application Hints (Continued)

surement, junction to ambient thermal resistance  $(\theta_{\text{JA}})$  can be improved by as much as two times if a LLP is soldered on the board with thermal land and thermal vias than if not.

Consider the following equation:

$$P = \frac{(T_J - T_A)}{\theta_{JA}}$$

Where P is the power dissipated,  $T_J$  is the maximum junction temperature of the die,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the thermal resistance of the package.  $T_J$  is specified at 150°C.

According to the above equation, in the case where the LP3927 is dissipating 3W of power,  $T_A$  is limited to 32.6°C when  $T_J$  of 125°C and  $\theta_{JA}$  of 30.8°C/W are used in the equation. In order to operate at a higher ambient temperature, power dissipation has to be reduced. A curve of maximum power dissipation vs ambient temperature is provided below.

Power Dissipation vs Ambient Temperature  $(\theta_{JA}=30.8^{\circ}\text{C/W})$

### LAYOUT CONSIDERATION

The LP3927 has an exposed die attach pad located at the bottom center of the LLP package. It is imperative to create a thermal land on the PCB board when designing a PCB layout for the LLP package. The thermal land helps to conduct heat away from the die, and the land should be the same dimension as the exposed pad on the bottom of the LLP (1:1 ratio). The land should be on both the top and the bottom layer of the PCB board. In addition, thermal vias should be added inside the thermal land to conduct more heat away from the surface of the PCB to the ground plane. Typical pitch and outer diameter for these thermal vias are 1.27 mm and 0.33 mm respectively. Typical copper via barrel plating is 1 oz. although thicker copper may be used to improve thermal performance. The LP3927 bottom pad is connected to ground. Therefore, the thermal land and vias on the PCB board need to be connected to ground.

For more information on board layout techniques, refer to Application Note 1187 "Leadless Leadframe Package (LLP)." The application note also discusses package handling, solder stencil, and assembly process.

## Physical Dimensions inches (millimeters) unless otherwise noted

28 Lead LLP Package NS Package Number Iqa28A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560