# **LP2989LV**

# Micropower 500 mA Low Noise Low Dropout Regulator for Applications with Output Voltages < 2V Designed for Use with Very Low ESR Output Capacitors

# **General Description**

The LP2989LV is a 500 mA fixed-output voltage regulator designed to provide high performance and low noise in applications requiring output voltages < 2V.

Output noise can be reduced to  $18\mu V$  (typical) by connecting an external 10 nF capacitor to the bypass pin.

Using an optimized  $VIP^{\text{TM}}$  (Vertically Integrated PNP) process, the LP2989LV delivers superior performance:

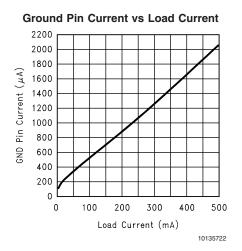

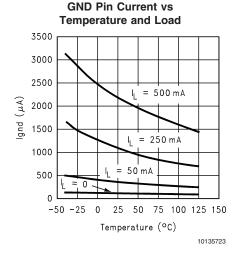

Ground Pin Current: Typically 3 mA @ 500 mA load, and 110  $\mu$ A @ 100  $\mu$ A load.

Sleep Mode: The LP2989LV draws less than 0.8  $\mu$ A quiescent current when shutdown pin is pulled low.

**Error Flag:** The built-in error flag goes low when the output drops approximately 5% below nominal.

**Precision Output:** Guaranteed output voltage accuracy is 0.75% ("A" grade) and 1.25% (standard grade) at room temperature.

For output voltages  $\geq$  2V, see LP2989 datasheet.

### **Features**

- Ultra low dropout voltage

- Guaranteed 500 mA continuous output current

- Very low output noise with external capacitor

- SO-8, Mini SO-8, 8 Lead LLP surface mount packages

- <0.8 µA quiescent current when shutdown

- Low ground pin current at all loads

- 0.75% output voltage accuracy ("A" grade)

- High peak current capability (800 mA typical)

- Wide supply voltage range (16V max)

- Overtemperature/overcurrent protection

- -40°C to +125°C junction temperature range

# **Applications**

- Notebook/Desktop PC

- PDA/Palmtop Computer

- Wireless Communication Terminals

- SMPS Post-Regulator

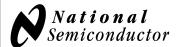

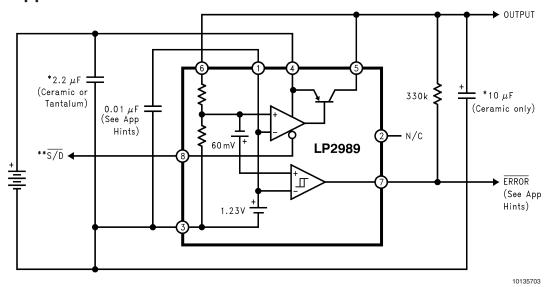

# **Block Diagram**

VIP™ is a trademark of National Semiconductor Corporation

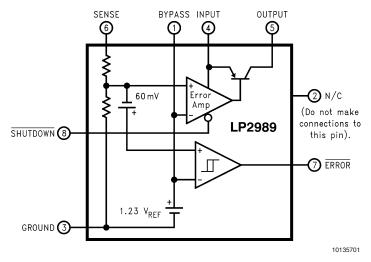

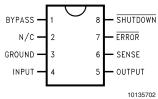

# **Connection Diagrams**

#### **Surface Mount Packages:**

SO-8/Mini SO-8 Package See NS Package Drawing Numbers M08A/MUA08A

#### 8 Lead LLP Surface Mount Package

Top View

See NS Package Number LDC08A

# **Ordering Information**

**TABLE 1. Package Marking and Ordering Information**

| Output Voltage   | e Grade Order Information Package Marking |                 | Supplied as: |                                 |  |  |

|------------------|-------------------------------------------|-----------------|--------------|---------------------------------|--|--|

| 8 Lead LLP       |                                           |                 |              | •                               |  |  |

| 1.8              | А                                         | LP2989AILD-1.8  | L01EA        | 1000 Units on Tape and Reel     |  |  |

| 1.8              | Α                                         | LP2989AILDX-1.8 | L01EA        | 4500 Units on Tape and Reel     |  |  |

| 1.8              | STD                                       | LP2989ILD-1.8   | L01EAB       | 1000 Units on Tape and Reel     |  |  |

| 1.8              | STD                                       | LP2989ILDX-1.8  | L01EAB       | 4500 Units on Tape and Reel     |  |  |

| SO-8 (M)         |                                           |                 |              |                                 |  |  |

| 1.8              | Α                                         | LP2989AIMX-1.8  | 2989AIM1.8   | 2500 Units on Tape and Reel     |  |  |

| 1.8              | A                                         | LP2989AIM-1.8   | 2989AIM1.8   | Shipped in Anti-Static<br>Rails |  |  |

| 1.8              | STD                                       | LP2989IMX-1.8   | 2989IM1.8    | 2500 Units on Tape and Reel     |  |  |

| 1.8              | STD                                       | LP298IM-1.8     | 2989IM1.8    | Shipped in Anti-Static<br>Rails |  |  |

| 8 Lead MSOP (MM) |                                           |                 |              |                                 |  |  |

| 1.8              | А                                         | LP2989AIMMX-1.8 | LA5A         | 3500 Units on Tape and Reel     |  |  |

| 1.8              | А                                         | LP2989AIMM-1.8  | LA5A         | 1000 Units on Tape and Reel     |  |  |

| 1.8              | STD                                       | LP2989IMMX-1.8  | LA5B         | 3500 Units on Tape and Reel     |  |  |

| 1.8              | STD                                       | LP2989IMM-1.8   | LA5B         | 1000 Units on Tape and Reel     |  |  |

For output voltages ≥ 2V, see LP2989 datasheet.

# **Basic Application Circuit**

\*Capacitance values shown are minimum required to assure stability, but may be increased without limit. Larger output capacitor provides improved dynamic response.

\*\*Shutdown must be actively terminated (see App. Hints). Tie to INPUT (Pin4) if not used.

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-65°C to +150°C Storage Temperature Range

Operating Junction Temperature

Range -40°C to +125°C

Lead Temperature (Soldering, 5

seconds)

260°C ESD Rating (Note 2) 2 kV

Power Dissipation (Note 3) Internally Limited Input Supply Voltage (Survival) -0.3V to +16V

Input Supply Voltage

2.1V to +16V (Operating) Sense Pin -0.3V to +6V

Output Voltage (Survival)

(Note 4) -0.3V to +16V

**Short Circuit** I<sub>OUT</sub> (Survival)

Protected

Input-Output Voltage (Survival)

-0.3V to +16V(Note 5)

#### **Electrical Characteristics**

Limits in standard typeface are for  $T_J = 25$ °C, and limits in **boldface type** apply over the full operating temperature range. Unless otherwise specified:  $V_{IN}$  =  $V_{O}(NOM)$  + 1V,  $I_{L}$  = 1 mA,  $C_{OUT}$  = 10  $\mu F$ ,  $C_{IN}$  = 2.2  $\mu F$ ,  $V_{S/D}$  = 2V.

|                                       | Parameter                                  | Conditions                                                            | Typical | <b>LP2989AI-X.X</b> (Note 6) |       | <b>LP2989I-X.X</b> (Note 6) |       | Units             |

|---------------------------------------|--------------------------------------------|-----------------------------------------------------------------------|---------|------------------------------|-------|-----------------------------|-------|-------------------|

| Symbol                                |                                            |                                                                       |         |                              |       |                             |       |                   |

|                                       |                                            |                                                                       |         | Min                          | Max   | Min                         | Max   | 1                 |

| V <sub>O</sub>                        | Output Voltage                             |                                                                       |         | -0.75                        | 0.75  | -1.25                       | 1.25  |                   |

|                                       | Tolerance                                  | 1 mA < I <sub>L</sub> < 500 mA                                        |         | -1.5                         | 1.5   | -2.5                        | 2.5   | 1                 |

|                                       |                                            | $V_O(NOM) + 1V \le V_{IN} \le 16V$                                    |         | -4.0                         | 2.5   | -5.0                        | 3.5   | -                 |

|                                       |                                            | 1 mA < I <sub>L</sub> < 500 mA                                        |         | -3.5                         | 2.5   | -4.5                        | 3.5   | %V <sub>NOM</sub> |

|                                       |                                            | $V_O(NOM) + 1V \le V_{IN} \le 16V$                                    |         |                              |       |                             |       |                   |

|                                       |                                            | $-25^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$ |         |                              |       |                             |       |                   |

| $\Delta V_0$                          | Output Voltage Line                        | $V_O(NOM) + 1V \le V_{IN} \le 16V$                                    |         |                              | 0.014 |                             | 0.014 |                   |

| $\frac{0}{\Delta V_{IN}}$             | Regulation                                 |                                                                       | 0.005   |                              | 0.032 |                             | 0.032 | %/V               |

| $\Delta V_0$                          | Load Regulation                            | 1 mA < I <sub>L</sub> < 500 mA                                        | 0.4     |                              |       |                             |       | %V <sub>NOM</sub> |

| $\frac{\Delta}{\Delta}$               |                                            |                                                                       |         |                              |       |                             |       |                   |

|                                       |                                            | V <sub>OUT</sub> = 1.8                                                | 1.96    |                              |       |                             |       |                   |

|                                       | N                                          | I <sub>L</sub> ≤ 50 mA                                                |         |                              |       |                             |       |                   |

| \/ (min)                              | Minimum Input Voltage Required To Maintain | V <sub>OUT</sub> = 1.8                                                | 1.98    |                              |       |                             |       | V                 |

|                                       | Output Regulation                          | I <sub>L</sub> = 250 mA                                               |         |                              |       |                             |       |                   |

|                                       | Output Hegulation                          | V <sub>OUT</sub> = 1.8                                                | 2.11    |                              |       |                             |       |                   |

|                                       |                                            | I <sub>L</sub> = 500 mA                                               |         |                              |       |                             |       |                   |

| $I_{GND}$                             | Ground Pin Current                         | I <sub>L</sub> = 100 μA                                               | 110     |                              | 175   |                             | 175   | μA                |

|                                       |                                            |                                                                       |         |                              | 200   |                             | 200   |                   |

|                                       |                                            | I <sub>L</sub> = 200 mA                                               |         |                              | 2     |                             | 2     | - mA              |

|                                       |                                            |                                                                       | '       |                              | 3.5   |                             | 3.5   |                   |

|                                       |                                            | I <sub>L</sub> = 500 mA                                               | 3 -     |                              | 6     |                             | 6     |                   |

|                                       |                                            |                                                                       |         |                              | 9     |                             | 9     |                   |

|                                       |                                            | V <sub>S/D</sub> < 0.18V                                              | 0.5     |                              | 2     |                             | 2     |                   |

|                                       |                                            | V <sub>S/D</sub> < 0.4V                                               | 0.05    |                              | 0.8   |                             | 0.8   | μΑ                |

| I <sub>O</sub> (PK)                   | Peak Output Current                        | $V_{OUT} \ge V_{O}(NOM) - 5\%$                                        | 800     | 600                          |       | 600                         |       | mA                |

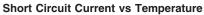

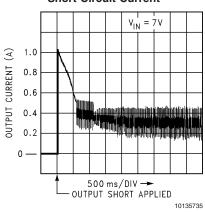

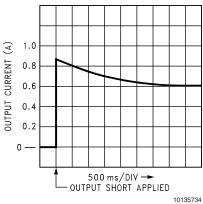

| I <sub>O</sub> (MAX)                  | Short Circuit Current                      | R <sub>L</sub> = 0 (Steady State) (Note 8)                            | 1000    |                              |       |                             |       |                   |

| e <sub>n</sub>                        | Output Noise Voltage                       | BW = 100 Hz to 100 kHz,                                               | 18      |                              |       |                             |       | μV(RMS)           |

|                                       | (RMS)                                      | C <sub>BYPASS</sub> = .01 μF                                          |         |                              |       |                             |       |                   |

| $\Delta V_{OUT}$                      | Ripple Rejection                           | f = 1 kHz                                                             | 60      |                              |       |                             |       | dB                |

| $\frac{\Delta V_{IN}}{\Delta V_{IN}}$ |                                            |                                                                       |         |                              |       |                             |       |                   |

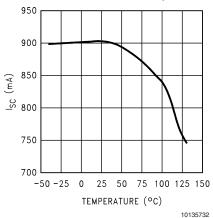

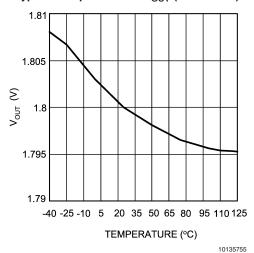

| ΔV <sub>OUT</sub>                     | Output Voltage                             | (Note 7)                                                              | 20      |                              |       |                             |       | ppm/°C            |

| $\frac{-7001}{\Delta T}$              | Temperature Coefficient                    |                                                                       |         |                              |       |                             |       |                   |

#### **Electrical Characteristics** (Continued)

Limits in standard typeface are for  $T_J = 25^{\circ}C$ , and limits in **boldface type** apply over the full operating temperature range. Unless otherwise specified:  $V_{IN} = V_O(NOM) + 1V$ ,  $I_L = 1$  mA,  $C_{OUT} = 10$  µF,  $C_{IN} = 2.2$  µF,  $V_{S/D} = 2V$ .

| Symbol           | Parameter             | Conditions                                                 | Typical | <b>LP2989AI-X.X</b> (Note 6) |      | LP2989I-X.X<br>(Note 6) |      | Units             |

|------------------|-----------------------|------------------------------------------------------------|---------|------------------------------|------|-------------------------|------|-------------------|

|                  |                       |                                                            |         | Min                          | Max  | Min                     | Max  |                   |

| SHUTDOW          | N INPUT               |                                                            | •       |                              | •    |                         |      |                   |

| V <sub>S/D</sub> | S/D Input Voltage     | V <sub>H</sub> = O/P ON                                    | 1.4     | 1.6                          |      | 1.6                     |      | V                 |

|                  |                       | $V_L = O/P OFF$<br>$I_{IN} \le 2 \mu A$                    | 0.50    |                              | 0.18 |                         | 0.18 |                   |

| I <sub>S/D</sub> | S/D Input Current     | V <sub>S/D</sub> = 0                                       | 0.001   |                              | -1   |                         | -1   |                   |

|                  |                       | $V_{S/D} = 5V$                                             | 5       |                              | 15   |                         | 15   | μΑ                |

| ERROR CO         | DMPARATOR             |                                                            |         |                              |      | •                       |      |                   |

| I <sub>OH</sub>  | Output "HIGH" Leakage | V <sub>OH</sub> = 16V                                      | 0.001   |                              | 1    |                         | 1    | μА                |

|                  |                       |                                                            |         |                              | 2    |                         | 2    |                   |

| V <sub>OL</sub>  | Output "LOW" Voltage  | $V_{OUT} = V_{O}(NOM) - 0.5V$<br>$I_{O}(COMP) = 150 \mu A$ | 150     |                              | 220  |                         | 220  | - mV              |

|                  |                       |                                                            |         |                              | 350  |                         | 350  |                   |

| V <sub>THR</sub> | Upper Threshold       | -4.8                                                       | -6.0    | -3.5                         | -6.0 | -3.5                    |      |                   |

| (MAX)            | Voltage               |                                                            | -4.8    | -8.3                         | -2.5 | -8.3                    | -2.5 |                   |

| V <sub>THR</sub> | Lower Threshold       |                                                            | 6.6     | -8.9                         | -4.9 | -8.9                    | -4.9 | %V <sub>OUT</sub> |

| (MIN)            | Voltage               |                                                            | -6.6    | -13.0                        | -3.0 | -13.0                   | -3.0 |                   |

| HYST             | Hysteresis            |                                                            | 2.0     |                              |      |                         |      |                   |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

Note 2: ESD testing was performed using Human Body Model, a 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor.

Note 3: The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$ (MAX), the junction-to-ambient thermal resistance,  $\theta_{J-A}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:

$$P(MAX) = \frac{T_{J}(MAX) - T_{A}}{\theta_{J-A}}$$

The value of  $\theta_{J-A}$  for the SO-8 (M) package is 160°C/W and the mini SO-8 (MM) package is 200°C/W. The value  $\theta_{J-A}$  for the LLP (LD) package is specifically dependent on PCB trace area, trace material, and the number of layers and thermal vias. For improved thermal resistance and power dissipation for the LLP package, refer to Application Note AN-1187. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown.

Note 4: If used in a dual-supply system where the regulator load is returned to a negative supply, the LP2989LV output must be diode-clamped to ground.

Note 5: The output PNP structure contains a diode between the V<sub>IN</sub> and V<sub>OUT</sub> terminals that is normally reverse-biased. Forcing the output above the input will turn on this diode and may induce a latch-up mode which can damage the part (see Application Hints).

**Note 6:** Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate National's Average Outgoing Quality Level (AOQL).

Note 7: Temperature coefficient is defined as the maximum (worst-case) change divided by the total temperature range.

Note 8: See Typical Performance Characteristics curves.

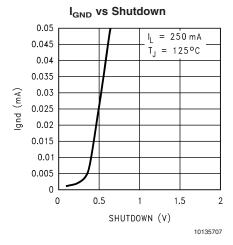

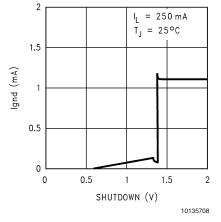

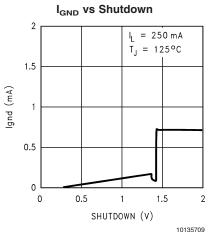

#

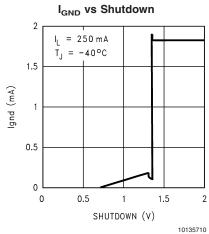

$I_{\rm GND}$  vs Shutdown

# $\begin{tabular}{ll} \textbf{Typical Performance Characteristics} & \textbf{Unless otherwise specified: $T_A=25^\circ$C, $C_{OUT}=10$ $\mu$F, $C_{IN}=2.2 $\mu$F, $S/D$ is tied to $V_{IN}$, $V_{IN}=V_O(NOM)+1V$, $I_L=1$ mA, $V_{OUT}=1.8V$. (Continued) $I_A=1.8V$. ($

#### **Short Circuit Current**

# Typical Temperature vs $V_{OUT}$ (LP2989-1.8)

#### **Short Circuit Current**

#### Minimum V<sub>IN</sub> vs Load Current

# **Application Hints**

#### **LLP Package Devices**

The LP2989LV is offered in the 8 lead LLP surface mount package to allow for increased power dissipation compared to the SO-8 and Mini SO-8. For details on thermal performance as well as mounting and soldering specifications, refer to Application Note AN-1187.

For output voltages ≥ 2V, see LP2989 datasheet.

#### **EXTERNAL CAPACITORS**

Like any low-dropout regulator, the LP2989LV requires external capacitors for regulator stability. These capacitors must be correctly selected for good performance.

**INPUT CAPACITOR:** An input capacitor whose capacitance is at least 2.2 µF is required between the LP2989LV input and ground (the amount of capacitance may be increased without limit).

Characterization testing performed on the LP2989LV has shown that if the amount of actual input capacitance drops below about 1.5  $\mu\text{F}$ , an unstable operating condition may result. Therefore, the next larger standard size (2.2  $\mu\text{F}$ ) is specified as the minimum required input capacitance. Capacitor tolerance and temperature variation must be considered when selecting a capacitor (see **Capacitor Characteristics** section) to assure the minimum requirement of 1.5  $\mu\text{F}$  is met over all operating conditions.

The input capacitor must be located at a distance of not more than 0.5" from the input pin and returned to a clean analog ground. Any good quality ceramic or tantalum may be used for this capacitor, assuming the minimum capacitance requirement is met.

**OUTPUT CAPACITOR:** The LP2989LV requires a ceramic output capacitor whose size is at least 10  $\mu$ F. The actual amount of capacitance on the output must never drop below about 7  $\mu$ F or unstable operation may result. For this reason, capacitance tolerance and temperature characteristics must be considered when selecting an output capacitor

The LP2989LV is designed specifically to work with ceramic output capacitors, utilizing circuitry which allows the regulator to be stable across the entire range of output current with an output capacitor whose ESR is as low as 4 m $\Omega$ . It may also be possible to use Tantalum or film capacitors at the output, but these are not as attractive for reasons of size and cost (see next section Capacitor Characteristics).

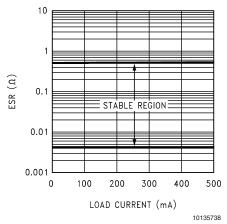

The output capacitor must meet the requirement for minimum amount of capacitance and also have an ESR (equivalent series resistance) value which is within the stable range. Curves are provided which show the stable ESR range as a function of load current (see ESR graph below).

Stable Region For Output Capacitor ESR

**Important:** The output capacitor must maintain its ESR within the stable region *over the full operating temperature range of the application* to assure stability.

It is important to remember that capacitor tolerance and variation with temperature must be taken into consideration when selecting an output capacitor so that the minimum required amount of output capacitance is provided over the full operating temperature range. (See Capacitor Characteristics section).

The output capacitor must be located not more than 0.5" from the output pin and returned to a clean analog ground.

NOISE BYPASS CAPACITOR: Connecting a 10 nF capacitor to the Bypass pin significantly reduces noise on the regulator output. However, the capacitor is connected directly to a high-impedance circuit in the bandgap reference.

Because this circuit has only a few microamperes flowing in it, any significant loading on this node will cause a change in the regulated output voltage. For this reason, DC leakage current through the noise bypass capacitor must never exceed 100 nA, and should be kept as low as possible for best output voltage accuracy.

The types of capacitors best suited for the noise bypass capacitor are ceramic and film. High-quality ceramic capacitors with either NPO or COG dielectric typically have very low leakage. 10 nF polypropolene and polycarbonate film capacitors are available in small surface-mount packages and typically have extremely low leakage current.

#### CAPACITOR CHARACTERISTICS

**CERAMIC:** The LP2989LV was designed to work with ceramic capacitors on the output to take advantage of the benefits they offer: for capacitance values in the 10  $\mu$ F range, ceramics are the least expensive and also have the lowest ESR values (which makes them best for eliminating high-frequency noise). The ESR of a typical 10  $\mu$ F ceramic capacitor is in the range of 5 m $\Omega$  to 10 m $\Omega$ , which meets the ESR limits required for stability by the LP2989LV.

One disadvantage of ceramic capacitors is that their capacitance can vary with temperature. Many large value ceramic capacitors ( $\geq$  2.2  $\mu F$ ) are manufactured with the Z5U or Y5V temperature characteristic, which results in the capacitance dropping by more than 50% as the temperature goes from 25°C to 85°C.

## Application Hints (Continued)

This could cause problems if a 10  $\mu$ F Y5V capacitor were used on the output since it will drop down to approximately 5  $\mu$ F at high ambient temperatures (which could cause the LP2989LV to oscillate).

Another significant problem with Z5U and Y5V dielectric devices is that the capacitance drops severely with applied voltage. A typical Z5U or Y5V capacitor can lose 60% of its rated capacitance with half of the rated voltage applied to it.

For these reasons, X7R and X5R type ceramic capacitors must be used on the input and output of the LP2989LV.

TANTALUM: Tantalum output capacitors are not recommended for use with the LP2989LV because:

Tantalum capacitors are less desirable than ceramics for use as output capacitors because they are typically more expensive when comparing equivalent capacitance and voltage ratings in the 1  $\mu F$  to 10  $\mu F$  range.

Another important consideration is that Tantalum capacitors have higher ESR values than equivalent size ceramics. This means that while it may be possible to find a Tantalum capacitor with an ESR value within the stable range, it would have to be larger in capacitance (which means bigger and more costly) than a ceramic capacitor with the same ESR value.

Most 10  $\mu F$  Tantalum capacitors have ESR values higher than the 0.5 $\Omega$  maximum limit required to make the LP2989LV stable.

It should also be noted that the ESR of a typical Tantalum will increase about 2:1 as the temperature goes from 25°C down to -40°C, so some guard band must be allowed.

**FILM:** Polycarbonate and polypropelene film capacitors have excellent electrical performance: their ESR is the lowest of the three types listed, their capacitance is very stable with temperature, and DC leakage currrent is extremely low.

One disadvantage is that film capacitors are larger in physical size than ceramic or tantalum which makes film a poor choice for either input or output capacitors.

However, their low leakage makes them a good choice for the noise bypass capacitor. Since the required amount of capacitance is only .01  $\mu$ F, small surface-mount film capacitors are available in this size.

#### SHUTDOWN INPUT OPERATION

The LP2989LV is shut off by driving the Shutdown input low, and turned on by pulling it high. If this feature is not to be used, the Shutdown input should be tied to  $V_{\text{IN}}$  to keep the regulator output on at all times.

To assure proper operation, the signal source used to drive the Shutdown input must be able to swing above and below the specified turn-on/turn-off voltage thresholds listed in the Electrical Characteristics section under  $V_{\rm ON/OFF}$ .

#### **REVERSE INPUT-OUTPUT VOLTAGE**

The PNP power transistor used as the pass element in the LP2989LV has an inherent diode connected between the regulator output and input.

During normal operation (where the input voltage is higher than the output) this diode is reverse-biased.

However, if the output is pulled above the input, this diode will turn ON and current will flow into the regulator output.

In such cases, a parasitic SCR can latch which will allow a high current to flow into  $V_{\rm IN}$  (and out the ground pin), which can damage the part.

In any application where the output may be pulled above the input, an external Schottky diode must be connected from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  (cathode on  $V_{\text{IN}}$ , anode on  $V_{\text{OUT}}$ ), to limit the reverse voltage across the LP2989LV to 0.3V (see Absolute Maximum Ratings).

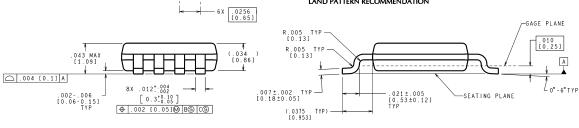

# **Physical Dimensions** inches (millimeters) unless otherwise noted 6±0.2 [.236±.008] 6X (1.27) RECOMMENDED LAND PATTERN LPIN 1 ID 1.35-1.75 [.053-.069] TYP 6X [1.27 [.050] R0.18±0.02 [.007±.0008] 45° X 0.25-0.50 [.010-.020] R0.23±0.02 0.25 [.010] GAGE PLAN 0.1[.004] C C -SEATING PLANE CONTROLLING DIMENSION IS MILLIMETER VALUES IN [ ] ARE INCHES DIMENSIONS IN ( ) FOR REFERENCE ONLY M08A (Rev K) SO-8 Package Type M **NS Package Number M08A** (.189) .193±.006 [4.9±0.15] .118±.004 PIN 1 IDENT LAND PATTERN RECOMMENDATION 6X [.0256 [0.65] -GAGE PLANE R.005 TYP [0.13] R.005 TYF

mini SO-8 Package Type MM NS Package Number MUA08A

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

MUA08A (Rev E)

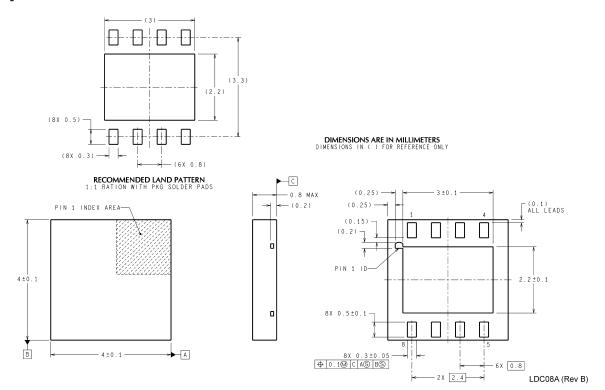

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

8 Lead LLP Surface Mount PackagePackage **NS Package Number LDC08A**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560