# LMV7219EP 7 nsec, 2.7V to 5V Comparator with Rail-to-Rail Output

# **General Description**

The LMV7219M5EP is a low-power, high-speed comparator with internal hysteresis. The LMV7219M5EP operating voltage ranges from 2.7V to 5V with push/pull rail-to-rail output. This device achieves a 7ns propagation delay while consuming only 1.1mA of supply current at 5V.

The LMV7219M5EP inputs have a common mode voltage range that extends 200mV below ground, allowing ground sensing. The internal hysteresis ensures clean output transitions even with slow-moving inputs signals.

The LMV7219M5EP is available in the SC70-5 and SOT23-5 packages, which are ideal for systems where small size and low power are critical.

#### ENHANCED PLASTIC

- Extended Temperature Performance of -40°C to +85°C

- Baseline Control Single Fab & Assembly Site

- Process Change Notification (PCN)

- Qualification & Reliability Data

- Solder (PbSn) Lead Finish is standard

- Enhanced Diminishing Manufacturing Sources (DMS) Support

### **Features**

$(V_{S} = 5V, T_{A} = 25^{\circ}C, Typical values unless specified)$

- Propagation delay

- Low supply current

- Input common mode voltage range extends 200mv below ground

- Ideal for 2.7V and 5V single supply applications

- Internal hysteresis ensures clean switching

- Fast rise and fall time

- Available in space-saving packages: 5-pin SC70-5 and SOT23-5

### **Applications**

- High speed differential line receiver

- Zero-crossing detectors

- High-speed sampling circuits

- Selected Military Applications

- Selected Avionics Applications

## **Ordering Information**

| PART NUMBER VID PART NUMBER NS PACKAGE NUMBER ( |              | NS PACKAGE NUMBER (Note 3) |

|-------------------------------------------------|--------------|----------------------------|

| LMV7219M5EP                                     | V62/04750-01 | MF05A                      |

| (Notes 1, 2)                                    | TBD          | TBD                        |

Note 1: For the following (Enhanced Plastic) version, check for availability: LMV7219M5XEP, LMV7219M7EP, LMV2917M7XEP. Parts listed with an "X" are provided in Tape & Reel and parts without an "X" are in Rails.

Note 2: FOR ADDITIONAL ORDERING AND PRODUCT INFORMATION, PLEASE VISIT THE ENHANCED PLASTIC WEB SITE AT: www.national.com/ mil

Note 3: Refer to package details under Physical Dimensions

7ns

1.1mA

1.3ns

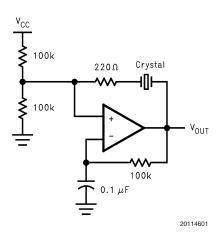

# **Typical Application**

LMV7219EP

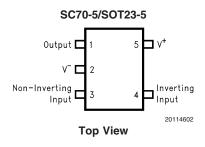

# **Connection Diagram**

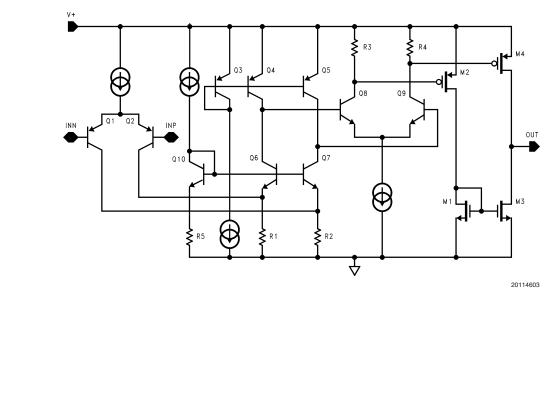

# **Simplified Schematic**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| ESD Tolerance (Note 5)                            |                   |

|---------------------------------------------------|-------------------|

| Machine Body                                      | 150V              |

| Human Model Body                                  | 2000V             |

| Differential Input Voltage                        | ± Supply Voltage  |

| Output Short Circuit Duration                     | (Note 6)          |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) | 5.5V              |

| Soldering Information                             |                   |

| Infrared or Convection (20                        | 235°C             |

| sec)                                              |                   |

| Wave Soldering (10 sec)                           | 260°C (lead temp) |

# Voltage at Input/Output pins Current at Input Pin (Note 12)

$(V^{+}) + 0.4V$

(V<sup>-</sup>) - 0.4V

±10mA

**Operating Ratings**

| Supply voltages (V <sup>+</sup> - V <sup>-</sup> ) | 2.7V to 5V      |

|----------------------------------------------------|-----------------|

| Operating temperature                              | -40°C to +85°C  |

| range (Note 7)                                     |                 |

| Storage Temperature Range                          | –65°C to +150°C |

| Package Thermal Resistance                         |                 |

| SC70-5                                             | 478°C/W         |

| SOT23-5                                            | 265°C/W         |

|                                                    |                 |

# **2.7V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = V^+/2$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $C_L = 10pF$  and  $R_L > 1M\Omega$  to  $V^-$ . **Boldface** limits apply at the temperature extremes. (Note 14)

| Symbol                         | Parameter                          | Conditions                     | Typ<br>(Note 8)       | Limit<br>(Note 9)     | Units |

|--------------------------------|------------------------------------|--------------------------------|-----------------------|-----------------------|-------|

| Vos                            | Input Offset Voltage               |                                | 1                     | 6                     | mV    |

|                                |                                    |                                |                       | 8                     | max   |

| I <sub>B</sub>                 | Input Bias Current                 |                                | 450                   | 950                   | nA    |

|                                |                                    |                                |                       | 2000                  | max   |

| l <sub>os</sub>                | Input Offset Current               |                                | 50                    | 200                   | nA    |

|                                |                                    |                                |                       | 400                   | max   |

| CMRR                           | Common Mode Rejection Ratio        | $0V < V_{CM} < 1.50V$          | 85                    | 62                    | dB    |

|                                |                                    |                                |                       | 55                    | min   |

| PSRR                           | Power Supply Rejection Ratio       | V <sup>+</sup> = 2.7V to 5V    | 85                    | 65                    | dB    |

|                                |                                    |                                |                       | 55                    | min   |

| V <sub>CM</sub>                | Input Common-Voltage Range         | CMRR > 50dB                    | V <sub>CC</sub> –1    | V <sub>CC</sub> -1.2  | V     |

|                                |                                    |                                |                       | V <sub>cc</sub> –1.3  | min   |

|                                |                                    |                                | -0.2                  | -0.1                  | V     |

|                                |                                    |                                |                       | 0                     | max   |

| Vo                             | Output Swing High                  | $I_L = 4mA$ ,                  | V <sub>CC</sub> -0.22 | V <sub>CC</sub> -0.3  |       |

|                                |                                    | $V_{ID} = 500 mV$              |                       | V <sub>cc</sub> –0.4  | V     |

|                                |                                    | $I_{L} = 0.4 mA,$              | V <sub>CC</sub> -0.02 | V <sub>CC</sub> -0.05 | min   |

|                                |                                    | $V_{ID} = 500 mV$              |                       | V <sub>cc</sub> –0.15 |       |

|                                | Output Swing Low                   | $I_L = -4mA$ ,                 | 130                   | 200                   |       |

|                                |                                    | $V_{ID} = -500 \text{mV}$      |                       | 300                   | mV    |

|                                |                                    | $I_{L} = -0.4 mA,$             | 15                    | 50                    | max   |

|                                |                                    | $V_{ID} = -500 \text{mV}$      |                       | 150                   |       |

| I <sub>sc</sub>                | Output Short Circuit Current       | Sourcing,                      | 20                    |                       |       |

|                                |                                    | $V_{O} = 0V$ (Note 6)          |                       |                       | mA    |

|                                |                                    | Sinking,                       | 20                    |                       | mA    |

|                                |                                    | V <sub>O</sub> = 2.7V (Note 6) |                       |                       |       |

| I <sub>S</sub>                 | Supply Current                     | No load                        | 0.9                   | 1.6                   | mA    |

|                                |                                    |                                |                       | 2.2                   | max   |

| V <sub>HYST</sub>              | Input Hysteresis Voltage           | (Note 13)                      | 7                     |                       | mV    |

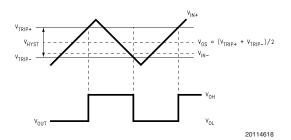

| V <sub>TRIP</sub> <sup>+</sup> | Input Referred Positive Trip Point | (see Figure 1)                 | 3                     | 8                     | mV    |

|                                |                                    |                                |                       |                       | max   |

| V <sub>TRIP</sub> -            | Input Referred Negative Trip Point | (see Figure 1)                 | -4                    | -8                    | mV    |

|                                |                                    |                                |                       |                       | min   |

### 2.7V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = V^+/2$ ,  $V^+ = 2.7V$ ,  $V^- = 0V$ ,  $C_L = 10pF$  and  $R_L > 1M\Omega$  to  $V^-$ . **Boldface** limits apply at the temperature extremes. (Note 14)

| Symbol            | Parameter              | Conditions              | Typ<br>(Note 8) | Limit<br>(Note 9) | Units |

|-------------------|------------------------|-------------------------|-----------------|-------------------|-------|

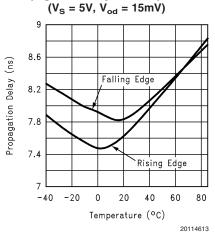

| t <sub>PD</sub>   | Propagation Delay      | Overdrive = 5mV         | 12              |                   |       |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   |       |

|                   | Overdrive = 15mV       | 11                      |                 | ns                |       |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   | max   |

|                   |                        | Overdrive = 50mV        | 10              | 20                |       |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   |       |

| t <sub>skew</sub> | Propagation Delay Skew | (Note 11)               | 1               |                   | ns    |

| t <sub>r</sub>    | Output Rise Time       | 10% to 90%              | 2.5             |                   | ns    |

| t <sub>f</sub>    | Output Fall Time       | 90% to 10%              | 2               |                   | ns    |

## **5V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = V^+/2$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $C_L = 10pF$  and  $R_L > 1M\Omega$  to  $V^-$ . **Boldface** limits apply at the temperature extremes. (Note 14)

| Symbol              | Parameter                          | Conditions                | Typ<br>(Note 8)       | Limit<br>(Note 9)     | Units |

|---------------------|------------------------------------|---------------------------|-----------------------|-----------------------|-------|

| V <sub>os</sub>     | Input Offset Voltage               |                           | 1                     | 6                     | mV    |

| 00                  |                                    |                           |                       | 8                     | max   |

| I <sub>B</sub>      | Input Bias Current                 |                           | 500                   | 950                   | nA    |

|                     |                                    |                           |                       | 2000                  | max   |

| l <sub>os</sub>     | Input Offset Current               |                           | 50                    | 200                   | nA    |

|                     |                                    |                           |                       | 400                   | max   |

| CMRR                | Common Mode Rejection Ratio        | $0V < V_{CM} < 3.8V$      | 85                    | 65                    | dB    |

|                     |                                    |                           |                       | 55                    | min   |

| PSRR                | Power Supply Rejection Ratio       | $V^+ = 2.7V$ to 5V        | 85                    | 65                    | dB    |

|                     |                                    |                           |                       | 55                    | min   |

| V <sub>CM</sub>     | Input Common-Mode Voltage Range    | CMRR > 50dB               | V <sub>CC</sub> -1    | V <sub>CC</sub> –1.2  | V     |

|                     |                                    |                           |                       | V <sub>CC</sub> –1.3  | min   |

|                     |                                    |                           | -0.2                  | -0.1                  | V     |

|                     |                                    |                           |                       | 0                     | max   |

| Vo                  | Output Swing High                  | $I_{L} = 4mA,$            | V <sub>CC</sub> -0.13 | V <sub>CC</sub> -0.2  |       |

|                     |                                    | V <sub>ID</sub> = 500mV   |                       | V <sub>CC</sub> –0.3  | V     |

|                     |                                    | $I_{L} = 0.4 mA,$         | V <sub>CC</sub> -0.02 | V <sub>CC</sub> -0.05 | min   |

|                     |                                    | V <sub>ID</sub> = 500mV   |                       | V <sub>CC</sub> –0.15 |       |

|                     | Output Swing Low                   | $I_{L} = -4mA,$           | 80                    | 180                   |       |

|                     |                                    | $V_{ID} = -500 \text{mV}$ |                       | 280                   | mV    |

|                     |                                    | $I_{L} = -0.4 mA,$        | 10                    | 50                    | max   |

|                     |                                    | $V_{ID} = -500 \text{mV}$ |                       | 150                   |       |

| I <sub>sc</sub>     | Output Short Circuit Current       | Sourcing, $V_{O} = 0V$    | 68                    | 30                    |       |

|                     |                                    | (Note 6)                  |                       | 20                    | mA    |

|                     |                                    | Sinking, $V_O = 5V$       | 65                    | 30                    | min   |

|                     |                                    | (Note 6)                  |                       | 20                    |       |

| ls                  | Supply Current                     | No load                   | 1.1                   | 1.8                   | mA    |

|                     |                                    |                           |                       | 2.4                   | max   |

| V <sub>HYST</sub>   | Input Hysteresis Voltage           | (Note 13)                 | 7.5                   |                       | mV    |

| $V_{Trip^+}$        | Input Referred Positive Trip Point | (See figure 1)            | 3.5                   | 8                     | mV    |

|                     |                                    |                           |                       |                       | max   |

| V <sub>Trip</sub> - | Input Referred Negative Trip Point | (See figure 1)            | -4                    | -8                    | mV    |

|                     |                                    |                           |                       |                       | min   |

## 5V Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V_{CM} = V^{+}/2$ ,  $V^{+} = 5V$ ,  $V^{-} = 0V$ ,  $C_L = 10pF$  and  $R_L > 1M\Omega$  to  $V^{-}$ . **Boldface** limits apply at the temperature extremes. (Note 14)

| Symbol            | Parameter              | Conditions              | Typ<br>(Note 8) | Limit<br>(Note 9) | Units |

|-------------------|------------------------|-------------------------|-----------------|-------------------|-------|

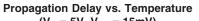

| t <sub>PD</sub>   | Propagation Delay      | Overdrive = 5mV         | 9               |                   |       |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   |       |

|                   |                        | Overdrive = 15mV        | 8               | 20                | ns    |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   | max   |

|                   |                        | Overdrive = 50mV        | 7               | 19                |       |

|                   |                        | $V_{CM} = 0V$ (Note 10) |                 |                   |       |

| t <sub>skew</sub> | Propagation Delay Skew | (Note 11)               | 0.4             |                   | ns    |

| t <sub>r</sub>    | Output Rise Time       | 10% to 90%              | 1.3             |                   | ns    |

| t <sub>f</sub>    | Output Fall Time       | 90% to 10%              | 1.25            |                   | ns    |

Note 4: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical characteristics.

Note 5: Human body model,  $1.5k\Omega$  in series with 100pF. Machine model,  $200\Omega$  in series with 100pF.

Note 6: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of ±30mA over long term may adversely affect reliability.

Note 7: The maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(max)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

Note 8: Typical Values represent the most likely parametric norm.

Note 9: All limits are guaranteed by testing or statistical analysis.

Note 10: Propagation delay measurements made with 100mV steps. Overdrive is measure relative to V<sub>Trip</sub>.

Note 11: Propagation Delay Skew is defined as absolute value of the difference between  $t_{\text{PDLH}}$  and  $t_{\text{PDHL}}$ .

Note 12: Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.

Note 13: The LMV7219M5EP comparator has internal hysteresis. The trip points are the input voltage needed to change the output state in each direction. The offset voltage is defined as the average of  $V_{trip}$ - and  $V_{trip}$ -, while the hysteresis voltage is the difference of these two.

Note 14: "Testing and other quality control techniques are used to the extent deemed necessary to ensure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific PARAMETRIC testing, product performance is assured by characterization and/or design."

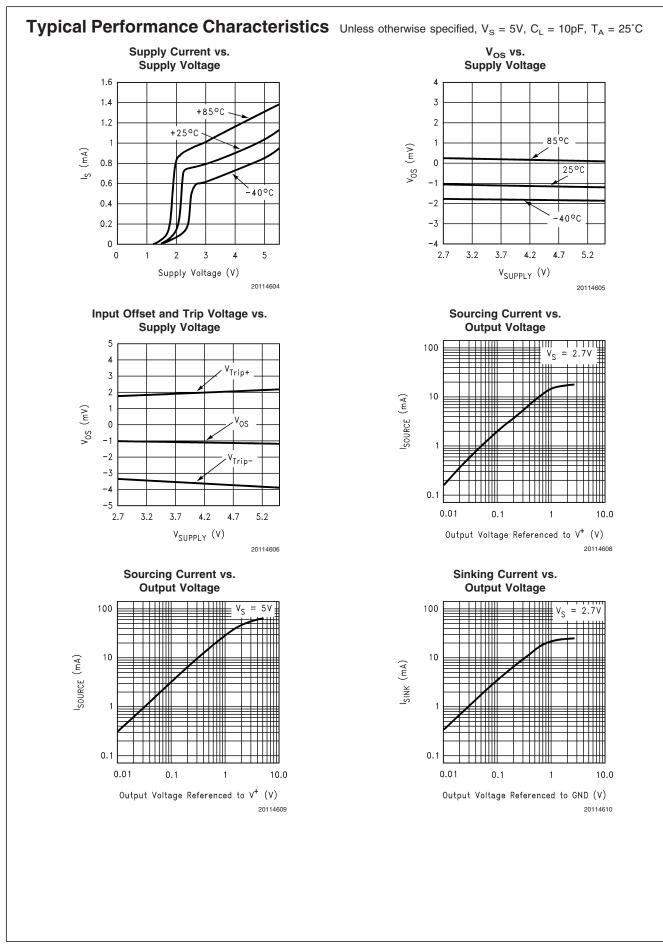

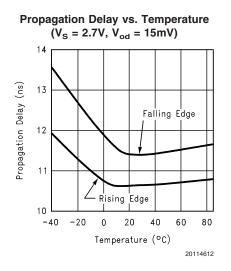

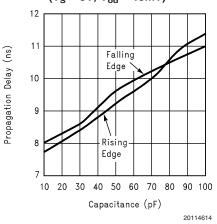

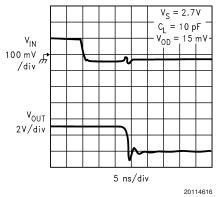

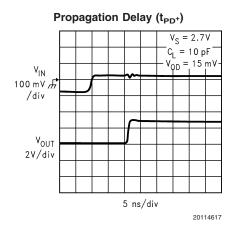

# **Typical Performance Characteristics** Unless otherwise specified, $V_s = 5V$ , $C_L = 10pF$ , $T_A = 25^{\circ}C$ (Continued)

#### Propagation Delay vs. Input Overdrive

Propagation Delay vs. Capacitive Load  $(V_S = 5V, V_{od} = 15mV)$

**Typical Performance Characteristics** Unless otherwise specified,  $V_S = 5V$ ,  $C_L = 10pF$ ,  $T_A = 25^{\circ}C$  (Continued)

# **Application Section**

LMV7219M5EP is a single supply comparator with internal hysteresis, 7ns of propagation delay and only 1.1mA of supply current.

The LMV7219M5EP has a typical input common mode voltage range of -0.2V below the ground to 1V below  $V_{\rm cc}$ . The differential input stage is a pair of PNP transistors, therefore, the input bias current flows out of the device. If either of the input signals falls below the negative common mode limit, the parasitic PN junction formed by the substrate and the base of the PNP will turn on, resulting in an increase of input bias current.

If one of the inputs goes above the positive common mode limit, the output will still maintain the correct logic level as long as the other input stays within the common mode range. However, the propagation delay will increase. When both inputs are outside the common mode voltage range, current saturation occurs in the input stage, and the output becomes unpredictable.

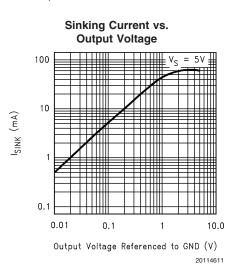

The propagation delay does not increase significantly with large differential input voltages. However, large differential voltages greater than the supply voltage should be avoided to prevent damages to the input stage. The LMV7219M5EP has a push pull output. When the output switches, there is a direct path between  $V_{\rm cc}$  and ground, causing high output sinking or sourcing current during the transition. After the transition, the output current decreases and the supply current settles back to about 1.1mA at 5V, thus conserving power consumption.

Most high-speed comparators oscillate when the voltage of one of the inputs is close to or equal to the voltage on the other input due to noise or undesirable feedback. The LMV7219M5EP have 7mV of internal hysteresis to counter parasitic effects and noise. The hysteresis does not change significantly with the supply voltages and the common mode input voltages as reflected in the specification table.

The internal hysteresis creates two trip points, one for the rising input voltage and one for the falling input voltage. The difference between the trip points is the hysteresis. With internal hysteresis, when the comparator's input voltages are equal, the hysteresis effectively causes one comparatorinput voltage to move quickly past the other, thus taking the input out of the region where oscillation occurs. Standard comparators require hysteresis to be added with external resistors. The fixed internal hysteresis eliminates these resistors.

FIGURE 1. Input and Output Waveforms, Non-Inverting Input Varied

# Application Section (Continued)

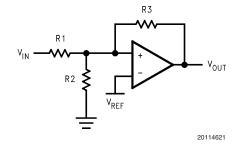

#### ADDITIONAL HYSTERESIS

If additional hysteresis is desired, this can be done with the addition of three resistors using positive feedback, as shown in *Figure 2*. The positive feedback method slows the comparator response time. Calculate the resistor values as follows:

1) Select R3. The current through R3 should be greater than the input bias current to minimize errors. The current through R3 ( $I_F$ ) at the trip point is ( $V_{REF} - V_{OUT}$ ) /R3. Consider the two possible output states when solving for R3, and use the smaller of the two resulting resistor values. The two formulas are:

$$R3 = V_{REF}/I_F \qquad (when V_{OUT} = 0)$$

$R3 = V_{CC} - V_{REF} / I_F \qquad (V_{OUT} = V_{CC})$

2) Choose a hysteresis band required (V<sub>HB</sub>).

3) Calculate R1, where R1 = R3  $X(V_{HB}/V_{CC})$

4) Choose the trip point for V<sub>IN</sub> rising. This is the threshold voltage (V<sub>THR</sub>) at which the comparator switches from low to high as V<sub>IN</sub> rises about the trip point.

5) Calculate R2 as follows:

$$R_2 = \frac{1}{\left(\frac{V_{\text{THR}}}{V_{\text{REF}} \times R_1}\right) - \frac{1}{R_1} - \frac{1}{R_3}}$$

6) Verify the trip voltage and hysteresis as follows:

$$V_{IN} \text{ rising: } V_{THR} = V_{REF} \times R_1 \times \left(\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right)$$

$$V_{IN} \text{ falling: } V_{THF} = V_{THR} - \left(\frac{R_1 \times V_{CC}}{R_3}\right)$$

Hysteresis = V<sub>THR</sub> - V<sub>THF</sub>

This method is recommended for additional hysteresis of up to a few hundred millivolts. Beyond that, the impedance of R3 is low enough to affect the bias string and adjustment of R1 may be also required.

FIGURE 2. Additional Hysteresis

#### CIRCUIT LAYOUT AND BYPASSING

The LMV7219M5EP requires high-speed layout. Follow these layout guidelines:

1. Power supply bypassing is critical, and will improve stability and transient response. A decoupling capacitor such as  $0.1 \mu F$  ceramic should be placed as close as possible to V<sup>+</sup> pin. An additional  $2.2 \mu F$  tantalum capacitor may be required for extra noise reduction.

2. Keep all leads short to reduce stray capacitance and lead inductance. It will also minimize unwanted parasitic feedback around the comparator.

3. The device should be soldered directly to the PC board instead of using a socket.

4. Use a PC board with a good, unbroken low inductance ground plane. Make sure ground paths are low-impedance, especially were heavier currents are flowing.

5. Input traces should be kept away from output traces. This can be achieved by running a topside ground plane between the output and inputs.

6. Run the ground trace under the device up to the bypass capacitor to shield the inputs from the outputs.

7. To prevent parasitic feedback when input signals are slow-moving, a small capacitor of 1000pF or less can be placed between the inputs. It can also help eliminate oscillations in the transition region. However, this capacitor can cause some degradation to tpd when the source impedance is low.

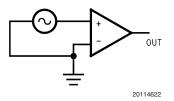

#### ZERO-CROSSING DETECTOR

The inverting input is connected to ground and the noninverting input is connected to 100mVp-p signal. As the signal at the non-inverting input crosses 0V, the comparator's output Changes State.

FIGURE 3. Zero-Crossing Detector

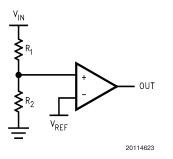

#### THRESHOLD DETECTOR

Instead of tying the inverting input to 0V, the inverting input can be tied to a reference voltage. The non-inverting input is connected to the input. As the input passes the  $V_{\mathsf{REF}}$  threshold, the comparator's output changes state.

**FIGURE 4. Threshold Detector**

# Application Section (Continued)

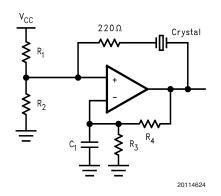

#### CRYSTAL OSCILLATOR

A simple crystal oscillator using the LMV7219M5EP is shown below. Resistors R1 and R2 set the bias point at the comparator's non-inverting input. Resistors R3, R4 and C1 sets the inverting input node at an appropriate DC average level based on the output. The crystal's path provides resonant positive feedback and stable oscillation occurs. The output duty cycle for this circuit is roughly 50%, but it is affected by resistor tolerances and to a lesser extent by the comparator offset.

FIGURE 5. Crystal Oscillator

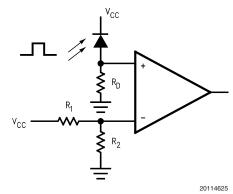

#### **IR RECEIVER**

The LMV7219M5EP is an ideal candidate to be used as an infrared receiver. The infrared photo diode creates a current relative to the amount of infrared light present. The current creates a voltage across RD. When this voltage level cross the voltage applied by the voltage divider to the inverting input, the output transitions.

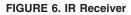

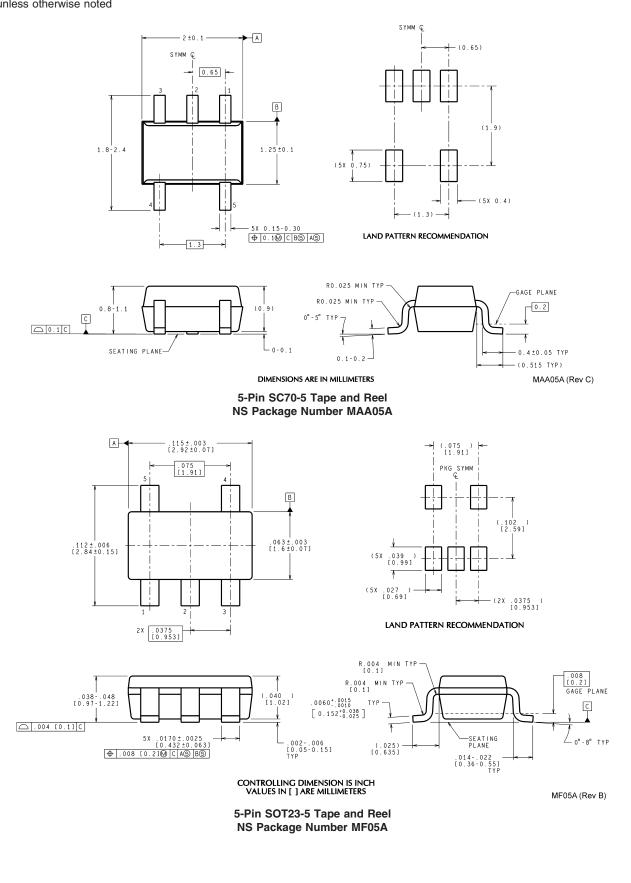

# Physical Dimensions inches (millimeters) unless otherwise noted

LMV7219EP

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +44 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

www.national.com