## **PRELIMINARY**

November 1995

# LMC2626 CMOS LDOR/Buffer Chip for Row Inversion Flat Panel Display Systems

## **General Description**

The LMC2626 integrated circuit is specifically developed for a row inversion TFT FPD system architecture. It is designed only to be used in conjunction with National's LM2625 switching regulator chip.

Built on National's advanced CMOS CS80 process, this chip generates a high-power, precision square-wave from a digital sync signal. The chip also contains thermal shutdown circuitry, system shutdown circuitry, and a low drop-out voltage regulator to generate a 4.2 volt supply from an externally applied reference voltage of 1.227V.

## **Features**

- Used in conjunction with LM2625 chip

- High output current buffer

- Low buffer on resistance

- System shutdown control

- LDO voltage regulator

- LDOR dropout 0.3V maximum at 150 mA

- Thermal shutdown/short circuit protection

- External reference required for LDOR

- V<sub>REF</sub> pin converts to a digital pin to shutdown LM2625

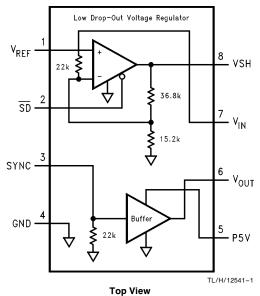

## **Connection Diagram**

#### 8-Pin SO

## **Pin Description**

| Pin # | Pin Name         | Description                                              |

|-------|------------------|----------------------------------------------------------|

| 1     | V <sub>REF</sub> | 1.218V to 1.242V Ext. Reference from LM2625 (see Note 8) |

| 2     | SD               | System Shutdown input pin for LMC2626 and LMC2625        |

| 3     | SYNC             | Digital input square wave from FPD controller            |

| 4     | GND              | Ground                                                   |

| 5     | P5V              | Precision Regulated +5V Supply                           |

| 6     | V <sub>OUT</sub> | Power Buffer Output                                      |

| 7     | V <sub>IN</sub>  | FPD System Supply (+4.5V to +5.5V)                       |

| 8     | V <sub>SH</sub>  | Low Drop-Out Voltage Regulator<br>Output                 |

# **Ordering Information**

| Package  | Temperature Range<br>-40°C to +85°C | NSC<br>Drawing | Transport<br>Media       |  |  |  |  |

|----------|-------------------------------------|----------------|--------------------------|--|--|--|--|

| 8-Pin SO | LMC2626IM                           | M08A           | Rail<br>Tape and<br>Reel |  |  |  |  |

# **Absolute Maximum Ratings** (Note 1)

ESD Tolerance 2 kV HBM, 200V MM (Note 4)

Sync Input Voltage P5V

Supply Voltage (V<sub>IN</sub>, P5V)

Continuous Total Power Dissipation (Note 1)

# Operating Ratings (Note 1)

$\begin{array}{lll} \text{V}_{\text{IN}} & \text{Supply Voltage} & 4.5 \text{V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{V} \\ \text{P5V Supply Voltage (Note 5)} & 4.8 \text{V} \leq \text{P5V} \leq 5.2 \text{V} \\ \text{Junction Temperature Range} & -25^{\circ}\text{C to} & +125^{\circ}\text{C} \\ \text{Ambient Temperature Range} & -40^{\circ}\text{C to} & +85^{\circ}\text{C} \\ \end{array}$

## **DC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $-20^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ , P5V = 5V and 4.5V  $\le \text{V}_{\text{IN}} \le 5.5\text{V}$ ,  $\text{V}_{\text{REF}} = 1.227\text{V}$  SYNC(OPEN),  $\overline{\text{SD}}(\text{OPEN}) < \text{P5V} = \text{V}_{\text{IN}} = 5\text{V}$

6.3V

VSH LDO Voltage Regulator (Notes 7, 10, 11)

| Symbol               | Parameter                                                   | Conditions                                                                                                                                | Min   | Typ<br>(Note 9) | Max   | Units |

|----------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|-------|

| V <sub>O(VREF)</sub> | V <sub>REF</sub> Voltage Level<br>in Shutdown               | $\overline{SD} = 0V$ $I_{VREF} = -1 \text{ mA}$ $V_{IN} = 5V$                                                                             | 4.00  | 4.76            |       | V     |

| I <sub>VREF</sub>    | DC Current from<br>V <sub>REF</sub> Pin                     |                                                                                                                                           | -40.0 | -13.3           | -5    | μΑ    |

| V <sub>SH</sub>      | Output Voltage on<br>V <sub>SH</sub> Pin (see Note 2)       | $\begin{array}{c} 4.5 V \leq V_{IN} \leq 5.5 V \\ 20 \text{ mA} \leq IL \leq 150 \text{ mA} \\ 1.218 \leq V_{REF} \leq 1.242 \end{array}$ | 4.10  | 4.20            | 4.30  | ٧     |

| $\Delta V_{SH}$      | Variation of V <sub>SH</sub> over<br>Temperature            | $\begin{array}{c} \text{4.5V} \leq \text{V}_{\text{IN}} \leq \text{5.5V} \\ \text{20 mA} \leq \text{IL} \leq \text{150 mA} \end{array}$   |       | 4               | 126   | mV    |

| $V_{DO}$             | LDOR Voltage Dropout<br>(V <sub>IN</sub> -V <sub>SH</sub> ) | IL = 150 mA                                                                                                                               |       | 0.17            | 0.30  | V     |

| I <sub>S(VIN)</sub>  | V <sub>IN</sub> Supply Current                              |                                                                                                                                           | 230   | 394             | 500   | μΑ    |

|                      | Load Regulation of LDO<br>Voltage Regulation                | $4.5V \le V_{IN} \le 5.5V$ $20 \text{ mA} \le IL \le 150 \text{ mA}$                                                                      |       | 0.002           | 0.015 | %/mA  |

|                      | Line Regulation of LDOR                                     | $4.5V \leq V_{IN} \leq 5.5V$ $20 \text{ mA} \leq IL \leq 150 \text{ mA}$                                                                  |       | 0.24            | 0.95  | %/V   |

| T <sub>SD</sub>      | Thermal Shutdown<br>Threshold                               | (see Note 8)                                                                                                                              |       | 160             |       | °C    |

| I <sub>OUT</sub>     | Output Load Current                                         | (see Note 2)                                                                                                                              |       |                 | 300   | mA    |

## Shutdown Control (Note 8)

| Symbol                  | Parameter                                       | Conditions                                                                                         | Min  | Typ<br>(Note 9) | Max  | Units |

|-------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-----------------|------|-------|

| $I_{IL(\overline{SD})}$ | Low Level Input Current for SD Pin              | $V_{IN} = 5V$ $\overline{SD} = 0V$                                                                 | -300 | -217            | -150 | μΑ    |

| I <sub>IH(SD)</sub>     | High Level Input Current for SD Pin             | <u>SD</u> = 5V                                                                                     |      | 310             | 1000 | nA    |

| I <sub>S(SD)</sub>      | V <sub>IN</sub> Supply Current in Shutdown Mode |                                                                                                    | 180  | 285             | 400  | μΑ    |

| C <sub>in(SYNC)</sub>   | Input Capacitance<br>at SYNC Pin (Note 6)       | $\begin{array}{c} \text{SYNC} = 5\text{V} \\ \text{T}_{\text{A}} = 27^{\circ}\text{C} \end{array}$ |      | 20              |      | pF    |

DC Electrical Characteristics Unless otherwise specified, all limits guaranteed for  $-20^{\circ}\text{C} \le T_{\text{A}} \le +85^{\circ}\text{C}$ , P5V = 5V and  $4.5\text{V} \le \text{V}_{\text{IN}} \le 5.5\text{V}$ ,  $\text{V}_{\text{REF}} = 1.227\text{V}$  SYNC(OPEN),  $\overline{\text{3D}}(\text{OPEN}) < \text{P5V} = \text{V}_{\text{IN}} = 5\text{V}$  (Continued)

## Buffer

| Symbol                                 | Parameter                                                          | Conditions                                       | Min   | Typ<br>(Note 9) | Max  | Units |

|----------------------------------------|--------------------------------------------------------------------|--------------------------------------------------|-------|-----------------|------|-------|

| V <sub>OUT</sub>                       | Peak to Peak Output<br>Voltage Swing or V <sub>OUT</sub>           | SYNC = 5V <sub>pp</sub> (no load)                | 4.997 | 4.999           |      | ٧     |

| V <sub>OL</sub>                        | Low Level Output<br>Voltage                                        | SYNC = 0V<br>(No Load)                           |       | 0.2             | 2    | mV    |

| V <sub>OH</sub>                        | High Level Output<br>Voltage                                       | SYNC = 5V<br>(No Load)                           |       | 4.999           |      | V     |

| $\Delta_{VOUT}$                        | Variation of V <sub>OUT</sub><br>Over Temperature                  |                                                  | 0.2   | 1               | 3    | mV    |

| V <sub>IH</sub><br>SYNC, <del>SD</del> | High Level Input<br>Voltage                                        |                                                  | 3.5   | 5               |      | V     |

| $V_{IL}$ SYNC, $\overline{SD}$         | Low Level Input<br>Voltage                                         |                                                  |       | 0               | 1.5  | V     |

| I <sub>IL(SYNC)</sub>                  | Low Level Input<br>Current for SYNC                                | SYNC = 0V                                        | 5.0   | 42              | 1000 | nA    |

| I <sub>IH(SYNC)</sub>                  | High Level Input<br>Current for SYNC                               | SYNC = 5V <sub>DC</sub>                          | 170   | 215             | 275  | μΑ    |

| I <sub>OUT-AVE</sub>                   | V <sub>OUT</sub> Maximum Average<br>Load Current from (see Note 2) | SYNC = 5V <sub>PP</sub>                          |       |                 | 100  | mA    |

| R <sub>ON</sub><br>N-Channel           | On Resistance                                                      | $IL = 150 \text{ mA}$ $T_A = 27^{\circ}\text{C}$ |       | 0.9             | 1.5  | Ω     |

| R <sub>ON</sub><br>P-Channel           | On Resistance                                                      | $IL = 150 \text{ mA}$ $T_A = 27^{\circ}\text{C}$ |       | 0.7             | 1.2  | Ω     |

| R <sub>ON</sub><br>Matching            | On Resistance                                                      | $IL = 150 \text{ mA}$ $T_A = 27^{\circ}\text{C}$ |       | 0.18            | 0.6  | Ω     |

| Is                                     | Supply Current<br>from P5V                                         | No SYNC                                          | 200   | 355             | 950  | μΑ    |

## **AC Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_A = 27^{\circ}C$ ,  $V_{IN} = P5V = 5V$ . Other conditions are shown in the test circuit. Conditions that deviate from those shown in the test circuit are listed in the conditions column.

| Symbol              | Parameter                          | Conditions                                                         | Min | Typ<br>(Note 9) | Max | Units |

|---------------------|------------------------------------|--------------------------------------------------------------------|-----|-----------------|-----|-------|

| t <sub>s(OUT)</sub> | Settling Time for V <sub>OUT</sub> | To 98% p-p V <sub>OUT</sub> ,<br>V <sub>IN</sub> = 5V (see Note 3) |     |                 | 5.0 | μs    |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions the device is intended to be functional, but device parameter specifications may not be guaranteed under these conditions. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The typical junction-ambient thermal resistance of the molded plastic SO(M) package is 155°C/W. Therefore the maximum current for the buffer and voltage regulator are limited to the maximum total power dissipation that the package can allow in order to keep the die comfortably below the maximum operating injunction temperature of 125°C.

Note 3: The settling time of the Power Buffer is mostly dependent upon the TFT effective series RC load. The measurement of the settling time is taken for the application when driving an all black display. The number in the datasheet reflects a series RC load (R =  $6.8\Omega$  and C =  $0.22~\mu$ F).

**Note 4:** Human Body Model 100 pF and 1.5 k $\Omega$ . Machine Model 0 $\Omega$ .

Note 5: The precision of the P5V supply determines the output voltage swing precision of the buffer for very small loads. The operating range of P5V in this datasheet assumes a  $\pm 4\%$  error in V<sub>OUT</sub> p-p such that the total error of the signal at the output of the buffer never exceeds  $\pm 5\%$ .

Note 6: This capacitance is dominated by the ESD protection zeners connected to the SYNC pin.

Note 7: It is important to understand that the load current of the low drop-out voltage regulator must not drop below 2 mA. Otherwise, the internal error amplifier will not have sufficient drive capability to the large series pass transistor. If load requirements from the FPD system is less than 2 mA, an external pre-load resistor must be connected from V<sub>SH</sub> to ground in order to satisfy the previously mentioned load requirements.

Note 8: The thermal shutdown mode of the voltage regulator and the system shutdown mode are identical. When either of the two functions are enabled, two results occur. The pass transistor of the voltage regulator is shut off and The V<sub>REF</sub> pin of the LMC2626 is pulled up to the V<sub>IN</sub> supply to shutdown the LM2625 switching regulator.

Note 9: Typical values represent the most likely parametric norm.

Note 10: The typical closed loop voltage gain of the low drop-out voltage regulator is 3.44(10.7 dB).

Note 11: The minimum load current of the voltage regulator is a specific parameter used to guarantee that the regulated output voltage of the LDO regulator stays within the limits specified in the datasheet for 1.216V < V<sub>REF</sub> < 1.242V. For applications requiring minimum load current less than 20 mA, regulated output voltage limits of the voltage regulator and V<sub>REF</sub> voltage range must be carefully determined by characterizing the change in regulated output voltage at the minimum load current needed.

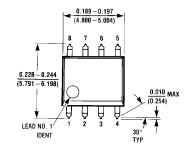

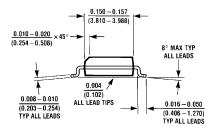

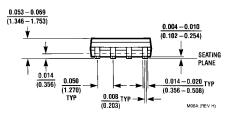

# Physical Dimensions inches (millimeters)

8-Lead (0.150" Wide) Molded Small Outline Package, JEDEC Order Number LMC2626IM NS Package M08A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor**

National Semiconducto Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor** Europe

Fax: +49 (0) 180-530 85 86 Fax: +49 (0) 180-530 so so Email: europe.support@nsc.com Deutsch Tel: +49 (0) 180-530 85 85 English Tel: +49 (0) 180-532 78 32 Français Tel: +49 (0) 180-532 95 58 Italiano Tel: +49 (0) 180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2308

Fax: 81-043-299-2408