## LM4917 Boomer® Audio Power Amplifier Series

# Ground-Referenced, 95mW Stereo Headphone Amplifier

### **General Description**

The LM4917 is a stereo, output capacitor-less headphone amplifier capable of delivering 95mW of continuous average power into a  $16\Omega$  load with less than 1% THD+N from a single 3V power supply.

The LM4917 provides high quality audio reproduction with minimal external components. A ground referenced output eliminates the output coupling capacitors typically required by single-ended loads, reducing component count, cost and board space consumption. This makes the LM4917 ideal for mobile phones and other portable equipment where board space is at a premium. Eliminating the output coupling capacitors also improves low frequency response.

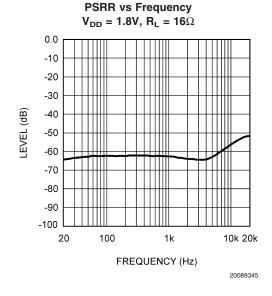

The LM4917 operates from a single 1.4V to 3.6V power supply, features low 0.02% THD+N and 70dB PSRR. Independent right/left channel low-power shutdown controls provide power saving flexibility for mono/stereo applications. Superior click and pop suppression eliminates audible transients during start up and shutdown. Short circuit and thermal overload protection protects the device during fault conditions.

## **Key Specifications**

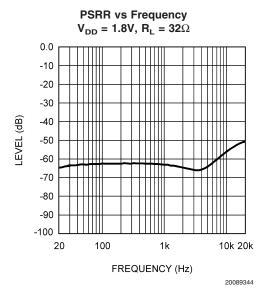

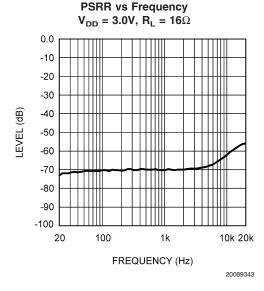

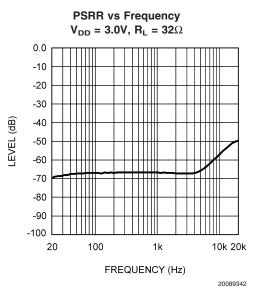

■ Improved PSRR at 1kHz 70dB (typ)

■ Power Output at  $V_{DD} = 3V$ ,

$R_L$  = 16 $\Omega$ , THD  $\leq$  1% 95mW (typ)

■ Shutdown Current 0.01µA (typ)

#### **Features**

- Ground referenced outputs

- High PSRR

- Available in space-saving TSSOP package

- Ultra low current shutdown mode

- Improved pop & click circuitry eliminates noises during turn-on and turn-off transitions

- 1.4 3.6V operation

- No output coupling capacitors, snubber networks, bootstrap capacitors

- Shutdown either channel independently

## **Applications**

- Notebook PCs

- Desktop PCs

- Mobile Phone

- PDAs

- Portable electronic devices

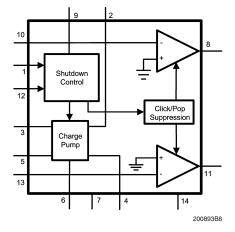

## **Block Diagram**

FIGURE 1. Circuit Block Diagram

Boomer® is a registered trademark of National Semiconductor Corporation.

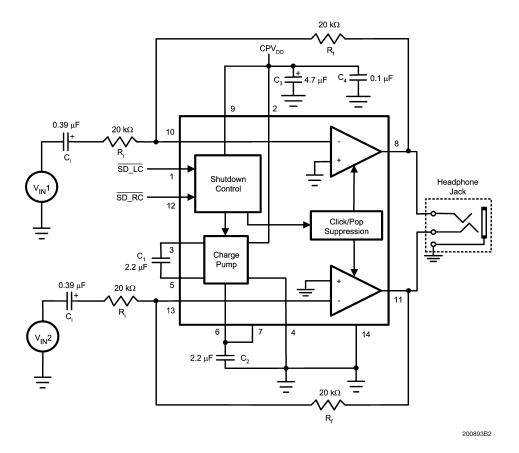

# **Typical Application**

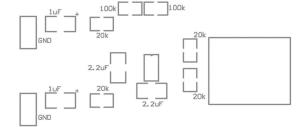

FIGURE 2. Typical Audio Amplifier Application Circuit

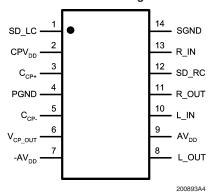

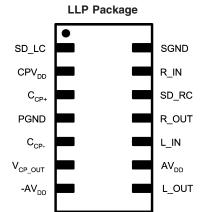

# **Connection Diagrams**

### **TSSOP Package**

Top View Order Number LM4917MT See NS Package Number MTC14

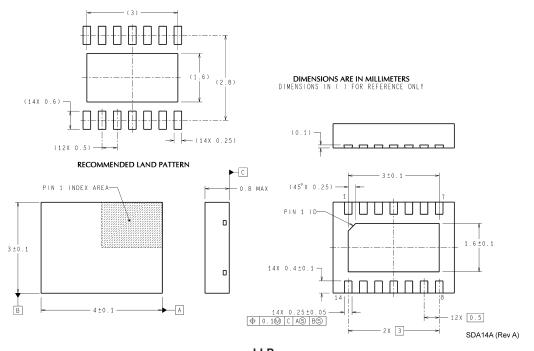

Top View Order Number LM4917SD See NS Package Number SDA14A

# ZXYTT L4917 MT

**TSSOP Marking**

Z - Assembly Plant Code XY - Date Code TT - Traceability

#### **LLP Marking**

Z - Assembly Plant Code XY - Date Code TT - Traceability

#### **Pin Descriptions**

| Pin | Name                | Function                                        |  |

|-----|---------------------|-------------------------------------------------|--|

| 1   | SD_LC               | Active_Low Shutdown, Left Channel               |  |

| 2   | CP <sub>VDD</sub>   | Charge Pump Power Supply                        |  |

| 3   | C <sub>CP+</sub>    | Positive Terminal-Charge Pump Flying Capacitor  |  |

| 4   | PGND                | Power Ground                                    |  |

| 5   | C <sub>CP-</sub>    | Negative Terminal- Charge Pump Flying Capacitor |  |

| 6   | V <sub>CP_OUT</sub> | Charge Pump Output                              |  |

| 7   | -AV <sub>DD</sub>   | Negative Power Supply-Amplifier                 |  |

| 8   | L_OUT               | Left Channel Output                             |  |

| 9   | $AV_DD$             | Positive Power Supply-Amplifier                 |  |

| 10  | L_IN                | Left Channel Input                              |  |

| 11  | R_OUT               | Right Channel Output                            |  |

| 12  | SD_RC               | Active_Low Shutdown, Right Channel              |  |

| 13  | R_IN                | Right Channel Input                             |  |

| 14  | SGND                | Signal Ground                                   |  |

## **Absolute Maximum Ratings** (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage 4.0V Storage Temperature -65°C to +150°C Input Voltage -0.3V to  $V_{DD} + 0.3V$ Power Dissipation (Note 3) Internally Limited

2000V ESD Susceptibility (Note 4) 200V

ESD Susceptibility (Note 5)

Junction Temperature 150°C

Thermal Resistance

$\theta_{JC}$  (TSSOP) 40°C/W  $\theta_{JA}$  (TSSOP) 109°C/W

## Operating Ratings

Temperature Range

$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$  $T_{MIN} \le T_A \le T_{MAX}$ Supply Voltage (V<sub>DD</sub>)  $1.4V \le V_{CC} \le 3.6V$

### Electrical Characteristics V<sub>DD</sub> = 3V (Notes 1, 2)

The following specifications apply for  $V_{DD}$  = 3V,  $A_V$  = 1, and 16 $\Omega$  load unless otherwise specified. Limits apply to  $T_A$  = 25°C.

| Symbol            | Parameter                         | Conditions                                                               | LM4917                                  |                          | Units    |

|-------------------|-----------------------------------|--------------------------------------------------------------------------|-----------------------------------------|--------------------------|----------|

|                   |                                   |                                                                          | Typ<br>(Note 6)                         | Limit<br>(Notes 7,<br>8) | (Limits) |

| I <sub>DD</sub>   | Quiescent Power Supply Current    | $V_{IN} = 0V$ , $I_O = 0A$ , both channels enabled                       | 11                                      | 20                       | mA (max) |

|                   |                                   | $V_{IN} = 0V$ , $I_O = 0A$ , one channel enabled                         | 9                                       |                          | mA       |

| I <sub>SD</sub>   | Shutdown Current                  | $V_{SD\_LC} = V_{SD\_RC} = GND$                                          | 0.01                                    | 1                        | μA (max) |

| V <sub>os</sub>   | Output Offset Voltage             | $R_L = 32\Omega$                                                         | 1                                       | 10                       | mV (max) |

| P <sub>O</sub>    | Output Power                      | THD+N = 1% (max); f = 1kHz, $R_L = 16\Omega$                             | 95                                      | 50                       | mW (min) |

|                   |                                   | THD+N = 1% (max); f = 1kHz, $R_L = 32\Omega$                             | 82                                      |                          | mW       |

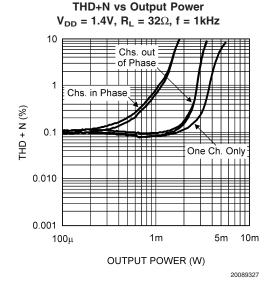

| THD+N             | Total Harmonic Distortion + Noise | $P_O = 50$ mW, $f = 1$ kHz, $R_L = 32\Omega$ (A-weighted) single channel | 0.02                                    |                          | %        |

| PSRR              | Power Supply Rejection Ratio      | $V_{RIPPLE}$ = 200mV sine p-p,<br>f = 1kHz<br>f = 20kHz                  | 70<br>55                                |                          | dB       |

| SNR               | Signal-to-Noise Ratio             | $R_L = 32\Omega$ , $P_{OUT} = 20$ mW, $f = 1$ kHz                        | 100                                     |                          | dB       |

| V <sub>IH</sub>   | Shutdown Input Voltage High       |                                                                          | V <sub>IH</sub> = 0.7*CPV <sub>DD</sub> |                          | V (min)  |

| V <sub>IL</sub>   | Shutdown Input Voltage Low        |                                                                          | V <sub>IL</sub> = 0.3*CPV <sub>DD</sub> |                          | V (max)  |

| T <sub>WU</sub>   | Wake Up Time From Shutdown        |                                                                          | 339                                     |                          | μs (max) |

| X <sub>TALK</sub> | Crosstalk                         | $R_L = 16\Omega$ , $P_O = 1.6$ mW, $f = 1$ kHz                           | 70                                      |                          | dB       |

| IL                | Input Leakage Current             |                                                                          | ±0.1                                    |                          | nA       |

Note 1: All voltages are measured with respect to the GND pin unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions that guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given; however, the typical value is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by T, IMAX,  $\theta$ , IA, and the ambient temperature, TA. The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A) / \theta_{JA}$  or the number given in Absolute Maximum Ratings, whichever is lower. For the LM4917, see power de-rating currents for more information.

**Note 4:** Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

Note 5: Machine Model, 220pF-240pF discharged through all pins.

Note 6: Typicals are measured at 25°C and represent the parametric norm.

Note 7: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 9: If the product is in shutdown mode and VDD exceeds 3.6V (to a max of 4V VDD) then most of the excess current will flow through the ESD protection circuits. If the source impedance limits the current to a max of 10mA, then the part will be protected. If the part is enabled when V<sub>DD</sub> is above 4V circuit performance will be curtailed or the part may be permanently damaged.

Note 10: Human body model, 100pF discharged through a 1.5k $\Omega$  resistor.

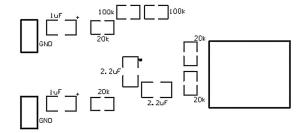

# External Components Description (Figure 1)

| Components |                | Functional Description                                                                                                                                                                                                                                                                                |  |  |

|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.         | R <sub>i</sub> | Inverting input resistance which sets the closed-loop gain in conjunction with $R_f$ . This resistor also forms a high-pass filter with $C_i$ at $f_c = 1 / (2\pi R_i C_i)$ .                                                                                                                         |  |  |

| 2.         | C <sub>i</sub> | Input coupling capacitor which blocks the DC voltage at the amplifier's input terminals. Also creates a high-pass filter with $R_i$ at $f_c = 1 / (2\pi R_i C_i)$ . Refer to the section <b>Proper Selection of External Components</b> , for an explanation of how to determine the value of $C_i$ . |  |  |

| 3.         | R <sub>f</sub> | Feedback resistance which sets the closed-loop gain in conjunction with R <sub>i</sub> .                                                                                                                                                                                                              |  |  |

| 4.         | C <sub>1</sub> | Flying capacitor. Low ESR ceramic capacitor (≤100mΩ)                                                                                                                                                                                                                                                  |  |  |

| 5.         | C <sub>2</sub> | Output capacitor. Low ESR ceramic capacitor (≤100mΩ)                                                                                                                                                                                                                                                  |  |  |

| 6.         | C <sub>3</sub> | Tantalum capacitor. Supply bypass capacitor which provides power supply filtering. Refer to the Power Supply Bypassing section for information concerning proper placement and selection of the supply bypass capacitor.                                                                              |  |  |

| 7.         | C <sub>4</sub> | Ceramic capacitor. Supply bypass capacitor which provides power supply filtering. Refer to the Power Supply Bypassing section for information concerning proper placement and selection of the supply bypass capacitor.                                                                               |  |  |

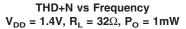

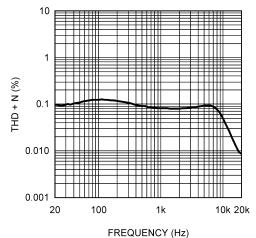

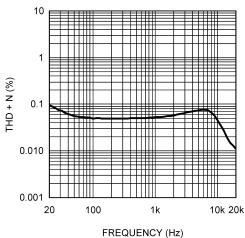

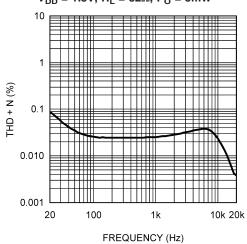

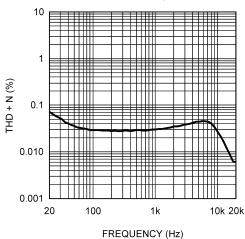

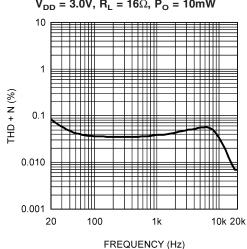

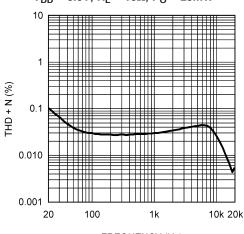

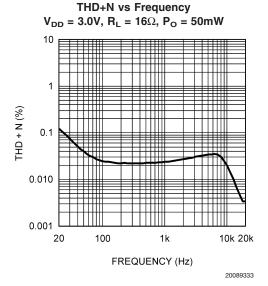

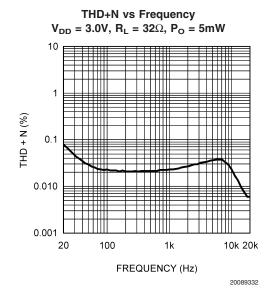

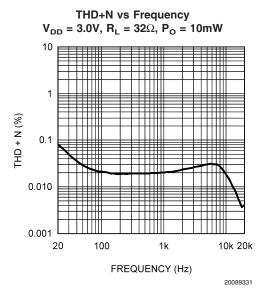

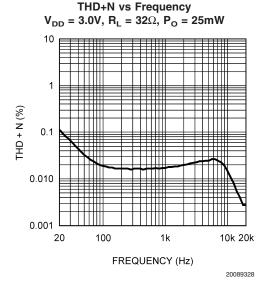

# **Typical Performance Characteristics**

20089341

# THD+N vs Frequency $\label{eq:VDD} {\rm V_{DD}} = {\rm 1.8V}, \, {\rm R_L} = {\rm 16}\Omega, \, {\rm P_O} = {\rm 5mW}$

20089339

# THD+N vs Frequency $V_{DD}$ = 1.8V, $R_L$ = 32 $\Omega$ , $P_O$ = 5mW

20089338

20089336

6

THD+N vs Frequency  $V_{DD}$  = 1.8V,  $R_L$  = 32 $\Omega$ ,  $P_O$  = 10mW

20089348

# THD+N vs Frequency $V_{DD}$ = 3.0V, $R_L$ = 16 $\Omega$ , $P_O$ = 10mW

THD+N vs Frequency  $V_{DD}$  = 3.0V,  $R_L$  = 16 $\Omega$ ,  $P_O$  = 25mW

FREQUENCY (Hz)

20089334

20089306

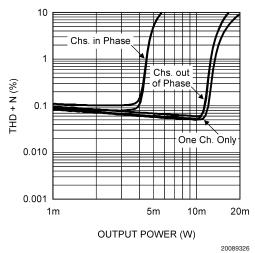

# THD+N vs Output Power $V_{DD}$ = 1.8V, $R_L$ = 16 $\Omega$ , f = 1kHz

# THD+N vs Output Power $V_{DD} = 1.8V$ , $R_L = 32\Omega$ , f = 1kHz

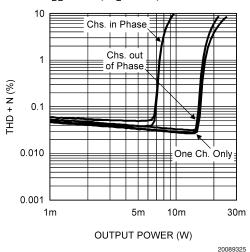

# THD+N vs Output Power $\label{eq:VDD} \textbf{V}_{\text{DD}} = \textbf{3.0V}, \ \textbf{R}_{\text{L}} = \textbf{16}\Omega, \ \textbf{f} = \textbf{1kHz}$

THD+N vs Output Power  $\label{eq:VDD} \textbf{V}_{\text{DD}} = \textbf{3.0V}, \ \textbf{R}_{\text{L}} = \textbf{32}\Omega, \ \textbf{f} = \textbf{1kHz}$

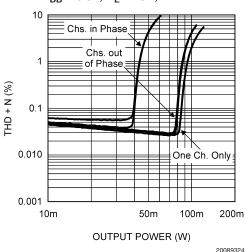

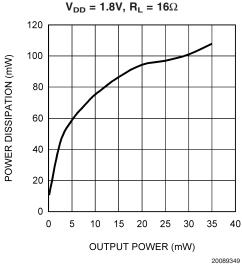

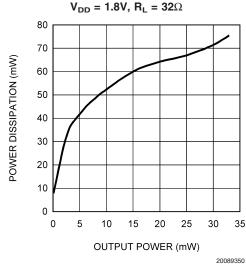

Power Dissipation vs Output Power

Power Dissipation vs Output Power

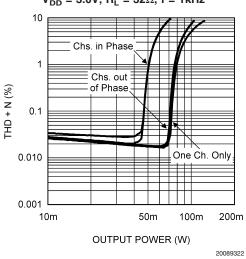

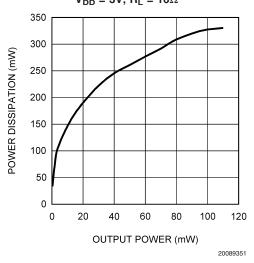

Power Dissipation vs Output Power  $\mbox{V}_{\mbox{\scriptsize DD}} = 3\mbox{V}, \mbox{R}_{\mbox{\scriptsize L}} = 16\Omega$

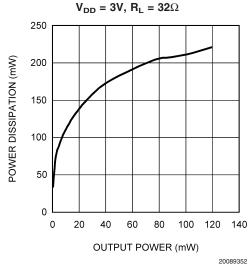

# Power Dissipation vs Output Power

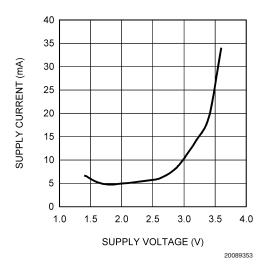

#### Supply Current vs Supply Voltage

### **Application Information**

#### **ELIMINATING THE OUTPUT COUPLING CAPACITOR**

The LM4917 features a low noise inverting charge pump that generates an internal negative supply voltage. This allows the outputs of the LM4917 to be biased about GND instead of a nominal DC voltage, like traditional headphone amplifiers. Because there is no DC component, the large DC blocking capacitors (typically 220µF) are not necessary. The coupling capacitors are replaced by two, small ceramic charge pump capacitors, saving board space and cost.

Eliminating the output coupling capacitors also improves low frequency response. The headphone impedance and the output capacitor form a high pass filter that not only blocks the DC component of the output, but also attenuates low frequencies, impacting the bass response. Because the LM4917 does not require the output coupling capacitors, the low frequency response of the device is not degraded by external components.

In addition to eliminating the output coupling capacitors, the ground referenced output nearly doubles the available dynamic range of the LM4917 when compared to a traditional headphone amplifier operating from the same supply voltage.

# OUTPUT TRANSIENT ('CLICK AND POPS') ELIMINATED

The LM4917 contains advanced circuitry that virtually eliminates output transients ('clicks and pops'). This circuitry prevents all traces of transients when the supply voltage is first applied or when the part resumes operation after coming out of shutdown mode.

To ensure optimal click and pop performance under low gain configurations (less than 0dB), it is critical to minimize the RC combination of the feedback resistor  $\rm R_F$  and stray input capacitance at the amplifier inputs. A more reliable way to lower gain or reduce power delivered to the load is to place a current limiting resistor in series with the load as explained in the <code>Minimizing Output Noise / Reducing Output Power section</code>.

#### **AMPLIFIER CONFIGURATION EXPLANATION**

As shown in Figure 2, the LM4917 has two operational amplifiers internally. The two amplifiers have externally configurable gain, and the closed loop gain is set by selecting the ratio of  $\rm R_f$  to  $\rm R_i$ . Consequently, the gain for each channel of the IC is

$$A_V = -(R_f / R_i)$$

Since this an output ground-referenced amplifier, by driving the headphone through  $R_{\rm OUT}$  (Pin 11) and  $L_{\rm OUT}$  (Pin 8), the LM4917 does not require output coupling capacitors. The typical single-ended amplifier configuration where one side of the load is connected to ground requires large, expensive output capacitors.

#### POWER DISSIPATION

Power dissipation is a major concern when using any power amplifier and must be thoroughly understood to ensure a successful design. Equation 1 states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$$P_{DMAX} = (V_{DD})^2 / (2\pi^2 R_L)$$

(1)

Since the LM4917 has two operational amplifiers in one package, the maximum internal power dissipation point is twice that of the number which results from Equation 1. Even with the large internal power dissipation, the LM4917 does not require heat sinking over a large range of ambient temperature. From Equation 1, assuming a 3V power supply and a 16 $\Omega$  load, the maximum power dissipation point is 28mW per amplifier. Thus the maximum package dissipation point is 56mW. The maximum power dissipation point obtained must not be greater than the power dissipation that results from Equation 2:

$$P_{DMAX} = (T_{JMAX} - T_A) / (\theta_{JA})$$

(2)

For package TSSOP,  $\theta_{JA} = 109^{\circ}\text{C/W}$ .  $T_{JMAX} = 150^{\circ}\text{C}$  for the LM4917. Depending on the ambient temperature, TA, of the system surroundings, Equation 2 can be used to find the maximum internal power dissipation supported by the IC packaging. If the result of Equation 1 is greater than that of Equation 2, then either the supply voltage must be decreased, the load impedance increased or TA reduced. For the typical application of a 3V power supply, with a  $16\Omega$  load, the maximum ambient temperature possible without violating the maximum junction temperature is approximately 119.9°C provided that device operation is around the maximum power dissipation point. Power dissipation is a function of output power and thus, if typical operation is not around the maximum power dissipation point, the ambient temperature may be increased accordingly. Refer to the Typical Performance Characteristics curves for power dissipation information for lower output powers.

#### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 3V power supply typically use a 4.7µF in parallel with a 0.1µF ceramic filter capacitors to stabilize the power supply's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 0.1µF supply bypass capacitor,  $C_{\rm S}$ , connected between the LM4917's supply pins and ground. Keep the length of leads and traces that connect capacitors between the LM4917's power supply pin and ground as short as possible.

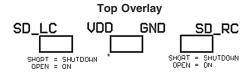

#### MICRO POWER SHUTDOWN

The voltage applied to the  $\overline{SD\_LC}$  (shutdown left channel) pin and the  $\overline{SD\_RC}$  (shutdown right channel) pin controls the LM4917's shutdown function. When active, the LM4917's micropower shutdown feature turns off the amplifiers' bias circuitry, reducing the supply current. The trigger point is  $0.3^*CPV_{DD}$  for a logic-low level, and  $0.7^*CPV_{DD}$  for logic-high level. The low  $0.01\mu A(typ)$  shutdown current is achieved by appling a voltage that is as near as ground a possible to the  $\overline{SD\_LC/SD\_RC}$  pins. A voltage that is higher than ground may increase the shutdown current.

There are a few ways to control the micro-power shutdown. These include using a single-pole, single-throw switch, a microprocessor, or a microcontroller. When using a switch, connect an external 100k $\Omega$  pull-up resistor between the  $\overline{SD\_LC/SD\_RC}$  pins and  $V_{DD}$ . Connect the switch between the  $\overline{SD\_LC/SD\_RC}$  pins and ground. Select normal amplifier

operation by opening the switch. Closing the switch connects the SD\_LC/SD\_RC pins to ground, activating micropower shutdown. The switch and resistor guarantee that the SD\_LC/SD\_RC pins will not float. This prevents unwanted state changes. In a system with a microprocessor or microcontroller, use a digital output to apply the control voltage to the SD\_LC/SD\_RC pins. Driving the SD\_LC/SD\_RC pins with active circuitry eliminates the pull-up resistor.

#### SELECTING PROPER EXTERNAL COMPONENTS

Optimizing the LM4917's performance requires properly selecting external components. Though the LM4917 operates well when using external components with wide tolerances, best performance is achieved by optimizing component values.

The LM4917 is unity-gain stable, giving a designer maximum design flexibility. The gain should be set to no more than a given application requires. This allows the amplifier to achieve minimum THD+N and maximum signal-to-noise ratio. These parameters are compromised as the closed-loop gain increases. However, low gain demands input signals with greater voltage swings to achieve maximum output power. Fortunately, many signal sources such as audio CODECs have outputs of 1V<sub>RMS</sub> (2.83V<sub>P-P</sub>). Please refer to the **Audio Power Amplifier Design** section for more information on selecting the proper gain.

#### **Charge Pump Capacitor Selection**

Choose low ESR (<100m $\Omega$ ) ceramic capacitors for optimum performance. Low ESR capacitors keep the charge pump output impedance to a minimum, extending the headroom on the negative supply. Choose capacitors with an X7R dielectric for best performance over temperature.

Charge pump load regulation and output resistance is affected by the value of the flying capacitor (C1). A larger valued C1 improves load regulation and minimizes charge pump output resistance. The switch on-resistance and capacitor ESR dominates the output resistance for capacitor values above  $2.2\mu F$ .

The output ripple is affected by the value and ESR of the output capacitor (C2). Larger valued capacitors reduce output ripple on the negative power supply. Lower ESR capacitors minimizes the output ripple and reduces the output resistance of the charge pump.

#### Input Capacitor Value Selection

Amplifying the lowest audio frequencies requires high value input coupling capacitor ( $C_i$  in Figure 2). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using speakers with this limited frequency response reap little improvement by using high value input and output capacitors.

Besides affecting system cost and size,  $C_i$  has an effect on the LM4917's click and pop performance. The magnitude of the pop is directly proportional to the input capacitor's size. Thus, pops can be minimized by selecting an input capacitor value that is no higher than necessary to meet the desired –3dB frequency.

As shown in Figure 2, the input resistor,  $R_i$  and the input capacitor,  $C_i$ , produce a -3dB high pass filter cutoff frequency that is found using Equation (3).

$$f_{i-3dB} = 1 / 2\pi R_i C_i$$

(3)

Also, careful consideration must be taken in selecting a certain type of capacitor to be used in the system. Different types of capacitors (tantalum, electrolytic, ceramic) have unique performance characteristics and may affect overall system performance.

#### **AUDIO POWER AMPLIFIER DESIGN**

#### Design a Dual 90mW/16Ω Audio Amplifier

Given:

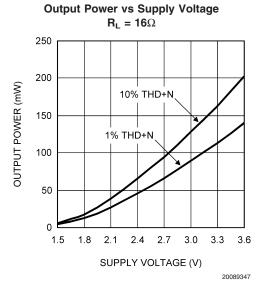

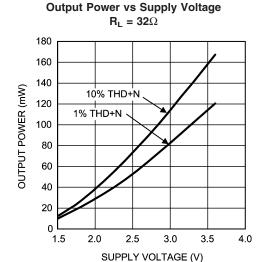

The design begins by specifying the minimum supply voltage necessary to obtain the specified output power. One way to find the minimum supply voltage is to use the Output Power vs Supply Voltage curve in the **Typical Performance Characteristics** section. Another way, using Equation (5), is to calculate the peak output voltage necessary to achieve the desired output power for a given load impedance. For a single-ended application, the result is Equation (5).

$$V_{\text{opeak}} = \sqrt{(2R_{L}P_{0})}$$

(4)

$$V_{DD} \ge [2V_{OPEAK} + (V_{DOTOP} + V_{DOBOT})]$$

(5)

The Output Power vs Supply Voltage graph for a  $16\Omega$  load indicates a minimum supply voltage of 3.1V. This is easily met by the commonly used 3.3V supply voltage. The additional voltage creates the benefit of headroom, allowing the LM4917 to produce peak output power in excess of 90mW without clipping or other audible distortion. The choice of supply voltage must also not create a situation that violates maximum power dissipation as explained above in the **Power Dissipation** section. Remember that the maximum power dissipation point from Equation (1) must be multiplied by two since there are two independent amplifiers inside the package. Once the power dissipation equations have been addressed, the required gain can be determined from Equation (6).

$$A_{V} \ge \sqrt{(P_{O}R_{L})}/(V_{IN}) = V_{orms}/V_{inrms}$$

(6)

Thus, a minimum gain of 1.2 allows the LM4917 to reach full output swing and maintain low noise and THD+N perfromance. For this example, let  $A_{\rm V}=1.5$ .

The amplifiers overall gain is set using the input ( $R_i$ ) and feedback ( $R_f$ ) resistors. With the desired input impedance set at  $20k\Omega$ , the feedback resistor is found using Equation (7).

$$A_{V} = R_{f} / R_{i} \tag{7}$$

The value of  $R_f$  is  $30k\Omega$ .

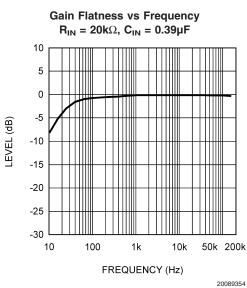

The last step in this design is setting the amplifier's -3db frequency bandwidth. To achieve the desired  $\pm 0.25dB$  pass band magnitude variation limit, the low frequency response must extend to at lease one–fifth the lower bandwidth limit and the high frequency response must extend to at least five times the upper bandwidth limit. The gain variation for both response limits is 0.17dB, well within the  $\pm 0.25dB$  desired limit. The results are

$$f_L = 100Hz / 5 = 20Hz$$

(8)

and

$$f_H = 20kHz \times 5 = 100kHz$$

(9)

As stated in the **External Components** section, both  $R_i$  in conjunction with  $C_i$ , and  $R_L$ , create first order highpass fil-

ters. Thus to obtain the desired low frequency response of 100Hz within  $\pm 0.5$ dB, both poles must be taken into consideration. The combination of two single order filters at the same frequency forms a second order response. This results in a signal which is down 0.34dB at five times away from the single order filter -3dB point. Thus, a frequency of 20Hz is used in the following equations to ensure that the response is better than 0.5dB down at 100Hz.

$$C_i \ge 1 / (2\pi^* 20 k\Omega^* 20 Hz) = 0.397 \mu F$$

; use  $0.39 \mu F$  (10)

The high frequency pole is determined by the product of the desired high frequency pole,  $f_{\rm H},$  and the closed-loop gain,  $A_{\rm V}.$  With a closed-loop gain of 1.5 and  $f_{\rm H}=100{\rm kHz},$  the resulting GBWP = 150kHz which is much smaller than the LM4917's GBWP of 3MHz. This figure displays that if a designer has a need to design an amplifier with a higher gain, the LM4917 can still be used without running into bandwidth limitations.

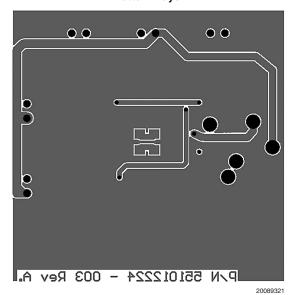

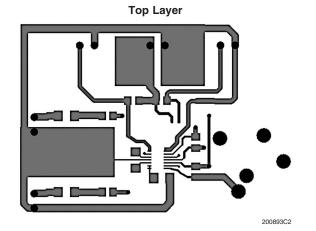

#### LM4917 SO DEMO BOARD ARTWORK

#### **Top Overlay**

## NATIONAL SEMICONDUCTOR

LM4917MT Audio Power Amplifier

## 20089304

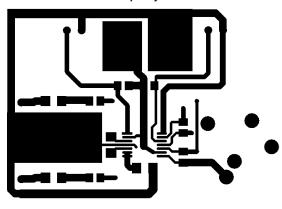

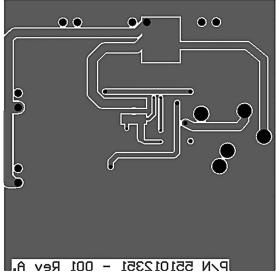

#### **Bottom Layer**

20089305

#### LM4917 LLP DEMO BOARD ARTWORK

### NATIONAL SEMICONDUCTOR

LM4917SD Audio Power Amplifier

200893C3

#### **Bottom Layer**

200893C1

15

#### LM4917 REFERENCE DESIGN BOARDS BILL OF MATERIALS

| Part Description                        | Qty | Ref Designator |

|-----------------------------------------|-----|----------------|

| LM4917 Mono Reference Design Board      | 1   |                |

| LM4917 Audio AMP                        | 1   | U1             |

| Tantalum Cap 1µF 16V 10                 | 1   | Cs             |

| Ceramic Cap 0.39µF 50V Z50 20           | 2   | Ci             |

| Resistor 20kΩ 1/10W 5                   | 4   | Ri, Rf         |

| Resistor 100kΩ 1/10W 5                  | 1   | Rpu            |

| Jumper Header Vertical Mount 2X1, 0.100 | 1   | J1             |

#### **PCB LAYOUT GUIDELINES**

This section provides practical guidelines for mixed signal PCB layout that involves various digital/analog power and ground traces. Designers should note that these are only "rule-of-thumb" recommendations and the actual results will depend heavily on the final layout.

#### Minimization of THD

PCB trace impedance on the power, ground, and all output traces should be minimized to achieve optimal THD performance. Therefore, use PCB traces that are as wide as possible for these connections. As the gain of the amplifier is increased, the trace impedance will have an ever increasing adverse affect on THD performance. At unity-gain (0dB) the parasitic trace impedance effect on THD performance is reduced but still a negative factor in the THD performance of the LM4917 in a given application.

# GENERAL MIXED SIGNAL LAYOUT RECOMMENDATION

#### **Power and Ground Circuits**

For two layer mixed signal design, it is important to isolate the digital power and ground trace paths from the analog power and ground trace paths. Star trace routing techniques (bringing individual traces back to a central point rather than daisy chaining traces together in a serial manner) can greatly enhance low level signal performance. Star trace routing refers to using individual traces to feed power and ground to each circuit or even device. This technique will require a greater amount of design time, but will not increase the final price of the board. The only extra parts required may be some jumpers.

#### **Single-Point Power / Ground Connections**

The analog power traces should be connected to the digital traces through a single point (link). A "PI-filter" can be helpful in minimizing high frequency noise coupling between the analog and digital sections. Further, place digital and analog power traces over the corresponding digital and analog ground traces to minimize noise coupling.

#### **Placement of Digital and Analog Components**

All digital components and high-speed digital signal traces should be located as far away as possible from analog components and circuit traces.

#### **Avoiding Typical Design / Layout Problems**

Avoid ground loops or running digital and analog traces parallel to each other (side-by-side) on the same PCB layer. When traces must cross over each other do it at 90 degrees. Running digital and analog traces at 90 degrees to each other from the top to the bottom side as much as possible will minimize capacitive noise coupling and cross talk.

## Physical Dimensions inches (millimeters) unless otherwise noted ₿ (5.94) 6.4 3.2 GAGE PLANE-0.25 ALL LEAD TIPS RECOMMENDED LAND PATTERN SEATING PLANE 0.6±0.1 DETAIL A SEE DETAIL A 1.1 MAX C ⊕ 0.13W A BS CS DIMENSIONS ARE IN MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY 12X 0.65

TSSOP Order Number LM4917MT NS Package Number MTC14

LLP Order Number LM4917SD NS Package Number SDA14A

MTC14 (Rev D)

#### **Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560