3.0V to 5.5V

#### **Boomer**® Audio Power Amplifier Series LM4817

# 1W Stereo Audio Amplifier Plus Adjustable Output **Limiter Plus Adjustable LDO**

# **General Description**

The LM4817 combines a bridge-connected (BTL) stereo audio power amplifier with a low dropout voltage regulator (LDO). The audio amplifier delivers 1.0W to a  $8\Omega$  load with a less than 1.0% THD+N while operating on a 5V power supply. With  $V_{\text{LIM}}$  set to 1.0V, the amplifier outputs are clamped to 6V<sub>p-p</sub>, ±800mV.

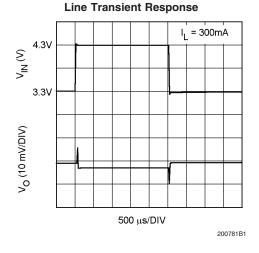

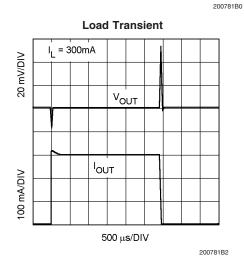

With the LM4817's adjustable low-dropout (LDO) CMOS linear regulator delivers an output current of up to 300mA, has shutdown mode (1nA, typ) low quiescent current (90µA, typ) and LDO voltage (120mV, typ). The regulator is stable with small ceramic capacitive load (2.2µF, typ). The regulator includes regulation fault detection, a bandgap voltage reference, and constant current limiting. It is designed for low power, low current applications that can take advantage of its 300mA output current capability.

The LM4817 features an externally controlled micropower shutdown mode and thermal shutdown protection. It also utilizes circuitry that reduces "clicks and pops" during device turn-on and return from shutdown.

Boomer audio power amplifiers are designed specifically to use few external components and provide high quality output power in a surface mount package.

# **Key Specifications**

■ Power supply range (amplifier)

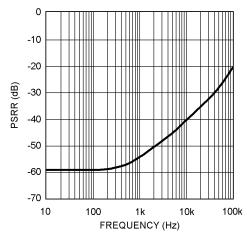

2.5V to 6.0V ■ Power supply range (LDO) ■ Shutdown current 0.07µA (typ) ■ LDO output current 300mA (min) ■ LDO dropout voltage (I<sub>OUT</sub> = 300mA) 120mV (typ) ■ LDO quiescent supply current 90μA (typ) ■ LDO shutdown supply current 1nA (typ) ■ LDO PSRR 60dB ■ LDO turn-on time 120ms (typ) ■ LDO ouput noise-voltage  $37\mu V_{RMS}$  (typ)

■  $P_O$  (BTL):  $V_{DD} = 5V$ , THD+N  $\leq 1\%$ ,  $R_L = 8\Omega$  1.0W(typ)

**Features**

- Stereo BTL amplifier

- Adjustable output voltage magnitude limiter

- Adjustable LDO regulator

- "Click and pop" suppression circuitry

- LDO is stable with small-value ceramic output capacitors

- Unity-gain stable audio amplifiers

- LDO has over-current protection

- Thermal shutdown protection circuitry

- TSSOP (MH) package

# Applications

- Multimedia monitors

- Portable and desktop computers

- Portable televisions

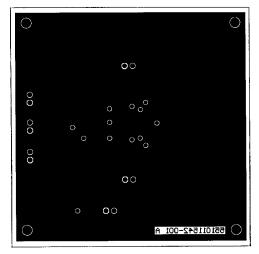

# **Connection Diagram**

**Top View** Order Number LM4817MH See NS Package Number MXA28A for TSSOP

Boomer® is a registered trademark of National Semiconductor Corporation.

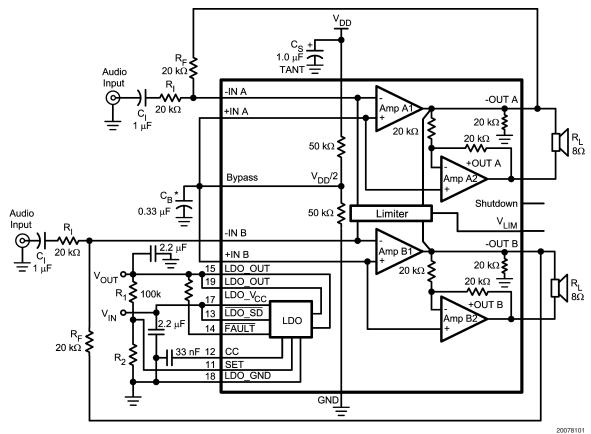

#### **Typical Application** $V_{DD}$ C<sub>S</sub> + 1.0 µF 1.0 µF R<sub>F</sub> 20 kΩ Audio Input -IN A -OUT A **-)|-**Ը<sub>լ</sub> 1 μF 20 kΩ Amp A +IN A 20 kΩ **§** 20 kΩ 20 kΩ 50 kΩ **≶** +OUT A V<sub>DD</sub>/2 Bypass Shutdown 0.33 μF 🗍 50 kΩ **≶** Limiter Audio Input -IN B **C**<sub>I</sub> 20 kΩ 1 μF -OUT B Amp B1 +IN B 20 kΩ **§** LDO\_OUT 20 kΩ **§** V<sub>OUT</sub> ❖ 20 kΩ = LDO\_OUT $R_1$ 100k rdo\_rcc +OUT B LDO\_SD 13 LDO FAULT R<sub>F</sub> \$ 20 kΩ CC SET LDO\_GND 11 18 GND 20078101

# **Absolute Maximum Ratings** Stereo Amplifier(Notes 1, 5)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Amplifier Supply Voltage (pins 5, 24) 6.0V

LDO-V<sub>CC</sub>, LDO-OUT, LDO-SHDN,

ADJ, CC, FAULT (pins 11-15, 17,19) -0.3V to 6.5V

Fault Sink Current 20mA

Storage Temperature -65°C to +150°C

Input Voltage -0.3V to  $V_{\rm DD}$  +0.3V

Power Dissipation (Note 2) Internally limited

ESD Susceptibility(Note 3) 2000V

ESD Susceptibility (Note 4) 200V

Junction Temperature 150°C

Solder Information

Small Outline Package

Vapor Phase (60 sec.) 215°C 220°C Infrared (15 sec.)

See AN-450 "Surface Mounting and their Effects on Product Reliablilty" for other methods of soldering surface mount devices.

Thermal Resistance

$\theta_{JC}$  (typ) — MXA28A 20°C/W  $\theta_{JA}$  (typ) — MXA28A (Note 2) 41°C/W

# Operating Ratings

Temperature Range

$T_{MIN} \le T_A \le T_{MAX}$  $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$

Supply Voltage

Pins 5, 24  $3.0V \leq V_{DD} \leq 5.5V$

Pin 17  $2.5V \le V_{CC} \le 6.0V$

# Stereo Amplifier Electrical Characteristics for Entire IC (Notes 1, 5)

The following specifications apply for  $V_{DD}$  = 5V unless otherwise noted. Limits apply for  $T_A$  = 25°C.

| Symbol            | Parameter                                   | Conditions                                              | LM <sup>2</sup> | LM4817   |                        |  |

|-------------------|---------------------------------------------|---------------------------------------------------------|-----------------|----------|------------------------|--|

|                   |                                             |                                                         | Typical         | Limit    | (Limits)               |  |

|                   |                                             |                                                         | (Note 6)        | (Note 7) |                        |  |

| V <sub>DD</sub>   | Supply Voltage                              |                                                         |                 | 3        | V (min)                |  |

|                   |                                             |                                                         |                 | 5.5      | V (max)                |  |

| I <sub>DD</sub>   | Quiescent Power Supply Current              | $V_{IN} = 0V$ , $I_O = 0A$ (Note 8)                     | 8               | 15       | mA (max)               |  |

|                   |                                             |                                                         |                 | 5        | mA (min)               |  |

| I <sub>SD</sub>   | Shutdown Current                            | V <sub>DD</sub> applied to the SHUTDOWN pin             | 0.07            | 2        | μA (min)               |  |

| V <sub>IH</sub>   | Shutdown Logic High Input Threshold Voltage |                                                         |                 | 3.0      | V (min)                |  |

| V <sub>IL</sub>   | Shutdown Logic Low Input                    |                                                         |                 | 1.8      | V (max)                |  |

|                   | Threshold Voltage                           |                                                         |                 |          |                        |  |

| V <sub>os</sub>   | Output Offset Voltage                       | $V_{IN} = 0V$                                           | 5               | 50       | mV (max)               |  |

| Po                | Output Power (Note 9)                       | THD+N = 1%, f = 1kHz, $R_L = 8\Omega$                   | 1.1             | 1.0      | W (min)                |  |

|                   |                                             | THD+N = 10%, f = 1kHz, $R_L = 8\Omega$                  | 1.5             |          | W                      |  |

| THD+N             | Total Harmonic Distortion+Noise             | $20$ Hz $\leq$ f $\leq$ $20$ kHz, $A_{VD} = 2$          | 0.13            |          | %                      |  |

|                   |                                             | $R_L = 8\Omega, P_O = 1W$                               |                 |          |                        |  |

| $V_{LIM}$         | Limiter Clamp Voltage                       | $V_{LIM} = 1.0V$ , $R_L = \infty$ , $V_{IN} = 4V_{P-P}$ | 6.0             | 5.2      | V <sub>P-P</sub> (min) |  |

|                   |                                             | $V_{O P-P} = (V_{OUT+} - V_{OUT-})$                     |                 | 6.8      | V <sub>P-P</sub> (max) |  |

| PSRR              | Power Supply Rejection Ratio                | $V_{DD} = 5V$ , $V_{RIPPLE} = 200 \text{mV}_{RMS}$ ,    |                 |          |                        |  |

|                   |                                             | $R_L = 8\Omega, C_B = 1.0\mu, f_{IN} = 1kHz$            |                 |          |                        |  |

|                   |                                             | Inputs Floating                                         | 67              |          | dB                     |  |

|                   |                                             | Inputs terminated with 10Ω                              | 45              |          | dB                     |  |

| X <sub>TALK</sub> | Channel Separation                          | $f = 1kHz$ , $C_B = 1.0\mu F$                           | 90              |          | dB                     |  |

| SNR               | Signal To Noise Ratio                       | $V_{DD} = 5V$ , $P_O = 1W$ , $R_L = 8\Omega$            | 98              |          | dB                     |  |

### **LDO Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $V_{IN} = V_O$  +0.5V (Note 10),  $V_{\overline{SHDN}} = V_{IN}$ ,  $C_{IN} = C_{OUT} = 2.2 \mu F$ ,  $C_{CC} = 33 n F$ ,  $T_J = 25$ °C. **Boldface** limits apply for the operating temperature extremes: -40°C and 85°C.

| Symbol          | Parameter     | Conditions | Min<br>(Note 7) | Typ<br>(Note 6) | Max<br>(Note 7) | Units |

|-----------------|---------------|------------|-----------------|-----------------|-----------------|-------|

| V <sub>IN</sub> | Input Voltage |            | 2.5             | (Note 6)        | 6.0             | V     |

### LDO Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for  $V_{IN} = V_O + 0.5V$  (Note 10),  $V_{\overline{SHDN}} = V_{IN}$ ,  $C_{IN} = C_{OUT} = 2.2\mu F$ ,  $C_{CC} = 33n F$ ,  $T_J = 25^{\circ}C$ . **Boldface** limits apply for the operating temperature extremes:  $-40^{\circ}C$  and  $85^{\circ}C$ .

| Symbol             | Parameter                    | Conditions                                                                     | Min<br>(Note 7) | Typ<br>(Note 6) | Max<br>(Note 7) | Units                  |

|--------------------|------------------------------|--------------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------------|

|                    |                              | 100μA ≤ I <sub>OUT</sub> ≤ 300mA                                               | -2.4            | (Note 6)        | +2.4            | -                      |

| $\Delta V_{O}$     | Output Voltage Tolerance     | $V_{IN} = V_O + 0.5V \text{ (Note 7)}$                                         | -2.4            |                 | +2.4            | % of                   |

| Δνο                | Output Vollage Tolerance     | SET = OUT                                                                      | -3              |                 | +3              | V <sub>OUT (NOM)</sub> |

| Vo                 | Output Adjust Range          |                                                                                | 1.25            |                 | 6               | V                      |

| Io                 | Maximum Output Current       | Average DC Current Rating                                                      | 300             |                 |                 | mA                     |

| I <sub>LIMIT</sub> | Output Current Limit         |                                                                                | 330             | 770             |                 | mA                     |

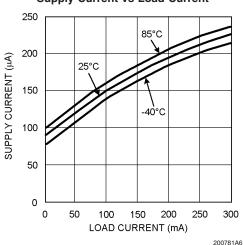

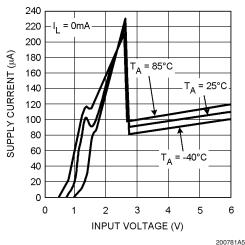

| IQ                 | Supply Current               | I <sub>OUT</sub> = 0mA                                                         |                 | 90              | 270             |                        |

|                    |                              | I <sub>OUT</sub> = 300mA                                                       |                 | 225             |                 | μA                     |

|                    | Shutdown Supply Current      | $V_O = 0V, \overline{SHDN} = GND$                                              |                 | 0.001           | 1               | μΑ                     |

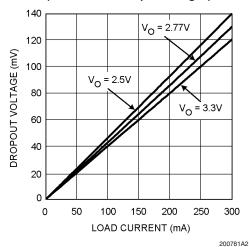

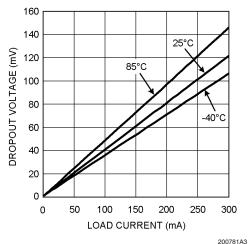

| $V_{DO}$           | Dropout Voltage              | I <sub>OUT</sub> = 1mA                                                         |                 | 0.4             |                 |                        |

|                    | (Note 10), (Note 11)         | I <sub>OUT</sub> = 200mA                                                       |                 | 80              | 220             | mV                     |

|                    |                              | I <sub>OUT</sub> = 300mA                                                       |                 | 120             |                 | 1                      |

| $\Delta V_{O}$     | Line Regulation              | $I_{OUT} = 1 \text{mA}, (V_O + 0.5 \text{V}) \le V_I \le 6 \text{V}$ (Note 10) | -0.1            | 0.01            | 0.1             | %/V                    |

|                    | Load Regulation              | $100\mu\text{A} \le I_{\text{OUT}} \le 300\text{mA}$                           |                 | 0.002           |                 | %/mA                   |

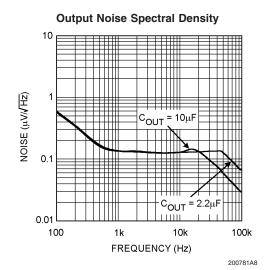

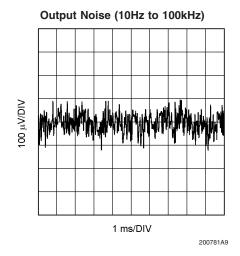

| e <sub>n</sub>     | Output Voltage Noise         | $I_{OUT} = 10$ mA, $10$ Hz $\leq f \leq 100$ kHz                               |                 | 37              |                 | μV <sub>RMS</sub>      |

|                    | Output Voltage Noise Density | $10$ Hz $\leq$ f $\leq$ $100$ kHz, $C_{OUT} = 10$ $\mu$ F                      |                 | 190             |                 | nV/ √Hz                |

| V <sub>SHDN</sub>  | SHDN Input Threshold         | $V_{IH}$ , $(V_O + 0.5V) \le V_I \le 6V$<br>(Note 10)                          | 2               |                 |                 | V                      |

|                    |                              | $V_{IL}, (V_O + 0.5V) \le V_I \le 6V$                                          |                 |                 | 0.4             | 1                      |

| I <sub>SHDN</sub>  | SHDN Input Bias Current      | SHDN = GND or IN                                                               |                 | 0.1             | 100             | nA                     |

| I <sub>SET</sub>   | SET Input Leakage            | SET = 1.3V                                                                     |                 | 0.1             | 2.5             | nA                     |

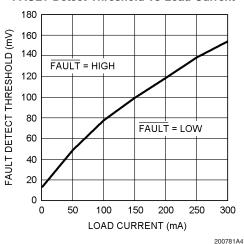

| V <sub>FAULT</sub> | FAULTDetection Voltage       | $V_O \ge 2.5V$ , $I_{OUT} = 200$ mA (Note 12)                                  |                 | 120             | 280             | mV                     |

|                    | FAULT Output Low Voltage     | I <sub>SINK</sub> = 2mA                                                        |                 | 0.115           | 0.25            | V                      |

| I <sub>FAULT</sub> | FAULT Off-Leakage Current    | FAULT = 3.6V, SHDN = 0V                                                        |                 | 0.1             | 100             | nA                     |

| T <sub>SD</sub>    | Thermal Shutdown             |                                                                                |                 | 160             |                 |                        |

|                    | Temperature                  |                                                                                |                 |                 |                 | °C                     |

|                    | Thermal Shutdown Hysteresis  |                                                                                |                 | 10              |                 | ]                      |

| T <sub>ON</sub>    | Start-Up Time                | $C_{OUT}$ = 10 $\mu$ F, $V_{O}$ at 90% of Final Value                          |                 | 120             |                 | μs                     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

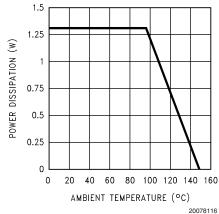

Note 2: The maximum power dissipation is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$  and must be derated at elevated temperatures. The maximum allowable power dissipation is  $P_{DMAX} = (T_{JMAX} - T_A)/\theta_{JA}$ . For the LM4817,  $T_{JMAX} = 150^{\circ}C$ . The  $\theta_{JA}$  for the LM4817 in the 28-pin MXA28A package, when board mounted and its DAP is soldered to a 2in<sup>2</sup> copper heatsink plane, is 41°C/W.

- Note 3: Human body model, 100pF discharged through a  $1.5k\Omega$  resistor.

- Note 4: Machine model, 220pF-240pF discharged through all pins.

- Note 5: All voltages are measured with respect to the ground (GND) pins unless otherwise specified.

- Note 6: Typicals are measured at 25°C and represent the parametric norm.

- Note 7: Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

- Note 8: The quiescent power supply current depends on the offset voltage when a practical load is connected to the amplifier.

- Note 9: Output power is measured at the device terminals.

- Note 10: Condition does not apply to input voltages below 2.5V since this is the minimum input operating voltage.

- Note 11: Dropout voltage is measured by reducing V<sub>IN</sub> until V<sub>O</sub> drops 100mV from its nominal value at V<sub>IN</sub> -V<sub>O</sub> = 0.5V. Dropout Voltage does not apply to the 1.8 version.

- Note 12: The FAULT detection voltage is specified for the input to output voltage differential at which the FAULT pin goes active low.

# **Stereo Amplifier Typical Performance Characteristics**

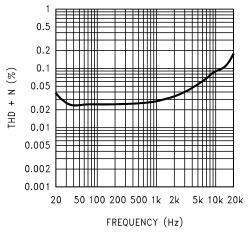

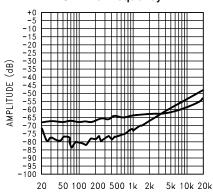

## THD+N vs Frequency

$V_{DD} = 3V, R_{L} = 8\Omega, P_{OUT} = 150mW$

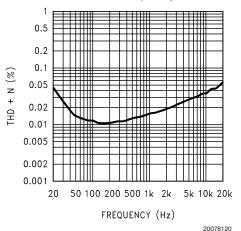

### THD+N vs Frequency

$V_{DD}$  = 5.5V,  $R_L$  = 8 $\Omega$ ,  $P_{OUT}$  = 150mW

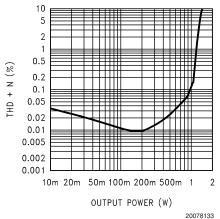

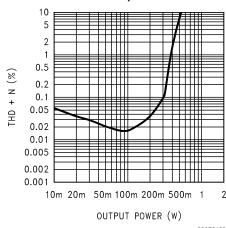

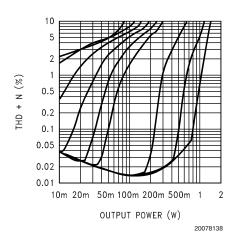

### THD+N vs Output Power

$V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ ,  $f_{IN}$  = 1kHz

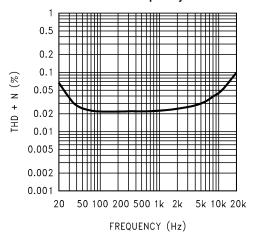

### THD+N vs Frequency

$V_{DD} = 5V$ ,  $R_L = 8\Omega$ ,  $P_{OUT} = 150$ mW

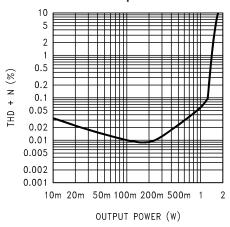

### THD+N vs Output Power

$V_{DD}$  = 3V,  $R_L$  =  $8\Omega$ ,  $f_{IN}$  = 1kHz

### THD+N vs Output Power

2007813

$V_{DD}$  = 5.5V,  $R_L$  = 8 $\Omega$ ,  $f_{IN}$  = 1kHz

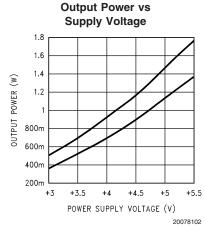

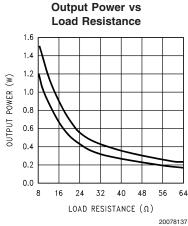

# Stereo Amplifier Typical Performance Characteristics (Continued)

$\rm R_L$  = 8 $\Omega,\,f_{\rm IN}$  = 1kHz, at (from top to bottom at 4.5V): THD+N = 10%, THD+N = 1%

R<sub>L</sub> = 8 $\Omega$ , f<sub>IN</sub> = 1kHz, at (from top to bottom at 24 $\Omega$ ): THD+N = 10%, THD+N = 1%

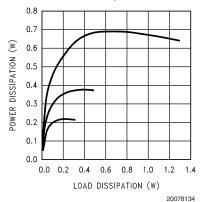

### Power Dissipation vs Load Dissipation

$V_{DD}$  = 5V,  $f_{IN}$  = 1kHz, at (from top to bottom at 0.2W):  $R_L$  = 8 $\Omega,~R_L$  = 16 $\Omega,~R_L$  = 32 $\Omega$

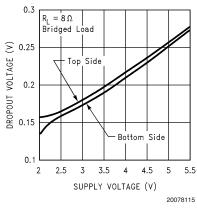

## Dropout Voltage vs Supply Voltage

### **Power Derating Curve**

$V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ ,  $f_{IN}$  = 1kHz  $2in^2$  copper heatsink area

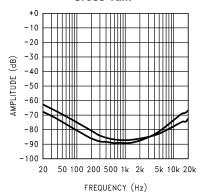

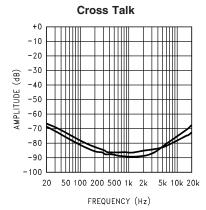

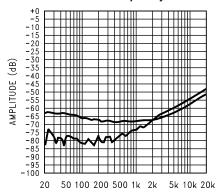

### **Cross Talk**

20078104

$V_{DD}$  = 3V,  $R_L$  = 8 $\Omega$ ,  $P_{OUT}$ = 150mW, at (from top to bottom at 2kHz):

-IN A driven,  $V_{\rm OUTB}$  measured; -IN B driven,  $V_{\rm OUTA}$  measured

# Stereo Amplifier Typical Performance Characteristics (Continued)

20078107

$V_{DD}$  = 5V,  $R_L$  = 8 $\Omega$ ,  $P_{OUT}$ = 150mW, at (from top to bottom at 2kHz):

-IN A driven,  $V_{\rm OUTB}$  measured;

-IN B driven, V<sub>OUTA</sub> measured

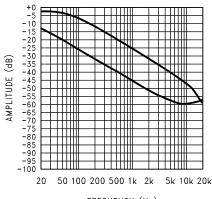

### **PSRR** vs Frequency

FREQUENCY (Hz)

$$\begin{split} &V_{DD}=3V,\,R_L=8\Omega,\,R_{SOURCE}=10\Omega,\\ &V_{RIPPLE}=200mVP\text{-P},\,at\,(from\,\,top\,\,to\,\,bottom\,\,at\,\,500Hz):}\\ &C_{BYPASS}=0.1\mu\text{F},\,C_{BYPASS}=1.0\mu\text{F} \end{split}$$

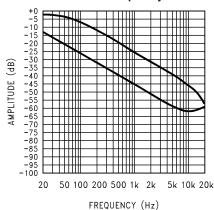

### **PSRR** vs Frequency

2007811

$$\begin{split} &\textbf{V}_{\text{DD}} = 5\text{V}, \ \textbf{R}_{\text{L}} = 8\Omega, \ \textbf{R}_{\text{SOURCE}} = 10\Omega, \\ \textbf{V}_{\text{RIPPLE}} = 200\text{mV}_{\text{P-P}}, \ \text{at (from top to bottom at 500Hz):} \\ \textbf{C}_{\text{BYPASS}} = 0.1\mu\text{F}, \ \textbf{C}_{\text{BYPASS}} = 1.0\mu\text{F} \end{split}$$

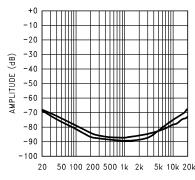

### **Cross Talk**

FREQUENCY (Hz)

$V_{DD}$  = 5.5V,  $R_L$  =  $8\Omega$ ,  $P_{OUT}$ = 150mW, at (from top to bottom at 2kHz):

-IN A driven,  $V_{\text{OUTB}}$  measured;

-IN B driven, V<sub>OUTA</sub> measured

### **PSRR** vs Frequency

FREQUENCY (Hz)

$$\begin{split} V_{DD} &= 3V, \ R_L = 8\Omega, \ R_{SOURCE} = \infty, \\ V_{RIPPLE} &= 200 mV_{P-P}, \ at \ (from \ top \ to \ bottom \ at \ 500 Hz): \\ C_{BYPASS} &= 0.1 \mu F, \ C_{BYPASS} = 1.0 \mu F \end{split}$$

### **PSRR vs Frequency**

FREQUENCY (Hz)

$$\begin{split} V_{DD} &= 5\text{V}, \text{ R}_{L} = 8\Omega, \text{ R}_{SOURCE} = ^{\infty}, \\ V_{RIPPLE} &= 200\text{mV}_{P-P}, \text{ at (from top to bottom at 500Hz):} \\ C_{BYPASS} &= 0.1\mu\text{F}, \text{ C}_{BYPASS} = 1.0\mu\text{F} \end{split}$$

# Stereo Amplifier Typical Performance Characteristics (Continued)

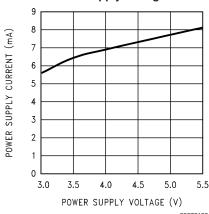

### Power Supply Current vs Power Supply Voltage

$R_L = \infty$ ,  $R_{SOURCE} = 50\Omega$ ,  $V_{IN} = 0V$

### THD+N vs Output Power

$$\begin{split} V_{DD} &= 5V, \ R_L = 8\Omega, \ f_{IN} = 1 kHz, \\ &\text{at (from left to right at 7% THD+N):} \\ V_{LIM} &= 2V, \ 1.9V, \ 1.8V, \ 1.7V, \ 1.6V, \ 1.5V, \ 1.0V, \ 0.5V, \ 0V \end{split}$$

# $\textbf{LDO Typical Performance Characteristics} \quad \text{Unless otherwise specified, V}_{\text{IN}} = \text{V}_{\text{OUT}} + 0.5 \text{V}, \ \text{C}_{\text{IN}} = \text{C}_{\text{OUT}} = 2.2 \mu\text{F}, \ \text{C}_{\text{CC}} = 33 \text{nF}, \ \text{T}_{\text{J}} = 25 \,^{\circ}\text{C}, \ \text{V}_{\overline{\text{SHDN}}} = \text{V}_{\text{IN}}.$

### **Dropout Voltage vs Load Current** (For Different Output Voltages)

### **FAULT** Detect Threshold vs Load Current

### **Supply Current vs Load Current**

### **Dropout Voltage vs Load Current** (For Different Output Temperatures)

### Supply Current vs Input Voltage

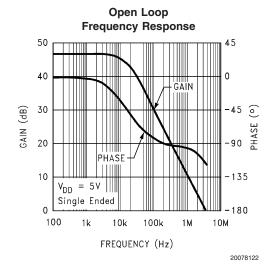

### Power Supply Rejection Ratio vs Frequency

200781A7

# **LDO Typical Performance Characteristics** Unless otherwise specified, $V_{IN} = V_{OUT} + 0.5V$ , $C_{IN} = C_{OUT} = 2.2 \mu F$ , $C_{CC} = 33 n F$ , $T_J = 25 ° C$ , $V_{\overline{SHDN}} = V_{IN}$ . (Continued)

1k

FREQUENCY (Hz)

10k

100k

o l

10

100

# $\textbf{LDO Typical Performance Characteristics} \text{ Unless otherwise specified, } V_{\text{IN}} = V_{\text{OUT}} + 0.5\text{V}, \text{ } C_{\text{IN}} = C_{\text{OUT}} = 2.2\mu\text{F}, \text{ } C_{\text{CC}} = 33\text{nF}, \text{ } T_{\text{J}} = 25^{\circ}\text{C}, \text{ } V_{\overline{\text{SHDN}}} = V_{\text{IN}}. \text{ } \text{ } \text{(Continued)}$

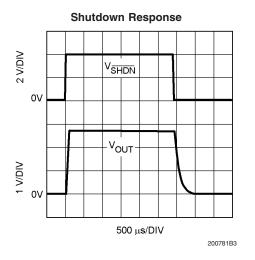

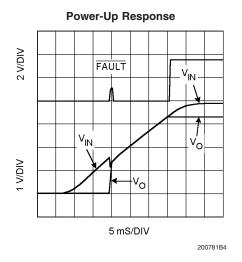

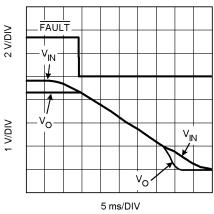

# **Power-Down Response**

200781B5

# **External Components Description**

(Refer to Figure 1).

| Components |                | Functional Description                                                                                                                                                                                                                                                                            |  |  |

|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.         | R <sub>i</sub> | The Inverting input resistance, along with $R_f$ , set the closed-loop gain. $R_i$ , along with $C_i$ , form a high pass filter with $f_c = 1/(2\pi R_i C_i)$ .                                                                                                                                   |  |  |

| 2.         | C <sub>i</sub> | The input coupling capacitor blocks DC voltage at the amplifier's input terminals. $C_i$ , along with $R_i$ , create a highpass filter with $f_c = 1/(2\pi R_i C_i)$ . Refer to the section, <b>SELECTING PROPER EXTERNAL COMPONENTS</b> , for an explanation of determining the value of $C_i$ . |  |  |

| 3.         | R <sub>f</sub> | The feedback resistance, along with R <sub>i</sub> , set the closed-loop gain.                                                                                                                                                                                                                    |  |  |

| 4.         | C <sub>s</sub> | The supply bypass capacitor. Refer to the <b>POWER SUPPLY BYPASSING</b> section for information about properly placing, and selecting the value of, this capacitor.                                                                                                                               |  |  |

| 5.         | Св             | The capacitor, C <sub>B</sub> , filters the half-supply voltage present on the BYPASS pin. Refer to the <b>SELECTING PROPER EXTERNAL COMPONENTS</b> section for information concerning proper placement and selecting C <sub>B</sub> 's value.                                                    |  |  |

| 6.         | R <sub>1</sub> | Combined with $R_2$ , sets the LDO's output voltage according to the following equation:<br>$R_1 = R_2 ((V_{OUT} / 1.25V) -1)$                                                                                                                                                                    |  |  |

| 7.         | R <sub>2</sub> | Combined with $R_1$ , sets the LDO's output voltage according to the following equation: $R_2 = (1.25 \text{V x } R_1) \ / \ (\text{V}_{\text{OUT}} - 1.25 \text{V})$                                                                                                                             |  |  |

# **Application Information**

### **BRIDGE CONFIGURATION EXPLANATION**

<sup>\*</sup> Refer to the section Proper Selection of External Components, for a detailed discussion of C<sub>B</sub> size.

FIGURE 1. Typical Audio Amplifier Application Circuit

Pin out shown for the LLP package. Refer to the Connection Diagrams for the pinout of the TSSOP package.

As shown in *Figure 1*, the LM4817 consists of two pairs of operational amplifiers, forming a two-channel (channel A and channel B) stereo amplifier. (Though the following discusses channel A, it applies equally to channel B.) External resistors  $R_{\rm f}$  and  $R_{\rm i}$  set the closed-loop gain of Amp1A, whereas two internal  $20k\Omega$  resistors set Amp2A's gain at -1. The LM4817 drives a load, such as a speaker, connected between the two amplifier outputs, -OUTA and +OUTA.

Figure 1 shows that Amp1A's output serves as Amp2A's input. This results in both amplifiers producing signals identical in magnitude, but 180° out of phase. Taking advantage of this phase difference, a load is placed between -OUTA and +OUTA and driven differentially (commonly referred to as "bridge mode"). This results in a differential gain of

$$A_{VD} = 2 x (R_f / R_i)$$

(1)

Bridge mode amplifiers are different from single-ended amplifiers that drive loads connected between a single amplifier's output and ground. For a given supply voltage, bridge mode has a distinct advantage over the single-ended configuration: its differential output doubles the voltage swing across the load. This produces four times the output power when compared to a single-ended amplifier under the same conditions. This increase in attainable output power assumes that the amplifier is not current limited or that the

output signal is not clipped. To ensure minimum output signal clipping when choosing an amplifier's closed-loop gain, refer to the **Audio Power Amplifier Design** section.

Another advantage of the differential bridge output is no net DC voltage across the load. This is accomplished by biasing channel A's and channel B's outputs at half-supply. This eliminates the coupling capacitor that single supply, single-ended amplifiers require. Eliminating an output coupling capacitor in a single-ended configuration forces a single-supply amplifier's half-supply bias voltage across the load. This increases internal IC power dissipation and may permanently damage loads such as speakers.

### POWER DISSIPATION

Power dissipation is a major concern when designing a successful single-ended or bridged amplifier. Equation (2) states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified output load

$$P_{DMAX} = (V_{DD})^2 / (2\pi^2 R_L) \text{ Single-Ended}$$

(2)

However, a direct consequence of the increased power delivered to the load by a bridge amplifier is higher internal power dissipation for the same conditions.

The LM4817 has two operational amplifiers per channel. The maximum internal power dissipation per channel operating in the bridge mode is four times that of a single-ended amplifier. From Equation (3), assuming a 5V power supply and an  $8\Omega$  load, the maximum single channel power dissipation is 0.633W or 1.27W for stereo operation.

$$P_{DMAX} = 4 \times (V_{DD})^2 / (2\pi^2 R_L) \text{ Bridge Mode}$$

(3)

The LM4817's power dissipation is twice that given by Equation (2) or Equation (3) when operating in the single-ended mode or bridge mode, respectively. Twice the maximum power dissipation point given by Equation (3) must not exceed the power dissipation given by Equation (4):

$$P_{DMAX}' = (T_{JMAX} - T_A) / \theta_{JA}$$

(4)

The LM4817's  $T_{JMAX}=150^{\circ}C$ . In the MH package soldered to a DAP pad that expands to a copper area of  $2\text{in}^2$  on a PCB , the LM4817's  $\theta_{JA}$  is 41°C/W. At any given ambient temperature  $T_{JVA}$ , use Equation (4) to find the maximum internal power dissipation supported by the IC packaging. Rearranging Equation (4) and substituting  $P_{DMAX}$  for  $P_{DMAX}$ ' results in Equation (5). This equation gives the maximum ambient temperature that still allows maximum stereo power dissipation without violating the LM4817's maximum junction temperature.

$$T_A = T_{JMAX} - 2 \times P_{DMAX} \theta_{JA}$$

(5)

For a typical application with a 5V power supply and an  $8\Omega$  load, the maximum ambient temperature that allows maximum stereo power dissipation without exceeding the maximum junction temperature is approximately 98°C for the MH package.

$$T_{\text{JMAX}} = P_{\text{DMAX}} \theta_{\text{JA}} + T_{\text{A}} \tag{6}$$

Equation (6) gives the maximum junction temperature  $T_{J^-}$  MAX. If the result violates the LM4817's 150°C, reduce the maximum junction temperature by reducing the power supply voltage or increasing the load resistance. Further allowance should be made for increased ambient temperatures.

The above examples assume that a device is a surface mount part operating around the maximum power dissipation point. Since internal power dissipation is a function of output power, higher ambient temperatures are allowed as output power or duty cycle decreases.

If twice the value given by Equation (3) exceeds the result of Equation (4), then decrease the supply voltage, increase the load impedance, or reduce the ambient temperature. If these measures are insufficient, a heat sink can be added to reduce  $\theta_{JA}.$  The heat sink can be created using additional copper area around the package, with connections to the ground pin(s), supply pin and amplifier output pins. External, solder attached SMT heatsinks such as the Thermalloy 7106D can also improve power dissipation. When adding a heat sink, the  $\theta_{JA}$  is the sum of  $\theta_{JC},\,\theta_{CS},\,$  and  $\theta_{SA}.\,(\theta_{JC}$  is the junction–to–case thermal impedance,  $_{CS}$  is the case–to–sink thermal impedance, and  $\theta_{SA}$  is the sink–to–ambient thermal impedance.) Refer to the Typical Performance Characteristics curves for power dissipation information at lower output power levels.

### **OUTPUT VOLTAGE LIMITER**

The LM4817's adjustable output voltage limiter can be used to set a maximum and minimum output voltage swing magnitude. The voltage applied to the  $V_{LIM}$  input (pin 28) controls the amount voltage limit magnitude.

Without the limiter's influence ( $V_{LIM} = 0V$ ), the LM4817's maximum BTL output swing is nominally

$$2 \times V_{DD}$$

When the limiter input voltage is greater than 0V, the BTL output voltage swing is

$$V_{OUT-BTL} = (2 \times V_{DD}) - (4 \times V_{LIM})$$

For any given value of  $V_{\text{LIM}}$ , the actual output swing will be limited to within  $\pm 200 \text{mV}$ .

### **POWER SUPPLY BYPASSING**

As with any power amplifier, proper supply bypassing is critical for low noise performance and high power supply rejection. Applications that employ a 5V regulator typically use a 10µF in parallel with a 0.1µF filter capacitors to stabilize the regulator's output, reduce noise on the supply line, and improve the supply's transient response. However, their presence does not eliminate the need for a local 1.0µF tantalum bypass capacitance connected between the LM4817's supply pins and ground. Do not substitute a ceramic capacitor for the tantalum. Doing so may cause oscillation in the output signal. Keep the length of leads and traces that connect capacitors between the LM4817's power supply pin and ground as short as possible. Connecting a 1μF capacitor, C<sub>B</sub>, between the BYPASS pin and ground improves the internal bias voltage's stability and improves the amplifier's PSRR. The PSRR improvements increase as the bypass pin capacitor value increases. Too large, however, increases turn-on time and can compromise amplifier's click and pop performance. The selection of bypass capacitor values, especially C<sub>B</sub>, depends on desired PSRR requirements, click and pop performance (as explained in the section, Proper Selection of External Components), system cost, and size constraints.

### **MICRO-POWER SHUTDOWN**

The voltage applied to the SHUTDOWN pin controls the LM4817's shutdown function. Activate micro-power shutdown by applying  $V_{\rm DD}$  to the SHUTDOWN pin. When active, the LM4817's micro-power shutdown feature turns off the amplifier's bias circuitry, reducing the supply current. The logic threshold is typically  $V_{\rm DD}/2$ . The low 0.7µA typical shutdown current is achieved by applying a voltage that is as near as  $V_{\rm DD}$  as possible to the SHUTDOWN pin. A voltage thrat is less than  $V_{\rm DD}$  may increase the shutdown current.

There are a few ways to control the micro-power shutdown. These include using a single-pole, single-throw switch, a microprocessor, or a microcontroller. When using a switch, connect an external  $10 k\Omega$  pull-up resistor between the SHUTDOWN pin and  $V_{\rm DD}$ . Connect the switch between the SHUTDOWN pin and ground. Select normal amplifier operation by closing the switch. Opening the switch connects the SHUTDOWN pin to  $V_{\rm DD}$  through the pull-up resistor, activating micro-power shutdown. The switch and resistor guarantee that the SHUTDOWN pin will not float. This prevents unwanted state changes. In a system with a microprocessor or a microcontroller, use a digital output to apply the control voltage to the SHUTDOWN pin. Driving the SHUTDOWN pin with active circuitry eliminates the pull up resistor.

TABLE 1. LOGIC LEVEL TRUTH TABLE FOR SHUTDOWN OPERATION

| SHUTDOWN | OPERATIONAL MODE       |

|----------|------------------------|

| Low      | Full power, stereo BTL |

|          | amplifiers             |

| High     | Micro-power Shutdown   |

### SELECTING PROPER EXTERNAL COMPONENTS

Optimizing the LM4817's performance requires properly selecting external components. Though the LM4817 operates well when using external components with wide tolerances, best performance is achieved by optimizing component values.

The LM4817 is unity-gain stable, giving a designer maximum design flexibility. The gain should be set to no more than a given application requires. This allows the amplifier to achieve minimum THD+N and maximum signal-to-noise ratio. These parameters are compromised as the closed-loop gain increases. However, low gain demands input signals with greater voltage swings to achieve maximum output power. Fortunately, many signal sources such as audio CODECs have outputs of 1V<sub>RMS</sub> (2.83V<sub>P-P</sub>). Please refer to the **Audio Power Amplifier Design** section for more information on selecting the proper gain.

### Input Capacitor Value Selection

Amplifying the lowest audio frequencies requires high value input coupling capacitor ( $C_i$  in *Figure 1*). A high value capacitor can be expensive and may compromise space efficiency in portable designs. In many cases, however, the speakers used in portable systems, whether internal or external, have little ability to reproduce signals below 150Hz. Applications using speakers with this limited frequency response reap little improvement by using large input capacitor.

Besides effecting system cost and size,  $C_i$  has an affect on the LM4817's click and pop performance. When the supply voltage is first applied, a transient (pop) is created as the charge on the input capacitor changes from zero to a quiescent state. The magnitude of the pop is directly proportional to the input capacitor's size. Higher value capacitors need more time to reach a quiescent DC voltage (usually  $V_{\rm DD}/2$ ) when charged with a fixed current. The amplifier's output charges the input capacitor through the feedback resistor,  $R_{\rm f}$ . Thus, pops can be minimized by selecting an input capacitor value that is no higher than necessary to meet the desired -3dB frequency.

A shown in *Figure 1*, the input resistor  $(R_1)$  and the input capacitor,  $C_1$  produce a –3dB high pass filter cutoff frequency that is found using Equation (7).

$$f_{-3 dB} = \frac{1}{2\pi R_{1N} C_1}$$

(7)

As an example when using a speaker with a low frequency limit of 150Hz,  $C_I$ , using Equation (4), is  $0.063\mu F$ . The  $1.0\mu F$   $C_I$  shown in *Figure 1* allows the LM4817 to drive high efficiency, full range speaker whose response extends below 30Hz.

### **Bypass Capacitor Value Selection**

Besides minimizing the input capacitor size, careful consideration should be paid to value of  $C_{\text{B}}$ , the capacitor connected to the BYPASS pin. Since  $C_{\text{B}}$  determines how fast

the LM4817 settles to quiescent operation, its value is critical when minimizing turn–on pops. The slower the LM4817's outputs ramp to their quiescent DC voltage (nominally 1/2  $V_{\rm DD}$ ), the smaller the turn–on pop. Choosing  $C_{\rm B}$  equal to 1.0µF along with a small value of  $C_{\rm i}$  (in the range of 0.1µF to 0.39µF), produces a click-less and pop-less shutdown function. As discussed above, choosing  $C_{\rm i}$  no larger than necessary for the desired bandwidth helps minimize clicks and pops.

# OPTIMIZING CLICK AND POP REDUCTION PERFORMANCE

The LM4817 contains circuitry to minimize turn-on and shutdown transients or "clicks and pop". For this discussion, turn-on refers to either applying the power supply voltage or when the shutdown mode is deactivated. While the power supply is ramping to its final value, the LM4817's internal amplifiers are configured as unity gain buffers. An internal current source changes the voltage of the BYPASS pin in a controlled, linear manner. Ideally, the input and outputs track the voltage applied to the BYPASS pin. The gain of the internal amplifiers remains unity until the voltage on the bypass pin reaches 1/2 V<sub>DD</sub>. As soon as the voltage on the BYPASS pin is stable, the device becomes fully operational. Although the bypass pin current cannot be modified, changing the size of C<sub>B</sub> alters the device's turn-on time and the magnitude of "clicks and pops". Increasing the value of CB reduces the magnitude of turn-on pops. However, this presents a tradeoff: as the size of  $C_{\mbox{\scriptsize B}}$  increases, the turn-on time increases. There is a linear relationship between the size of C<sub>B</sub> and the turn-on time. Here are some typical turn-on times for various values of C<sub>B</sub>:

| Св     | T <sub>ON</sub> |

|--------|-----------------|

| 0.01µF | 20 ms           |

| 0.1µF  | 200 ms          |

| 0.22µF | 440 ms          |

| 0.47µF | 940 ms          |

| 1.0µF  | 2 Sec           |

In order eliminate "clicks and pops", all capacitors must be discharged before turn-on. Rapidly switching  $V_{\rm DD}$  may not allow the capacitors to fully discharge, which may cause "clicks and pops".

### **NO LOAD STABILITY**

The LM4817 may exhibit low level oscillation when the load resistance is greater than  $10k\Omega$ . This oscillation only occurs as the output signal swings near the supply voltages. Prevent this oscillation by connecting a  $5k\Omega$  between the output pins and ground.

### **AUDIO POWER AMPLIFIER DESIGN**

### Audio Amplifier Design: Driving 1W into an 8 $\Omega$ Load

The following are the desired operational parameters:

Power Output:  $1W_{RMS}$  Load Impedance:  $8\Omega$  Input Level:  $1V_{RMS}$  Input Impedance:  $20k\Omega$  Bandwidth:  $100Hz-20~kHz~\pm~0.25~dB$

The design begins by specifying the minimum supply voltage necessary to obtain the specified output power. One way to find the minimum supply voltage is to use the Output Power vs Supply Voltage curve in the **Typical Performance Characteristics** section. Another way, using Equation (4), is to calculate the peak output voltage necessary to achieve the desired output power for a given load impedance. To account for the amplifier's dropout voltage, two additional voltages, based on the Dropout Voltage vs Supply Voltage in the **Typical Performance Characteristics** curves, must be added to the result obtained by Equation (8). The result in Equation (9).

$$V_{opeak} = \sqrt{(2R_L P_O)}$$

(8)

$$V_{DD} \ge (V_{OUTPEAK} + (V_{OD_{TOP}} + V_{OD_{BOT}}))$$

(9)

The Output Power vs Supply Voltage graph for an  $8\Omega$  load indicates a minimum supply voltage of 4.6V. This is easily met by the commonly used 5V supply voltage. The additional voltage creates the benefit of headroom, allowing the LM4817 to produce peak output power in excess of 1W without clipping or other audible distortion. The choice of supply voltage must also not create a situation that violates maximum power dissipation as explained above in the **Power Dissipation** section.

After satisfying the LM4817's power dissipation requirements, the minimum differential gain is found using Equation (10).

$$A_{VD} \ge \sqrt{(P_O R_L)}/(V_{IN}) = V_{orms}/V_{inrms}$$

(10)

Thus, a minimum gain of 2.83 allows the LM4817's to reach full output swing and maintain low noise and THD+N performance. For this example, let  $A_{VD}=3$ .

The amplifier's overall gain is set using the input  $(R_i)$  and feedback  $(R_f)$  resistors. With the desired input impedance set at  $20k\Omega$ , the feedback resistor is found using Equation (11).

$$R_f/R_i = A_{VD}/2 \tag{11}$$

The value of  $R_f$  is  $30k\Omega$ .

The last step in this design example is setting the amplifier's -3dB frequency bandwidth. To achieve the desired  $\pm 0.25dB$  pass band magnitude variation limit, the low frequency response must extend to at least one–fifth the lower bandwidth limit and the high frequency response must extend to at least five times the upper bandwidth limit. The gain variation for both response limits is 0.17dB, well within the  $\pm 0.25dB$  desired limit. The results are an

$$f_L = 100Hz/5 = 20Hz$$

(12)

and an

$$F_{H} = 20kHzx5 = 100kHz \tag{13}$$

As mentioned in the **External Components** section,  $R_i$  and  $C_i$  create a highpass filter that sets the amplifier's lower bandpass frequency limit. Find the coupling capacitor's value using Equation (14).

$$C_{i} \geq \frac{1}{2\pi R_{i} f_{C}}$$

$$\tag{14}$$

the result is

$$1/(2\pi^*20k\Omega^*20Hz) = 0.398\mu F$$

(15)

Use a 0.39µF capacitor, the closest standard value.

The product of the desired high frequency cutoff (100kHz in this example) and the differential gain,  $A_{VD}$ , determines the upper passband response limit. With  $A_{VD}=3$  and  $f_{H}=100\text{kHz}$ , the closed-loop gain bandwidth product (GBWP) is 300kHz. This is less than the LM4817's 3.5MHz GBWP. With this margin, the amplifier can be used in designs that require more differential gain while avoiding performance-lrestricting bandwidth limitations.

#### **LDO General Information**

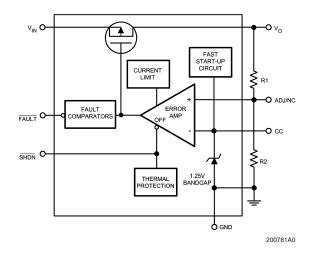

Figure 2 shows the LM4817's LDO functional block diagram. A 1.25V bandgap reference, an error amplifier and a PMOS pass transistor perform voltage regulation while being supported by shutdown, fault, and the usual Temperature and current protection circuitry

The regulator's topology is the classic type with negative feedback from the output to one of the inputs of the error amplifier. Feedback resistors  $\rm R_1$  and  $\rm R_2$  are either internal or external to the IC, depending on whether it is the fixed voltage version or the adjustable version. The negative feedback and high open loop gain of the error amplifier cause the two inputs of the error amplifier to be virtually equal in voltage. If the output voltage changes due to load changes, the error amplifier provides the appropriate drive to the pass transistor to maintain the error amplifier's inputs as virtually equal. In short, the error amplifier keeps the output voltage constant in order to keep its inputs equal.

FIGURE 2. LDO Functional Block Diagram

### **Output Voltage Setting**

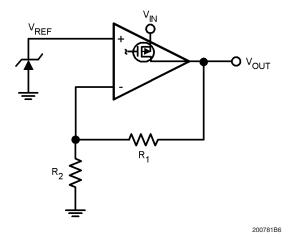

The output voltage is set according to the amount of negative feedback (Note that the pass transistor inverts the feedback signal). Figure 3 simplifies the LDO's topology. This

type of regulator can be represented as an op amp configured as non-inverting amplifier and a fixed DC Voltage  $(V_{\rm REF})$  for its input signal. The special characteristic of this op amp is its extra-large output transistor that only sources current. In terms of its non-inverting configuration, the output voltage equals  $V_{\rm REF}$  times the closed loop gain:

$$V_O = V_{REF} \left[ \frac{R_1}{R_2} + 1 \right]$$

Utilize the following equation for adjusting the output to a particular voltage:

$$R_1 = R_2 \left[ \frac{V_0}{1.25V} - 1 \right]$$

Choose  $R_2$  = 100k to optimize accuracy, power supply rejection, noise and power consumption.

FIGURE 3. Regulator Topology Simplified

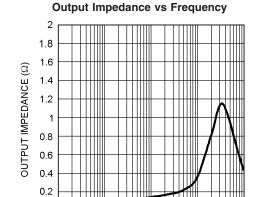

Similarity in the output capabilities exists between op amps and linear regulators. Just as rail-to-rail output op amps allow their output voltage to approach the supply voltage, low dropout regulators (LDOs) allow their output voltage to operate close to the input voltage. Both achieve this by the configuration of their output transistors. Standard op amps and regulator outputs are at the source (or emitter) of the output transistor. Rail-to-rail op amp and LDO regulator outputs are at the drain (or collector) of the output transistor. This replaces the threshold (or diode drop) limitations on the output with the less restrictive source-to-drain (or V<sub>SAT</sub>) limitations. There is a trade-off, of course. The output impedance become significantly higher, thus providing a critically lower pole when combined with the capacitive load. That's why rail-to-rail op amps are usually poor at driving capacitive loads and recommend a series output resistor when doing so. LDOs require the same series resistance except that the internal resistance of the output capacitor will usually suffice. Refer to the output capacitance section for more information.

### **Output Capacitance**

The LDO is specifically designed to employ ceramic output capacitors as low as  $2.2\mu F$ . Ceramic capacitors below  $10\mu F$  offer significant cost and space savings, along with high

frequency noise filtering. Higher values and other types and of capacitor may be used, but their equivalent series resistance (ESR) should be maintained below  $0.5\Omega$

Ceramic capacitor of the value required by the LDO are available in the following dielectric types: Z5U, Y5V, X5R and X7R. The Z5U and Y5V types exhibit a 50% or more drop in capacitance value as their temperature increases from 25 $^{\circ}$ C, an important consideration. The X5R generally maintain their capacitance value within  $\pm 20\%$ . The X7R type are desirable for their tighter tolerance of 10% over temperature.

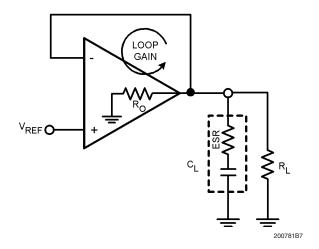

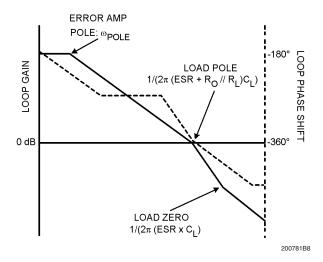

Ceramic capacitors pose a challenge because of their relatively low ESR. Like most other LDOs, the LDO relies on a zero in the frequency response to compensate against excessive phase shift in the regulator's feedback loop. If the phase shift reaches 360° (i.e.; becomes positive), the regulator will oscillate. This compensation usually resides in the zero generated by the combination of the output capacitor with its equivalent series resistance (ESR). The zero is intended to cancel the effects of the pole generated by the load capacitance (CL) combined with the parallel combination of the load resistance (RL) and the output resistance (R<sub>O</sub>) of the regulator. The challenge posed by low ESR capacitors is that the zero it generates can be too high in frequency for the pole that it's intended to compensate. The LM4817 overcomes this challenge by internally generating a strategically placed zero.

FIGURE 4. Simplified Model of Regulator Loop Gain Components

Figure 4 shows a basic model for the linear regulator that helps describe what happens to the output signal as it is processed through its feedback loop; that is, describe its loop gain (LG). The LG includes two main transfer functions: the error amplifier and the load. The error amplifier provides voltage gain and a dominant pole, while the load provides a zero and a pole. The LG of the model in Figure 3 is described by the following equation:

$$LG (j\omega) = \frac{A_O}{1 + j \left[\frac{\omega}{\omega_{POLE}}\right]} * \frac{1 + j\omega (ESR \times C_L)}{1 + j\omega ((ESR + R_O // R_L) C_L)}$$

The first term of the above equation expresses the voltage gain (numerator) and a single pole role-off (denominator) of

the error amplifier. The second term expresses the zero (numerator) and pole (denominator) of the load in combination with the  $R_{\rm O}$  of the regulator.

Figure 5 shows a Bode plot that represents a case where the zero contributed by the load is too high to cancel the effect of the pole contributed by the load and  $R_{\rm O}$ . The solid line illustrates the loop gain while the dashed line illustrates the corresponding phase shift. Notice that the phase shift at unity gain is a total  $360^{\circ}$  -the criteria for oscillation.

FIGURE 5. Loop Gain Bode Plot Illustrating Inadequately High Zero for Stability Compensation

The LDO generates an internal zero that makes up for the inadequately high zero of the low ESR ceramic output capacitor. This internally generated zero is strategically placed to provide positive phase shift near unity gain, thus providing a stable phase margin.

### **No-Load Stability**

The LM4817 remains stable during no-load conditions, a necessary feature for CMOS RAM keep-alive applications.

### **Input Capacitor**

The LM4817 requires a minimum input capacitance of about 1 $\mu$ F. The value may be increased indefinitely. The type is not critical to stability. However, instability may occur with bench set-ups where long supply leads are used, particularly at near dropout and high current conditions. This is attributed to the lead inductance coupling to the output through the gate oxide of the pass transistor; thus, forming a pseudo LCR network within the Loop-gain. A 10 $\mu$ F tantalum input capacitor remedies this non-situ condition; its larger ESR acts to dampen the pseudo LCR network. This may only be necessary for some bench setups.  $1\mu$ F ceramic input capacitor are fine for most end-use applications.

If a tantalum input capacitor is intended for the final application, it is important to consider their tendency to fail in short circuit mode, thus potentially damaging the part.

### **Noise Bypass Capacitor**

The noise bypass capacitor (CC) significantly reduces the LDO'soutput noise. Connect the CC capacitor between pin 6 and ground. The optimum value for CC is 33nF.

Pin 6 directly connects to the high impedance output of the bandgap. The DC leakage of the CC capacitor should be considered; loading down the reference will reduce the output voltage. NPO and COG ceramic capacitors typically offer very low leakage. Polypropylene and polycarbonate film carbonate capacitor offer even lower leakage currents.

CC does not affect the transient response; however, it does affect turn-on time. The smaller the CC value, the quicker the turn-on time.

### **Power Dissipation**

Power dissipation refers to the part's ability to radiate heat away from the silicon, with packaging being a key factor. A reasonable analogy is the packaging a human being might wear, a jacket for example. A jacket keeps a person comfortable on a cold day, but not so comfortable on a hot day. It would be even worse if the person was exerting power (exercising). This is because the jacket has resistance to heat flow to the outside ambient air, like the IC package has a thermal resistance from its junctions to the ambient  $(\theta_{\text{JA}})$ .  $\theta_{\text{JA}}$  has a unit of temperature per power and can be used to calculate the IC's junction temperature as follows:

$$T_J = \theta_{JA} (PD) + T_A$$

$T_J$  is the junction temperature of the IC.  $\theta_{JA}$  is the thermal resistance from the junction to the ambient air outside the package. PD is the power exerted by the IC, and  $T_A$  is the ambient temperature.

PD is calculated as follows:

$$PD = I_{OUT} (V_{IN} - V_{O})$$

$\theta_{JA}$  for the LM4817 package (MSOP-8) is 223°C/W with no forced air flow, 182°C/W with 225 linear feet per minute (LFPM) of air flow, 163°C/W with 500 LFPM of air flow, and 149°C/W with 900 LFPM of air flow.

$\theta_{JA}$  can also be decreased (improved) by considering the layout of the PC board: heavy traces (particularly at  $V_{IN}$  and the two  $V_{OUT}$  pins), large planes, through-holes, etc.

Improvements and absolute measurements of the  $\theta_{JA}$  can be estimated by utilizing the thermal shutdown circuitry that is internal to the IC. The thermal shutdown turns off the pass transistor of the device when its junction temperature reaches 160°C (Typical). The pass transistor doesn't turn on again until the junction temperature drops about 10°C (hysteresis).

Using the thermal shutdown circuit to estimate ,  $\theta_{JA}$  can be done as follows: With a low input to output voltage differential, set the load current to 300mA. Increase the input voltage until the thermal shutdown begins to cycle on and off. Then slowly decrease  $V_{IN}$  (100mV increments) until the part stays on. Record the resulting voltage differential  $(V_D)$  and use it in the following equation:

$$\theta_{JA} = \frac{(160 - T_A)}{(0.300 \times V_D)}$$

### **Fault Detection**

The LDO provides a FAULT pin that goes low during out of regulation conditions like current limit and thermal shutdown, or when it approaches dropout. The latter monitors the input-to-output voltage differential and compares it against a threshold that is slightly above the dropout voltage. This threshold also tracks the dropout voltage as it varies with load current. Refer to Fault Detect vs. Load Current curve in the typical characteristics section.

The  $\overline{\text{FAULT}}$  pin requires a pull-up resistor since it is an open-drain output. This resistor should be large in value to reduce energy drain. A 100k $\Omega$  pull-up resistor works well for most applications.

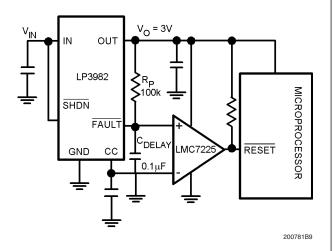

Figure 6 shows the LDO's with delay added to the FAULT pin for the reset pin of a microprocessor. The output of the comparator stays low for a preset amount of time after the regulator comes out of a fault condition.

FIGURE 6. Power on Delayed Reset Application

The delay time for the application of Figure 5 is set as follows:

$$C_{DELAY} = \frac{-t}{R_{P} ln \left[ 1 - \frac{V_{REF}}{V_{O}} \right]}$$

The application is set for a reset delay time of 8.8ms. Note that the comparator should have high impedance inputs so as to not load down the  $V_{\rm REF}$  at the CC pin of the LM4817.

### **Shutdown**

The LM4817's LDO goes into sleep mode when the  $\overline{SHDN}$  pin is in a logic low condition. During this condition, the pass transistor, error amplifier, and bandgap are turned off, reducing the supply current to 1nA typical. The maximum guaranteed voltage for a logic low at the  $\overline{SHDN}$  pin is 0.4V. A minimum guaranteed voltage of 2V at the  $\overline{SHDN}$  pin will turn the LDO back on. The  $\overline{SHDN}$  pin may be directly tied to  $V_{IN}$  to keep the part on. The  $\overline{SHDN}$  pin may exceed  $V_{IN}$  but not the ABS MAX of 6.5V.

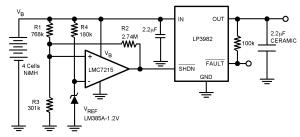

Figure 6 shows an application that uses the SHDN pin. It detects when the battery is too low and disconnects the load by turning off the regulator. A micropower comparator (LMC7215) and reference (LM385) are combined with resistors to set the minimum battery voltage. At the minimum battery voltage, the comparator output goes low and tuns off the LDO and corresponding load. Hysteresis is added to the minimum battery threshold to prevent the battery's recovery voltage from falsely indicating an above minimum condition. When the load is disconnected from the battery, it automatically increases in terminal voltage because of the reduced IR drop across its internal resistance. The Minimum battery detector of figure 6 has a low detection threshold (V<sub>LT</sub>) of 3.6V that corresponds to the minimum battery voltage. The upper threshold (V<sub>UT</sub>) is set for 4.6V in order to exceed the recovery voltage of the battery.

200781C0

FIGURE 7. Minimum Battery Detector that Disconnects the Load Via the SHDN Pin of the LM4817

Resistor value for  $V_{UT}$  and  $V_{LT}$  are determined as follows:

$$G_T = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

$$V_{UT} = R_1 (V_{RFF}) G_T$$

$$V_{LT} = R_1 // R_2 (V_{REF}) G_T$$

(The application of Figure 6 used a  $G_T$  of  $5\mu$  mho)

$$R_1 = \frac{V_{UT1}}{V_{REF}(G_T)}$$

$$R_2 = \frac{1}{\frac{V_{REF}(G_T)}{V_{LT}} - \frac{1}{R_1}}$$

$$R_3 = \frac{1}{G_T - \left[\frac{1}{R_1} + \frac{1}{R_2}\right]}$$

The above procedure assumes a rail-to-rail output comparator. Essentially,  $R_2$  is in parallel with  $R_1$  prior to reaching the lower threshold, then  $R_2$  becomes parallel with  $R_3$  for the upper threshold. Note that the application requires rail-to-rail input as well.

The resistor values shown in Figure 7 are the closest practical to calculated values.

### Fast Start-up

The LM4817's LDO provides fast start-up time for better system efficiency. The start-up speed is maintained when using the optional noise bypass capacitor. An internal  $500\mu A$  current source charges the capacitor until it reaches about 90% of its final value.

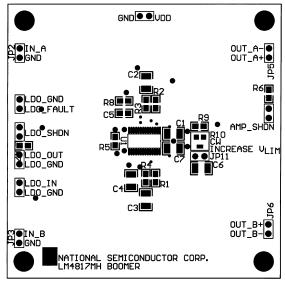

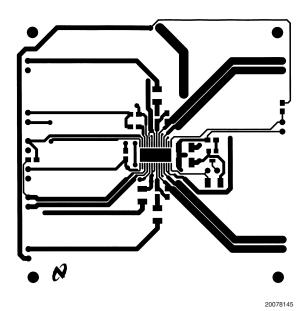

### RECOMMENDED PRINTED CIRCUIT BOARD LAYOUT

Figures 8 through 10 show the recommended two-layer PC board layout that is optimized for the 28-pin MH-packaged LM4817 and associated components. These circuits are designed for use with an external 5V supply and  $8\Omega$  (or greater) speakers.

This circuit board is easy to use. Apply 5V and ground to the board's  $V_{\rm DD}$  and GND pads, respectively. Connect speakers between the board's -OUTA and +OUTA and OUTB and +OUTB pads. Apply the stereo input signal to the input pins labeled "-INA" and "-INB." The stereo input signal's ground references are connected to the respective input channel's "GND" pin, adjacent to the input pins.

200781D2

FIGURE 8. Recommended MH board layout: component-side silkscreen

FIGURE 9. Recommended MHPC board layout: component-side layout

20078148

FIGURE 10. Recommended MH board layout: bottom-side layout

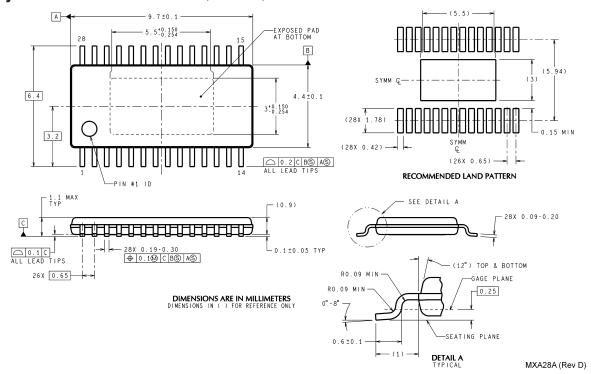

### Physical Dimensions inches (millimeters) unless otherwise noted

28-Lead Molded PKG, TSSOP, JEDEC, 4.4mm BODY WIDTH Order Number LM4817MH NS Package Number MXA28A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560