# ADC081S051

# Single Channel, 500 ksps, 8-Bit A/D Converter

# **General Description**

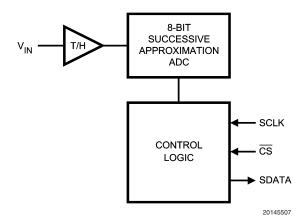

The ADC081S051 is a low-power, single channel CMOS 8-bit analog-to-digital converter with a high-speed serial interface. Unlike the conventional practice of specifying performance at a single sample rate only, the ADC081S051 is fully specified over a sample rate range of 200 kSPS to 500 kSPS. The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit.

The output serial data is straight binary, and is compatible with several standards, such as SPI™, QSPI™, MICROWIRE, and many common DSP serial interfaces.

The ADC081S051 operates with a single supply that can range from +2.7V to +5.25V. Normal power consumption using a +3V or +5V supply is 1.6 mW and 8.5 mW, respectively. The power-down feature reduces the power consumption to as low as 2.6  $\mu$ W using a +5V supply.

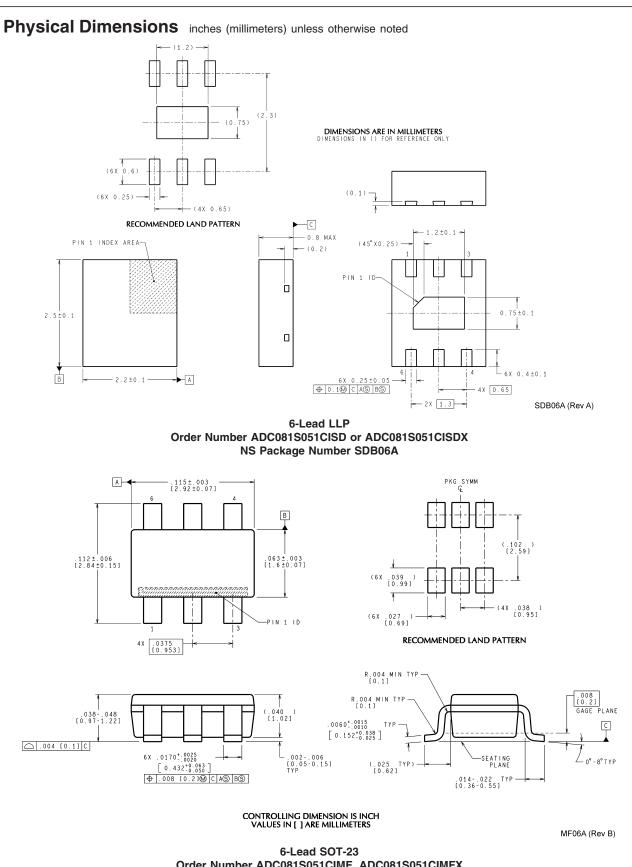

The ADC081S051 is packaged in a 6-lead LLP and SOT-23 package. Operation over the industrial temperature range of -40°C to +85°C is guaranteed.

#### **Features**

- Specified over a range of sample rates.

- 6-lead LLP and SOT-23 package

- Variable power management

- Single power supply with 2.7V 5.25V range

- SPI™/QSPI™/MICROWIRE/DSP compatible

# **Key Specifications**

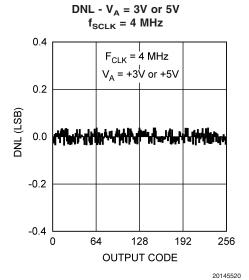

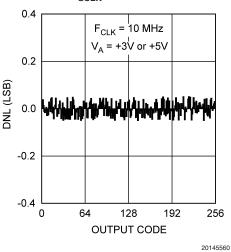

■ DNL +0.06/-0.045 LSB (typ)

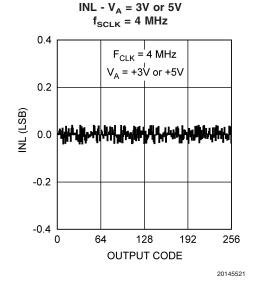

■ INL +0.06/-0.05 LSB (typ)

■ SNR 49.6 dB (typ)

■ Power Consumption

— 3V Supply

— 5V Supply

1.6 mW (typ)

8.5 mW (typ)

# **Applications**

- Portable Systems

- Remote Data Acquisition

- Instrumentation and Control Systems

# Pin-Compatible Alternatives by Resolution and Speed

All devices are fully pin and function compatible.

| Resolution | Specified for Sample Rate Range of:              |            |            |  |  |  |

|------------|--------------------------------------------------|------------|------------|--|--|--|

|            | 50 to 200 kSPS 200 to 500 kSPS 500 kSPS to 1 MSF |            |            |  |  |  |

| 12-bit     | ADC121S021                                       | ADC121S051 | ADC121S101 |  |  |  |

| 10-bit     | ADC101S021                                       | ADC101S051 | ADC081S101 |  |  |  |

| 8-bit      | ADC081S021                                       | ADC081S051 | ADC081S101 |  |  |  |

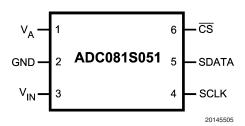

# **Connection Diagram**

# **Ordering Information**

| Order Code                                                     | Order Code Temperature Range Description |                                    | Top Mark |

|----------------------------------------------------------------|------------------------------------------|------------------------------------|----------|

| ADC081S051CISD                                                 | -40°C to +85°C                           | 6-Lead LLP Package                 | X6C      |

| ADC081S051CISDX -40°C to +85°C 6-Lead LLP Package, Tape & Reel |                                          | X6C                                |          |

| ADC081S051CIMF                                                 | -40°C to +85°C                           | 6-Lead SOT-23 Package              | X15C     |

| ADC081S051CIMFX                                                | -40°C to +85°C                           | 6-Lead SOT-23 Package, Tape & Reel | X15C     |

| ADC081S051EVAL                                                 |                                          | SOT-23 Evaluation Board            |          |

TRI-STATE® is a trademark of National Semiconductor Corporation

QSPI™ and SPI™ are trademarks of Motorola, Inc

# **Block Diagram**

# Pin Descriptions and Equivalent Circuits

| Pin No.     | Symbol                                                                                                     | Description                                                                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG I/C  | )                                                                                                          |                                                                                                                                                                                                       |

| 3           | V <sub>IN</sub>                                                                                            | Analog inputs. This signal can range from 0V to V <sub>A</sub> .                                                                                                                                      |

| DIGITAL I/O |                                                                                                            |                                                                                                                                                                                                       |

| 4           | SCLK                                                                                                       | Digital clock input. This clock directly controls the conversion and readout processes.                                                                                                               |

| 5           | 5 SDATA Digital data output. The output samples are clocked out of this pin on falling edges the SCLK pin. |                                                                                                                                                                                                       |

| 6           | CS                                                                                                         | Chip select. On the falling edge of $\overline{\text{CS}}$ , a conversion process begins.                                                                                                             |

| POWER SUI   | PPLY                                                                                                       |                                                                                                                                                                                                       |

| 1           | V <sub>A</sub>                                                                                             | Positive supply pin. This pin should be connected to a quiet +2.7V to +5.25V source and bypassed to GND with a 1 µF capacitor and a 0.1 µF monolithic capacitor located within 1 cm of the power pin. |

| 2           | GND                                                                                                        | The ground return for the supply and signals.                                                                                                                                                         |

# Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to 6.5VAnalog Supply Voltage V<sub>A</sub> Voltage on Any Analog Pin to GND -0.3V to  $(V_A + 0.3V)$ Voltage on Any Digital Pin to GND -0.3V to 6.5VInput Current at Any Pin (Note 3) ±10 mA Package Input Current (Note 3) ±20 mA Power Consumption at  $T_A = 25^{\circ}C$ See (Note 4) ESD Susceptibility (Note 5) Human Body Model 3500V Machine Model 300V Junction Temperature +150°C Storage Temperature -65°C to +150°C

## Operating Ratings (Notes 1, 2)

$\begin{array}{lll} \mbox{Operating Temperature Range} & -40\mbox{°C} \leq T_{\mbox{\scriptsize A}} \leq +85\mbox{°C} \\ \mbox{$V_{\mbox{\scriptsize A}}$ Supply Voltage} & +2.7\mbox{$V$ to } +5.25\mbox{$V$} \\ \mbox{Digital Input Pins Voltage Range} & -0.3\mbox{$V$ to } 5.25\mbox{$V$} \\ \end{array}$

regardless of supply voltage)

# **Package Thermal Resistance**

| Package       | $\theta_{JA}$ |  |  |

|---------------|---------------|--|--|

| 6-lead LLP    | 78°C / W      |  |  |

| 6-lead SOT-23 | 265°C / W     |  |  |

Soldering process must comply with National Semiconductor's Reflow Temperature Profile specifications. Refer to www.national.com/packaging. (Note 6)

### **ADC081S051 Converter Electrical Characteristics** (Note 9)

The following specifications apply for  $V_A = +2.7V$  to 5.25V, GND = 0V,  $f_{SCLK} = 4$  MHz to 10 MHz,  $C_L = 25$  pF,  $f_{SAMPLE} = 200$  kSPS to 500 kSPS, unless otherwise noted. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A = 25$  °C.

| Symbol                           | Parameter                             | Conditions                                                                       | Typical | Limits<br>(Note 9) | Units      |  |  |

|----------------------------------|---------------------------------------|----------------------------------------------------------------------------------|---------|--------------------|------------|--|--|

| STATIC CONVERTER CHARACTERISTICS |                                       |                                                                                  |         |                    |            |  |  |

|                                  | Resolution with No Missing Codes      |                                                                                  |         | 8                  | Bits       |  |  |

|                                  | Integral Non-Linearity                | $V_A = +2.7V \text{ to } +3.6V$                                                  | ±0.04   | ±0.3               | LSB (max)  |  |  |

| INL                              |                                       | V 475V1 5.05V                                                                    | +0.06   | ±0.3               | LSB (max)  |  |  |

|                                  |                                       | $V_A = +4.75V$ to $+5.25V$                                                       | -0.045  | ±0.5               | LSB (min)  |  |  |

|                                  |                                       | $V_A = +2.7V \text{ to } +3.6V$                                                  | ±0.05   | ±0.2               | LSB (max)  |  |  |

| DNL                              | Differential Non-Linearity            | $V_A = +4.75V \text{ to } +5.25V$                                                | +0.06   | ±0.2               | LSB (max)  |  |  |

|                                  |                                       | V <sub>A</sub> = +4.75V to +5.25V                                                | -0.05   |                    | LSB (min)  |  |  |

| V                                | Offset Error                          | $V_A = +2.7V \text{ to } +3.6V$                                                  | -0.01   | ±0.2               | LSB (max)  |  |  |

| $V_{OFF}$                        | Oliset Elloi                          | $V_A = +4.75V$ to $+5.25V$                                                       | +0.04   | ±0.2               | LSB (max)  |  |  |

| GE                               | Online France                         | $V_A = +2.7V \text{ to } +3.6V$                                                  | +0.01   | ±0.4               | LSB (max)  |  |  |

| GE Gain Erro                     | Gain Error                            | $V_A = +4.75V$ to $+5.25V$                                                       | -0.075  | ±0.4               | LSB (max)  |  |  |

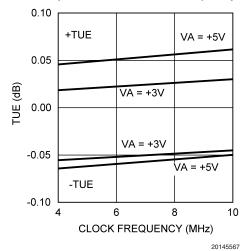

|                                  | Total Unadjusted Error                | V <sub>A</sub> = +2.7V to +3.6V                                                  | +0.04   | ±0.3               | LSB (max)  |  |  |

| <b>-</b>                         |                                       |                                                                                  | -0.045  |                    | LSB (min)  |  |  |

| TUE                              |                                       | V <sub>A</sub> = +4.75V to +5.25V                                                | +0.07   | ±0.3               | LSB (max)  |  |  |

|                                  |                                       |                                                                                  | -0.055  |                    | LSB (min)  |  |  |

| DYNAMIC                          | CONVERTER CHARACTERISTICS             |                                                                                  |         |                    |            |  |  |

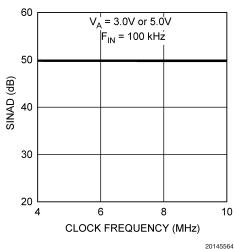

| SINAD                            | Signal-to-Noise Plus Distortion Ratio | $V_A = +2.7 \text{ to } 5.25V$<br>$f_{IN} = 100 \text{ kHz}, -0.02 \text{ dBFS}$ | 49.5    | 49                 | dB (min)   |  |  |

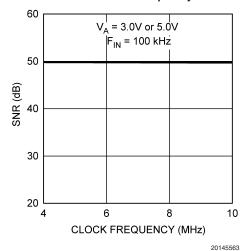

| SNR                              | Signal-to-Noise Ratio                 | $V_A = +2.7 \text{ to } 5.25V$<br>$f_{IN} = 100 \text{ kHz}, -0.02 \text{ dBFS}$ | 49.6    | 49                 | dB (min)   |  |  |

| THD                              | Total Harmonic Distortion             | $V_A = +2.7 \text{ to } 5.25V$<br>$f_{IN} = 100 \text{ kHz}, -0.02 \text{ dBFS}$ | -77     | -65                | dB (max)   |  |  |

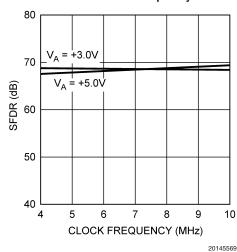

| SFDR                             | Spurious-Free Dynamic Range           | $V_A = +2.7 \text{ to } 5.25V$<br>$f_{IN} = 100 \text{ kHz}, -0.02 \text{ dBFS}$ | 67      | 65                 | dB (min)   |  |  |

| ENOB                             | Effective Number of Bits              | $V_A = +2.7 \text{ to } 5.25V$<br>$f_{IN} = 100 \text{ kHz}, -0.02 \text{ dBFS}$ | 7.9     | 7.8                | Bits (min) |  |  |

**ADC081S051 Converter Electrical Characteristics** (Note 9) (Continued) The following specifications apply for  $V_A = +2.7V$  to 5.25V, GND = 0V,  $f_{SCLK} = 4$  MHz to 10 MHz,  $C_L = 25$  pF,  $f_{SAMPLE} = 200$  kSPS to 500 kSPS, unless otherwise noted. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A = 25$  °C.

| Symbol  | Parameter                                      | Conditions                                                           | Typical | Limits<br>(Note 9) | Units |  |  |

|---------|------------------------------------------------|----------------------------------------------------------------------|---------|--------------------|-------|--|--|

| DYNAMIC | DYNAMIC CONVERTER CHARACTERISTICS              |                                                                      |         |                    |       |  |  |

| IMD     | Intermodulation Distortion, Second Order Terms | $V_A = +5.25V$<br>$f_a = 104.3 \text{ kHz}, f_b = 113.5 \text{ kHz}$ | -83     |                    | dB    |  |  |

| IIVID   | Intermodulation Distortion, Third Order Terms  | $V_A = +5.25V$<br>$f_a = 104.3 \text{ kHz}, f_b = 113.5 \text{ kHz}$ | -82     |                    | dB    |  |  |

| FPBW    | -3 dB Full Power Bandwidth                     | $V_A = +5V$                                                          | 11      |                    | MHz   |  |  |

|         |                                                | $V_A = +3V$                                                          | 8       |                    | MHz   |  |  |

**ADC081S051 Converter Electrical Characteristics** (Note 9) (Continued) The following specifications apply for  $V_A$  = +2.7V to 5.25V, GND = 0V,  $f_{SCLK}$  = 4 MHz to 10 MHz,  $C_L$  = 25 pF,  $f_{SAMPLE}$  = 200 kSPS to 500 kSPS, unless otherwise noted. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A$  = 25°C.

| Symbol                                | Parameter                          | Conditions                                     | Typical               | Limits<br>(Note 9)   | Units           |  |  |  |

|---------------------------------------|------------------------------------|------------------------------------------------|-----------------------|----------------------|-----------------|--|--|--|

| ANALOG INPUT CHARACTERISTICS          |                                    |                                                |                       |                      |                 |  |  |  |

| V <sub>IN</sub>                       | Input Range                        |                                                | 0 to V <sub>A</sub>   |                      | V               |  |  |  |

| I <sub>DCL</sub>                      | DC Leakage Current                 |                                                |                       | ±1                   | μA (max)        |  |  |  |

| C <sub>INA</sub>                      | Input Capacitance                  | Track Mode                                     | 30                    |                      | pF              |  |  |  |

|                                       |                                    | Hold Mode                                      | 4                     |                      | pF              |  |  |  |

| DIGITAL                               | DIGITAL INPUT CHARACTERISTICS      |                                                |                       |                      |                 |  |  |  |

| $V_{IH}$                              | Input High Voltage                 | $V_A = +5.25V$                                 |                       | 2.4                  | V (min)         |  |  |  |

| *IH                                   | Input riight voltage               | $V_A = +3.6V$                                  |                       | 2.1                  | V (min)         |  |  |  |

| $V_{IL}$                              | Input Low Voltage                  | $V_A = +5.25V$                                 |                       | 0.8                  | V (max)         |  |  |  |

| VIL                                   | Input Low Voltage                  | $V_A = +3.6V$                                  |                       | 0.4                  | V (max)         |  |  |  |

| I <sub>IN</sub>                       | Input Current                      | $V_{IN} = 0V \text{ or } V_A$                  | ±0.1                  | ±1                   | μA (max)        |  |  |  |

| $C_{IND}$                             | Digital Input Capacitance          |                                                | 2                     | 4                    | pF (max)        |  |  |  |

| DIGITAL (                             | OUTPUT CHARACTERISTICS             |                                                |                       |                      |                 |  |  |  |

| · · · · · · · · · · · · · · · · · · · | Output High Voltage                | I <sub>SOURCE</sub> = 200 μA                   | V <sub>A</sub> - 0.07 | V <sub>A</sub> - 0.2 | V (min)         |  |  |  |

| $V_{OH}$                              | Output High Voltage                | I <sub>SOURCE</sub> = 1 mA                     | V <sub>A</sub> - 0.1  |                      | V               |  |  |  |

|                                       | Output Law Valtage                 | I <sub>SINK</sub> = 200 μA                     | 0.03                  | 0.4                  | V (max)         |  |  |  |

| $V_{OL}$                              | Output Low Voltage                 | I <sub>SINK</sub> = 1 mA                       | 0.1                   |                      | V               |  |  |  |

| I <sub>OZH</sub> ,                    | TDL OTATE® Laster to Occurrent     |                                                | .0.1                  |                      | ()              |  |  |  |

| l <sub>OZL</sub>                      | TRI-STATE® Leakage Current         |                                                | ±0.1                  | ±10                  | μA (max)        |  |  |  |

| C <sub>OUT</sub>                      | TRI-STATE® Output Capacitance      |                                                | 2                     | 4                    | pF (max)        |  |  |  |

|                                       | Output Coding                      |                                                | Stra                  | aight (Natura        | al) Binary      |  |  |  |

| POWER S                               | SUPPLY CHARACTERISTICS (CL = 10    | ) pF)                                          | '                     |                      |                 |  |  |  |

|                                       | 0 1 1/1                            |                                                |                       | 2.7                  | V (min)         |  |  |  |

| $V_A$                                 | Supply Voltage                     |                                                |                       | 5.25                 | V (max)         |  |  |  |

|                                       | Supply Current, Normal Mode        | $V_A = +5.25V,$                                | 1.01                  | 0.4                  | <b>A</b> / )    |  |  |  |

|                                       |                                    | f <sub>SAMPLE</sub> = 200 kSPS                 | 1.61                  | 2.4                  | mA (max)        |  |  |  |

|                                       | (Operational, CS low)              | $V_A = +3.6V$ ,                                | 0.40                  | 1.0                  | να Λ. (να α.κ.) |  |  |  |

| 1                                     | ( )                                | f <sub>SAMPLE</sub> = 200 kSPS                 | 0.43                  | 1.0                  | mA (max)        |  |  |  |

| I <sub>A</sub>                        |                                    | $f_{SCLK}= 0 \text{ MHz}, V_A = +5.25V$        | 0.5                   |                      |                 |  |  |  |

|                                       | Supply Current, Shutdown (CS high) | f <sub>SAMPLE</sub> = 0 kSPS                   | 0.5                   |                      | μΑ              |  |  |  |

|                                       | Supply Current, Shutdown (CS high) | $V_A = +5.25V$ , $f_{SCLK} = 10$ MHz,          | 21                    |                      |                 |  |  |  |

|                                       |                                    | f <sub>SAMPLE</sub> = 0 kSPS                   | 21                    |                      | μΑ              |  |  |  |

|                                       | Power Consumption, Normal Mode     | $V_A = +5.25V$                                 | 8.5                   | 12.6                 | mW (max)        |  |  |  |

|                                       | (Operational, CS low)              | $V_A = +3.6V$                                  | 1.6                   | 3.6                  | mW (max)        |  |  |  |

| $P_D$                                 |                                    | $f_{SCLK} = 0 \text{ MHz}, V_A = +5.25V$       | 2.6                   |                      | μW              |  |  |  |

| ' D                                   | Power Consumption, Shutdown (CS    | f <sub>SAMPLE</sub> = 0 kSPS                   | 2.0                   |                      | μνν             |  |  |  |

|                                       | high)                              | $V_A = +5.25V$ , $f_{SCLK} = 10 \text{ MHz}$ , | 110                   |                      | μW              |  |  |  |

|                                       |                                    | f <sub>SAMPLE</sub> = 0 kSPS                   | 110                   |                      | μνν             |  |  |  |

| AC ELEC                               | TRICAL CHARACTERISTICS             |                                                |                       |                      |                 |  |  |  |

| f                                     | Clock Frequency                    | (Note 8)                                       |                       | 4                    | MHz (min)       |  |  |  |

| f <sub>SCLK</sub>                     | Clock Frequency                    | (Note 8)                                       |                       | 10                   | MHz (max)       |  |  |  |

| f                                     | Sample Pate                        | (Note 8)                                       | 50                    | 200                  | kSPS (min)      |  |  |  |

| f <sub>S</sub>                        | Sample Rate                        | (Note 8)                                       |                       | 500                  | kSPS (max)      |  |  |  |

| t <sub>CONV</sub>                     | Conversion Time                    |                                                |                       | 16                   | SCLK cycles     |  |  |  |

|                                       | CCLK Duty Co-1-                    | f 40 MH                                        | 50                    | 40                   | % (min)         |  |  |  |

| DC                                    | SCLK Duty Cycle                    | f <sub>SCLK</sub> = 10 MHz                     | 50                    | 60                   | % (max)         |  |  |  |

| t <sub>ACQ</sub>                      | Track/Hold Acquisition Time        |                                                |                       | 400                  | ns (max)        |  |  |  |

|                                       |                                    | 1                                              |                       |                      |                 |  |  |  |

#### ADC081S051 Converter Electrical Characteristics (Note 9) (Continued)

The following specifications apply for  $V_A = +2.7V$  to 5.25V, GND = 0V,  $f_{SCLK} = 4$  MHz to 10 MHz,  $C_L = 25$  pF,  $f_{SAMPLE} = 200$  kSPS to 500 kSPS, unless otherwise noted. **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A = 25^{\circ}C$ .

| Symbol             | Parameter                     | Conditions                         | Typical | Limits<br>(Note 9) | Units       |  |  |

|--------------------|-------------------------------|------------------------------------|---------|--------------------|-------------|--|--|

| AC ELEC            | AC ELECTRICAL CHARACTERISTICS |                                    |         |                    |             |  |  |

|                    | Throughput Time               | Acquisition Time + Conversion Time |         | 20                 | SCLK cycles |  |  |

| t <sub>QUIET</sub> | (Note 10)                     |                                    |         | 50                 | ns (min)    |  |  |

| t <sub>AD</sub>    | Aperture Delay                |                                    | 3       |                    | ns          |  |  |

| t <sub>AJ</sub>    | Aperture Jitter               |                                    | 30      |                    | ps          |  |  |

# **ADC081S051 Timing Specifications**

The following specifications apply for  $V_A = +2.7V$  to 5.25V, GND = 0V,  $f_{SCLK} = 4$  MHz to 10 MHz,  $C_L = 25$  pF,  $f_{SAMPLE} = 200$  kSPS to 500 kSPS, **Boldface limits apply for T\_A = T\_{MIN} to T\_{MAX}**: all other limits  $T_A = 25^{\circ}C$ .

| Symbol                | Parameter                                                                      | Conditions                             | Typical | Limits            | Units       |

|-----------------------|--------------------------------------------------------------------------------|----------------------------------------|---------|-------------------|-------------|

| t <sub>CS</sub>       | Minimum CS Pulse Width                                                         |                                        |         | 10                | ns (min)    |

| t <sub>su</sub>       | CS to SCLK Setup Time                                                          |                                        |         | 10                | ns (min)    |

| t <sub>EN</sub>       | Delay from $\overline{\text{CS}}$ Until SDATA TRI-STATE®<br>Disabled (Note 11) |                                        |         | 20                | ns (max)    |

| +                     | Data Access Time after SCLK Falling Edge                                       | $V_A = +2.7V \text{ to } +3.6V$        |         | 40                | ns (max)    |

| t <sub>ACC</sub>      | (Note 12)                                                                      | $V_A = +4.75V$ to $+5.25V$             |         | 20                | ns (max)    |

| t                     | SCLK Low Pulse Width                                                           |                                        |         | 0.4 x             | ns (min)    |

| t <sub>CL</sub>       |                                                                                |                                        |         | t <sub>SCLK</sub> | 113 (11111) |

| t                     | SCLK High Pulse Width                                                          |                                        |         | 0.4 x             | ns (min)    |

| t <sub>CH</sub>       | SCLK High Fulse Width                                                          |                                        |         | t <sub>sclk</sub> | 113 (11111) |

| +                     | SCLK to Data Valid Hold Time                                                   | $V_A = +2.7V \text{ to } +3.6V$        |         | 7                 | ns (min)    |

| t <sub>H</sub>        |                                                                                | $V_A = +4.75V \text{ to } +5.25V$      |         | 5                 | ns (min)    |

|                       | SCLK Falling Edge to SDATA High<br>Impedance (Note 13)                         | V <sub>A</sub> = +2.7V to +3.6V        |         | 25                | ns (max)    |

| t <sub>DIS</sub>      |                                                                                |                                        |         | 6                 | ns (min)    |

|                       |                                                                                | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |         | 25                | ns (max)    |

|                       |                                                                                | $V_A = +4.75V \text{ to } +5.25V$      |         | 5                 | ns (min)    |

| t <sub>POWER-UP</sub> | Power-Up Time from Full Power-Down                                             |                                        | 1       |                   | μs          |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND = 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds the power supply (that is,  $V_{IN} < GND$  or  $V_{IN} > V_A$ ), the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two. The Absolute Maximum Rating specification does not apply to the  $V_A$  pin. The current into the  $V_A$  pin is limited by the Analog Supply Voltage specification.

Note 4: The absolute maximum junction temperature  $(T_J max)$  for this device is 150°C. The maximum allowable power dissipation is dictated by  $T_J max$ , the junction-to-ambient thermal resistance  $(\theta_{JA})$ , and the ambient temperature  $(T_A)$ , and can be calculated using the formula  $P_D MAX = (T_J max - T_A)/\theta_{JA}$ . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor. Machine model is 220 pF discharged through zero ohms

Note 6: Reflow temperature profiles are different for lead-free and non-lead-free packages.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: This is the frequency range over which the electrical performance is guaranteed. The device is functional over a wider range which is specified under Operating Ratings.

Note 9: Data sheet min/max specification limits are guaranteed by design, test, or statistical analysis.

Note 10: Minimum Quiet Time required by Bus relinquish and start of the next conversion.

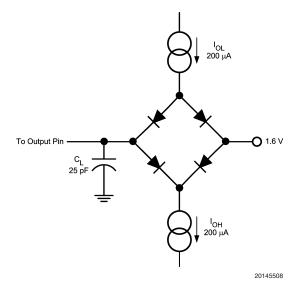

Note 11: Measured with the timing test circuit shown in Figure 1 and defined as the time taken by the output signal to cross 1.0V.

Note 12: Measured with the timing test circuit shown in Figure 1 and defined as the time taken by the output signal to cross 1.0V going low or 2.0V going high.

Note 13:  $t_{DIS}$  is derived from the time taken by the output to change by 0.5V with the timing test circuit shown in Figure 1. The measured number is then adjusted to remove the effects of charging or discharging the load capacitance. This means that  $t_{DIS}$  is the true bus relinquish time, independent of the bus loading.

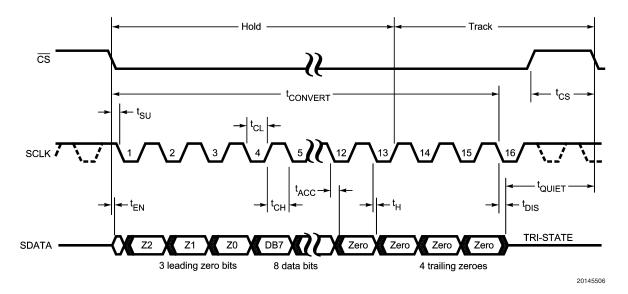

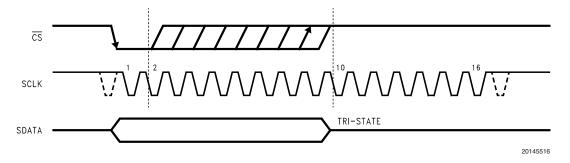

# **Timing Diagrams**

FIGURE 1. Timing Test Circuit

FIGURE 2. ADC081S051 Serial Timing Diagram

# **Specification Definitions**

**ACQUISITION TIME** is the time required to acquire the input voltage. That is, it is time required for the hold capacitor to charge up to the input voltage.

**APERTURE DELAY** is the time between the fourth falling SCLK edge of a conversion and the time when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

**CONVERSION TIME** is the time required, after the input voltage is acquired, for the ADC to convert the input voltage to a digital word.

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**DUTY CYCLE** is the ratio of the time that a repetitive digital waveform is high to the total time of one period. The specification here refers to the SCLK.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion or SINAD. ENOB is defined as (SINAD – 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

**GAIN ERROR** is the deviation of the last code transition (111...110) to (111...111) from the ideal ( $V_{REF}-1.5$  LSB), after adjusting for offset error.

**INTEGRAL NON-LINEARITY (INL)** is a measure of the deviation of each individual code from a line drawn from negative full scale (½ LSB below the first code transition) through positive full scale (½ LSB above the last code transition). The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. It is defined as the ratio of the power in the second and third order intermodulation products to the sum of the power in both of the original frequencies. IMD is usually expressed in

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC081S051 is guaranteed not to have any missing codes.

**OFFSET ERROR** is the deviation of the first code transition (000...000) to (000...001) from the ideal (i.e. GND + 0.5 LSB).

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or d.c.

SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD) Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

**SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal and the peak spurious signal where a spurious signal is any signal present in the output spectrum that is not present at the input, excluding d.c.

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dB or dBc, of the rms total of the first five harmonic components at the output to the rms level of the input signal frequency as seen at the output. THD is calculated as

THD=

$$20 \cdot \log_{10} \sqrt{\frac{{A_{f2}}^2 + \dots + {A_{f6}}^2}{{A_{f1}}^2}}$$

where  $A_{f1}$  is the RMS power of the input frequency at the output and  $A_{f2}$  through  $A_{f6}$  are the RMS power in the first 5 harmonic frequencies.

**THROUGHPUT TIME** is the minimum time required between the start of two successive conversion. It is the acquisition time plus the conversion time.

**TOTAL UNADJUSTED ERROR** is the worst deviation found from the ideal transfer function. As such, it is a comprehensive specification which includes full scale error, linearity error, and offset error.

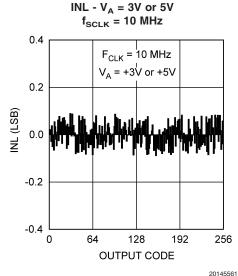

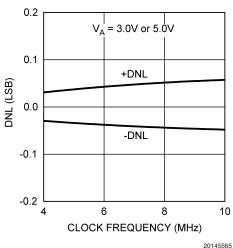

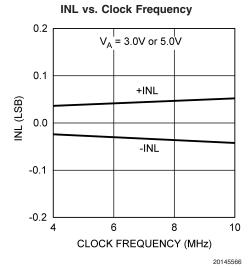

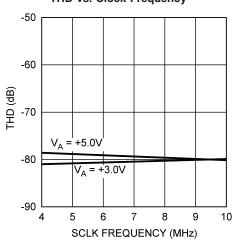

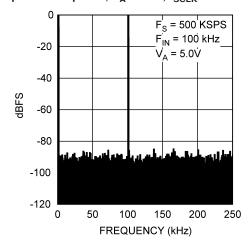

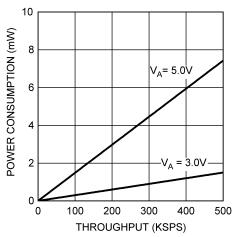

# **Typical Performance Characteristics** $T_A = +25^{\circ}C$ , $f_{SAMPLE} = 200$ kSPS to 500 kSPS, $f_{SCLK} = 4$ MHz to 10 MHz, $f_{IN} = 100$ kHz unless otherwise stated.

DNL -  $V_A = 3V$  or 5V

# **Typical Performance Characteristics** $T_A = +25^{\circ}C$ , $f_{SAMPLE} = 200$ kSPS to 500 kSPS, $f_{SCLK} = 4$ MHz to 10 MHz, $f_{IN} = 100$ kHz unless otherwise stated. (Continued)

#### SINAD vs. Clock Frequency

#### SFDR vs.Clock Frequency

#### SNR vs. Clock Frequency

THD vs. Clock Frequency

Spectral Response,  $V_A = 5.0V$ ,  $f_{SCLK} = 10 \text{ MHz}$

20145562

# $\textbf{Typical Performance Characteristics} \ T_{A} = +25^{\circ}\text{C}, \ f_{SAMPLE} = 200 \ \text{kSPS to 500 kSPS}, \\ f_{SCLK} = 4 \ \text{MHz to 10 MHz}, \ f_{IN} = 100 \ \text{kHz unless otherwise stated}. \ \textbf{(Continued)}$

### Power Consumption vs. Throughput, $f_{SCLK} = 10 \text{ MHz}$

20145555

# **Applications Information**

#### 1.0 ADC081S051 OPERATION

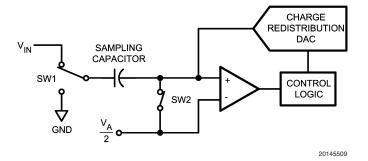

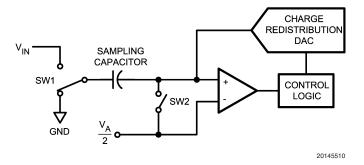

The ADC081S051 is a successive-approximation analog-to-digital converter designed around a charge-redistribution digital-to-analog converter. Simplified schematics of the ADC081S051 in both track and hold modes are shown in *Figure 3* and *Figure 4*, respectively. In *Figure 3*, the device is in track mode: switch SW1 connects the sampling capacitor to the input and SW2 balances the comparator inputs. The device is in this state until  $\overline{\text{CS}}$  is brought low, at which point the device moves to hold mode.

Figure 4 shows the device in hold mode: switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The device moves from hold mode to track mode on the 13th rising edge of SCLK following assertion of  $\overline{\text{CS}}$ .

FIGURE 3. ADC081S051 in Track Mode

FIGURE 4. ADC081S051 in Hold Mode

#### 2.0 USING THE ADC081S051

The serial interface timing diagram for the ADC081S051 is shown in Figure 2.  $\overline{\text{CS}}$  is chip select, which initiates conversions on the ADC081S051 and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. SDATA is the serial data out pin, where a conversion result is found as a serial data stream.

Basic operation of the ADC081S051 begins with  $\overline{CS}$  going low, which initiates a conversion process and data transfer. Subsequent rising and falling edges of SCLK will be labelled with reference to the falling edge of  $\overline{CS}$ ; for example, "the third falling edge of SCLK" shall refer to the third falling edge of SCLK after  $\overline{CS}$  goes low.

At the fall of  $\overline{\text{CS}}$ , the SDATA pin comes out of TRI-STATE and the converter moves from track mode to hold mode. The input signal is sampled and held for conversion on the falling edge of  $\overline{\text{CS}}$ . The converter moves from hold mode to track

mode on the 13th rising edge of SCLK (see *Figure 2*). The SDATA pin will be placed back into TRI-STATE after the 16th falling edge of SCLK, or at the rising edge of  $\overline{CS}$ , whichever occurs first. After a conversion is completed, the quiet time ( $t_{QUIET}$ ) must be satisfied before bringing  $\overline{CS}$  low again to begin another conversion.

Sixteen SCLK cycles are required to read a complete sample from the ADC081S051. The sample bits (including leading or trailing zeroes) are clocked out on falling edges of SCLK, and are intended to be clocked in by a receiver on subsequent rising edges of SCLK. The ADC081S051 will produce three leading zero bits on SDATA, followed by eight data bits, most significant first. After the data bits, the ADC081S051 will clock out four trailing zeros.

If  $\overline{\text{CS}}$  goes low before the rising edge of SCLK, an additional (fourth) zero bit may be captured by the next falling edge of SCLK.

## **Applications Information** (Continued)

#### 3.0 ADC081S051 TRANSFER FUNCTION

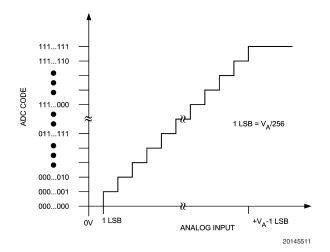

The output format of the ADC081S051 is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC081S051 is  $V_{\rm A}/256$ . The ideal transfer characteristic is shown in *Figure 5*. The transition from an output code of 0000 0000 to a code of 0000 0001 is at 1/2 LSB, or a voltage of  $V_{\rm A}/512$ . Other code transitions occur at steps of one LSB.

FIGURE 5. Ideal Transfer Characteristic

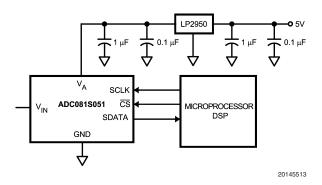

#### 4.0 TYPICAL APPLICATION CIRCUIT

A typical application of the ADC081S051 is shown in *Figure 6*. Power is provided in this example by the National Semiconductor LP2950 low-dropout voltage regulator, available in a variety of fixed and adjustable output voltages. The power supply pin is bypassed with a capacitor network located close to the ADC081S051. Because the reference for the ADC081S051 is the supply voltage, any noise on the supply will degrade device noise performance. To keep noise off the supply, use a dedicated linear regulator for this device, or provide sufficient decoupling from other circuitry to keep noise off the ADC081S051's low power requirements, it is also possible to use a precision reference as a power supply to maximize performance. The three-wire interface is shown connected to a microprocessor or DSP.

**FIGURE 6. Typical Application Circuit**

#### **5.0 ANALOG INPUTS**

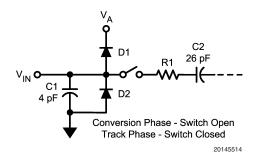

An equivalent circuit of the ADC081S051's input is shown in *Figure 7*. Diodes D1 and D2 provide ESD protection for the analog inputs. At no time should the analog input go beyond  $(V_A + 300 \text{ mV})$  or (GND - 300 mV), as these ESD diodes will begin to conduct, which could result in erratic operation.

The capacitor C1 in *Figure 7* has a typical value of 4 pF, and is mainly the package pin capacitance. Resistor R1 is the on resistance of the track / hold switch, and is typically 500 ohms. Capacitor C2 is the ADC081S051 sampling capacitor and is typically 26 pF. The ADC081S051 will deliver best performance when driven by a low-impedance source to eliminate distortion caused by the charging of the sampling capacitance. This is especially important when using the ADC081S051 to sample AC signals. Also important when sampling dynamic signals is an anti-aliasing filter.

FIGURE 7. Equivalent Input Circuit

#### **6.0 DIGITAL INPUTS AND OUTPUTS**

The ADC081S051 digital inputs (SCLK and  $\overline{\text{CS}}$ ) are not limited by the same maximum ratings as the analog inputs. The digital input pins are instead limited to +5.25V with respect to GND, regardless of V<sub>A</sub>, the supply voltage. This allows the ADC081S051 to be interfaced with a wide range of logic levels, independent of the supply voltage.

#### 7.0 MODES OF OPERATION

The ADC081S051 has two possible modes of operation: normal mode, and shutdown mode. The ADC081S051 enters normal mode (and a conversion process is begun) when  $\overline{\text{CS}}$  is pulled low. The device will enter shutdown mode if  $\overline{\text{CS}}$  is pulled high before the tenth falling edge of SCLK after  $\overline{\text{CS}}$  is pulled low, or will stay in normal mode if  $\overline{\text{CS}}$  remains low. Once in shutdown mode, the device will stay there until  $\overline{\text{CS}}$  is brought low again. By varying the ratio of time spent in the normal and shutdown modes, a system may trade-off throughput for power consumption.

#### 7.1 Normal Mode

The fastest possible throughput is obtained by leaving the ADC081S051 in normal mode at all times, so there are no power-up delays. To keep the device in normal mode continuously,  $\overline{\text{CS}}$  must be kept low until after the 10th falling edge of SCLK after the start of a conversion (remember that a conversion is initiated by bringing  $\overline{\text{CS}}$  low).

If  $\overline{\text{CS}}$  is brought high after the 10th falling edge, but before the 16th falling edge, the device will remain in normal mode, but the current conversion will be aborted, and SDATA will return to TRI-STATE (truncating the output word).

Sixteen SCLK cycles are required to read all of a conversion word from the device. After sixteen SCLK cycles have elapsed,  $\overline{CS}$  may be idled either high or low until the next

# **Applications Information** (Continued)

conversion. If  $\overline{\text{CS}}$  is idled low, it must be brought high again before the start of the next conversion, which begins when  $\overline{\text{CS}}$  is again brought low.

After sixteen SCLK cycles, SDATA returns to TRI-STATE. Another conversion may be started, after  $t_{QUIET}$  has elapsed, by bringing  $\overline{CS}$  low again.

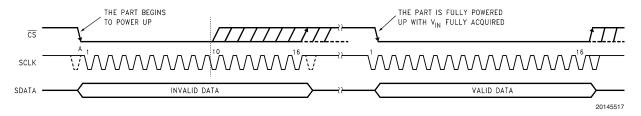

#### 7.2 Shutdown Mode

Shutdown mode is appropriate for applications that either do not sample continuously, or it is acceptable to trade throughput for power consumption. When the ADC081S051 is in shutdown mode, all of the analog circuitry is turned off.

To enter shutdown mode, a conversion must be interrupted by bringing  $\overline{CS}$  high anytime between the second and tenth falling edges of SCLK, as shown in Figure 8. Once  $\overline{CS}$  has been brought high in this manner, the device will enter shutdown mode, the current conversion will be aborted and SDATA will enter TRI-STATE. If  $\overline{CS}$  is brought high before the second falling edge of SCLK, the device will not change mode; this is to avoid accidentally changing mode as a result of noise on the  $\overline{CS}$  line.

FIGURE 8. Entering Shutdown Mode

FIGURE 9. Entering Normal Mode

To exit shutdown mode, bring  $\overline{CS}$  back low. Upon bringing  $\overline{CS}$  low, the ADC081S051 will begin powering up (power-up time is specified in the Timing Specifications table). This microsecond of power-up delay results in the first conversion result being unusable. The second conversion performed after power-up, however, is valid, as shown in *Figure 9*.

If  $\overline{\text{CS}}$  is brought back high before the 10th falling edge of SCLK, the device will return to shutdown mode. This is done to avoid accidentally entering normal mode as a result of noise on the  $\overline{\text{CS}}$  line. To exit shutdown mode and remain in normal mode,  $\overline{\text{CS}}$  must be kept low until after the 10th falling edge of SCLK. The ADC081S051 will be fully powered-up after 16 SCLK cycles.

#### **8.0 POWER MANAGEMENT**

The ADC081S051 takes time to power-up, either after first applying  $V_{\rm A},$  or after returning to normal mode from shutdown mode. This corresponds to one "dummy" conversion for any SCLK frequency within the specifications in this document. After this first dummy conversion, the ADC081S051 will perform conversions properly. Note that the  $t_{\rm QUIET}$  time must still be included between the first dummy conversion and the second valid conversion.

When the  $V_A$  supply is first applied, the ADC081S051 may power up in either of the two modes: normal or shutdown. As such, one dummy conversion should be performed after start-up, exactly as described in the previous paragraph. The part may then be placed into either normal mode or the shutdown mode, as described in Sections 7.1 and 7.2.

When the ADC081S051 is operated continuously in normal mode, the maximum throughput is f<sub>SCLK</sub> / 20. Throughput may be traded for power consumption by running f<sub>SCLK</sub> at its maximum rate and performing fewer conversions per unit time, raising the ADC081S051 CS line after the 10th to 15th clock cycle of each conversion. A plot of typical power consumption versus throughput is shown in the Typical Performance Curves section. To calculate the power consumption for a given throughput, multiply the fraction of time spent in the normal mode by the normal mode power consumption and add the fraction of time spent in shutdown mode multiplied by the shutdown mode power consumption. Note that the curve of power consumption vs. throughput is essentially linear. This is because the power consumption in the shutdown mode is so small that it can be ignored for all practical purposes.

# **Applications Information** (Continued)

#### 9.0 POWER SUPPLY NOISE CONSIDERATIONS

The charging of any output load capacitance requires current from the power supply,  $V_A$ . The current pulses required from the supply to charge the output capacitance will cause voltage variations on the supply. If these variations are large enough, they could degrade SNR and SINAD performance of the ADC. Furthermore, discharging the output capacitance when the digital output goes from a logic high to a logic low will dump current into the die substrate, which is resistive. Load discharge currents will cause "ground bounce"

noise in the substrate that will degrade noise performance if that current is large enough. The larger the output capacitance, the more current flows through the die substrate and the greater is the noise coupled into the analog channel, degrading noise performance.

To keep noise out of the power supply, keep the output load capacitance as small as practical. If the load capacitance is greater than 25 pF, use a 100  $\Omega$  series resistor at the ADC output, located as close to the ADC output pin as practical. This will limit the charge and discharge current of the output capacitance and maintain noise performance.

6-Lead SOT-23

Order Number ADC081S051CIMF, ADC081S051CIMFX

NS Package Number MF06A

### **Notes**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.cor

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560