**Two ports 10/100Mbps Ethernet Switch Controller**

Winbond LAN W89C871F Two Ports Switch Controller

| OVERVIEW DESCRIPTION                                                                                                                      | 2              |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| FEATURES                                                                                                                                  | 3              |

| PIN ASSIGNMENT                                                                                                                            | 4              |

| PIN CONFIGURATION                                                                                                                         | 4              |

| SYSTEM DIAGRAM                                                                                                                            | 11             |

| BLOCK DIAGRAM                                                                                                                             | 11             |

| FUNCTIONAL DESCRIPTION                                                                                                                    | 12             |

| Buffer Memory and Bus<br>External Memory Configuration<br>VLAN-tagged Frame<br>Address Table Format<br>The Operation of the Address table |                |

| THE OPERATION OF THE PACKET SWITCH                                                                                                        | 22             |

| THE FUNCTIONS OF MEDIA ACCESS CONTROLLER(MAC)                                                                                             | 35             |

| NETWORK MEDIA SPEED SELECTION FUNCTION<br>THE RECEIVE FUNCTIONS OF MAC<br>THE TRANSMIT FUNCTIONS OF MAC<br>DMA FUNCTIONS                  |                |

| MII Management<br>LED DISPLAYING INTERFACE                                                                                                |                |

| MISCELLANEOUS REPORT<br>EXTERNAL MANAGER INTERFACE                                                                                        | 48             |

| ELECTRICAL CHARACTERISTICS                                                                                                                | 50             |

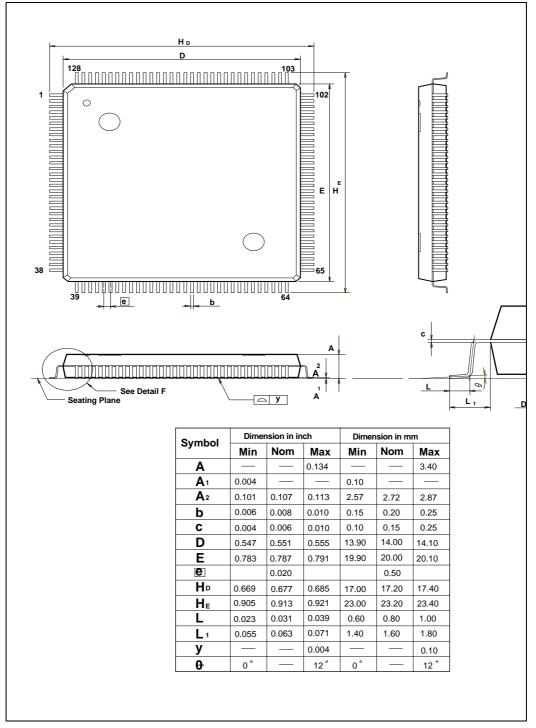

| Absolute Maximum Ratings<br>Power Supply<br>DC Characteristics<br>AC Characteristics<br>PACKACE AND DIMENSIONS                            | 50<br>51<br>51 |

| PACKAGE AND DIMENSIONS                                                                                                                    |                |

# **OVERVIEW DESCRIPTION**

The W89C871F is a two-port 10/100Mbps Ethernet switch/bridge single chip controller that provides an excellent performance with extremely low packet lost rate. It is able to forward packets with full wire speed, and bridges the network segments between two auto-negotiated ports. The W89C871F is specifically designed to construct the unmanaged network applications with minimum cost, which are suitable for seamless connecting 10M and 100M Ethernet network segments, bridging two Ethernet network segments and extending 100M Fast Ethernet segments scope.

For bridging network segments or forwarding/filtering any data stream, even Virtual LAN tagged frame with unicast or multicast/broadcast addresses at wire speed, W89C871F is implemented many intelligent functions which are hardware address self-learning, filtering and forwarding algorithms supporting up to 4k address entries, as well as advanced active aging algorithm for fully utilizing the space of address table. An active back-pressure flow control for half duplex operation is also implemented to keep buffer memory from overflow.

With its high performance capability, W89C871F implements two deep independent FIFOs on each port with enhanced 32-bit DMA channel to share the packet buffer for full/half duplex operation and different speed network operation. Specially, W89C871F offers a loading balance-like function for the communication between 10M Ethernet and 100M fast Ethernet to prevent from extreme low forwarding performance for 10M network segment if 100M network segment is very busy. Configurable SRAM interface supports a maximum of 512k bytes with different type of SRAM easily sourced, in which 128kx8 or 64kx8 SRAM is fine, as well as a group of control and status registers programmable through MII bus for design and productivity.

# **FEATURES**

- Store and forward switching

- Shared memory for packet buffering

- 14880/148800 forwarding rate for 10M/100M operation respectively

- 4K entries routing table supported

- Two 10M/100M auto-sensing MII ports provided

- Half duplex and full duplex function provided

- Back pressure flow control for half duplex operation provided

- Packet buffer congestion control function provided

- Hardware aging function provided

- Supports VLAN tagged frame

- Network activity status LED displaying function provided

- 128Kx8 or 64Kx16 SRAM interface provided

- Jumper setting for system configuration

- Single 25 MHz clock source

- Single 5V power supply with Winbond advanced low power CMOS process

- 128 pin QFP package

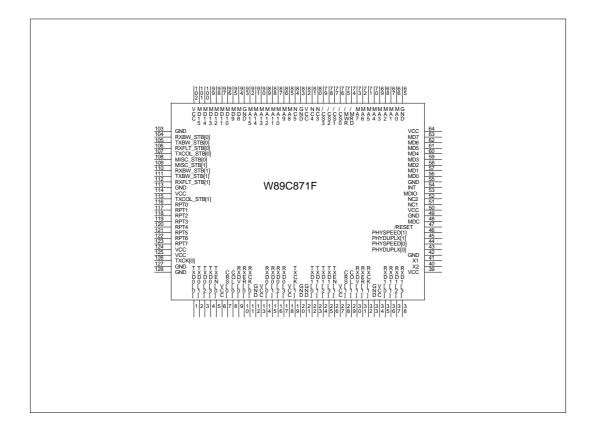

# **PIN ASSIGNMENT**

# **PIN CONFIGURATION**

| MII INTERF | MII INTERFACE PINS |     |                                                                                                                                                                        |  |

|------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.                | I/O | DESCRIPTION                                                                                                                                                            |  |

| CRS[1:0]   | 28,7               | I   | MII Carrier Sense Input of port 1 and port 0.                                                                                                                          |  |

|            |                    |     | Asserted by physical layer device(PHY) when media is busy, and de-asserted when media is idle. CRS[1:0] stay asserted, even at the duration of a collision.            |  |

|            |                    |     | High means carrier is presenting on the medium.                                                                                                                        |  |

| COL[1:0]   | 29,8               | I   | MII Collision input of port 1 and port 0.                                                                                                                              |  |

|            |                    |     | Asserted by PHY device (Physical layer controller) <b>once</b> a collision occurred. It will be asserted and lasted until the collision condition thoroughly vanishes. |  |

|            |                    |     | High means collision is presenting on the transmitting and receiving channel of PHY device.                                                                            |  |

| TXEN[1:0]  | 26,5               | 0   | MII Transmit Enable Output of port 1 and port 0.                                                                                                                       |  |

|            |                    |     | High means transmit enable. Transmitted data on each port                                                                                                              |  |

|           |        |     | will be valid when its responded signal TXEN[1:0] is high.                                                                                                                                                                                                                                                       |  |

|-----------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TXD0[3:0] | 1-4    | 0   | MII Transmit Data of port 0.                                                                                                                                                                                                                                                                                     |  |

|           |        |     | Port 0 transmit data bus. This indicates transmission of activity to an external PHY and is synchronized with TXEN[0]. The bus is valid only when the TXEN[0] is high.                                                                                                                                           |  |

| TXD1[3:0] | 22-25  | 0   | MII Transmit Data of port 1.                                                                                                                                                                                                                                                                                     |  |

|           |        |     | Port 1 transmit data bus. This indicates transmission of activity to an external PHY and is synchronized with TXEN[1]. The bus is valid only when the TXEN[1] is high.                                                                                                                                           |  |

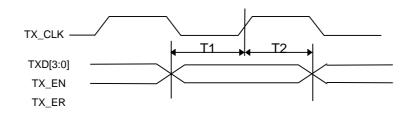

| TXCK[1:0] | 19,126 | I/O | MII Transmit Clock of port 0 and port 1.                                                                                                                                                                                                                                                                         |  |

|           |        |     | Both TXCK[1:0] are continuous uniformed clock from<br>external PHY, which provides the timing reference for<br>TXEN[1:0], TXD1 and TXD0. The TXCK[1:0] is either<br>2.5 MHZ or 25 Mhz clock pulse, determined by each PHY<br>they connected to, respectively. The TXCK is always<br>active after powerup.        |  |

| RXDV[1:0] | 30,9   | I   | MII Receive Data Valid of port 1 and port 0.                                                                                                                                                                                                                                                                     |  |

|           |        |     | Received data valid signal. Both signals are driven by PHY device. <b>They will assert</b> when data is present, and will be de-asserted at the end of the data frame. RXDVs are synchronized with RXCKs. The received data is valid only when RXDV is high.                                                     |  |

| RXD0<3:0> | 14-17  | I   | MII Receive Data of port 0.                                                                                                                                                                                                                                                                                      |  |

|           |        |     | Receive data from port 0. They are driven by PHY;<br>synchronized with <b>RXCK</b> ; valid only when <b>RXDV[0]</b><br>asserts. RXD0[0] is the least significant bit.                                                                                                                                            |  |

| RXD1<3:0> | 35-38  | I   | MII Receive Data of port 1.                                                                                                                                                                                                                                                                                      |  |

|           |        |     | Receive data from port 1. They are driven by PHY; synchronized with RXCK; valid only when RXDV[1] <b>asserts</b> . RXD1[0] is the least significant bit.                                                                                                                                                         |  |

| RXER[1:0] | 31,10  | I   | MII PHY Receive Error of port 1 and port 0.                                                                                                                                                                                                                                                                      |  |

|           |        |     | These pins are driven by PHY device. They indicate that a data conversion error from PHY is detected. The assertion of RXER[1:0] will last for a time longer than a period of RXCK[1:0]. When <b>RXERs assert</b> , W89C871F will report a receive error and a CRC error. High means a receiving error occurred. |  |

| RXCK[1:0] | 32,11  | I   | MII Receive Clock input of port 0 and port 1.                                                                                                                                                                                                                                                                    |  |

|           |        |     | The RXCK[1:0] is either 2.5 MHZ or 25 Mhz clock.<br>RXCKs are active all the time after power-up. RXCK and<br>TXCK are allowed to be asynchronous.                                                                                                                                                               |  |

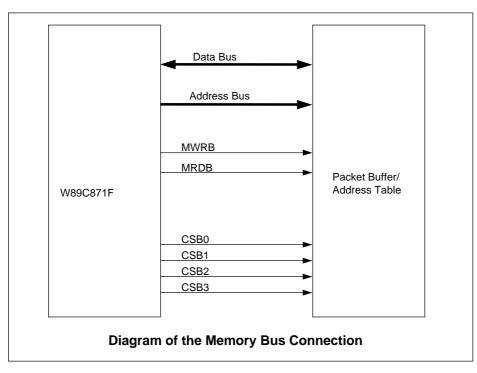

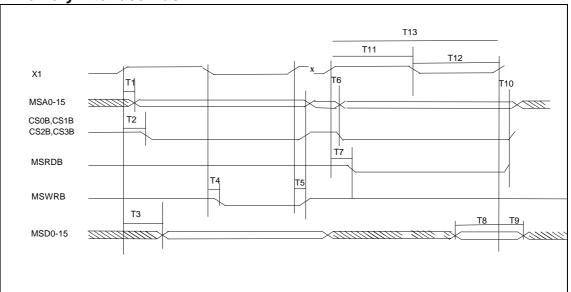

|          | SRAM INTERFACE PINS |      |                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MA[15:0] | 92-85,<br>73-66     | 0    | SRAM Address Bus.<br>W89C871F supports up to 512k bytes SRAM buffer which<br>is capable of being configured to fit 128Kx8 or 64Kx16<br>SRAM, and stores the received packets, addresses and<br>routing information. The MA[15:0] should be directly<br>connected to the A[15:0] of the memory device. |  |  |  |

| MD[15:0] | 101-94,             | I/O/ | SRAM Data Bus.                                                                                                                                                                                                                                                                                        |  |  |  |

|          | 63-56               | Z    | This is a 16-bit width data channel to forward packets<br>between W89C871F and external SRAM devices, and<br>access routing information between W89C871F and<br>external SRAM devices.                                                                                                                |  |  |  |

| MRDB     | 74                  | 0    | SRAM Read Enable.                                                                                                                                                                                                                                                                                     |  |  |  |

|          |                     |      | This signal has SRAM ready to output data to W89C871F.<br>This pin is active low.                                                                                                                                                                                                                     |  |  |  |

| MWRB     | 75                  | 0    | SRAM Write Enable.                                                                                                                                                                                                                                                                                    |  |  |  |

|          |                     |      | This signal has SRAM ready to receive data. This pin is active low.                                                                                                                                                                                                                                   |  |  |  |

| CSB0     | 76                  | 0    | SRAM Chip Select 0.                                                                                                                                                                                                                                                                                   |  |  |  |

|          |                     |      | This pin is internally pulled down and is active low.                                                                                                                                                                                                                                                 |  |  |  |

|          |                     |      | This pin determines the type of memory configuration and bank.                                                                                                                                                                                                                                        |  |  |  |

|          |                     |      | Memory Configuration:                                                                                                                                                                                                                                                                                 |  |  |  |

|          |                     |      | Both CSB0 and CSB1 are used to configured the size and<br>the type of buffer memory after power is on or W89C871F<br>is reset. A 4.7k ohm pull-up resistor has to be connected to<br>CSB0 if 256k bytes buffer memory is specified; Floating<br>CSB0 if 512k bytes buffer memory is specified.        |  |  |  |

|          |                     |      | During the reset operation, W89C871F detects the signal combination of CBS0/CBS1 to tell its memory size and type configuration.                                                                                                                                                                      |  |  |  |

|          |                     |      | The following table shows the memory size configuration in terms of CSB0 and CSB1.                                                                                                                                                                                                                    |  |  |  |

|          |                     |      | CSB0/CSB1 1/1 1/0 0/1 0/0                                                                                                                                                                                                                                                                             |  |  |  |

|          |                     |      | Memory size 64k16x2 128k8x2 64k16x4 128k8x2                                                                                                                                                                                                                                                           |  |  |  |

|          |                     |      | Memory Bank Selection:                                                                                                                                                                                                                                                                                |  |  |  |

|          |                     |      | When CSB0 is active, W89C871F can address the buffer memory space ranged from 0000H to 0FFFH in the configuration mode of 64k16x2 and 64k16x4, or from 0000H to 1FFFH in the configuration mode of 128k8x2 and 128k8x4. See the section Buffer Memory and Bus for details.                            |  |  |  |

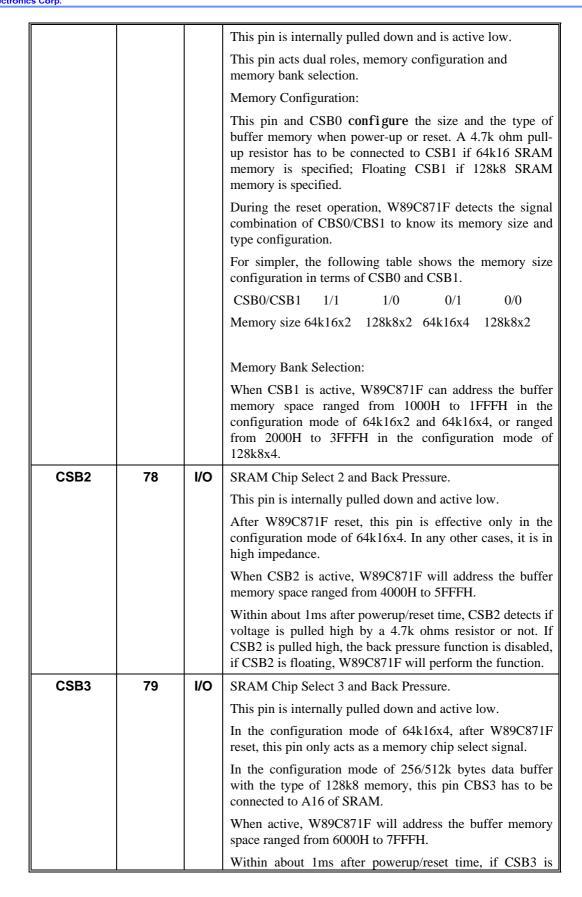

| CSB1     | 77                  | 0    | SRAM Chip Select 1.                                                                                                                                                                                                                                                                                   |  |  |  |

Winbond

pulled high with a 4.7k ohms resistor, W89C871F will issue back-pressure pattern for forwarded packet only. If CSB3 is floating, W89C871F will issue back pressure pattern for any packet, included local packet and forwarded packet.

| LED INTERFACE PINS |         |     |                                                                                                                                                                                                                                                                                                                                                     |  |  |

|--------------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RPT[7:0]           | 123-116 | I/O | LED report output and VLAN frame.                                                                                                                                                                                                                                                                                                                   |  |  |

|                    |         |     | This pin is internally pulled down and active low.                                                                                                                                                                                                                                                                                                  |  |  |

|                    |         |     | After power-up/reset, W89C871F will have the network status output on the RPT[0:7] with different display mode messages determined by hardware settings.                                                                                                                                                                                            |  |  |

|                    |         |     | Device ID Select :                                                                                                                                                                                                                                                                                                                                  |  |  |

|                    |         |     | RPT[0:4] is also used to set ID code for W89C871F being<br>able to be accessed through MDC and MDIO. Setting ID<br>code can be achieved by pulling some of RPT[0:4] high<br>with 4.7k ohms beforehand at system power-up/reset.                                                                                                                     |  |  |

|                    |         |     | Within about 1ms after powerup/reset time, RPT[5:7] have the following special functions.                                                                                                                                                                                                                                                           |  |  |

|                    |         |     | At this time frame, RPT[5] will enable VLAN frame<br>function to allow forwarding VLAN tagged frame with<br>1522 bytes long if it detects a pulled high voltage from a<br>4.7k ohms resistor. If this is floated, W89C871F will<br>process each packet with the maximum of 1518 bytes<br>long.                                                      |  |  |

|                    |         |     | If RPT[6] is connected to a 4.7k ohm pull high resistor, both MII ports will shrink the backoff time with the same scale to speed up packet processing.                                                                                                                                                                                             |  |  |

|                    |         |     | If RPT[7] is connected to a 4.7k ohm resistor for<br>pull high, it will perform discontinuous back pressure<br>function when the buffer utilization reaches threshold.<br>W89C871F will lost one packet after every 55 consecutive<br>back pressure pattern in 100M port and every 23<br>consecutive back pressure pattern are respectively issued. |  |  |

| RXBW_STB[          | 110,104 | 0   | Bandwidth utilization report strobe.                                                                                                                                                                                                                                                                                                                |  |  |

| 1:0]               |         |     | A strobe signal to latch each port network utilization report data.                                                                                                                                                                                                                                                                                 |  |  |

| TXBW_STB[          | 111,105 | 0   | Forwarding ratio report strobe.                                                                                                                                                                                                                                                                                                                     |  |  |

| 1:0]               |         |     | A strobe signal to latch each port forwarding ratio report data.                                                                                                                                                                                                                                                                                    |  |  |

| RXFLT_STB          | 112,106 | 0   | Filtering ratio report strobe.                                                                                                                                                                                                                                                                                                                      |  |  |

| [1:0]              |         |     | A strobe signal to latch each port filtering ratio report data.                                                                                                                                                                                                                                                                                     |  |  |

| TXCOL_ST           | 115,107 | 0   | Collision ratio report strobe.                                                                                                                                                                                                                                                                                                                      |  |  |

| B[1:0]             |         |     | A strobe signal to latch each port collision ratio report                                                                                                                                                                                                                                                                                           |  |  |

|            |         |     | data.                                                                                                                                                                                                                                   |          |             |

|------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

| MISC_STB[1 | 108,109 | I/O | Miscellaneous Report Strobe.                                                                                                                                                                                                            |          |             |

| :0]        |         |     | These pins are internally pulled down and active low                                                                                                                                                                                    |          |             |

|            |         |     | These two pins are used to latch each port network status report in terms of memory buffer full, Tx/Rx activity, speed, duplex and collision and have them showed on RPT[0:7]. See the section of LED Displaying Interface for details. |          |             |

|            |         |     | Duplex Definit                                                                                                                                                                                                                          | ion:     |             |

|            |         |     | The duplex mode is determined by the combination of MISC_STB[0] and PHYDUPLX from the connected PHY that has completed auto-negotiation. When this pin is active, duplex mode will present on RPT[4].                                   |          |             |

|            |         |     | The following table is the combination of the MISC_STB[0] and PHYDUPLX. There are two kinds of PHYDUPLX output for different brands of PHY, either low or high.                                                                         |          |             |

|            |         |     | MISC_STB[0] PHYDUPLX Duplex mode                                                                                                                                                                                                        |          |             |

|            |         |     | 0                                                                                                                                                                                                                                       | 0        | full duplex |

|            |         |     | 0                                                                                                                                                                                                                                       | 1        | half duplex |

|            |         |     | 1 0 half duplex                                                                                                                                                                                                                         |          |             |

|            |         |     | 1 1 full duplex                                                                                                                                                                                                                         |          |             |

|            |         |     | Speed Definition                                                                                                                                                                                                                        | on:      |             |

|            |         |     | The speed of each port is determined by the combination of MISC_STB[1] and PHYSPEED from the connected PHY which has completed auto-negotiation. When this pin is active, Line speed will present on RPT[3].                            |          |             |

|            |         |     | The following table is the combination of MISC_STB[1] and PHYSPEED. Like PHYDUPLX, PHYSPEED also has two kinds of output for brands of PHY.                                                                                             |          |             |

|            |         |     | MISC_STB[1]                                                                                                                                                                                                                             | PHYSPEED | Port Speed  |

|            |         |     | 0                                                                                                                                                                                                                                       | 0        | 100M        |

|            |         |     | 0                                                                                                                                                                                                                                       | 1        | 10 <b>M</b> |

|            |         |     | 1                                                                                                                                                                                                                                       | 0        | 10 <b>M</b> |

|            |         |     | 1                                                                                                                                                                                                                                       | 1        | 100M        |

| MISCELLANEOUS |                                                                         |   |                       |  |

|---------------|-------------------------------------------------------------------------|---|-----------------------|--|

| RSTB          | 47                                                                      | I | System Reset.         |  |

|               | Active low. Minimum 50 us reset pulse width is required when VDD valid. |   |                       |  |

| X1            | 41                                                                      | I | System Clock Source : |  |

|                        |       |     | It is required to offer a steady and stable 25Mhz clock<br>source with +/- 50 PPM. This pin should be directly<br>connected to clock source. Oscillator or crystal is<br>available.                     |  |

|------------------------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| X2                     | 40    | I   | System Clock Source :                                                                                                                                                                                   |  |

|                        |       |     | This pin should be directly connected to clock source if crystal is applied; floating if an oscillator is applied.                                                                                      |  |

| PHYSPEED               | 46,44 | I   | External PHY Device Speed for port 1 and port 0:                                                                                                                                                        |  |

| [1]<br>PHYSPEED<br>[0] |       |     | These two pins detect the line speed status from the responded PHY to determine each port operating speed. W89C871F will blend this bit with MISC_STB[1] to display the speed of each port of W89C871F. |  |

| PHYDUPLX               | 45,43 | I   | External PHY Device Duplex for port 1 and port 0:                                                                                                                                                       |  |

| [1]<br>PHYDUPLX<br>[0] |       |     | These two pins detect the duplex mode status from the responded PHY to determine each port duplex mode. W89C871F will blend this bit with MISC_STB[0] to display the duplex mode of each port.          |  |

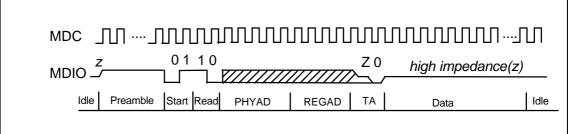

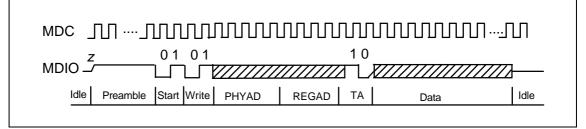

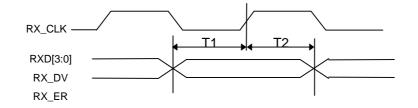

| MDC                    | 48    | I   | MII Reference Clock :                                                                                                                                                                                   |  |

|                        |       |     | A reference clock for accessing MII management data.<br>The maximum clock rate is 25Mhz.                                                                                                                |  |

| MDIO                   | 53    | I/O | MII Data Input/Output Bus :                                                                                                                                                                             |  |

|                        |       |     | MII management data bus.                                                                                                                                                                                |  |

| INT                    | 54    | 0   | Interrupt Output :                                                                                                                                                                                      |  |

|                        |       |     | An interrupt output indicates that there is an abnormal <b>event</b> detected by W89C871F itself.                                                                                                       |  |

|     | POWER&GROUND PINS                                                 |   |               |  |

|-----|-------------------------------------------------------------------|---|---------------|--|

| VDD | 6,13,18,<br>27,34,39<br>,50,64,8<br>2,102,11<br>4,124,12<br>5     | Ρ | Power supply. |  |

| VSS | 12,20,21<br>,33,42,4<br>9,55,65,<br>83,93,10<br>3,113,12<br>7,128 | G | Ground.       |  |

| NC  | 51,52,80<br>,81,84,                                               | G | No contact.   |  |

Note :

P : power pin; G : ground pin; I : input pin; O : output pin; I/O : bidirection pin;

I/O/Z : bidirection pin with high-z state

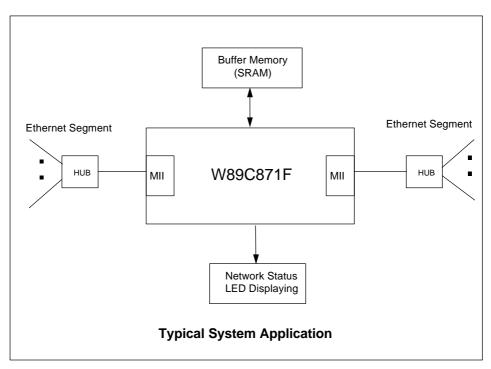

# SYSTEM DIAGRAM

Constructing a dual speed hub or a single 10/100M converter, you can use W89C871F to design them with minimum cost and effort. Like the following example of system application, a typical application, only SRAMs and LED driver has to be implemented. Switching and its related functions are integrated on a chip. This is not only simplifying design effort but saving its size, as well as assembly time.

Fig. 1

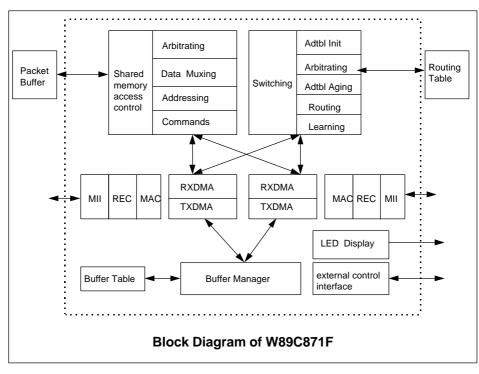

# **BLOCK DIAGRAM**

#### Fig. 2

# FUNCTIONAL DESCRIPTION

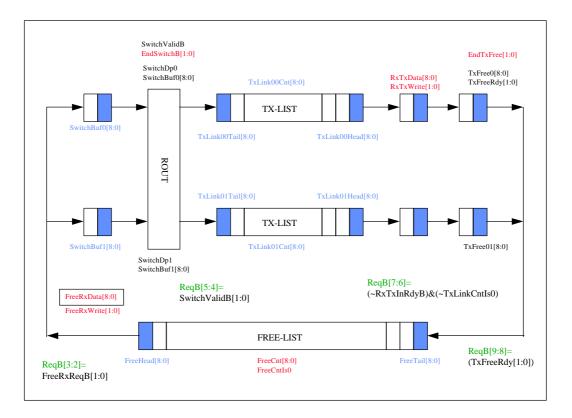

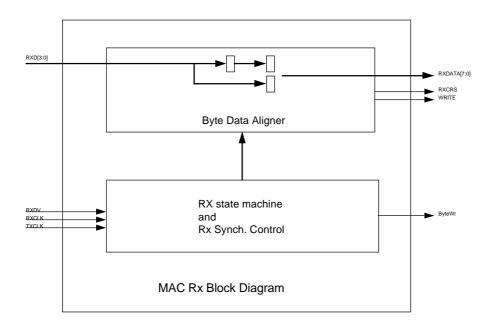

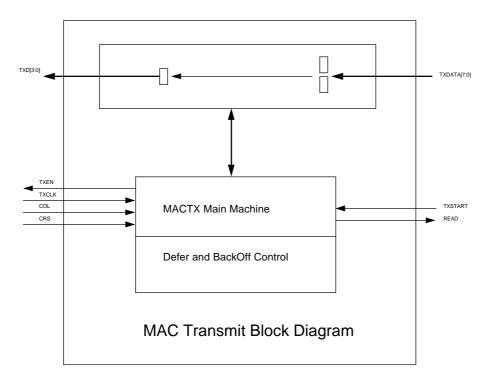

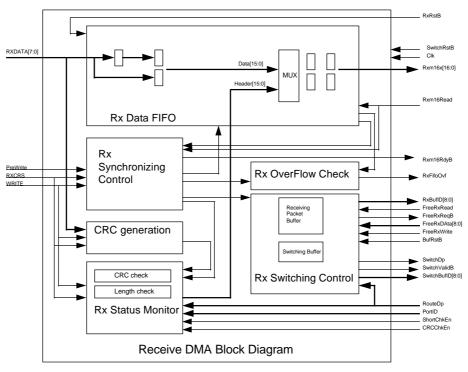

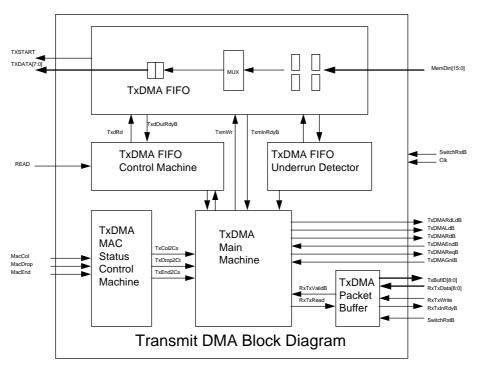

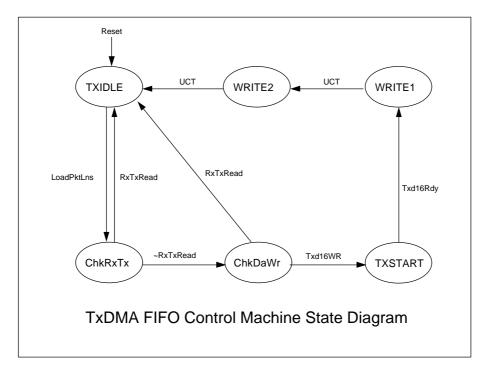

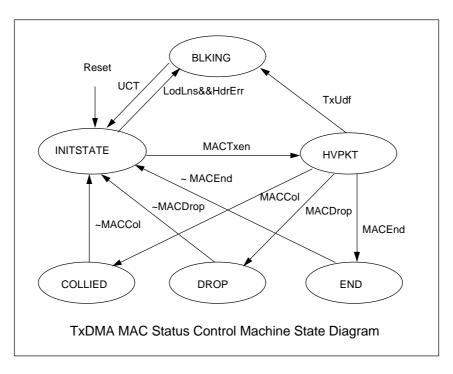

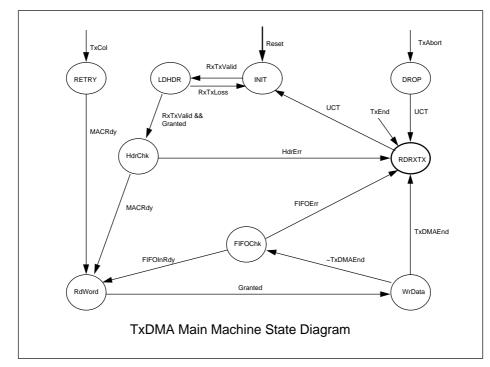

W89C871F is constructed by the function blocks shown in above diagram. It consists of the function units of switch fabric, buffer management and memory access control, routing, address self-learning and aging, media access controller(MAC) and its DMA, and LED display logic. They will be detailedly described in the coming paragraph.

# **Buffer Memory and Bus**

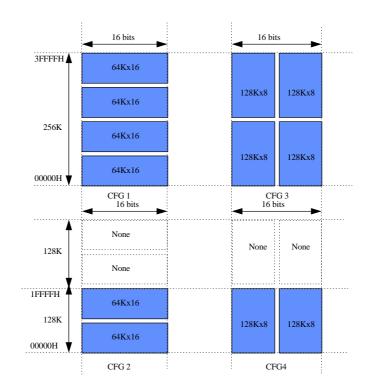

W89C871F is implemented a configurable memory interface, tied with external SRAM, to construct the packet buffer memory. The size of buffer memory can be configured as either 256K bytes or 512K bytes in the aspect of buffer capacity. There are four configurations available: 64Kx16x2, 64Kx16x4, 128Kx8x2 and 128Kx8x4. All of them have 16-bit data width that can afford totally 400Mbps aggregation bandwidth at 25M Hz operating frequency.

For selecting one configuration out of four, W89C871F supports two pins CSB0 and CSB1 to reach this at power-up stage. After power is on, W89C871F reset itself to its preset initial status. But some status, like memory configuration, are detected from outside at this time interval. CSB0 and CSB1 are some of them. CSB0 and CSB1 must be previously set by hardware before powered on. As soon as power-up, W89C871F detects CSB0 and CSB1 to the memory configuration. CSB0 is for the size of packet buffer and CSB1 is for the type of memory device.

Usually, they are output pins and connect to Chip Select pin(CS) of SRAM, but during the power-on stage after reset, they are input pins for detecting configuration. At this period, W89C871F latches these two signals to initialize internal configure table for the size of packet buffer and its type. The following table shows the combination of the CSB0 and CSB1 at the power-on time. Both CSB0 and CSB1 are pull down internally. When preset it to high, a 4. 7k ohmresistor must be serialized to VDD. When preset it to low, just let it floating.

| CSB0 | CSB1 |                                                         |  |  |  |  |  |  |  |

|------|------|---------------------------------------------------------|--|--|--|--|--|--|--|

| 1    | 1    | packet buffer size = 256K bytes, memory device = 64Kx16 |  |  |  |  |  |  |  |

| 1    | 0    | packet buffer size = 256K bytes, memory device = 128Kx8 |  |  |  |  |  |  |  |

| 0    | 1    | packet buffer size = 512K bytes, memory device = 64Kx16 |  |  |  |  |  |  |  |

| 0    | 0    | packet buffer size = 512K bytes, memory device = 128Kx8 |  |  |  |  |  |  |  |

|      |      |                                                         |  |  |  |  |  |  |  |

| Та | ble | 1 |

|----|-----|---|

|----|-----|---|

For the above four memory configurations, each corresponds to a different memory space. The following diagram(Fig. 3) shows all configuration and each address map they will be. In CFG1 and CFG3, they are configured to the maximum size of buffer memory. In the former, 4 pcs of 64k16 bytes SRAMs are used; in the later, 4 pcs of 128k8 bytes SRAMs are used. Both are total 512k bytes.

In CFG2 and CFG4 modes, they are the same as that of CFG1 and CFG3 modes, except they are configured to be a half of buffer memory in CFG1 and CFG3.

Publication Release Date:April 1998 Revision A1

To successfully configure the memory buffer in a practical application, CSB3 and CSB4 have to be involved. For simplicity, we compose a configure table in which the most left column is the symbols on W89C871F and the remains are the symbols at the memory devices. CSB2 is **active only in the CFG1 mode and is** floating in the rest modes. CSB3 is floating in CFG2 mode; connected to A16 of SRAM in CFG3&4 modes; connected to Chip Select(CS1) of SRAM in CFG1.

| W89C871F | CFG1     | CFG2     | CFG3       | CFG4       |

|----------|----------|----------|------------|------------|

| D0 ~ D15 | D0 ~ D15 | D0 ~ D15 | D0~D7/D0~7 | D0~D7/D0~7 |

| A0 ~ A15 | A0 ~ A15 | A0 ~ A15 | A0 ~ A15   | A0 ~ A15   |

| CSB3     | CS1      | Floating | A16        | A16        |

| CSB2     | CS1      | Floating | Floating   | Floating   |

| CSB1     | CS1      | CS1      | CS1/CS1    | Floating   |

| CSB0     | CS1      | CS1      | CS1/CS1    | CS1/CS1    |

| MWRB     | MWRB     | MWRB     | MWRB       | MWRB       |

| MRDB     | MRDB     | MRDB     | MRDB       | MRDB       |

Table 2

In the fig. 4, the practical connections between W89C871F and the external packet buffer are shown. There are four optional pull up resistors shown, which depend on the configurations of the size of buffer memory and the type of memory.

Fig. 4

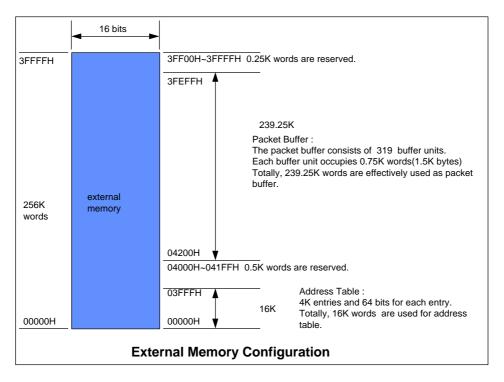

# **External Memory Configuration**

The external memory is divided into two portions, buffer memory, a place to temporarily store the packets ready to be delivered, and routing information table, a place to store every nodes address and its routing information, came from both ports.

As the description above, W89C871F supports either 256k bytes or 512k bytes, in both of which the first 16k words, counted from the address 0000H to 03FFFH, are reserved for routing information, each of which occupies a consecutive 64 bits, and next, 0.5k words are reserved for future. The mapping is shown in the Fig. 5.

In 512k-byte mode, 239.25k words are allocated for packet buffer that is totally divided to 319 pre-partitioned buffer units each of which is fixed in 1536 bytes long.

In 256k-byte mode, there are totally 158 buffer units that were pre-partitioned and are addressed from 04200H by step of 600H bytes.

# **VLAN-tagged Frame**

Normally, Ethernet packet is 1518 bytes long, but in some special cases, the packet length is more than 1518 bytes. The most well known is VLAN-tagged frame of which the length of packet is 1522 bytes. W89C871F supports this VLAN-tagged packet by only connecting a 4.7k ohms resistor to pull RPT[5] high.

There are at most four thousands (4096) of address entry stored in the address look-up table of W89C871F. Each of them is **composed of the information included** used flag, port number, aging flag, vendor ID part I, aging index and vendor ID part II. All of which will clearly explain in the next paragraph.

The memory map below detailedly shows the allocated space and its address range. In the diagram of fig. 5, 512k bytes buffer memory is used.

Fig. 5

# Address Table Format

The table 5 shows the format of the address entry and the structure of the first five entries each of which has the same structure as that of the rest entries. There are totally 32k bytes reserved for the address look-up table, in which each entry is allocated continuous 4 words of memory, i.e. 64 bits, starting from the address in bytes of 0000H to 7FFFH of the external memory device.

As table 5 shows, address table stores the routing information and is linked to the buffer memory through the transfer of the buffer management unit. When a packet comes, W89C871F will parse the packet and memorize(the so-called self-learning) its source MAC address, and stores this and some specific routing information such as FLG, AGFLG etc., in the address table with the format as Table 5 no matter where this packet was from.

If W89C871F finds that destination address and source address are from the same network segment, i.e. has the same port number, it will not forward the packet and keep quiet listening the source port. If destination and source is located at different network segment, W89C871F will first parse this packet to learn if it is a good packet or not. In case of short packet or packet with errors happened, W89C871F discards the packet or will store it to buffer memory if the packet is good, and meanwhile, write its source address, destination address and routing information to address table, and packet data to buffer memory respectively. This guarantees the packets in the buffer are good.

After having updated routing information, W89C871F starts counting down the aging index of the new updated address entry. When time is out, default value 5 minutes, the address entry will be marked available by cleaning AGFLG and no more count down for this address entry. In W89C871F, when an address entry is accessed, the aging index is updated to be BFH and also set AGFLG.

In half duplex operation mode, if buffer memory is full and next packet is coming, the back pressure flow control of W89C871F will be invoked. W89C871F issues a JAM packet to the

source port to eliminate the possible errors and to suppress transmit action temporarily on that network segment. This will last for a period of time as long as the length of the incoming packet.

If a collision happens, the MAC of W89C871F will start backoff timer to wait for a period of random time and transmit again. When collisions happen continuously 16 times, the packet ready to be forwarded will be discarded and release its buffer space. If W89C871F can not get media, the packet ready to be transferred will be kept in the buffer memory all the time.

In the cases of broadcast and multicast, W89C871F unconditionally forwards all the packet and updates specific entries in the address table to which the source physical address points.

When the opposed segment is idle, W89C871F will forward the packet from memory to that port according to the sequence of the content of the buffer identifier in the buffer ID link list which is controlled by buffer management control unit.

The detail meaning of each field in the address entry is described as following.

FLG: This flag bit determines the content of the bit[0:11] of the address entry in the address look-up table. It is dependent on the address learning machine to set or reset this bit. When set, the content of bit[0:11] of the address entry is composed by the lower twelve bits of the physical address of the source node. When reset, composed by the upper half bits of the lower 24 bits of physical address of source node.

If there is a MAC of which the lower 12 bits of the physical address is mapped into an address entry which is not available in the address look-up table, then an address collision happens. In this case, W89C871F will automatically choose the next available address entry.

PNO: Port number bit. When set, means the packet is from port 1, when reset, means the packet is from port 0. W89C871F receives each packet from either port 0 or port 1, but will be released immediately when it detects that the destination port of the received packet is the same as its source port. If the destination port is different from its source port, the packet will be stored in buffer memory. W89C871F then updates the address entry and starts to count down aging index.

For the case of which there are two same MAC address from different port, W89C871F will have the packet stored in the same buffer location and update the content of the address entry storing the routing information of the previous packet alternately according to their arrival time.

AGFLG: Aging flag bits. These two bits are used to designate if the address entry is in use or not. When set, means in use, when reset, means available.

ID pattern: This field contains the content of the bits 0-11 or bits 12-23 of the Ethernet physical address. If FLG bit is set, this field contains the content of the lower twelve bits of the first half of the physical address; if reset, it contains the content of the upper twelve bits of the first half of the physical address.

Vendor ID part I: This field contains the content of the bit39-24 of the Ethernet physical address. This is a part of the Organizational Unique Identity code(OUI) and should be applied to IEEE.

Aging Index: This index indicates if the entry is time-out. If it is time-out, i.e., this entry has not been accessed within five minutes, then W89C871F will reset AGFLG bit and release the address entry for other use. W89C871F checks this field many times a second, and updates its content as BFH if it is accessed. In W89C871F, Default aging time is five minutes.

Vendor ID part II: This field contains the content of the bit47-40 of the Ethernet physical address. A full OUI code is constructed by combining this field and Vendor ID part I. This is a part of the Organizational Unique Identity code(OUI) and should be applied to IEEE.

Reserved: This field is free for future use.

|       | 1       |                                     |                                    |                      |   |   | 1 | r | r – | r |                  |     |     |   |   |   |   |

|-------|---------|-------------------------------------|------------------------------------|----------------------|---|---|---|---|-----|---|------------------|-----|-----|---|---|---|---|

| No.of | memo    | В                                   | В                                  | В                    | В | В | В | В | В   | В | В                | В   | В   | В | В | В | В |

| entry | . addr. | 15                                  | 14                                 | 1                    | 1 | 1 | 1 | 9 | 8   | 7 | 6                | 5   | 4   | 3 | 2 | 1 | 0 |

|       |         |                                     |                                    | 3                    | 2 | 1 | 0 |   |     |   |                  |     |     |   |   |   |   |

| 0000H | 0000H   | flg                                 | pno                                | ID Pattern (12 bits) |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0001H   | vendor ID part 1                    |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0002H   | age index vendor ID p               |                                    |                      |   |   |   |   |     |   |                  | par | t 2 |   |   |   |   |

|       | 0003H   | reserved                            |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

| 0001H | 0004H   | flg                                 | lg pno ageflg ID Pattern (12 bits) |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0005H   | vendor ID part 1                    |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0006H   | age index                           |                                    |                      |   |   |   |   |     |   | vendor ID part 2 |     |     |   |   |   |   |

|       | 0007H   | reserved                            |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

| 0002H | 0008H   | flg pno ageflg ID Pattern (12 bits) |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0009H   | vendor ID part 1                    |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 000aH   | age index                           |                                    |                      |   |   |   |   |     |   | vendor ID part 2 |     |     |   |   |   |   |

|       | 000bH   | reserved                            |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

| 0003H | 000cH   | flg pno ageflg ID Pattern (12 bits) |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 000dH   | vendor ID part 1                    |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 000eH   | age index                           |                                    |                      |   |   |   |   |     |   | vendor ID part 2 |     |     |   |   |   |   |

|       | 000fH   | reserved                            |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

| 0004H | 0010H   | flg                                 | g pno ageflg ID Pa                 |                      |   |   |   |   |     |   | attern (12 bits) |     |     |   |   |   |   |

|       | 0011H   | vendor ID part 1                    |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

|       | 0012H   | age index                           |                                    |                      |   |   |   |   |     |   | vendor ID part 2 |     |     |   |   |   |   |

|       | 0013H   | reserved                            |                                    |                      |   |   |   |   |     |   |                  |     |     |   |   |   |   |

Table 3.

# The Operation of the Address table

## Initialization

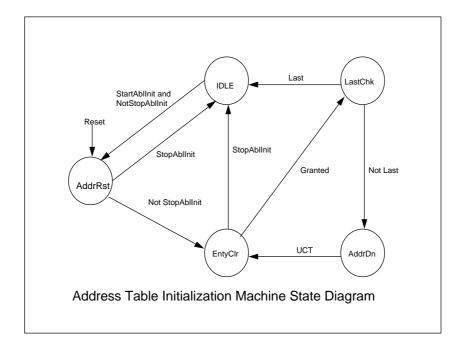

After power-up/reset, the initialization of the address table starts. The hardware reset can be reached by power-up or hardwiring the reset pin to ground. The following diagram shows the initial operation of the address table.

At the initial phase, W89C871F will have the first word(16 bits width) of each address entry of the address table cleaned as 0000H, in which a continuous 64-bit long memory was allocated to each address entry. Hence, this 0000H will be in orderly written to each entry, addressed at 1FFEH, 1FFAH, ..., 000AH, 0006H, and 0002H. After finished initialization, the state machine enters the idle state and waits for servicing the incoming packet.

During initialization, W89C871F allows to stop the initial operation for some purpose by resetting the bit 7 of the control register. This will have some un-initialized address entries

uncertained so that less than 4k address entries are available within 5 minutes after power up. All 4k address entries are available at 5 minutes later after power-up. The bit 7 of the control register has the highest priority on the machine control. The state machine will stay at the idle state whenever the StopAbIInit signal is asserted.

The following diagram shows the initial sequence and its related state in the next paragraph.

In Figure 6, we will see how the state machine of the address table works at the initial phase. Here, we will explain the meaning of the states and the events to next state.

## IDLE : Idle state.

The state machine always stays at the IDLE state whenever compulsorily stopping the initialization operation(StopAblInit) happens or the initialization is normally completed(Last). If the initial command from the control register is issued, the state machine will enter AddrRst state to perform the initialization of the address table. Normally, the address state machine always completes the initialization and is ready for identifying the routing information status of the income packet.

#### AddrRst :Address reset state.

This is the entry point of the address state machine. After power on hardwire reset, the state machine automatically enters this state. Another way is by programming the control register

through MDIO to have StartAblInit set and StopAblInit reset, shown in the diagram. This will have address state machine interrupted and force to be in the AddrRst state. In W89C871F, no matter it is reset by hardware or software, the state machine starts formatting the address entries in sequence from the top high address of the address table, i.e. 4096 to 0.

#### EntyClr : Address entity clear state.

A request to write 0000H to the address table will be issued to get a grant from buffer management control unit to clean the first 16 bits of each address entry when the address state machine stays at the EntyClr state.

#### LastChk :Last entity check state.

As soon as the address entry clean request is finished, the address state machine enters LastChk state to check if the current address entry being serviced is the last one in the address table or not. If the last one is reached, the address state machine will go to the IDLE state, otherwise, it will enter to the AddrDn state.

#### AddrDn :Address count down state.

In this state, the address state machine will count down by one and point to the next address entry in the address table.

### **Address Aging**

It is possible to move a MAC address crossing over a network bridge, especially for notebook PC. In such a case, W89C871F can detect the change soon and update its address table accordingly. W89C871F implements an intelligent address recognition mechanism to support this operation. It supports hardware aging function with default value 300 seconds which is fixed and no need to re-configure it. W89C871F checks each address entry 191 times per second based on 25Mhz system operation clock. If any address entry is not accessed within 300 seconds, it will be removed automatically from the address table. There is an age timer to generate the trigger signal pulse with the width of 120ns for starting aging the address entry of the address table. The frequency of the trigger signal is depended on the LifeTime setting. If LifeTime is set to be 1, it means that aging time is one second. If the LifeTime is set to be 100, it means the aging time is 100 seconds.

For getting the time reference, there is a 5 bits ripple counter implemented to generate a 781.25 Khz clock based on 25 Mhz Clock input. This 781.25 Khz clock is fed to the input of a twenty bits count down counter which was preloaded an initial value the same as the LifeTime had been set previously. Each time the counter reaches zero, W89C871F will issue an AgeTrig pulse as well as reload the value of LifeTime to the twenty bits count down counter for next trigger. The LifeTime can be set by programming the age time register through MDIO and MDC, MII serial management interface.

When AgeTrig pulse is issued, the age index of all the 4096 address entries will be counted down by 1. Hence, if LifeTime is set to be 2 and all the age index of the 4096 address entries are 191(BFH), all the 4096 entries can be aged out 2 seconds later.

The aging mechanism can not be started if the bit 3 of the control register is reset to low, and the aging timer is inhibited as well.

The following equation shows the above conclusion, based on 25Mhz operating clock and LifeTime=2.

40ns x 32 x 2 x 4906 x 191 = 2.00278016 second

Vinbond

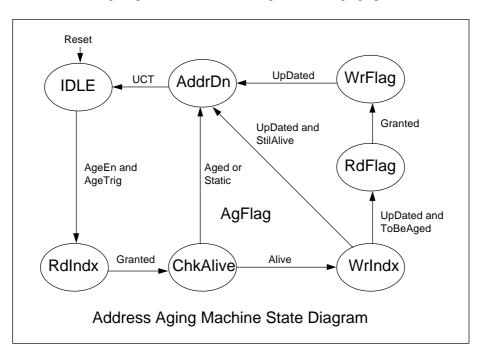

The following diagram shows the state diagram of the aging operation.

## The Operation of Address Aging

The address aging operation shown above states how it works detailedly. After power-up or reset, W89C871F have the address aging state machine entered into IDLE state to wait for servicing. When a packet is receiving, both AgeEn and AgeTrig will be set to allow accessing the age index of the address entry(RdIndx state). If granted by buffer management control unit, the address aging device reads the age index and parse it to learn if the address entry is still alive. If it is not alive, then the address aging device will enter into AddrDn state. If it is alive, the address aging device will update the address entry and directly enter into AddrDn state. If the address aging device detects the address entry is time-out, it will update its contents and reset its Ageflg and Age Index to mark available for this entry. The following paragraph describes the states of the address aging state machine and its relations.

IDLE : Idle state.

The address aging device always keeps in the IDLE state whenever the aging function is disabled or the aging timer is still counting down. The machine will leave the IDLE state if the aging function is enabled and the AgeTrig signal is received.

#### RdIndx :Read the age index of the address entry

At this state, the address aging machine issues a data read request to the buffer management control device to get a grant for accessing the aging index of the address entry, stored in SRAM. The address aging machine reads the third word of the address entry to get the age index value.

#### ChkAlive : Age index check state.

After the age index is read and parsed, the aging state of the address entry will be checked. The aging state has three types: alive, aged and static. Alive state means that the age index of the address entry is larger than 00H but smaller than or equal to C0H. Aged state means that the address entry has released for other's use, and has an age index with 00H. Static state means that the address entry is blank and available, and its age index has valued other than 00H~BFH.

#### WrIndx :Update aging index.

At the WrIndx state, the address aging machine issues a write request to the buffer management control unit for getting a grant to update the age index of the current address entry. The age index will be decreased by one each time the age index is updated, i.e. the age index is count down when the age index is updated.

#### AddrDn :Address count down state.

The addressing logic of the aging device will count down the pointer of the address entry when the address aging machine enters AddrDn state.

#### RdFlag:Read back the age flag state.

The age flag indicates the aging state of the address entry. If it is still alive, the age flag is equal to 1H. If it is aged out, the age flag is equal to 0H. If it is static, the age flag is equal to 3H. The age flag with the value 2H means nothing. Not all the aging operation needs to update the age flag. The address aging machine will update the age flag only when the age index counting down from 01H to 00H. Before updating the age flag, the rest bits of the first word of the address entry pointer currently pointed to must be read back for keeping the consistency.

#### WrFlag:Write the age flag state.

After the data of the first word of the address entry has been read and parsed, the address aging machine updates the age flag only at the WrFlag state.

# THE OPERATION OF THE PACKET SWITCH

### Data Flow of Switching

The switching operation of W89C871F is receiving incoming packets from ports, and searching the address table for the destination MAC address according to the destination address of the packet, and then forwarding the packet to the other port if the port number of destination and source is different. For multicast and broadcast packets, W89C871F forwards packets directly

without identifying. During the time to forward the packet, W89C871F abstracts all the source MAC address(SA) and keep them, accompanied with other information, in the address table with the structure form as shown in the Table 3. This is hence building an address table for filtering. The destination MAC address is used to tell the port where a packet should be routed to.

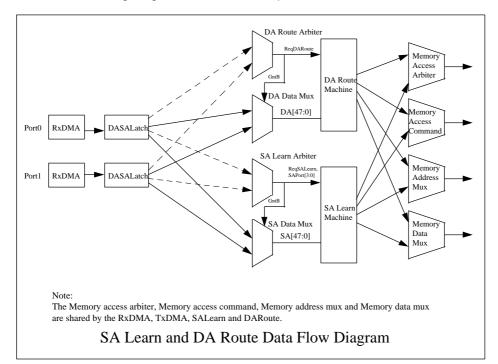

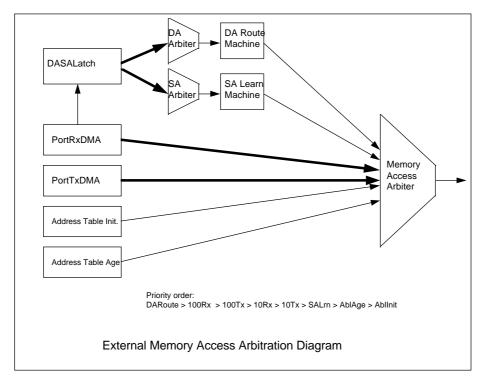

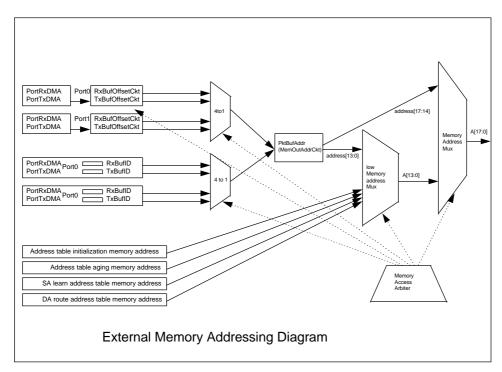

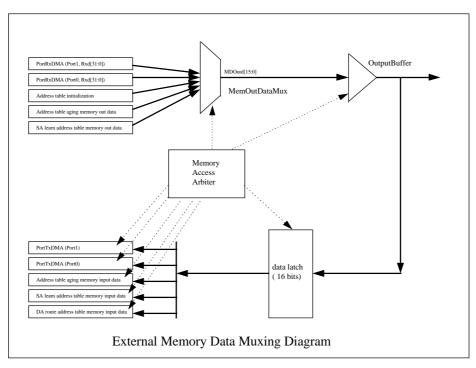

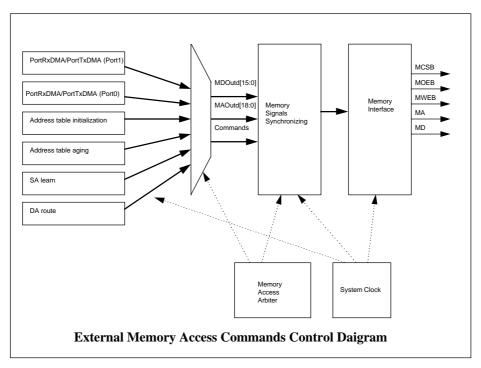

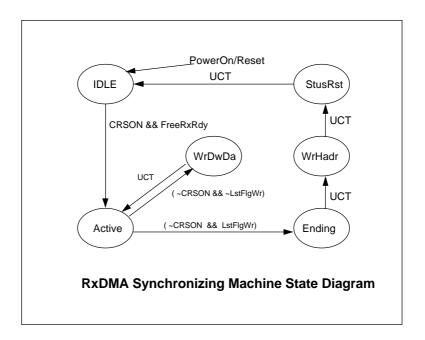

The following diagram shows how the packet data flows.

All the packet is received by RXDMA in which a receive FIFO is constructed to queue the data temporarily. The DASALatch extracts the destination address(DA) and the source address(SA) from RXDMA device. When DASALatch completed latching DA and SA, it will issue a request to the address state machine for routing and learning. The address state machine includes the SA learning machine and DA routing machine. The former is responsible for serving the learning request, and the later is responsible for the routing request. These two operations are done by the cooperation of the memory access arbiter, memory access command control and memory address/data MUX. They may conflict while accessing the buffer memory at the same time. It is arbitrated by memory access arbiter. Due to implement such an intelligent memory access arbiter, W89C871F can perform a loading balance-like operation between the communication of 10M and 100M network segments. In the case, 10M network transmits/receives packets slower 10 times than Fast network does, the packets from 100M segment will always wait for 10M segment digestion or the port to 100M segment will always wait for getting the packets. This could degrade the system performance. W89C871F improved this by balancing the packet loading ratio for 10M and 100M Ethernet.

## MAC Address Learning Procedures

W89C871F implements a smart address searching algorithm to perform the operation of searching, learning, and updating the address entry of the address table. For the MAC address learning operation, W89C871F extracts the source MAC address(SA) of an incoming packet and searches if the same one existed in the address table. If SA is found, W89C871F updates the aging index, if not found, W89C871F creates and updates the address entry of the address table with all data with the structure shown in Table 3, and stores the packet in the buffer memory pointed by buffer ID. But packet will be released soon if the destination MAC address(DA) is a unicast address and the address was found in the address table and the port number is the same as that of source port. This means the packet is filtered.

Physical address is sorted to be three types of address:unicast, multicast and broadcast. If the first bit of the DA is 0, the packet is unicast, which means that the packet can only be received by a single network node. If the first bit of the DA is 1, the packet is multicast, which means a group of network nodes will receive it. If DA is composed of all 1s, the packet is broadcast, a special type of multicast, all nodes in the network will receive it.

According to the rule of IEEE. The MAC address, 48 bits long, consists of two parts, one is the vendor ID field, higher 24 bits, and the other is the customers` serial number, lower 24 bits. The address searching algorithm compares the full address of the source MAC address(SA). The 24 bits of the serial number is divided to two halves. Either of these two halves may be used as an address index of the address entry of the address table. There is a search flag defined for the search operation of the address table. The search flag is 0 if the address learning machine searches the address table based on the lower half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address table based on the upper half of the 24 bits serial number of the source MAC address of the received packet.

During the learning procedures, there will be three words read for each entry search. They will include, 8 bits age index, 24 bits vendor ID, 1 bit input port ID, 1 bit addressing flag, 2 bits age flag and 12 bits serial number. The age flag indicates that if the address entry is in use or available or not. If alive, the age flag is equal to 1H. If dead, the age flag is equal to 0H and means available. The value of 2H and 3H of the age flag means nothing and will not be allowed. An alive address entry means that the value of the age index is larger than 00H and lower than C0H and is active. An aged address entry means that the address entry means that the address entry means that the address entry has an age index equal to 00H and has been released. The age index with number larger than C0 has not been defined and will be not allowed.

If the address table is full, and no one address entry is aged out, and a packet with new source address comes at this moment, W89C871F will perform the address recognition procedures the same as that of normal case, i.e. update the oldest address entry with the new information of the received packet. Thus the old one is wiped out from the address table.

A hit to an address entry must meet the following requirements, this means the matched was found.

1) The contents of the 24-bit vendor ID in Table 3. = that of the upper half 24 bits of the source MAC address of the received packet.

2) The age index is not equal to 00H and not larger than BFH.

- 3) The age flag is 1H.

- 4) The addressing flag is 0

5) The serial number, i.e. ID pattern bits of the data structure in Table 3, is equal to the contents of the upper 12 bits of the serial number of the source MAC address of the received packet.

6) search flag is 0

or

1) The contents of the 24-bit vendor ID in Table 3. = that of the upper half 24 bits of the source MAC address of the received packet.

2) The age index is not equal to 00H and not larger than BFH.

3) The age flag is 1H.

4) The addressing flag is 1

5) The serial number, i.e. ID pattern bits of the data structure in Table 3, is equal to the contents of the upper 12 bits of the serial number of the source MAC address of the received packet.

6) search flag is 1

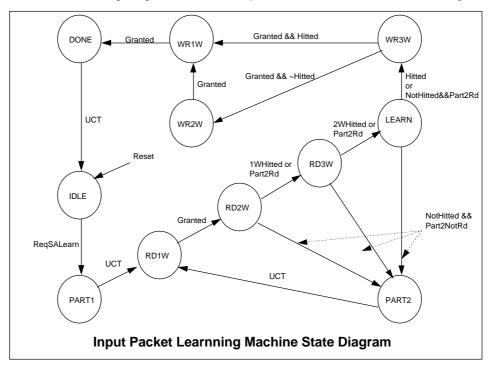

The following diagram shows the operation of the address self-learning.

Fig. 9

## IDLE :idle state.

The address learning machine keeps idle when no packet is coming or system is power-up/reset or state machine just finished the job.

#### PART1 :set search flag state.

The address learning machine resets the search flag to 0 at this state. The bits 0-11 of the serial number of the source MAC address (SA) will be used as the address search index.

#### PART2 :set search flag state.

The address learning machine resets the search flag to 1 at this state. The bits 12-23 of the serial number of the source MAC address will be used as the address search index.

#### RD1W, RD2W, RD3W :read data state.

The address learning machine read the first 3 words of the address entry at the state of the RD1W, RD2W and RD3W respectively.

### LEARN :learning state.

The address learning machine identifies if an address entry is matched or not at this state.

#### WR1W, WR2W, Wr3W :write entity data state.

The address learning machine will write the routing data to the first 3 words of the address entry at the state of WR1W, WR2W and WR3W respectively.

DONE :Done state.

# DA Routing Procedure(address recognition and aging)

W89C871F forwards the packet between ports according to destination MAC address(DA). In the routing procedures, the DA routing machine first do the address recognition which detects if the packet is an unicast one. If yes, it will search the address table to find the matched address entry and compare if the port number of the matched address entry is the same as the source port. If they are different, then the packet is forwarded, otherwise, the packet is discarded. If the DA can not be found in the address table, W89C871F will unconditionally forward the packet to the opposed network segment, as if it is multicast/broadcast packet and memorize its source address and related information in the address table with the form of the structure as table 3.

When finishing the address recognition, W89C871F checks if the following requirements are matched. They are addressing flag, age flag, serial number, and vendor ID etc. Should they meet the requirements, the routing machine will route the packet to its destination.

- 1) The age flag is 1H.

- 2) The addressing flag is 0

3) The serial number, i.e. ID pattern bits of the data structure in Table 3, is equal to the contents of the upper 12 bits of the serial number of the destination MAC address of the received packet.

4) search flag is 0

or

1) The age flag is 1H.

2) The addressing flag is 1

3) The serial number, i.e. ID pattern bits of the data structure in Table 3, is equal to the contents of the lower 12 bits of the serial number of the destination MAC address of the received packet.

4) search flag is 1

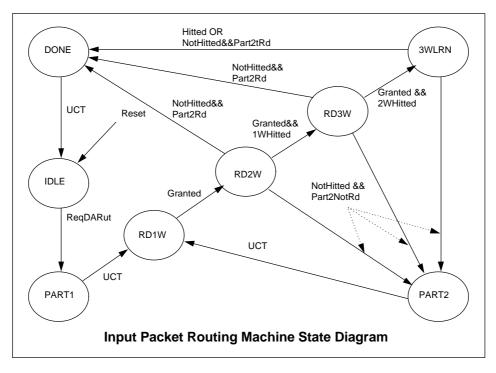

The operation of the routing state machine is shown in the figure 10. After powerup/reset or no routing activity, the routing state machine stays at IDLE state. When capturing DA of a received packet, the routing state machine enters the PART I state which searches the matched address entry based on the address index claimed by the content of the lower twelve bits of the serial number of the physical address of the received packet. And next, read the first word(16 bits) of the matched address entry, which is composed of address entry flag, port number, age flag and ID pattern bits. After extracting these data, the routing machine parses and identifies them if the address entry is a matched one which meet the requirements listed above. If matched, the second and the third word will be reading in order, which are composed of age index and vendor identifier. If unmatched, the routing machine will alternatively use the higher twelve bits of the serial number of the DA of the received packet and repeat the operation it just did.

With them, the routing machine can detect if the received packet has the same vendor ID as that of the matched entry, and if the matched address entry is available or in use. If available, it means the DA does not exist in the address table. If it is in use, routing state machine will set search flag as 0, and alternatively, re-searches another address entry addressed by the content of the higher twelve bits of the serial number of the DA of the received packet and repeat the operation it did. If the entry found in second time is still in use, it means that the DA does not exist in the address table. The packet will be forwarded directly.

When finished parsing the first three words and ascertained that the DA of the received packet was found in the table, the port ID will be compared to decide if the packet should be forwarded or not. When finishes, routing state machine will enter the DONE state and next to IDLE state.

The following paragraph describes the operation and meaning of the states of the routing machine.

## IDLE :

idle state.

The routing machine keeps idle when no routing activity or after power-up/reset.

#### PART1:

set search flag state 1.