TOSHIBA BIPOLAR LINEAR INTEGRATED CIRCUIT SILICON MONOLITHIC

# TA2058F

# POWER DRIVER IC FOR CD PLAYER

TA2058F is a power driver IC developed for CD players. This IC have built-in 4 channel BTL power amplifiers which drives focus-coil and tracking coil for 3-beam pickup head, disc motor and feed motor.

### **FEATURES**

- 4 channel BTL linear divers

- Few external parts

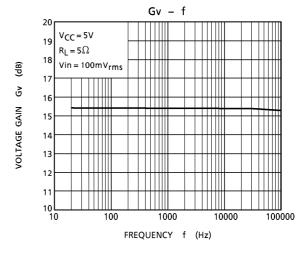

- Fixed voltage gain

- : Gv = 15dB (Typ.)

- High output power

- :  $V_{OM}1 = 5V_{p-p}$  (Typ.)  $V_{CC} = 5V$ ,  $R_L = 50HM$

- :  $V_{OM}2 = 6V_{p-p}$  (Typ.)  $V_{CC} = 6V$ ,  $R_L = 50HM$

- Thermal shut down protector

- Input reference voltage short protector

- Small Package

- : Power-flat package 1mm pitch 20pins

- Operation Supply Voltage Range

- :  $V_{CC(opr)} = 4.0 \sim 10.0 \text{V} \text{ (Ta} = 25 ^{\circ}\text{C)}$

Weight: 0.8g (Typ.)

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

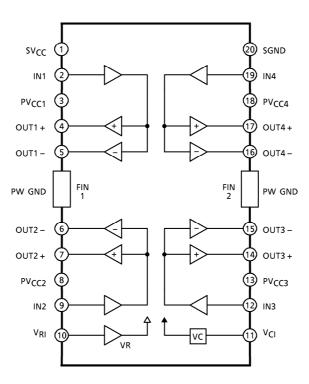

# **BLOCK DIAGRAM**

# **TERMINAL EXPLANATION**

| TERMINAL<br>No. | SYMBOL            | FUNCTION                                                                                                                         | EQUIVALENT CIRCUIT                |  |  |  |

|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| 1               | SVCC              | Supply terminal of small signal                                                                                                  |                                   |  |  |  |

| 2               | IN1               | Input for CH1  ■ Not biased inside.                                                                                              | SGND SGND                         |  |  |  |

| 3               | PV <sub>CC1</sub> | Supply terminal of output stage for CH1  • Supply terminal of output stage are not connected to other channel terminal.          | SV <sub>CC</sub> PV <sub>CC</sub> |  |  |  |

| 4               | OUT1+             | Non-inverted output for CH1                                                                                                      | OUT                               |  |  |  |

| 5               | OUT1 –            | Inverted output for CH1                                                                                                          |                                   |  |  |  |

| FIN1            | PGND              | Power GND  • Connected to FIN2 and substrate.                                                                                    | PGND                              |  |  |  |

| 6               | OUT2 –            | Inverted output for CH2                                                                                                          | Same as CH1                       |  |  |  |

| 7               | OUT2+             | Non-inverted output for CH2                                                                                                      | 1                                 |  |  |  |

| 8               | PV <sub>CC2</sub> | Supply terminal of output stage for CH2                                                                                          | ]                                 |  |  |  |

| 9               | IN2               | Input for CH2                                                                                                                    | 7                                 |  |  |  |

| 10              | V <sub>RI</sub>   | <ul> <li>Input reference voltage</li> <li>Under condition of V<sub>R1</sub>≤ 1.8V, internal bias circuit is shut off.</li> </ul> | 30kΩ 39kΩ 39kΩ                    |  |  |  |

| 11              | V <sub>CI</sub>   | Output reference voltage  ■ V <sub>OUT</sub> = V <sub>CI</sub> = (V <sub>CC</sub> – VF) / 2                                      | SONS OND SONS                     |  |  |  |

| 12              | IN3               | Input for CH3                                                                                                                    | Same as CH1                       |  |  |  |

| 13              | PV <sub>CC3</sub> | Supply terminal of output stage for CH3                                                                                          | 1                                 |  |  |  |

| 14              | OUT3 +            | Non-inverted output for CH3                                                                                                      | 4                                 |  |  |  |

| 15              | OUT3 -            | Inverted output for CH3                                                                                                          | C                                 |  |  |  |

| FIN2            | PGND              | Power GND                                                                                                                        | Connected to FIN1                 |  |  |  |

| 16              | OUT4 -            | Inverted output for CH4                                                                                                          | Same as CH1                       |  |  |  |

| 17              | OUT4+             | Non-inverted output for CH4                                                                                                      | -                                 |  |  |  |

| 18              | PV <sub>CC4</sub> | Supply terminal of output stage for CH4                                                                                          | -                                 |  |  |  |

| 19              | IN4               | Input for CH4                                                                                                                    |                                   |  |  |  |

| 20              | SGND              | Small signal GND                                                                                                                 |                                   |  |  |  |

### **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC        | SYMBOL                  | RATING          | UNIT |

|-----------------------|-------------------------|-----------------|------|

| Supply Voltage        | Vcc                     | 14              | V    |

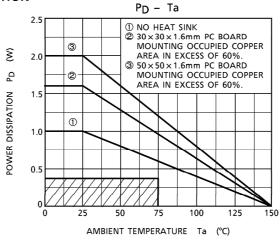

| Power Dissipation     | P <sub>D</sub> (Note 1) | 2 (Note 2)      | W    |

| Operating Temperature | T <sub>opr</sub>        | <b>- 30∼85</b>  | °C   |

| Storage Temperature   | T <sub>stg</sub>        | <b>-</b> 55∼150 | °C   |

(Note 1): Mounted on 50mm x 50mm x 1.6mm size board with copper area 60% over.

(Note 2) : Derated above  $Ta = 25^{\circ}C$ , in the proportion of  $62.5 \text{mW}/^{\circ}C$ .

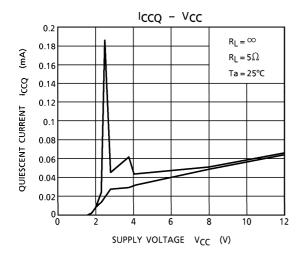

# **ELECTRICAL CHARACTERISTICS**

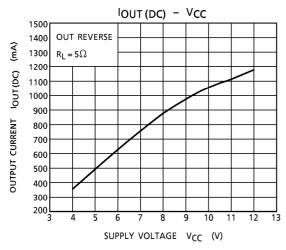

(Unless otherwise specified,  $V_{CC} = 5V$ ,  $R_L = 5\Omega$ ,  $R_S = 620\Omega$ ,  $V_{RI} = 2.1V$ , f = 1kHz,  $T_0 = 25^{\circ}C$ )

|                                                  |                     | TEST         |                                              |       |      |      |                       |

|--------------------------------------------------|---------------------|--------------|----------------------------------------------|-------|------|------|-----------------------|

| CHARACTERISTIC                                   | SYMBOL              | CIR-<br>CUIT | TEST CONDITION                               | MIN.  | TYP. | MAX. | UNIT                  |

| Operating Voltage                                | Vcc                 | _            |                                              | 4.0   | _    | 10.0 | ٧                     |

| Quiescent Current                                | <sup>I</sup> ccQ    | _            | Vin = $0$ , $R_L = OPEN$                     | 20    | 35   | 60   | mA                    |

| Input Offset Current                             | ΙΝ                  | _            | VIN = 2.1V                                   |       | 250  | 800  | nΑ                    |

| V <sub>RI</sub> Terminal Offset Current          | l <sub>10</sub>     | _            | V <sub>RI</sub> = 2.1V                       | _     | 35   | 120  | μΑ                    |

|                                                  | Vo os1              | _            | $V_{CC} = 5V$ , $Rg = 0\Omega$               | - 30  | _    | 30   | mV                    |

| Output Offset Voltage                            | Vo os2              | _            | $V_{CC} = 8V$ , $Rg = 0\Omega$               | - 50  | _    | 50   |                       |

|                                                  | VO OS3              | _            | $V_{CC} = 12V$ , $Rg = 0\Omega$              | - 100 |      | 100  |                       |

| Reference Output Voltage                         | Vout                | _            |                                              |       | 2.1  | _    | V                     |

| Maximum Output Voltage                           | V <sub>OM</sub> 1   | _            | V <sub>CC</sub> = 5V                         | 4.0   | 5.0  | _    | V <sub>p-p</sub>      |

| Maximum Output Voltage                           | V <sub>OM</sub> 2   | _            | V <sub>CC</sub> = 6V                         | 5.0   | 6.0  | _    |                       |

| Voltage Gain                                     | Gv                  | _            | Vin = 100mV <sub>rms</sub>                   | 14.5  | 15.5 | 16.5 | dB                    |

| Frequency Response                               | fc                  | _            | Vin = 100mV <sub>rms</sub>                   | _     | 100  | _    | kHz                   |

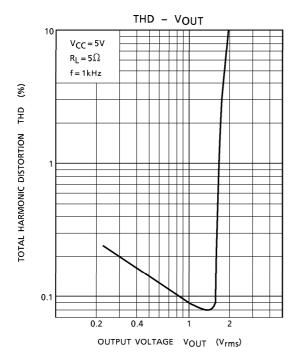

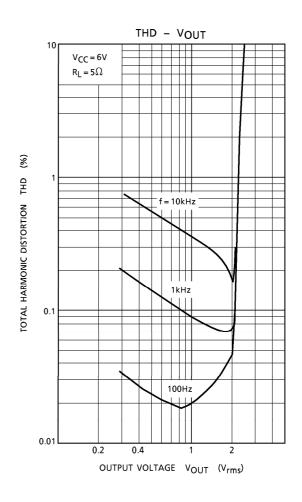

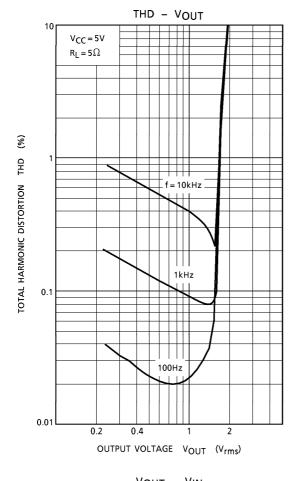

| Total Harmonic Distortion                        | THD                 | _            | Vin = 100mV <sub>rms</sub>                   | _     | - 50 | _    | dB                    |

| Slew Rate                                        | S.R.                | <b>—</b>     | Vout = 2V <sub>p-p</sub>                     | _     | 1.0  | _    | <b>V</b> / μ <b>s</b> |

| Cross Talk                                       | C.T.                | _            | Vout = 1V <sub>rms</sub>                     | _     | - 60 | _    | dB                    |

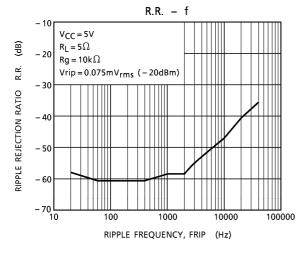

| Ripple Rejection Ratio                           | R.R.                | _            | frip = 100Hz,<br>Vrip = 100mV <sub>rms</sub> | _     | - 60 | _    | dB                    |

| Thermal Shut Down<br>Temperature                 | T <sub>TSD</sub>    | _            | Chip temperature                             |       | 150  |      | °C                    |

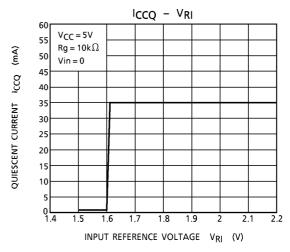

| V <sub>RI</sub> ~GND Short Protection<br>Voltage | V <sub>RI</sub> OFF | _            |                                              | 1.4   | 1.6  | 1.8  | V                     |

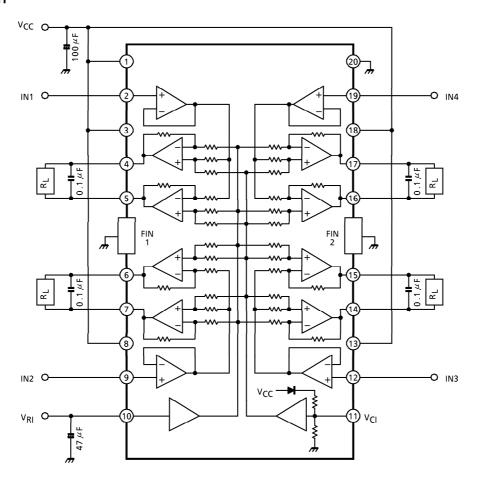

### **TEST CIRCUIT**

### **HSOP 20 POWER DISSIPATION**

(Note) In case of normal use, power dissipation of IC only is oblique line portion.

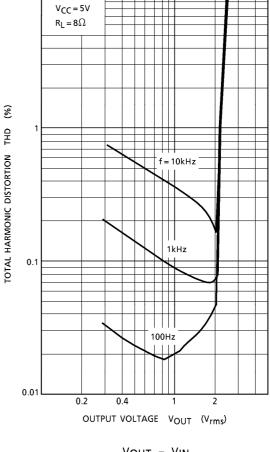

THD - VOUT

### PRECAUTION USE

- Input Stage

- Input stages are consisted of differential circuit of NPN Tr, and have built-in IB compensation circuit.

- Built-in Driver

- Each channel driver consists of BTL configuration linear amplifier.

- Voltage gain is fixed: G<sub>V</sub> = 15.5dB (Typ.)

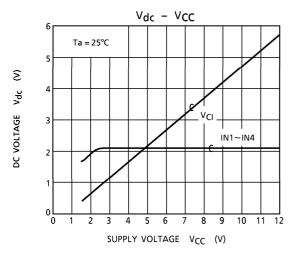

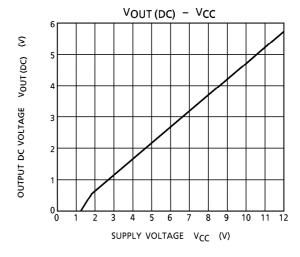

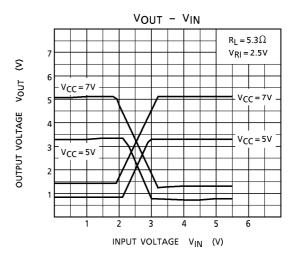

- Voltage loss for output stage is 2V<sub>BE</sub> + V<sub>CE</sub> (sat) for positive cycle, V<sub>CE</sub> (sat) for negative cycle, because of no-bootstrap circuit. So, output DC voltage is designed as less than 1/2V<sub>CC</sub>.

- V<sub>RI</sub> Terminal

- VRI is reference voltage terminal for input signal.

- If reference voltage from servo IC drop less than 1.8V, protection circuit operates and shut off bias circuit inside. This operation is to prevent load from moving undesirably in case of V<sub>RI</sub> drop for accident or some reason.

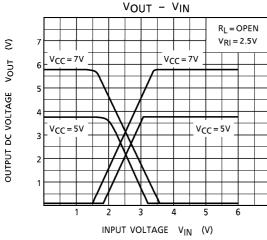

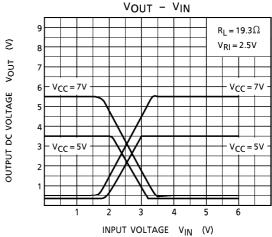

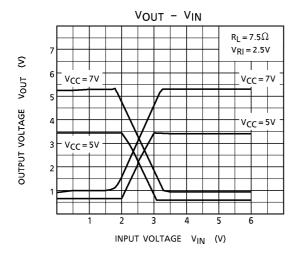

- V<sub>CI</sub> Terminal

- Output DC voltage is determined by circuit of this terminal inside as;

VCI = VOUT (DC) = (VCC VF) / 2

- Output signal dynamic range is depend on V<sub>CC</sub>. On the other hand, input signal dynamic range

is determined by V<sub>R</sub>I as mentioned and voltage gain is fixed inside. So, maximum output voltage

does not increase as V<sub>CC</sub> increases.

- Because of BTL configuration, Ripple Rejection Ratio does not improve not much when capacitor is connected to VCI terminal to GND.

- GND

- Large signal GND is for output stage and small signal GND is for stages from input circuit to pre-output stage.

- These GND pins are not connected inside.

- Phin① and Phin② are connected to Bedflame, and it is connected to substrate.

- It is advised that you make a Printed Board layout of small signal GND and large signal GND should be isolated each other.

- Oscillation preventive capacitor

- We recommend to use the capacitor of  $0.1\mu\text{F}$ , between each output terminals. But perform the temperature test to check the oscillation allowance, since the oscillation allowance is varied according to the causes described below.

- 1) Supply voltage

- 2) Ambient temperature

- 3) Load impedance

- 4) Capacity value of condenser

- 5) Kind of condenser

- 6) Layout of Printed board

- ullet We recommend to connect Pass-condenser, which is about 10 to  $100 \mu {

m F}$  between V<sub>RI</sub> terminal and GND

- V<sub>CI</sub> terminal is recommend to use "OPEN".

# OUTLINE DRAWING HSOP20-P-450-1.00 Unit : mm 1.0TYP 16.5MAX 16.0±0.2 16.5MAX

Weight: 0.8g (Typ.)

0.92±0.2