# Microcomputer Components

8-Bit CMOS Single-Chip Microcontroller

SAB 80C515 / SAB 80C535

### High-Performance 8-Bit CMOS Single-Chip Microcontroller

SAB 80C515/80C535

#### **Preliminary**

SAB 80C515/80C515-16 CMOS microcontroller with factory mask-programmable ROM SAB 80C535/80C535-16 CMOS microcontroller for external ROM

- 8 K × 8 ROM (SAB 80C515 only)

- 256 × 8 RAM

- Six 8-bit I/O ports, one input port for digital or analog input

- Three 16-bit timer/counters

- Highly flexible reload, capture, compare capabilities

- Full-duplex serial channel

- Twelve interrupt vectors, four priority levels

- 8-bit A/D converter with 8 multiplexed inputs and programmable internal reference voltages

- 16-bit watchdog timer

- Boolean processor

- Most instructions execute in 1 μs (750 ns)

- 4 μs (3 μs) multiply and divide

- External memory expandable up to 128 Kbytes

- Backwardly compatible with SAB 8051

- Functionally compatible with SAB 80515

- Idle and power-down mode

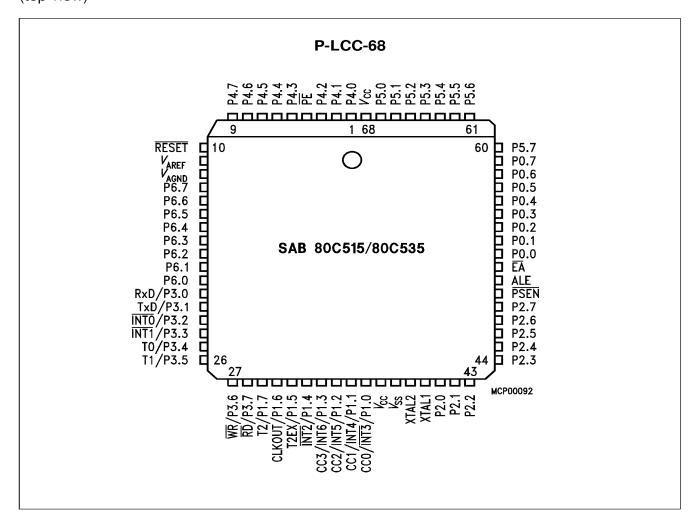

- Plastic leaded chip carrier package: P-LCC-68

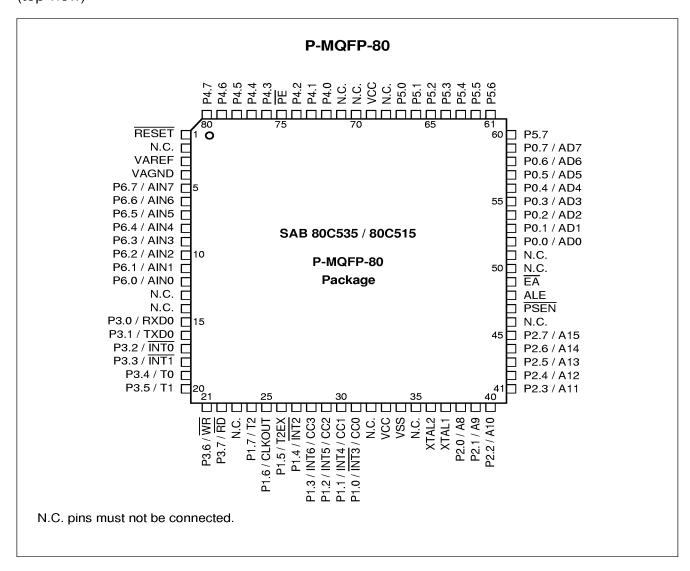

- Plastic Metric Quad Flat Package P-MQFP-80

- Two temperature ranges available:

0 to 70 °C (for 12, 16, 20 MHz)

40 to 85 °C (for 12, 16 MHz)

The SAB 80C515/80C535 is a powerful member of the Siemens SAB 8051 family of 8-bit microcontrollers. It is designed in Siemens ACMOS technology and is functionally compatible with the SAB 80515/80535 devices designed in MYMOS technology.

The SAB 80C515/80C535 is a stand-alone, high-performance single-chip microcontroller based on the SAB 8051/80C51 architecture. While maintaining all the SAB 80C51 operating characteristics, the SAB 80C515/80C535 incorporates several enhancements which significantly increase design flexibility and overall system performance.

In addition, the low-power properties of Siemens ACMOS technology allow applications where power consumption and dissipation are critical. Furthermore, the SAB 80C515/80C535 has two software-selectable modes of reduced activity for further power reduction: idle and power-down mode.

The SAB 80C535 is identical with the SAB 80C515 except that it lacks the on-chip program memory. The SAB 80C515/80C535 is supplied in a 68-pin plastic leaded chip carrier package (P-LCC-68) or in a plastic metric quad flat package (P-MQFP-80).

There are versions for 12, 16 and 20 MHz operation and for 16 MHz operation and for extended temperature ranges - 40 to 85 °C. Versions for extended temperature range - 40 to + 110 °C are available on request.

### **Ordering Information**

| Туре                       | Ordering<br>Code | Package   | Description<br>8-Bit CMOS Microcontroller                                 |

|----------------------------|------------------|-----------|---------------------------------------------------------------------------|

| SAB 80C515-N               | Q67120-DXXXX     | P-LCC-68  | with mask-programmable ROM, 12 MHz                                        |

| SAB 80C535-N               | Q67120-C0508     | P-LCC-68  | for external memory, 12 MHz                                               |

| SAB 80C515-N-T40/85        | Q67120-DXXXX     | P-LCC-68  | with mask-programmable ROM,<br>12 MHz<br>ext. temperature – 40 to + 85 °C |

| SAB 80C535-N-T40/85        | Q67120-C0510     | P-LCC-68  | for external memory, 12 MHz ext. temperature – 40 to + 85 °C              |

| SAB 80C515-16-N            | Q67120-DXXXX     | P-LCC-68  | with mask-programmable ROM, 16 MHz                                        |

| SAB 80C535-16-N            | Q67120-C0509     | P-LCC-68  | for external memory, 16 MHz                                               |

| SAB 80C535-16-N-<br>T40/85 | Q67120-C0562     | P-LCC-68  | for external memory, 16 MHz ext. temperature – 40 to + 85 °C              |

| SAB 80C535-20-N            | Q67120-C0778     | P-LCC-68  | for external memory, 20 MHz                                               |

| SAB 80C535-M               | Q67120-C0857     | P-MQFP-80 | for external memory, 12 MHz                                               |

| SAB 80C515-M               | Q67120-DXXXX     | P-MQFP-80 | with mask-programmable ROM, 12 MHz                                        |

| SAB 80C535-M-T40/85        | Q67120-C0937     | P-MQFP-80 | for external memory, 12 MHz ext. temperature – 40 to + 85 °C              |

| SAB 80C515-M-T40/85        | Q67120-DXXXX     | P-MQFP-80 | with mask-programmable ROM,<br>12 MHz<br>ext. temperature – 40 to + 85 °C |

Notes: Versions for extended temperature range – 40 to + 110 °C on request.

The ordering number of ROM types (DXXXX extension) is defined after program release

(verification) of the customer.

#### **Pin Configuration**

(top view)

### **Pin Configuration**

(top view)

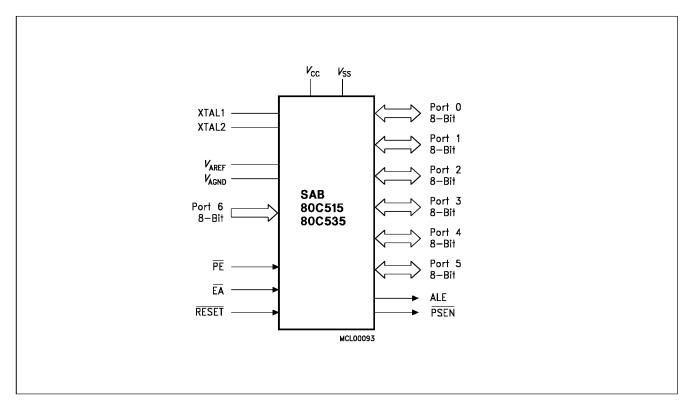

**Logic Symbol**

### **Pin Definitions and Functions**

| Symbol                | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80 | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|-----------------|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P4.0-P4.7             | 1-3, 5-9        | 72-74,<br>76-80  | I/O                     | Port 4 is an 8-bit bidirectional I/O port with internal pullup resistors. Port 4 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 4 pins being externally pulled low will source current (I <sub>IL</sub> , in the DC characteristics) because of the internal pullup resistors. |

| PE                    | 4               | 75               | I                       | Power saving mode enable A low level on this pin enables the use of the power saving modes (idle mode and power-down mode). When PE is held on high level it is impossible to enter the power saving modes.                                                                                                                                                                   |

| RESET                 | 10              | 1                | I                       | Reset pin A low level on this pin for the duration of two machine cycles while the oscillator is running resets the SAB 80C515. A small internal pullup resistor permits power-on reset using only a capacitor connected to $V_{\rm SS}$ .                                                                                                                                    |

| $V_{AREF}$            | 11              | 3                |                         | Reference voltage for the A/D converter                                                                                                                                                                                                                                                                                                                                       |

| $\overline{V_{AGND}}$ | 12              | 4                |                         | Reference ground for the A/D converter                                                                                                                                                                                                                                                                                                                                        |

| P6.7-P6.0             | 13-20           | 5-12             |                         | Port 6 is an 8-bit undirectional input port. Port pins can be used for digital input if voltage levels simultaneously meet the specifications for high/low input voltages and for the eight multiplexed analog inputs of the A/D converter.                                                                                                                                   |

| Symbol    | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80 | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----------------|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0-P3.7 | 21-28           | 15-22            | I/O                     | Port 3 is an 8-bit bidirectional I/O port with internal pullup resistors. Port 3 pins that have1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 3 pins being externally pulled low will source current ( $I_{\rm IL}$ , in the DC characteristics) because of the internal pullup resistors. Port 3 also contains the interrupt, timer, serial port and external memory strobe pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate. The secondary functions are assigned to the pins of port 3, as follows: |

|           |                 |                  |                         | <ul> <li>RxD (P3.0): serial port's receiver data<br/>input (asynchronous) or data input/<br/>output (synchronous)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                 |                  |                         | - TxD (P3.1): serial port's transmitter data output (asynchronous) or clock output (synchronous)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |                 |                  |                         | - INTO (P3.2): interrupt 0 input/timer 0 gate control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |                 |                  |                         | - INT1 (P3.3): interrupt 1 input/timer 1 gate control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |                 |                  |                         | - T0 (P3.4): counter 0 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                 |                  |                         | - T1 (P3.5): counter 1 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                 |                  |                         | WR (P3.6): the write control signal latches the data byte from port 0 into the external data memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |                 |                  |                         | - RD (P3.7): the read control signal enables the external data memory to port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Symbol    | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80 | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|-----------------|------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.7-P1.0 | 29-36           | 24-31            | I/O                     | is an 8-bit bidirectional I/O port with internal pullup resistors. Port 1 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 1 pins being externally pulled low will source current ( <i>I</i> <sub>1L</sub> in the DC characteristics) because of the internal pullup resistors. The port is used for the low-order address byte during program verification. Port 1 also contains the interrupt, timer, clock, capture and compare pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to operate (except when used for the compare functions). The secondary functions are assigned to the port 1 pins as follows:  — INT3/CC0 (P1.0): interrupt 3 input/compare 0 output/capture 0 input |

|           |                 |                  |                         | <ul> <li>INT4/CC1 (P1.1): interrupt 4 input/<br/>compare 1 output/capture 1 input</li> <li>INT5/CC2 (P1.2): interrupt 5 input/<br/>compare 2 output/capture 2 input</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           |                 |                  |                         | <ul> <li>INT6/CC3 (P1.3): interrupt 6 input/<br/>compare 3 output/capture 3 input</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |                 |                  |                         | - INT2 (P1.4): interrupt 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |                 |                  |                         | - T2EX (P1.5): timer 2 external reload trigger input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |                 |                  |                         | - CLKOUT (P1.6): system clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           |                 |                  |                         | - T2 (P1.7): counter 2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Symbol         | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80 | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-----------------|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

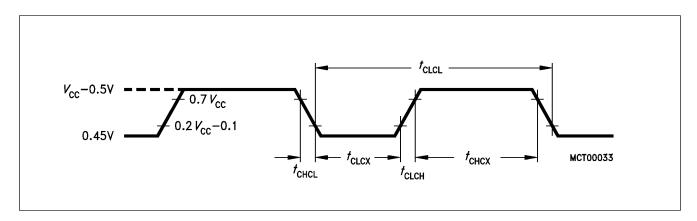

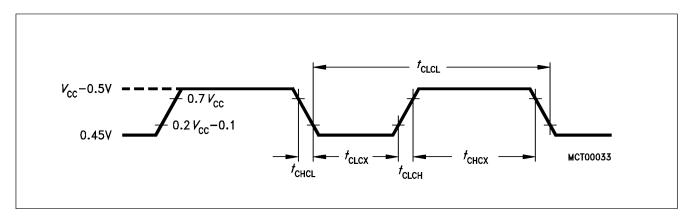

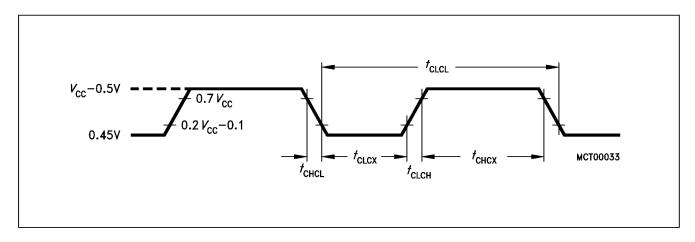

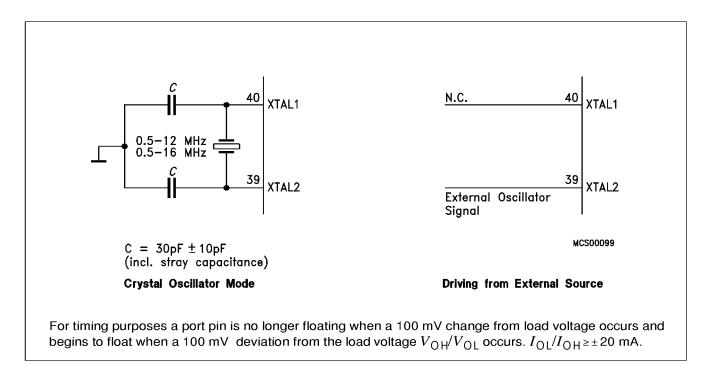

| XTAL2<br>XTAL1 | 39<br>40        | 36<br>37         |                         | Input to the inverting oscillator amplifier and input to the internal clock generator circuits.  XTAL1  Output of the inverting oscillator amplifier. To drive the device from an external clock source, XTAL2 should be driven, while XTAL1 is left unconnected. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is divided down by a divide-by-two flip-flop. Minimum and maximum high and low times and rise/fall times specified in the AC characteristics must be observed.                                                                                                                                                                                                                     |

| P2.0-P2.7      | 41-48           | 38-45            | I/O                     | is an 8-bit bidirectional I/O port with internal pullup resistors. Port 2 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 2 pins being externally pulled low will source current ( <i>I</i> <sub>IL</sub> , in the DC characteristics) because of the internal pullup resistors. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX@DPTR). In this application it uses strong internal pullup resistors when issuing 1's. During accesses to external data memory that use 8-bit addresses (MOVX@Ri), port 2 issues the contents of the P2 special function register. |

| Symbol    | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80 | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-----------------|------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

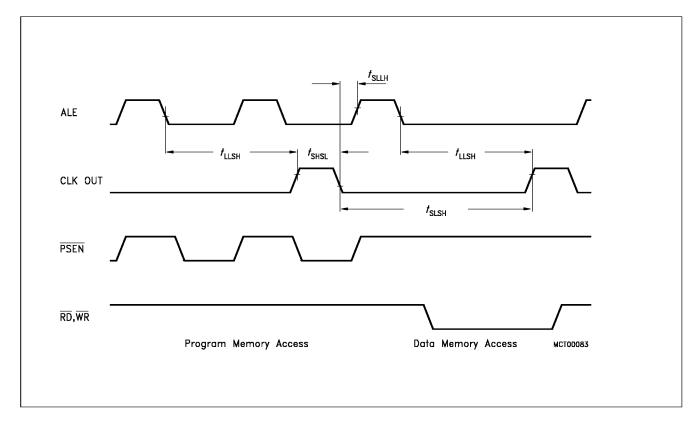

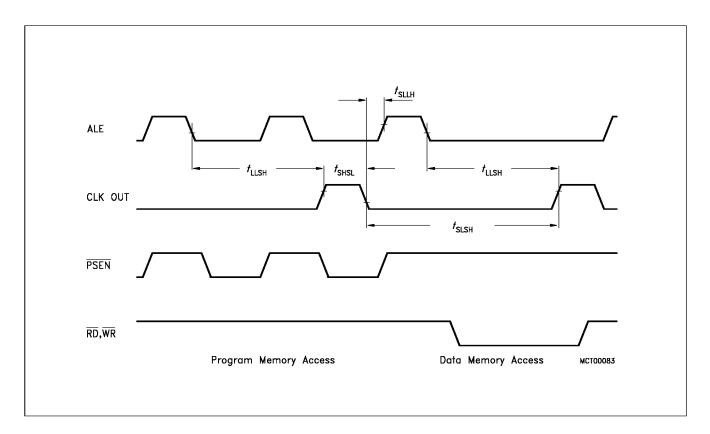

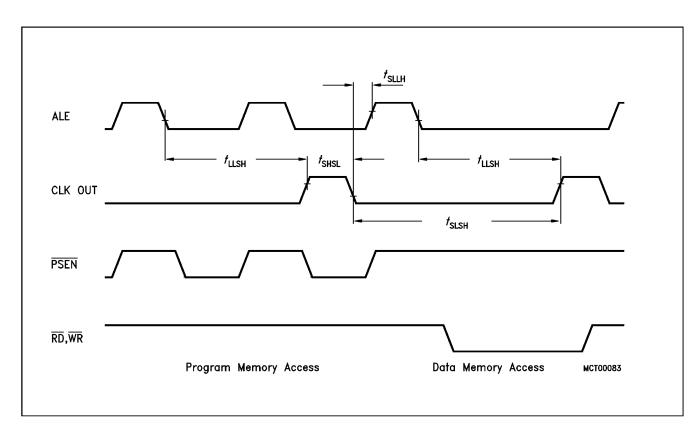

| PSEN      | 49              | 47               | Ο                       | The Program store enable output is a control signal that enables the external program memory to the bus during external fetch operations. It is activated every six oscillator periods, except during external data memory accesses. The signal remains high during internal program execution.                                                                                                                                                                                                                        |

| ALE       | 50              | 48               | 0                       | The Address latch enable output is used for latching the address into external memory during normal operation. It is activated every six oscillator periods, except during an external data memory access.                                                                                                                                                                                                                                                                                                             |

| ĒĀ        | 51              | 49               | I                       | External access enable When held high, the SAB 80C515 executes instructions from the internal ROM as long as the PC is less than 8192. When held low, the SAB 80C515 fetches all instructions from external program memory. For the SAB 80C535 this pin must be tied low.                                                                                                                                                                                                                                              |

| P0.0-P0.7 | 52-59           | 52-59            | I/O                     | Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application it uses strong internal pullup resistors when issuing 1's. Port 0 also outputs the code bytes during program verification in the SAB 80C515. External pullup resistors are required during program verification. |

| Symbol              | Pin<br>P-LCC-68 | Pin<br>P-MQFP-80                                       | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|-----------------|--------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5.7-P5.0           | 60-67           | 60-67                                                  | I/O                     | Port 5 is an 8-bit bidirectional I/O port with internal pullup resistors. Port 5 pins that have 1's written to them are pulled high by the internal pullup resistors, and in that state can be used as inputs. As inputs, port 5 pins being externally pulled low will source current (I <sub>IL</sub> in the DC characteristics) because of the internal pullup resistors. |

| $V_{\rm CC}$        | 37              | 33                                                     | _                       | Supply voltage during normal, idle, and power-down operation. Internally connected to pin 68.                                                                                                                                                                                                                                                                               |

| $\overline{V_{SS}}$ | 38              | 34                                                     | _                       | Ground (0 V)                                                                                                                                                                                                                                                                                                                                                                |

| $V_{\rm CC}$        | 68              | 69                                                     | _                       | Supply voltage<br>during normal, idle, and power-down<br>operation. Internally connected to pin 37.                                                                                                                                                                                                                                                                         |

| N. C.               | _               | 2, 13, 14,<br>23, 32, 35,<br>46, 50, 51,<br>68, 70, 71 | _                       | Not connected These pins of the P-MQFP-80 package must not be connected                                                                                                                                                                                                                                                                                                     |

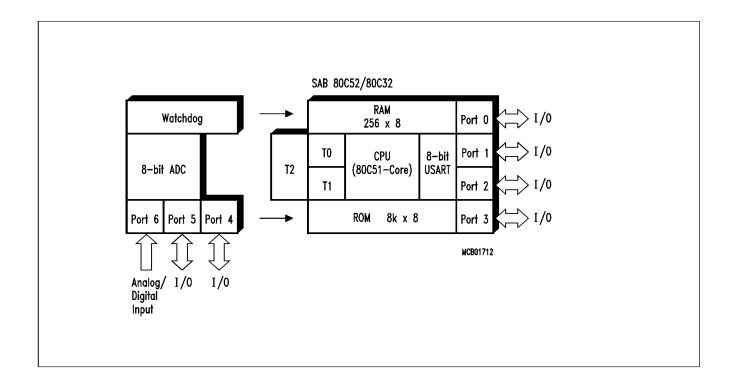

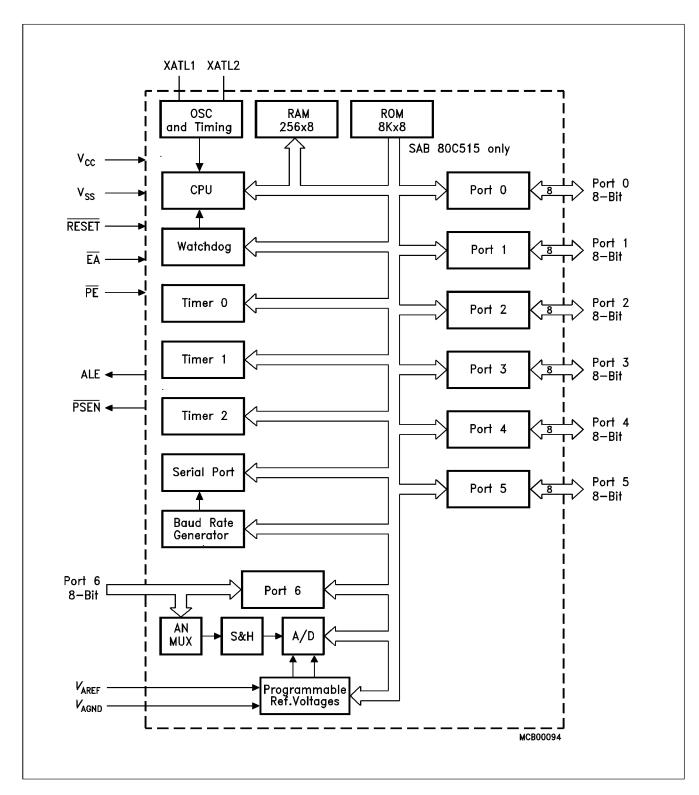

Figure 1 Block Diagram

#### **Functional Description**

The members of the SAB 80515 family of microcontrollers are:

- SAB 80C515: Microcontroller, designed in Siemens ACMOS technology, with

8 Kbyte factory mask-programmable ROM

SAB 80C535: ROM-less version of the SAB 80C515

SAB 80515: Microcontroller, designed in Siemens MYMOS technology, with

8 Kbyte factory mask-programmable ROM

SAB 80535: ROM-less version of the SAB 80515

The SAB 80C535 is identical to the SAB 80C515, except that it lacks the on-chip ROM. In this data sheet the term "SAB 80C515" is used to refer to both the SAB 80C515 and SAB 80C535, unless otherwise noted.

### **Principles of Architecture**

The architecture of the SAB 80C515 is based on the SAB 80C51/SAB 80C51 microcontroller family. The following features of the SAB 80C515 are fully compatible with the SAB 80C51 features:

- Instruction set

- External memory expansion interface (port 0 and port 2)

- Full-duplex serial port

- Timer/counter 0 and 1

- Alternate functions on port 3

- The lower 128 bytes of internal RAM and the lower 4 Kbytes of internal ROM

The SAB 80C515 additionally contains 128 bytes of internal RAM and 4 Kbytes of internal ROM, which results in a total of 256 bytes of RAM and 8 Kbytes of ROM on-chip.

The SAB 80C515 has a new 16-bit timer/counter with a 2:1 prescaler, reload mode, compare and capture capability. It also contains at 16-bit watchdog timer, an 8-bit A/D converter with programmable reference voltages, two additional quasi-bidirectional 8-bit ports, one 8-bit input port for analog or digital signals, and a programmable clock output ( $f_{\rm OSC}/12$ ).

Furthermore, the SAB 80C515 has a powerful interrupt structure with 12 vectors and 4 programmable priority levels.

Figure 1 shows a block diagram of the SAB 80C515.

#### CPU

The SAB 80C515 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and 15 % three-byte instructions. With a 12 MHz crystal, 58 % of the instructions execute in 1.0  $\mu$ s.

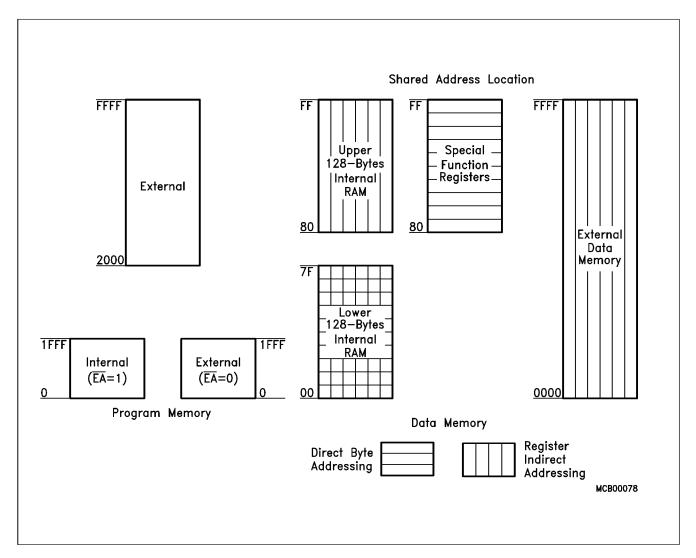

### **Memory Organization**

The SAB 80C515 manipulates operands in the four memory address spaces described below: Figure 1 illustrates the memory address spaces of the SAB 80C515.

### **Program Memory**

The SAB 80C515 has 8 Kbyte of on-chip ROM, while the SAB 80C535 has no internal ROM. The program memory can be externally expanded up to 64 Kbytes. If the  $\overline{EA}$  pin is held high, the SAB 80C515 executes out of internal ROM unless the address exceeds 1FFF<sub>H</sub>. Locations 2000<sub>H</sub> through 0FFFF<sub>H</sub> are then fetched from the external program memory. If the  $\overline{EA}$  pin is held now, the SAB 80C515 fetches all instructions from the external program memory. Since the SAB 80C535 has no internal ROM, pin  $\overline{EA}$  must be tied low when using this component.

#### **Data Memory**

The data memory address space consists of an internal and an external memory space. The internal data memory is divided into three physically separate and distinct blocks: the lower 128 bytes of RAM, the upper 128 bytes of RAM, and the 128 byte special function register (SRF) area. While the upper 128 bytes of data memory and the SFR area share the same address locations, they are accessed through different addressing modes. The lower 128 bytes of data memory can be accessed through direct or register indirect addressing; the upper 128 bytes of RAM can be accessed through register indirect addressing; the special function registers are accessible through direct addressing.

Four 8-register banks, each bank consisting of eight 8-bit multi-purpose registers, occupy locations 0 through 1F<sub>H</sub> in the lower RAM area. The next 16 bytes, locations 20<sub>H</sub> through 2F<sub>H</sub>, contain 128 directly addressable bit locations. The stack can be located anywhere in the internal data memory address space, and the stack depth can be expanded up to 256 bytes.

The external data memory can be expanded up to 64 Kbytes and can be accessed by instructions that use a 16-bit or an 8-bit address.

Figure 2 Memory Address Spaces

#### **Special Function Registers**

All registers, except the program counter and the four general purpose register banks, reside in the special function register area. The special function registers include arithmetic registers, pointers, and registers that provide an interface between the CPU and the on-chip peripherals. There are also 128 directly addressable bits within the SFR area. All special function registers are listed in table 1 and table 2.

In table 1 they are organized in numeric order of their addresses. In table 3 they are organized in groups which refer to the functional blocks of the SAB 80C515.

Table 1

Special Function Register

| Address                                                                                                                                              | Register                                                             | Contents after Reset                                                                                                                                                                                                                                             | Address                                                                                                                                              | Register                                                             | Contents after Reset                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80 <sub>H</sub><br>81 <sub>H</sub><br>82 <sub>H</sub><br>83 <sub>H</sub><br>84 <sub>H</sub><br>85 <sub>H</sub><br>86 <sub>H</sub><br>87 <sub>H</sub> | P0 1) SP DPL DPH reserved reserved reserved PCON                     | 0FF <sub>H</sub><br>07 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>XX <sub>H</sub> <sup>2)</sup><br>XX <sub>H</sub> <sup>2)</sup><br>XX <sub>H</sub> <sup>2)</sup><br>000X 0000 <sub>B</sub> <sup>2)</sup>                                             | 98 <sub>H</sub><br>99 <sub>H</sub><br>9A <sub>H</sub><br>9B <sub>H</sub><br>9C <sub>H</sub><br>9D <sub>H</sub><br>9E <sub>H</sub><br>9F <sub>H</sub> | SCON 1) SBUF reserved reserved reserved reserved reserved reserved   | 00 <sub>H</sub> XX <sub>H</sub> <sup>2)</sup>  |

| 88 <sub>H</sub><br>89 <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8E <sub>H</sub><br>8F <sub>H</sub> | TCON 1) TMOD TL0 TL1 TH0 TH1 reserved reserved                       | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>XX <sub>H</sub> <sup>2)</sup><br>XX <sub>H</sub> <sup>2)</sup>                                                                                 | A0 <sub>H</sub> A1 <sub>H</sub> A2 <sub>H</sub> A3 <sub>H</sub> A4 <sub>H</sub> A5 <sub>H</sub> A6 <sub>H</sub> A7 <sub>H</sub>                      | P2 1) reserved reserved reserved reserved reserved reserved reserved | 0FF <sub>H</sub> XX <sub>H</sub> <sup>2)</sup>                               |

| 90 <sub>H</sub><br>91 <sub>H</sub><br>92 <sub>H</sub><br>93 <sub>H</sub><br>94 <sub>H</sub><br>95 <sub>H</sub><br>96 <sub>H</sub><br>97 <sub>H</sub> | P1 1) reserved reserved reserved reserved reserved reserved reserved | 0FF <sub>H</sub> XX <sub>H</sub> <sup>2)</sup> | A8 <sub>H</sub> A9 <sub>H</sub> AA <sub>H</sub> AB <sub>H</sub> AC <sub>H</sub> AD <sub>H</sub> AE <sub>H</sub> AF <sub>H</sub>                      | IENO 1) IPO reserved reserved reserved reserved reserved reserved    | 00 <sub>H</sub><br>X000 0000 <sub>B</sub> <sup>2)</sup><br>XX <sub>H</sub> <sup>2)</sup> |

<sup>1)</sup> Bit-addressable Special Function Register

<sup>2)</sup> X means that the value is indeterminate and the location is reserved

Table 1 Special Function Register (cont'd)

| Address         | Register         | Contents after Reset                 | Address         | Register            | Contents after Reset                 |

|-----------------|------------------|--------------------------------------|-----------------|---------------------|--------------------------------------|

| B0 <sub>H</sub> | P3 <sup>1)</sup> | 0FF <sub>H</sub>                     | D0 <sub>H</sub> | PSW 1)              | 00 <sub>H</sub>                      |

| B1 <sub>H</sub> | reserved         | XXH <sup>2)</sup>                    | D1 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B2 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D2 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B3 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D3 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B4 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D4 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B5 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D5 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B6 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D6 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B7 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | D7 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| B8 <sub>H</sub> | IEN1 1)          | 00 <sub>H</sub>                      | D8 <sub>H</sub> | ADCON <sup>1)</sup> | 00X0 0000 <sub>B</sub> <sup>2)</sup> |

| B9 <sub>H</sub> | IP1              | XX00 0000 <sub>B</sub> <sup>2)</sup> | D9 <sub>H</sub> | ADDAT               | 00 <sub>H</sub>                      |

| BA <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2</sup> )       | DA <sub>H</sub> | DAPR                | 00 <sub>H</sub>                      |

| BB <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2</sup> )       | DB <sub>H</sub> | P6                  | XX <sub>H</sub> <sup>2)</sup>        |

| BC <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2</sup> )       | DC <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| BD <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2</sup> )       | DD <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| BS <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2</sup> )       | DE <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| BF <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | DF <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C0 <sub>H</sub> | IRCON 1)         | 00 <sub>H</sub>                      | E0 <sub>H</sub> | ACC 1)              | 00 <sub>H</sub>                      |

| C1 <sub>H</sub> | CCEN             | 00 <sub>H</sub>                      | E1 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C2 <sub>H</sub> | CCL1             | 00 <sub>H</sub>                      | E2 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C3 <sub>H</sub> | CCH1             | 00 <sub>H</sub>                      | E3 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C4 <sub>H</sub> | CCL2             | 00 <sub>H</sub>                      | E4 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C5 <sub>H</sub> | CCH2             | 00 <sub>H</sub>                      | E5 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C6 <sub>H</sub> | CCL3             | 00 <sub>H</sub>                      | E6 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C7 <sub>H</sub> | ССНЗ             | 00 <sub>H</sub>                      | E7 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| C8H             | T2CON 1)         | 00 <sub>H</sub>                      | E8 <sub>H</sub> | <b>P4</b> 1)        | 0FF <sub>H</sub>                     |

| C9 <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | E9 <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CA <sub>H</sub> | CRCL             | 00 <sub>H</sub>                      | EA <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CB <sub>H</sub> | CRCH             | 00 <sub>H</sub>                      | EB <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CCH             | TL2              | 00 <sub>H</sub>                      | ECH             | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CD <sub>H</sub> | TH2              | 00 <sub>H</sub>                      | ED <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CE <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | EEH             | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

| CF <sub>H</sub> | reserved         | XX <sub>H</sub> <sup>2)</sup>        | EF <sub>H</sub> | reserved            | XX <sub>H</sub> <sup>2)</sup>        |

<sup>1)</sup> Bit-addressable Special Function Register

2) X means that the value is indeterminate and the location is reserved

Table 1 Special Function Register (cont'd)

| Address         | Register    | Contents after Reset          | Address         | Register | Contents<br>after Reset       |

|-----------------|-------------|-------------------------------|-----------------|----------|-------------------------------|

| F0 <sub>H</sub> | <b>B</b> 1) | 00 <sub>H</sub>               | F8 <sub>H</sub> | P5 1)    | 0FF <sub>H</sub>              |

| F1 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | F9 <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F2 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FA <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F3 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FB <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F4 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FC <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F5 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FD <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F6 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FE <sub>H</sub> | reserved | XX <sub>H</sub> <sup>2)</sup> |

| F7 <sub>H</sub> | reserved    | XX <sub>H</sub> <sup>2)</sup> | FFH             | reserved | XX <sub>H</sub> <sup>2)</sup> |

<sup>1)</sup> Bit-addressable Special Function Register2) X means that the value is indeterminate and the location is reserved

Table 2 Special Function Registers - Functional Blocks

| Block                                 | Symbol                                                                                      | Name                                                                                                                                                                                                                                                                                                                                                                             | Address                                                                                                                                                                                     | Contents after Reset                                                                                                                                                                       |

|---------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                                   | ACC<br>B<br>DPH<br>DPL<br>PSW<br>SP                                                         | Accumulator B-Register Data Pointer, High Byte Data Pointer, Low Byte Program Status Word Register Stack Pointer                                                                                                                                                                                                                                                                 | 0E0 <sub>H</sub> 1)<br>0F0 <sub>H</sub> 1)<br>83 <sub>H</sub><br>82 <sub>H</sub><br>0D0 <sub>H</sub> 1)<br>81 <sub>H</sub>                                                                  | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>07 <sub>H</sub>                                                                             |

| A/D-<br>Converter                     | ADCON<br>ADDAT<br>DAPR                                                                      | A/D Converter Control Register<br>A/D Converter Data Register<br>D/A Converter Program Register                                                                                                                                                                                                                                                                                  | <b>0D8<sub>H</sub></b> <sup>1)</sup><br>0D9 <sub>H</sub><br>0DA <sub>H</sub>                                                                                                                | 00X0 0000 <sub>B</sub> <sup>2)</sup><br>00 <sub>H</sub><br>00 <sub>H</sub>                                                                                                                 |

| Interrupt<br>System                   | EN0<br>IEN1<br>IP0<br>IP1<br>IRCON<br>TCON <sup>2)</sup><br>T2CON <sup>2)</sup>             | Interrupt Enable Register 0 Interrupt Enable Register 1 Interrupt Priority Register 0 Interrupt Priority Register 1 Interrupt Request Control Register Timer Control Register Timer 2 Control Register                                                                                                                                                                           | 0A8 <sub>H</sub> <sup>1)</sup> 0B8 <sub>H</sub> <sup>1)</sup> 0A9 <sub>H</sub> 0B9 <sub>H</sub> 0C0 <sub>H</sub> <sup>1)</sup> 88 <sub>H</sub> <sup>1)</sup> 0C8 <sub>H</sub> <sup>1)</sup> | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>X000 0000 <sub>B</sub> <sup>2)</sup><br>XX00 0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub><br>00 <sub>H</sub>                |

| Compare/<br>Capture-<br>Unit<br>(CCU) | CCEN<br>CCH1<br>CCH2<br>CCH3<br>CCL1<br>CCL2<br>CCL3<br>CRCH<br>CRCL<br>TH2<br>TL2<br>T2CON | Comp./Capture Enable Reg. Comp./Capture Reg. 1, High Byte Comp./Capture Reg. 2, High Byte Comp./Capture Reg. 3, High Byte Comp./Capture Reg. 1, Low Byte Comp./Capture Reg. 2, Low Byte Comp./Capture Reg. 3, Low Byte Comp./Capture Reg. 3, Low Byte Com./Rel./Capt. Reg. High Byte Com./Rel./Capt. Reg. Low Byte Timer 2, High Byte Timer 2, Low Byte Timer 2 Control Register | 0C1 <sub>H</sub> 0C3 <sub>H</sub> 0C5 <sub>H</sub> 0C7 <sub>H</sub> 0C2 <sub>H</sub> 0C4 <sub>H</sub> 0C6 <sub>H</sub> 0CB <sub>H</sub> 0CA <sub>H</sub> 0CC <sub>H</sub> 0CC <sub>H</sub>  | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub> |

<sup>1)</sup> Bit-addressable special function registers

<sup>&</sup>lt;sup>2)</sup> This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

<sup>3)</sup> X means that the value is indeterminate and the location is reserved

Table 2

Special Function Registers- Functional Blocks (cont'd)

| Block               | Symbol                                                                    | Name                                                                                                                         | Address                                                                                                                                                                   | Contents after Reset                                                                                                              |

|---------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Ports               | P0<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6                                    | Port 0 Port 1 Port 2 Port 3 Port 4 Port 5 Port 6, Analog/Digital Input                                                       | 80 <sub>H</sub> <sup>1)</sup> 90 <sub>H</sub> <sup>1)</sup> 0A0 <sub>H</sub> <sup>1)</sup> 0B0 <sub>H</sub> <sup>1)</sup> 0F8 <sub>H</sub> <sup>1)</sup> 0DB <sub>H</sub> | OFF <sub>H</sub> OFF <sub>H</sub> OFF <sub>H</sub> OFF <sub>H</sub> OFF <sub>H</sub>                                              |

| Pow.Sav.M<br>odes   | PCON                                                                      | Power Control Register                                                                                                       | 87 <sub>H</sub>                                                                                                                                                           | 000X 0000 <sub>B</sub> <sup>2)</sup>                                                                                              |

| Serial<br>Channels  | ADCON 2)<br>PCON 2)<br>SBUF<br>SCON                                       | A/D Converter Control Reg.<br>Power Control Register<br>Serial Channel Buffer Reg.<br>Serial Channel Control Reg.            | <b>0D8<sub>H</sub></b> <sup>1)</sup><br>87 <sub>H</sub><br>99 <sub>H</sub><br><b>98<sub>H</sub></b> <sup>1)</sup>                                                         | 00X0 0000 <sub>B</sub> <sup>2)</sup><br>000X 0000 <sub>B</sub> <sup>2)</sup><br>0XX <sub>H</sub> <sup>3)</sup><br>00 <sub>H</sub> |

| Timer 0/<br>Timer 1 | TCON<br>TH0<br>TH1<br>TL0<br>TL1<br>TMOD                                  | Timer Control Register Timer 0, High Byte Timer 1, High Byte Timer 0, Low Byte Timer 1, Low Byte Timer Mode Register         | 88 <sub>H</sub> <sup>1)</sup><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>                                              | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                       |

| Watchdog            | IENO <sup>2)</sup> IEN1 <sup>2)</sup> IPO <sup>2)</sup> IP1 <sup>2)</sup> | Interrupt Enable Register 0<br>Interrupt Enable Register 1<br>Interrupt Priority Register 0<br>Interrupt Priority Register 1 | <b>0A8<sub>H</sub></b> <sup>1)</sup><br><b>0B8<sub>H</sub></b> <sup>1)</sup><br>0A9 <sub>H</sub><br>0B9 <sub>H</sub>                                                      | 00 <sub>H</sub><br>00 <sub>H</sub><br>X000 0000 <sub>B</sub> <sup>2)</sup><br>XX00 0000 <sub>B</sub> <sup>3)</sup>                |

<sup>1)</sup> Bit-addressable special function registers

<sup>&</sup>lt;sup>2)</sup> This special function register is listed repeatedly since some bits of it also belong to other functional blocks.

<sup>3)</sup> X means that the value is indeterminate and the location is reserved

#### I/O Ports

The SAB 80C515 has six 8-bit I/O ports and one 8-bit input port. Port 0 is an open-drain bidirectional I/O port, while ports 1 to 5 are quasi-bidirectional I/O ports with internal pullup resistors. That means, when configured as inputs, ports 1 to 5 will be pulled high and will source current when externally pulled low. Port 0 will float when configured as input.

Port 0 and port 2 can be used to expand the program and data memory externally. During an access to external memory, port 0 emits the low-order address byte and reads/writes the data byte, while port 2 emits the high-order address byte. In this function, port 0 is not an open-drain port, but uses a strong internal pullup FET. Ports 1 and 3 are provided for several alternate functions, as listed below:

| Port | Symbol   | Function                                                              |  |  |  |

|------|----------|-----------------------------------------------------------------------|--|--|--|

| P1.0 | INT3/CC0 | External interrupt 3 input, compare 0 output, capture 0 input         |  |  |  |

| P1.1 | INT4/CC1 | External interrupt 4 input, compare 1 output, capture 1 input         |  |  |  |

| P1.2 | INT5/CC2 | External interrupt 5 input, compare 2 output, capture 2 input         |  |  |  |

| P1.3 | INT6/CC3 | External interrupt 6 input, compare 3 output, capture 3 input         |  |  |  |

| P1.4 | INT2     | External interrupt 2 input                                            |  |  |  |

| P1.5 | T2EX     | Timer 2 external reload trigger input                                 |  |  |  |

| P1.6 | CLKOUT   | System clock output                                                   |  |  |  |

| P1.7 | T2       | Timer 2 external count or gate input                                  |  |  |  |

| P3.0 | R×D      | Serial port's receiver data input (asynchronous) or data input/output |  |  |  |

|      |          | (synchronous)                                                         |  |  |  |

| P3.1 | T×D      | Serial port's transmitter data output (asynchronous) or clock output  |  |  |  |

|      |          | (synchronous)                                                         |  |  |  |

| P3.2 | INTO     | External interrupt 0 input, timer 0 gate control                      |  |  |  |

| P3.3 | INT1     | External interrupt 1 input, timer 1 gate control                      |  |  |  |

| P3.4 | T0       | Timer 0 external counter input                                        |  |  |  |

| P3.5 | T1       | Timer 1 external counter input                                        |  |  |  |

| P3.6 | WR       | External data memory write strobe                                     |  |  |  |

| P3.7 | RD       | External data memory read strobe                                      |  |  |  |

The SAB 80C515 has dual-purpose input port. As the ANx lines in the SAB 80515 (NMOS version), the eight port lines at port 6 can be used as analog inputs. But if the input voltages at port 6 meet the specified digital input levels ( $V_{\rm IL}$  an d  $V_{\rm IH}$ ), the port can also be used as digital input port. Reading the special function register P6 allows the user to input the digital values currently applied to the port pins. It is not necessary to select these modes by software; the voltages applied at port 6 pins can be converted to digital values using the A/D converter and at the same time the pins can be read via SFR P6.

It must be noted, however, that the results in port P6 bits will be indeterminate if the levels at the corresponding pins are not within their respective  $V_{\rm IL}/V_{\rm IH}$  specifications. Furthermore, it is not possible to use port P6 as output lines. Special function register P6 is located at address 0DB<sub>H</sub>.

#### Timer/Counters

The SAB 80C515 contains three 16-bit timers/counters which are useful in many applications for timing and counting. The input clock for each timer/counter is 1/12 of the oscillator frequency in the timer operation or can be taken from an external clock source for the counter operation (maximum count rate is 1/24 of the oscillator frequency).

#### Timer/Counter 0 and 1

These timers/counters can operate in four modes:

Mode 0: 8-bit timer/counter with 32:1 prescaler

Mode 1: 16-bit timer/counter

Mode 2: 8-bit timer/counter with 8-bit auto-reload

Mode 3: Timer/counter 0 is configured as one 8-bit timer/counter and one 8-bit timer; Timer/counter 1 in this mode holds its count.

External inputs INTO and INT1 can be programmed to function as a gate for timer/counters 0 and 1 to facilitate pulse width measurements.

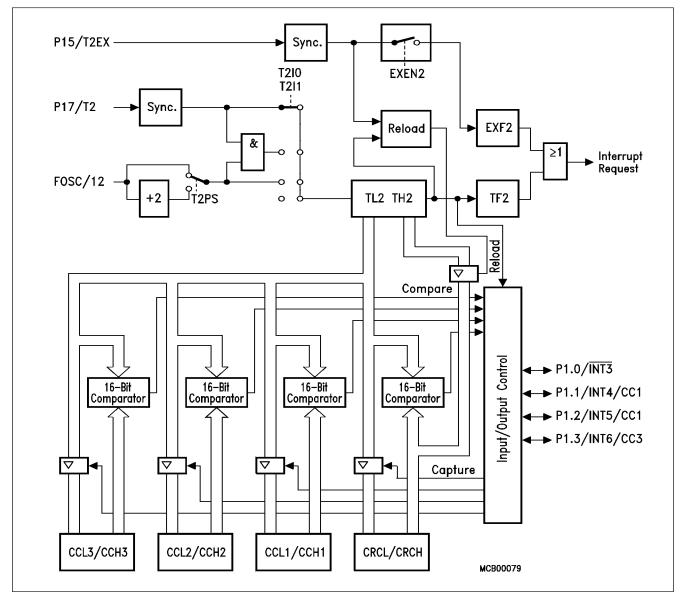

#### - Timer/Counter 2

Timer/counter 2 of the SAB 80C515 is a 16-bit timer/counter with several additional features. It offers a 2:1 prescaler, a selectable gate function, and compare, capture and reload functions. Corresponding to the 16-bit timer register there are four 16-bit capture/compare registers, one of them can be used to perform a 16-bit reload on a timer overflow or external event. Each of these registers corresponds to a pin of port 1 for capture input/compare output. Figure 3 shows a block diagram of timer/counter 2.

#### Reload

A 16-bit reload can be performed with the 16-bit CRC register consisting of CRCL and CRCH. There are two modes from which to select:

Mode 0: Reload is caused by a timer 2 overflow (auto-reload).

Mode 1: Reload is caused in response to a negative transition at pin T2EX (P1.5), which can also request an interrupt.

#### Capture

This feature permits saving the actual timer/counter contents into a selected register upon an external event or a software write operation. Two modes are provided to latch the current 16-bit value in timer 2 registers TL2 and TH2 into a dedicated capture register:

- Mode 0: Capture is performed in response to a transition at the corresponding port 1 pins CC0 to CC3.

- Mode 1: Write operation into the low-order byte of the dedicated capture register causes the timer 2 contents to be latched into this register.

#### Compare

In the compare mode, the 16-bit values stored in the dedicated compare registers are compared to the contents of the timer 2 registers. If the count value in the timer 2 registers matches one of the stored values, an appropriate output signal is generated and an interrupt is requested. Two compare modes are provided:

- Mode 0: Upon a match the output signal changes from low to high. It goes back to a low level when timer 2 overflows.

- Mode 1: The transition of the output signal can be determined by software. A timer 2 overflow causes no output change

Figure 3

Block Diagram of Timer/Counter 2

#### **Serial Port**

The serial port of the SAB 80C515 enables full duplex communication between microcontrollers or between microcontroller and peripheral devices.

The serial port can operate in 4 modes:

- Mode 0: Shift register mode. Serial data enters and exits through RxD. TxD outputs the shift clock. 8-bits are transmitted/received: 8 data bits (LSB first). The baud rate is fixed at 1/12 of the oscillator frequency.

- Mode 1: 10-bits are transmitted (through R×D) or received (through T×D): a start bit (0), 8 data bits (LSB first), and a stop bit (1). The baud rate is variable.

- Mode 2: 11-bits are transmitted (through R×D) or received (through T×D): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). The baud rate is programmable to either 1/32 or 1/64 of the oscillator frequency.

- Mode 3: 11-bits are transmitted (through T×D) or received (through R×D): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). Mode 3 is identical to mode 2 except for the baud rate. The baud rate in mode 3 is variable.

The variable baud rates in modes 1 and 3 can be generated by timer 1 or an internal baud rate generator.

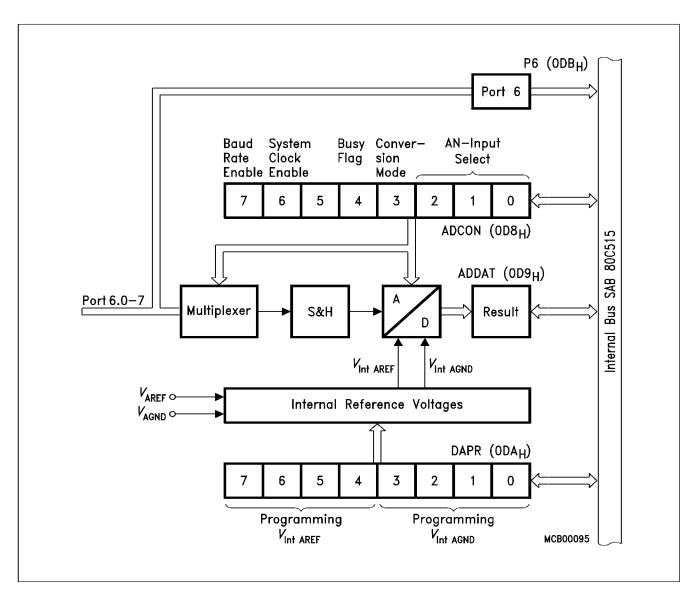

#### A/D Converter

The 8-bit A/D converter of the SAB 80C515 has eight multiplexed analog inputs (Port 6) and uses the successive approximation method.

There are three characteristic time frames in a conversion cycle (see A/D converter characteristics): the conversion time  $t_{\rm C}$ , which is the time required for one conversion; the sample time  $t_{\rm S}$  which is included in the conversion time and is measured from the start of the conversion; the load time  $t_{\rm L}$ , which in turn is part of the sample time and also is measured from the conversion start.

Within the <u>load time</u>  $t_{\rm L}$ , the analog input capacitance  $C_{\rm I}$  must be loaded to the analog input voltage level. For the rest of the <u>sample time</u>  $t_{\rm S}$ , after the load time has passed, the selected analog input must be held constant. During the rest of the <u>conversion time</u>  $t_{\rm C}$  the conversion itself is actually performed. Conversion can be programmed to be single or continuous; at the end of a conversion an interrupt can be generated.

A unique feature is the capability of internal reference voltage programming. The internal reference voltages  $V_{\rm IntAREF}$  and  $V_{\rm IntAGND}$  for the A/D converter both are programmable to one of 16 steps with respect to the external reference voltages. This feature permits a conversion with a smaller internal reference voltage range to gain a higher resolution. In addition, the internal reference voltages can easily be adapted by software to the desired analog input voltage range.

Figure 4 shows a block diagram of the A/D converter.

Figure 4

Block Diagram of the A/D Converter

#### **Interrupt Structure**

The SAB 80C515 has 12 interrupt vectors with the following vector addresses and request flags:

Table 3 Interrupt Sources and Vectors

| Source (Request Flags) | Vector Address    | Vector                  |  |

|------------------------|-------------------|-------------------------|--|

| IE0                    | 0003 <sub>H</sub> | External interrupt 0    |  |

| TF0                    | 000B <sub>H</sub> | Timer 0 interrupt       |  |

| IE1                    | 0013 <sub>H</sub> | External interrupt 1    |  |

| TF1                    | 001B <sub>H</sub> | Timer 1 interrupt       |  |

| RI + TI                | 0023 <sub>H</sub> | Serial port interrupt   |  |

| TF2 + EXF2             | 002B <sub>H</sub> | Timer 2 interrupt       |  |

| IADC                   | 0043 <sub>H</sub> | A/D converter interrupt |  |

| IEX2                   | 004B <sub>H</sub> | External interrupt 2    |  |

| IEX3                   | 0053 <sub>H</sub> | External interrupt 3    |  |

| IEX4                   | 005B <sub>H</sub> | External interrupt 4    |  |

| IEX5                   | 0063 <sub>H</sub> | External interrupt 5    |  |

| IEX6                   | 006B <sub>H</sub> | External interrupt 6    |  |

Each interrupt vector can be individually enabled/disabled. The minimum response time to an interrupt request is more than 3 machine cycles and less than 9 machine cycles.

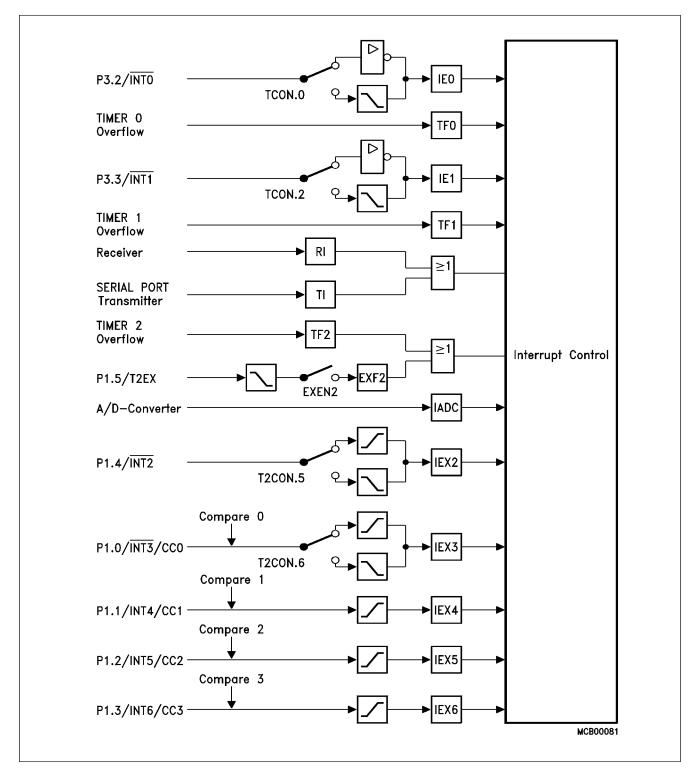

Figure 5 shows the interrupt request sources.

External interrupts 0 and 1 can be activated by a low-level or a negative transition (selectable) at their corresponding input pin, external interrupts 2 and 3 can be programmed for triggering on a negative or a positive transition. The external interrupts 3 or 6 are combined with the corresponding alternate functions compare (output) and capture (input) on port 1.

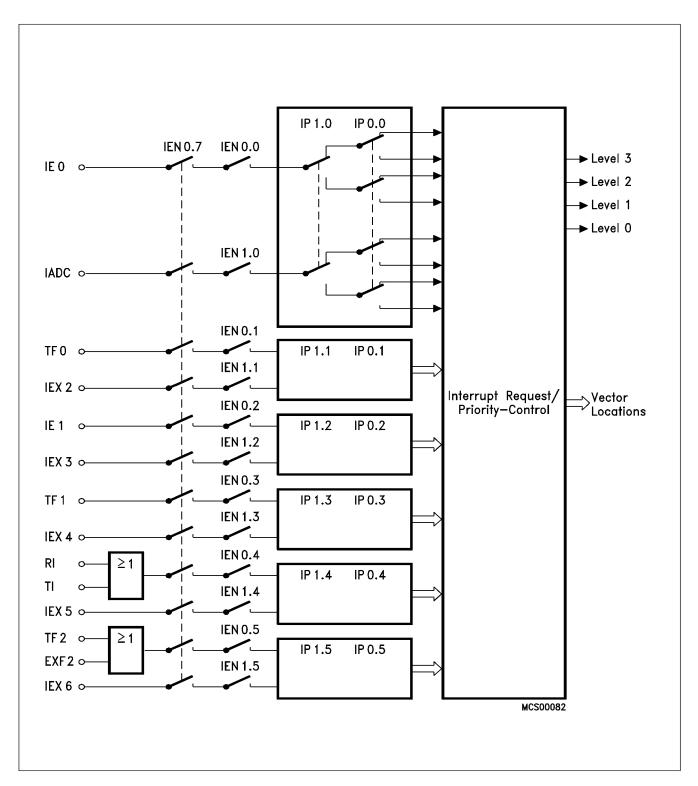

For programming of the priority levels the interrupt vectors are combined to pairs. Each pair can be programmed individually to one of four priority levels by setting or clearing one bit in the special function register IPO and one in IP1.

Figure 6 shows the priority level structure.

Figure 5

Interrupt Request Sources

Figure 6 Interrupt Priority Level Structure

### **Watchdog Timer**

This feature is provided as a means of graceful recovery from a software upset. After an external reset, the watchdog timer is cleared and stopped. It can be started and cleared by software, but it cannot be stopped during active mode of the device. If the software fails to clear the watchdog timer at least every 65532 machine cycles (about 65 ms if a 12 MHz oscillator frequency is used), an internal reset will be initiated. The reset cause (external reset or reset caused by the watchdog) can be examined by software. To clear the watchdog, two bits in two different special function registers must be set by two consecutive instructions (bits IEN0.6 and IEN1.6). This is done to prevent the watchdog from being cleared by unexpected opcodes.

It must be noted, however, that the watchdog timer is halted during the idle mode and power-down mode of the processor (see section "Power Saving Modes" below).

Therefore, it is possible to use the idle mode in combination with the watchdog timer function. But even the watchdog timer cannot reset the device when one of the power saving modes has been is entered accidentally.

For these reasons several precautions are taken against unintentional entering of the power-down or idle mode (see below).

#### **Power Saving Modes**

The ACMOS technology of the SAB 80C515 allows two new power saving modes of the device: The idle mode and the power-down mode. These modes replace the power-down supply mode via pin  $V_{\rm PD}$  of the SAB 80515 (NMOS). The SAB 80C515 is supplied via pins  $V_{\rm CC}$  also during idle and power-down operation.

However, there are applications where unintentional entering of these power saving modes must be absolutely avoided. Such critical applications often use the watchdog timer to prevent the system from program upsets. Then accidental entering of the power saving modes would even stop the watchdog timer and would circumvent the watchdog timer's task of system protection.

Thus, the SAB 80C515 has an extra pin that allows it to disable both of the power saving modes. When pin  $\overline{PE}$  is held high, idle mode and power-down mode are completely disabled and the instruction sequences that are used for entering these modes (see below) will NOT affect the normal operations of the device. When  $\overline{PE}$  is held low, the use of the idle mode and power-down mode is possible as described in the following sections.

Pin PE has a weak internal pullup resistor. Thus, when left open, the power saving modes are disabled.

#### The Special Function Register PCON

In the NMOS version SAB 80515 the SFR PCON (address 87<sub>H</sub>) contains only bit SMOD; in the CMOS version SAB 80C515 there are more bits used (see table 4).

The bits PDE, PDS and IDLE, IDLS select the power-down mode or the idle mode, respectively, when the use of the power saving modes is enabled by pin  $\overline{PE}$  (see next page).

If the power-down mode and the idle mode are set at the same time, power-down takes precedence.

Furthermore, register PCON contains two general purpose flags. For example, the flag bits GF0 and GF1 can be used to give an indication if an interrupt occurred during normal operation or during an idle. Then an instruction that activates Idle can also set one or both flag bits. When idle is terminated by an interrupt, the interrupt service routine can examine the flag bits. The reset value of PCON is  $000X0000_B$ .

Table 4 SFR PCON (87H)

| SMOD | PDS | IDLS | _ | GF1 | GF0 | PDE | IDLE | 87H |

|------|-----|------|---|-----|-----|-----|------|-----|

| 7    | 6   | 5    | 4 | 3   | 2   | 1   | 0    |     |

| Symbol | Position | Function                                                                                                                      |  |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------|--|

| SMOD   | PCON.7   | When set, the baud rate of the serial channel in mode 1, 2, 3 is doubled.                                                     |  |

| PDS    | PCON.6   | Power-down start bit. The instruction that sets the PDS flag bit is the last instruction before entering the power-down mode. |  |

| IDLS   | PCON.5   | Idle start bit. The instruction that sets the IDLS flag bit is the last instruction before entering the idle mode.            |  |

| _      | PCON.4   | Reserved                                                                                                                      |  |

| GF1    | PCON.3   | General purpose flag                                                                                                          |  |

| GF0    | PCON.2   | General purpose flag                                                                                                          |  |

| PDE    | PCON.1   | Power-down enable bit. When set, starting of the power-down mode is enabled.                                                  |  |

| IDLE   | PCON.0   | Idle mode enable bit. When set, starting of the idle mode is enabled.                                                         |  |

#### Idle Mode