# Four-Bit Single-Chip Microcontrollers with 4, 6, 8, 12, and 16 KB of On-Chip ROM

### **Preliminary**

#### Overview

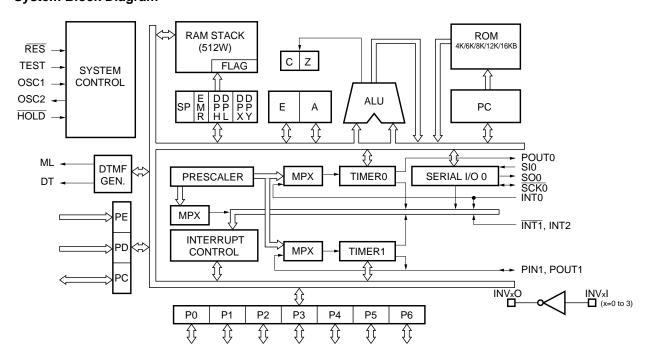

The LC662304A, LC662306A, LC662308A, LC662312A, and LC662316A are 4-bit CMOS microcontrollers that integrate on a single chip all the functions required in a special-purpose telephone controller, including ROM, RAM, I/O ports, a serial interface, a DTMF generator, timers, and interrupt functions. These microcontrollers are available in a 42-pin package.

#### **Features and Functions**

- On-chip ROM capacities of 4, 6, 8, 12, and 16 kilobytes, and an on-chip RAM capacity of 512 × 4 bits.

- Fully supports the LC66000 Series common instruction set (128 instructions).

- I/O ports: 36 pins

- · DTMF generator

This microcontroller incorporates a circuit that can generate two sine wave outputs, DTMF output, or a melody output for software applications.

- 8-bit serial interface: one circuit

- Instruction cycle time: 0.95 to 10 µs (at 3.0 to 5.5 V)

- Powerful timer functions and prescalers

- Time limit timer, event counter, pulse width measurement, and square wave output using a 12-bit timer.

- Time limit timer, event counter, PWM output, and square wave output using an 8-bit timer.

- Time base function using a 12-bit prescaler.

- Powerful interrupt system with 10 interrupt factors and 7 interrupt vector locations.

- External interrupts: 3 factors/3 vector locations

- Internal interrupts: 4 factors/4 vector locations

(Waveform output internal interrupts: 3 factors and 1 vector; shared with external expansion interrupts)

- Flexible I/O functions Selectable options include 20-mA drive outputs, inverter circuits, pull-up and open drain circuits.

- Optional runaway detection function (watchdog timer)

- 8-bit I/O functions

- Power saving functions using halt and hold modes.

- Packages: DIP42S, QIP48E (QFP48E)

- Evaluation LSIs: LC66599 (evaluation chip) + EVA800/850-TB662YXX2

LC66E2316(on-chip EPROM microcontroller)

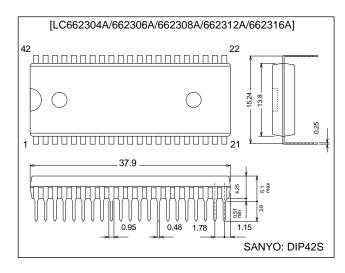

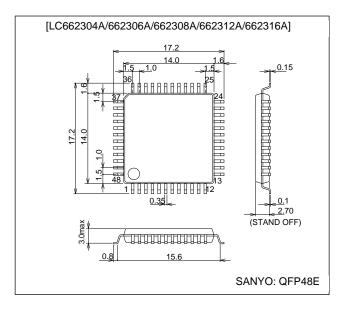

### **Package Dimensions**

unit: mm

#### 3025B-DIP42S

unit: mm

#### 3156-QFP48E

# **Series Organization**

| Type No.                  | No. of pins | ROM capacity           | RAM capacity | Pa                    | ckage                | Features                                                |

|---------------------------|-------------|------------------------|--------------|-----------------------|----------------------|---------------------------------------------------------|

| LC66304A/306A/308A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               |                                                         |

| LC66404A/406A/408A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | Normal versions                                         |

| LC66506B/508B/512B/516B   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64A               | 4.0 to 6.0 V/0.92 μs                                    |

| LC66354A/356A/358A        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               |                                                         |

| LC66354S/356S/358S        | 42          | 4 K/6 K/8 KB           | 512 W        |                       | QFP44M               | Low-voltage versions<br>2.2 to 5.5 V/3.92 µs            |

| LC66556A/558A/562A/566A   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64E               | 2.2 10 5.5 7/3.92 μs                                    |

| LC66354B/356B/358B        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | Low-voltage high-speed versions                         |

| LC66556B/558B/562B/566B   | 64          | 6 K/8 K/12 K/16 KB     | 512 W        | DIP64S                | QFP64E               | 3.0 to 5.5 V/0.92 µs                                    |

| LC66354C/356C/358C        | 42          | 4 K/6 K/8 KB           | 512 W        | DIP42S                | QFP48E               | 2.5 to 5.5 V/0.92 µs                                    |

| LC662104A/06A/08A         | 30          | 4 K/6 K/8 KB           | 384 W        | DIP30SD               | MFP30S               | O LI DINE                                               |

| LC662304A/06A/08A/12A/16A | 42          | 4 K/6 K/8 K/12 K/16 KB | 512 W        | DIP42S                | QFP48E               | On-chip DTMF generator versions<br>3.0 to 5.5 V/0.95 µs |

| LC662508A/12A/16A         | 64          | 8 K/12 K/16 KB         | 512 W        | DIP64S                | QFP64E               | μο                                                      |

| LC665304A/06A/08A/12A/16A | 48          | 4 K/6 K/8 K/12 K/16 KB | 512 W        | DIP48S                | QFP48E               | Dual oscillator support<br>3.0 to 5.5 V/0.95 µs         |

| LC66E308                  | 42          | EPROM 8 KB             | 512 W        | DIC42S<br>with window | QFC48<br>with window |                                                         |

| LC66P308                  | 42          | OTPROM 8 KB            | 512 W        | DIP42S                | QFP48E               |                                                         |

| LC66E408                  | 42          | EPROM 8 KB             | 512 W        | DIC42S<br>with window | QFC48<br>with window | Window and OTP evaluation versions                      |

| LC66P408                  | 42          | OTPROM 8 KB            | 512 W        | DIP42S                | QFP48E               | 4.5 to 5.5 V/0.92 μs                                    |

| LC66E516                  | 64          | EPROM 16 KB            | 512 W        | DIC64S<br>with window | QFC64<br>with window |                                                         |

| LC66P516                  | 64          | OTPROM 16 KB           | 512 W        | DIP64S                | QFP64E               |                                                         |

| LC66E2108*                | 30          | EPROM 8 KB             | 384 W        |                       |                      |                                                         |

| LC66E2316                 | 42          | EPROM 16 KB            | 512 W        | DIC42S<br>with window | QFC48<br>with window | Window evaluation versions                              |

| LC66E2516                 | 64          | EPROM 16 KB            | 512 W        | DIC64S<br>with window | QFC64<br>with window | 4.5 to 5.5 V/0.92 μs                                    |

| LC66E5316                 | 52/48       | EPROM 16 KB            | 512 W        | DIC52S<br>with window | QFC48<br>with window |                                                         |

| LC66P2108*                | 30          | OTPROM 8 KB            | 384 W        | DIP30SD               | MFP30S               |                                                         |

| LC66P2316*                | 42          | OTPROM 16 KB           | 512 W        | DIP42S                | QFP48E               | ОТР                                                     |

| LC66P2516                 | 64          | OTPROM 16 KB           | 512 W        | DIP64S                | QFP64E               | 4.0 to 5.5 V/0.95 μs                                    |

| LC66P5316                 | 48          | OTPROM 16 KB           | 512 W        | DIP48S                | QFP48E               |                                                         |

Note: \* Under development

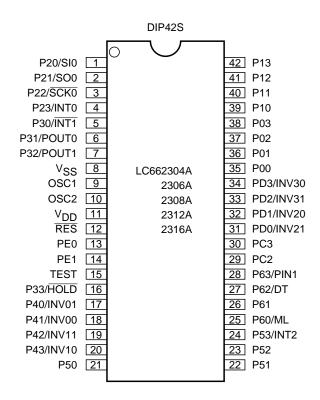

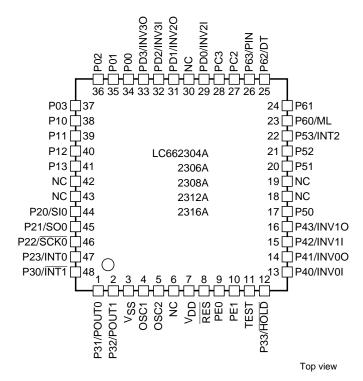

#### **Pin Assignments**

We recommend the use of reflow-soldering techniques to solder-mount QFP packages.

Please consult with your Sanyo representative for details on process conditions if the package itself is to be directly immersed in a dip-soldering bath (dip-soldering techniques).

### **System Block Diagram**

#### Differences between the LC663XX Series and the LC6623XX Series

| Item                                                                                                  | LC6630X Series<br>(Including the LC66599 evaluation chip)                                         | LC6635XB Series                                                                                        | LC6623XX Series                                                             |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| System differences  • Hardware wait time (number of cycles) when hold mode is cleared                 | 65536 cycles<br>About 64 ms at 4 MHz (Tcyc = 1 μs)                                                | 16384 cycles<br>About 16 ms at 4 MHz (Tcyc = 1 µs)                                                     | 16384 cycles<br>About 16 ms at 4 MHz (Tcyc = 1 µs)                          |

| Value of timer 0 after a reset<br>(Including the value after hold mode<br>is cleared)                 | Set to FF0.                                                                                       | Set to FFC.                                                                                            | Set to FFC.                                                                 |

| DTMF generator                                                                                        | None (Tools are handled with external devices.)                                                   | None                                                                                                   | Yes                                                                         |

| Inverter array                                                                                        | None (Tools are handled with external devices.)                                                   | None                                                                                                   | Yes                                                                         |

| • SIO1                                                                                                | Yes                                                                                               | Yes                                                                                                    | None                                                                        |

| Three-value inputs/comparator inputs                                                                  | Yes                                                                                               | Yes                                                                                                    | None                                                                        |

| Three-state output from P31 and P32                                                                   | None                                                                                              | None                                                                                                   | Yes                                                                         |

| Using P0 to clear halt mode                                                                           | In 4-bit groups                                                                                   | In 4-bit groups                                                                                        | Can be specified for each bit.                                              |

| External extended interrupts                                                                          | None for INT3, INT4, and INT5.<br>(Tools are handled with external<br>devices.)                   | None for INT3, INT4, and INT5.                                                                         | INT3, INT4, and INT5 can be used with the internal functions.               |

| Other P53 functions                                                                                   | Shared with INT2 (Tools are handled with external devices.)                                       | Shared with INT2                                                                                       | Shared with INT2                                                            |

| Differences in main characteristics • Operating power-supply voltage and operating speed (cycle time) | LC66304A/306A/308A     4.0 to 6.0 V/0.92 t 10 μs     LC66E308/P308     4.5 to 5.5 V/0.92 to 10 μs | • 3.0 to 5.5 V/0.92 to 10 µs<br>• LC6635XA<br>2.2 to 5.5 V/3.92 to 10 µs<br>3.0 to 5.5 V/1.96 to 10 µs | 3.0 to 5.5 V/0.95 to 10 μs                                                  |

| Pull-up resistors                                                                                     | P0, P1, P4, and P5: about 3 to 10 k                                                               | P0, P1, P4, and P5: about 3 to 10 k                                                                    | P0, P1, P4, and P5: about 100 k                                             |

| Port voltage handling                                                                                 | P2 to P6 and PC: 15-V handling P0, P1, PD, PE: Normal voltage handling                            | P2 to P6 and PC: 15-V handling P0, P1, PD, PE: Normal voltage handling                                 | P2, P3, P61, and P63: 12-V voltage handling Others: normal voltage handling |

### **Pin Function Overview**

| Pin                                              | I/O | Overview                                                                                                                                                                                                                                                                                                                                                                                                         | Output driver type                                                                                               | Options                                                                   | State after a reset                        | Standby mode operation                                                            |

|--------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|

| P00<br>P01<br>P02<br>P03                         | I/O | I/O ports P00 to P03 Input or output in 4-bit or 1-bit units P00 to P03 support the halt mode control function (This function can be specified in bit units.)                                                                                                                                                                                                                                                    | Pch: Pull-up MOS type     Nch: Intermediate sink current type                                                    | Pull-up MOS or<br>Nch OD output     Output level on<br>reset              | High or low (option)                       | Hold mode: Output off Halt mode: Output                                           |

|                                                  |     | oposition in the armony                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                  |                                                                           |                                            | retained                                                                          |

| P10<br>P11                                       | 1/0 | I/O ports P10 to P13                                                                                                                                                                                                                                                                                                                                                                                             | Pch: Pull-up MOS type     Nch: Intermediate sink current                                                         | Pull-up MOS or<br>Nch OD output                                           | High or low                                | Hold mode:<br>Output off                                                          |

| P12<br>P13                                       | "0  | Input or output in 4-bit or 1-bit units                                                                                                                                                                                                                                                                                                                                                                          | type                                                                                                             | Output level on<br>reset                                                  | (option)                                   | Halt mode:<br>Output<br>retained                                                  |

| P20/SI0<br>P21/SO0                               | I/O | I/O ports P20 to P23 Input or output in 4-bit or 1-bit units P20 is also used as the serial input SI0 pin. P21 is also used as the serial output SO0 pin.                                                                                                                                                                                                                                                        | Pch: CMOS type Nch: Intermediate sink current type                                                               | CMOS or Nch OD                                                            | н                                          | Hold mode:<br>Output off                                                          |

| P22/SCK0<br>P23/INT0                             | 170 | P22 is also used as the serial clock SCK0 pin. P23 is also used as the INT0 interrupt request pin, and also as the timer 0 event counting and pulse width measurement input.                                                                                                                                                                                                                                     | Nch: +12-V handling when<br>OD option selected                                                                   | output                                                                    | ·                                          | Halt mode:<br>Output<br>retained                                                  |

| P30/INT1<br>P31/POUT0                            | I/O | I/O ports P30 to P32 Input or output in 3-bit or 1-bit units P30 is also used as the INT1 interrupt request. P31 is also used for the square wave                                                                                                                                                                                                                                                                | Pch: CMOS type     Nch: Intermediate sink current type                                                           | CMOS or Nch OD                                                            | н                                          | Hold mode:<br>Output off                                                          |

| P32/POUT1                                        |     | output from timer 0.     P32 is also used for the square wave and PWM output from timer 1.     P31 and P32 also support 3-state outputs.                                                                                                                                                                                                                                                                         | Nch: +12-V handling when<br>OD option selected                                                                   | output                                                                    |                                            | Halt mode:<br>Output<br>retained                                                  |

| P33/ <del>HOLD</del>                             | I   | Hold mode control input  Hold mode is set up by the HOLD instruction when HOLD is low.  In hold mode, the CPU is restarted by setting HOLD to the high level.  This pin can be used as input port P33 along with P30 to P32.  When the P33/HOLD pin is at the low level, the CPU will not be reset by a low level on the RES pin. Therefore, applications must not set P33/HOLD low when power is first applied. |                                                                                                                  |                                                                           |                                            |                                                                                   |

| P40/INV0I<br>P41/INV0O<br>P42/INV1I<br>P43/INV1O | I/O | <ul> <li>I/O ports P40 to P43</li> <li>Input or output in 4-bit or 1-bit units</li> <li>Input or output in 8-bit units when used in conjunction with P50 to P53.</li> <li>Can be used for output of 8-bit ROM data when used in conjunction with P50 to P53.</li> </ul>                                                                                                                                          | Pch: Pull-up MOS type CMOS type when the inverter circuit option is selected Nch: Intermediate sink current type | Pull-up MOS or<br>Nch OD output Output level on<br>reset Inverter circuit | High or low<br>or inverter<br>I/O (option) | Hold mode: Port output off, inverter output off  Halt mode: Port output retained, |

| P41/INV0O<br>P42/INV1I                           | I/O | Input or output in 8-bit units when used in conjunction with P50 to P53.     Can be used for output of 8-bit ROM data when used in conjunction with                                                                                                                                                                                                                                                              | CMOS type when the inverter circuit option is selected     Nch: Intermediate sink current                        | Nch OD output  Output level on reset                                      | or inverter                                | outpu<br>Halt m<br>Port o                                                         |

Continued from preceding page.

| Pin                                              | I/O | Overview                                                                                                                                                                                                                                                                 | Output driver type                                                                                                  | Options                                                  | State after a reset                            | Standby mode operation                                                     |

|--------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|

| P50<br>P51<br>P52<br>P53/INT2                    | I/O | I/O ports P50 to P53 Input or output in 4-bit or 1-bit units Input or output in 8-bit units when used in conjunction with P40 to P43. Can be used for output of 8-bit ROM data when used in conjunction with P40 to P43. P53 is also used as the INT2 interrupt request. | Pch: Pull-up MOS type Nch: Intermediate sink current type                                                           | Pull-up MOS or<br>Nch OD output Output level on<br>reset | High or low<br>(option)                        | Hold mode:<br>Output off<br><br>Halt mode:<br>Output<br>retained           |

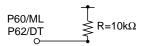

| P60/ML<br>P61<br>P62/DT<br>P63/PIN1              | I/O | I/O ports P60 to P63 Input or output in 4-bit or 1-bit units P60 is also used as the melody output ML pin. P62 is also used as the tone output DT pin. P63 is also used for the event count input to timer 1.                                                            | Pch: CMOS type  Nch: Intermediate sink current type  Nch: +12-V handling when OD option selected (P61 and P63 only) | CMOS or Nch OD output                                    | н                                              | Hold mode:<br>Output off<br>                                               |

| PC2<br>PC3                                       | I/O | I/O ports PC2 to PC3 Output in 2-bit or 1-bit units                                                                                                                                                                                                                      | Pch: CMOS type Nch: Intermediate sink current type                                                                  | CMOS or Nch OD output                                    | н                                              | Hold mode:<br>Port output<br>off<br>                                       |

| PD0/INV2I<br>PD1/INV2O<br>PD2/INV3I<br>PD3/INV4O | ı   | Dedicated input ports PD0 to PD3<br>Dedicated inverter circuits (option)                                                                                                                                                                                                 | When the inverter circuit option is selected.     Pch: CMOS type     Nch: Intermediate sink current type            | Inverter circuits                                        | Normal<br>input or<br>inverter I/O<br>(option) | Inverter • Hold mode: output off • Halt mode: output continues             |

| PE0<br>PE1                                       | ı   | Dedicated input ports                                                                                                                                                                                                                                                    |                                                                                                                     |                                                          | Normal input                                   |                                                                            |

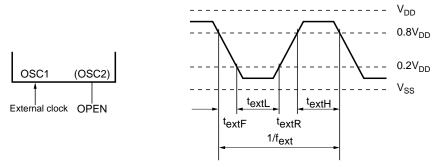

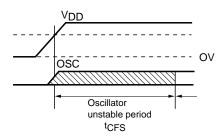

| OSC1                                             | 0   | System clock oscillator connections When an external clock is used, leave OSC2 open and connect the clock signal to OSC1.                                                                                                                                                |                                                                                                                     | Ceramic oscillator<br>or external clock<br>selection     | Option<br>selection                            | Hold mode:<br>Oscillator<br>stops<br>Halt mode:<br>Oscillator<br>continues |

| RES                                              | I   | System reset input When the P33/HOLD pin is at the high level, a low level input to the RES pin will initialize the CPU.                                                                                                                                                 |                                                                                                                     |                                                          |                                                |                                                                            |

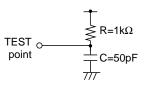

| TEST                                             | I   | CPU test pin This pin must be connected to V <sub>SS</sub> during normal operation.                                                                                                                                                                                      |                                                                                                                     |                                                          |                                                |                                                                            |

| $V_{DD}$ $V_{SS}$                                |     | Power supply pins                                                                                                                                                                                                                                                        |                                                                                                                     |                                                          |                                                |                                                                            |

Note: Pull-up MOS type: The output circuit includes a MOS transistor that pulls the pin up to V<sub>DD</sub>. CMOS output: Complementary output.

OD output: Open-drain output.

#### **User Options**

1. Port 0, 1, 4, and 5 output level at reset option

The output levels at reset for I/O ports 0, 1, 4, and 5 in independent 4-bit groups, can be selected from the following two options.

| Option                 | Conditions and notes                                    |

|------------------------|---------------------------------------------------------|

| Output high at reset   | The four bits of ports 0, 1, 4, or 5 are set in a group |

| 2. Output low at reset | The four bits of ports 0, 1, 4, or 5 are set in a group |

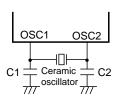

#### 2. Oscillator circuit options

• Main clock

| Option                | Circuit                             | Conditions and notes                  |

|-----------------------|-------------------------------------|---------------------------------------|

| 1. External clock     | OSC1                                | The input has Schmitt characteristics |

| 2. Ceramic oscillator | C1 OSC1  Ceramic oscillator C2 OSC2 |                                       |

Note: There is no RC oscillator option.

#### 3. Watchdog timer option

A runaway detection function (watchdog timer) can be selected as an option.

### 4. Port output type options

• The output type of each bit (pin) in ports P0, P1, P2, P3 (except for the P33/HOLD pin), P4, P5, P6, and PC can be selected individually from the following two options.

| Option                                | Circuit                       | Conditions and notes                                                                                                                                                                                                                |

|---------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open-drain output                     | Output data    DSB            | The port P2, P3, P5, and P6 inputs have Schmitt characteristics.                                                                                                                                                                    |

| Output with built-in pull-up resistor | Output data  DSB  Output data | The port P2, P3, P5, and P6 inputs have Schmitt characteristics.  The CMOS outputs (ports P2, P3, P6, and PC) and the pull-up MOS outputs (P0, P1, P4, and P5) are distinguished by the drive capacity of the p-channel transistor. |

### 5. Inverter array circuit option

One of the following options can be selected for each of the following port sets: P40/P41, P42/P43, PD0/PD1, and PD2/PD3. (PDs do not use option 1 because they are dedicated to input.)

| Option                  | Circuit                                                                                      | Conditions and notes                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Output data    DSB                                                                           | When the open-drain output type is selected                                                                                                                                           |

| Normal port I/O circuit | Output data  Input data                                                                      | When the built-in pull-up resistor output type is selected                                                                                                                            |

| 2. Inverter I/O circuit | Output data high Output data Output data DSB Output data Output data Output data Output data | If this option is selected, The I/O circuit is disabled by the DSB signal. Also note that the open-drain port output type option and the high level at reset option must be selected. |

# LC662316 Series Option Data Area and Definitions

| FF0H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ROM area | Bit |        | Option specified      | Option/data relationship      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|--------|-----------------------|-------------------------------|--|

| SFF0H   S   Unused   This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | 7   | P5     |                       |                               |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | 6   |        | Output level at leset | ·                             |  |

| 3   Unused   This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |     |        |                       |                               |  |

| 3   Unused   This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3FF0H    |     |        | option                |                               |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |     |        |                       | This bit must be set to 0.    |  |

| O   Watchdog timer option   O = none, 1 = yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |     |        | Output level at reset | 0 = low level, 1 = high level |  |

| FF1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |     | -      | times and in          | 0                             |  |

| SF1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |     |        | uner option           | 0 = Horie, 1 = yes            |  |

| 3FF1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |     |        |                       |                               |  |

| 3FF1H  4 P10 3 P03 2 P02 1 P01 0 P00  7 Unused 6 P32 5 P31 4 P30 3 P23 2 P22 1 P21 1 P21 0 P20 7 P53 6 P52 5 P51 4 P50 3 3 P43 2 P42 1 P41 0 P40  3FF3H  3FF3H  3FF3H  4 P50 3 P63 2 P62 1 P61 5 Unused  This bit must be set to 0.  0 = OD, 1 = PU  This bit must be set to 0.  0 = OD, 1 = PU  0 = OD, 1 = PU  This bit must be set to 0.  0 = OD, 1 = PU  This bit must be set to 0.  1 P0  2 P0  2 P0  3 P63 3 P63 3 P63 4 P50 5 Dutput type  0 = OD, 1 = PU  This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |     |        | Output type           | 0 = OD, 1 = PU                |  |

| 3FF1H  3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |     |        |                       |                               |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3FF1H    |     |        |                       |                               |  |

| 1 P01 0 P00 7 Unused 6 P32 5 P31 3 P23 2 P22 1 P21 0 P20 7 P53 6 P52 5 P51 4 P50 3 P43 2 P42 1 P41 0 P40 0 Unput type 0 = OD, 1 = PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |     |        |                       |                               |  |

| 7 Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |     |        | Output type           | 0 = OD, 1 = PU                |  |

| 3FF2H     6     P32       5     P31     Output type     0 = OD, 1 = PU       4     P30     3     P23       2     P22     1     P21       1     P50     Output type     0 = OD, 1 = PU       3     P43     Output type     0 = OD, 1 = PU       3     P43     Output type     0 = OD, 1 = PU       4     P50     Output type     0 = OD, 1 = PU       7     Output type     0 = OD, 1 = PU       7     Output type     0 = OD, 1 = PU       7     Output type     0 = OD, 1 = PU       7     Output type     0 = OD, 1 = PU       7     Output type     0 = OD, 1 = PU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 0   | P00    |                       |                               |  |

| 3FF2H    5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | 7   | Unused |                       | This bit must be set to 0.    |  |

| 3 FF2H  4 P30 3 P23 2 P22 1 P21 0 P20 7 P53 6 P51 4 P50 3 P43 2 P42 1 P41 0 P40  Output type  0 = OD, 1 = PU  This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | 6   | P32    |                       |                               |  |

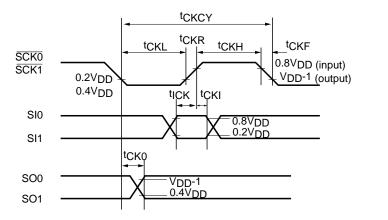

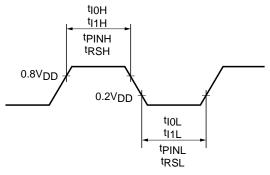

| 3 P23 2 P22 1 P21 0 P20 7 P53 6 P52 5 P51 4 P50 3 P43 2 P42 1 P41 0 P40  Output type  0 = OD, 1 = PU  This bit must be set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | 5   | P31    | Output type           | 0 = OD, 1 = PU                |  |