# 2 x 35W POWER AMPLIFIER FOR CAR RADIO

- HIGH OUTPUT POWER CAPABILITY: 2 x 40W max./4Ω

2 x 35W/4Ω EIAJ

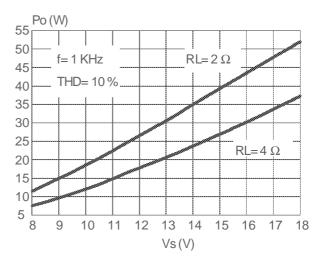

2 x 25W4Ω @ 14.4V, 1KHz, 10%

2 x 37W2Ω @ 14.4V, 1KHz, 10%

- 2Ω DRIVING

- DIFFERENTIAL INPUTS

- MINIMUM EXTERNAL COMPONENT COUNT

- INTERNALLY FIXED GAIN (26dB)

- MUTE FUNCTION (CMOS COMPATIBLE)

- AUTOMUTE AT MINIMUM SUPPLY VOLT-AGE DETECTION

- STAND-BY FUNCTION

- NO AUDIBLE POP DURING MUTE AND ST-BY OPERATIONS

- CLIPPING DETECTOR WITH PROGRAMMA-BLE DISTORTION THRESHOLD

#### **PROTECTIONS:**

- SHORT CIRCUIT (OUT TO GROUND, OUT TO SUPPLY VOLTAGE, ACROSS THE LOAD)

- OVERRATING CHIP TEMPERATURE WITH SOFT THERMAL LIMITER

- LOAD DUMP VOLTAGE

- FORTUITOUS OPEN GROUND

- LOUDSPEAKER DC CURRENT

- ESD

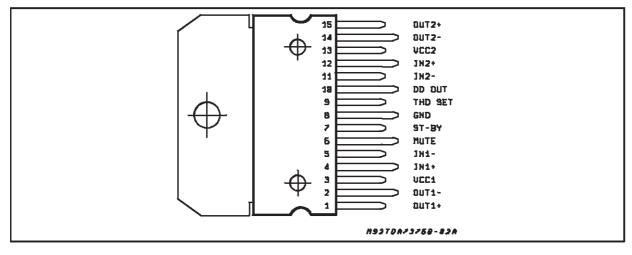

#### **PIN CONNECTION** (Continued)

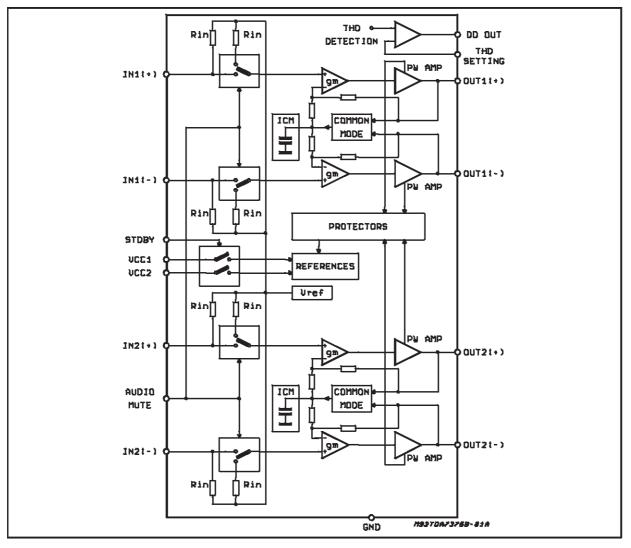

#### DESCRIPTION

The TDA7376B is a new technology dual bridge Audio Amplifier in Multiwatt 15 package designed for car radio applications. Thanks to the fully complementary PNP/NPN output stage configuration the TDA7376B delivers a rail-to-rail voltage swing with no need of bootstrap capacitors. Differential input pairs, that will accept either single ended or differential input signals, guarantee high noise immunity making the device suitable for both car radio and car boosters applications.

The audio mute control, that attenuates the output signal of the audio amplifiers, suppresses pop on - off transients and cuts any noises coming from previous stages. The St-By control, that debiases the amplifiers, reduces the cost of the power switch. The on-board programmable distortion detector allows compression facility whenever the amplifier is overdriven, so limiting the distortion at any levels inside the presettable range.

May 2000

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Parameter                                                                       | Value      | Unit   |

|-----------------------|---------------------------------------------------------------------------------|------------|--------|

| V <sub>OP</sub>       | Operating Supply Voltage                                                        | 18         | V      |

| Vs                    | DC Supply Voltage                                                               | 28         | V      |

| V <sub>peak</sub>     | Peak Supply Voltage (t = 50ms)                                                  | 50         | V      |

| lo                    | Output Peak Current (non rep. t = 100μs)<br>Output Peak Current (rep. f > 10Hz) | 8<br>6     | A<br>A |

| P <sub>tot</sub>      | Power Dissipation at $T_{case} = 85^{\circ}C$                                   | 36         | W      |

| T <sub>stg</sub> , Tj | Storage and Junction Temperature                                                | -40 to 150 | °C     |

#### THERMAL DATA

| Symbol                 | Parameter                             | Value | Unit |

|------------------------|---------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case max. | 1.8   | °C/W |

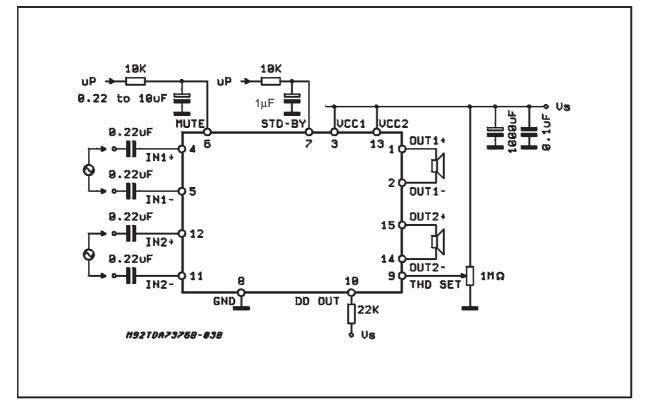

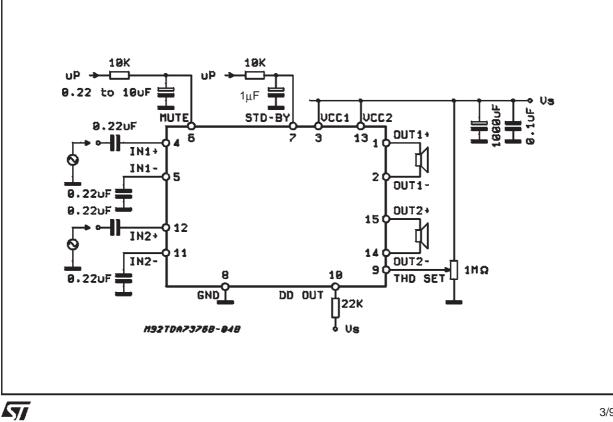

Figure 1: Differential Inputs Test and Application Circuit

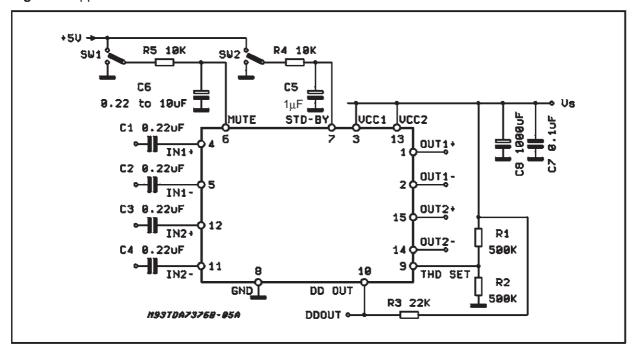

Figure 2: Single Ended Inputs Test and Application Circuit

3/9

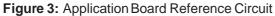

Figure 4: P.C. Board and Components Layout of the Circuit of Fig. 3 (1:1 scale)

| Symbol             | Parameter                                | Test Condition                                                                                    | Min.     | Тур.         | <b>Max.</b><br>18 | Unit<br>V |

|--------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|----------|--------------|-------------------|-----------|

| Vs                 | Supply Voltage                           |                                                                                                   | 8        |              |                   |           |

| I <sub>d</sub>     | Total Quiescent Drain Current            | $R_L = \infty$                                                                                    |          |              | 200               | mA        |

| V <sub>OS</sub>    | Output Offset Voltage                    |                                                                                                   |          |              | 120               | mV        |

| Po                 | Output Power                             | THD = 10%<br>THD = 10%, RL 2Ω                                                                     | 23<br>33 | 25<br>37     |                   | W<br>W    |

| P <sub>O max</sub> | Max. Output Power (*)                    | VS = 14.4V                                                                                        | 36       | 40           |                   | W         |

| Po eiaj            | EIAJ Output Power (*)                    | V <sub>S</sub> = 13.7V                                                                            | 32       | 35           |                   | W         |

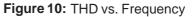

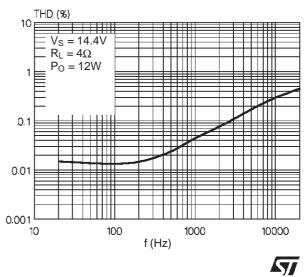

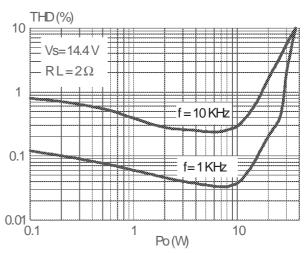

| THD                | Distortion                               | Distortion $P_O = 0.5 \text{ to } 10W$<br>$P_O = 0.5 \text{ to } 15W$                             |          | 0.03<br>0.08 | 0.3<br>0.5        | %<br>%    |

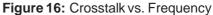

| C <sub>T</sub>     | Cross Talk                               | f = 1KHz; Rg = 0<br>f = 10KHz; Rg = 0                                                             |          | 80<br>70     |                   | dB<br>dB  |

| R <sub>IN</sub>    | Input Resistance                         | differential input<br>single ended input                                                          | 45<br>40 |              |                   | ΚΩ<br>ΚΩ  |

| G <sub>V</sub>     | Voltage Gain                             | differential input<br>single ended input                                                          | 25<br>25 | 26<br>26     | 27<br>27          | dB<br>dB  |

| $\Delta G_V$       | Channel Gain Balance                     |                                                                                                   |          |              | 1                 | dB        |

| E <sub>N</sub>     | Input Noise Voltage                      | Rg = $600\Omega$ ; "A Weighted"<br>Rg = $600\Omega$ ; 22Hz to 22KHz                               |          | 3<br>4       | 6                 | μV<br>μV  |

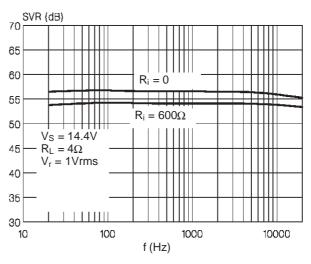

| SVR                | Supply Voltage Rejection                 | f = 100Hz; Vr = 1Vrms; 45<br>Rg = 0<br>f = 10KHz; Vr = 1Vrms;<br>Rg = 0                           |          | 55           |                   | dB<br>dB  |

| BW                 | Power Bandwidth                          | (-3dB)                                                                                            | 75       |              |                   | KHz       |

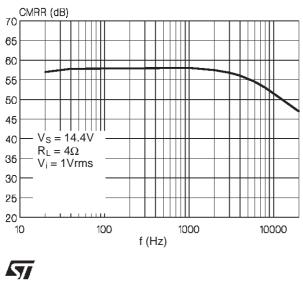

| CMRR               | Common Mode Rejection Ratio              | V <sub>CM</sub> = 1Vrms input referred                                                            | 60       |              |                   | dB        |

| A <sub>SB</sub>    | Stand-by Attenuation                     | $V_{SB} = 1.5V$ ; $P_{Oref} = 1W$                                                                 | 80       | 90           |                   | dB        |

| $V_{\text{sb IN}}$ | Stand-by in Threshold                    |                                                                                                   |          |              | 1.5               | V         |

| $V_{sb \ OUT}$     | Stand-by out Threshold                   |                                                                                                   | 3.5      |              |                   | V         |

| I <sub>sb</sub>    | Stand-by Current Consumption             |                                                                                                   |          |              | 100               | μA        |

| A <sub>M</sub>     | Mute Attenuation                         | $V_{M} = 1.5V; P_{Oref} = 1W$                                                                     |          | 85           |                   | dB        |

| V <sub>MIN</sub>   | Mute in Threshold                        |                                                                                                   |          |              | 1.5               | V         |

| V <sub>M OUT</sub> | Mute out Threshold                       |                                                                                                   | 3.5      |              |                   | V         |

| $I_6$              | Mute pin Current                         | $V6 = 0 \text{ to } V_{S}, ; V_{S \text{ max.}} = 18V$                                            |          |              | 100               | μA        |

| D <sub>DL</sub>    | Distortion Detection Level (**)          |                                                                                                   | 3.5      |              |                   | %         |

| D <sub>DOUT</sub>  | Distortion Detector Output DC<br>Current | Output low, sinked current<br>(V <sub>pin10</sub> = 1.5V)                                         | 1        |              |                   | mA        |

|                    |                                          | Output high, leakage current<br>(V <sub>pin10</sub> = V <sub>S</sub> , @ V <sub>Smax</sub> = 18V) |          |              | 10                | μΑ        |

**ELECTRICAL CHARACTERISTICS** (Refer to the test fig. 1 and 2 circuit,  $T_{amb} = 25^{\circ}C$ ;  $V_S = 14.4V$ ;  $f = 1 KHz; R_L = 4\Omega;$  unless otherwise specified.)

(\*) Saturated square wave output (\*\*) see figure 5 for THD setting.

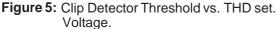

The TDA7376B is equipped with a programmable clipping distortion detector circuitry that allows to signal out the output stage saturation by providing a current sinking into an open collector output (DDout) when the total harmonic distortion of the output signal reaches the preset level. The desired threshold is fixed through an external divider that produces a proper voltage level across the

THD set pin. Fig. 5 shows the THD detection threshold versus the THD set voltage. Since it is essential that the THD set voltage be proportional to the supply voltage, fig. 5 shows its value as a fraction of  $V_{CC}.$  The actual voltage can be computed by multiplying the fraction corresponding to the desired THD threshold by the application's supply voltage.

THD (%) 16  $V_{\rm S} = 14.4V$ 14  $R_L = 4\Omega$ f = 1 KHz12 10 8 6 4 2 0 0.1Vs 0.2Vs 0.3Vs 0.4Vs 0.5Vs 0.6Vs

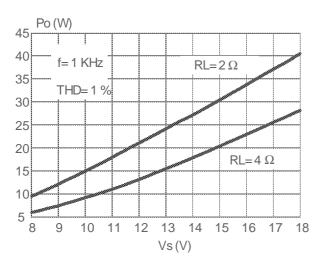

#### Figure 7: Ouput Power vs. Supply Voltage

THD SET (V)

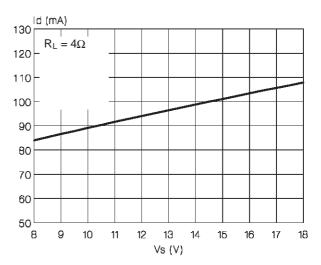

Figure 6: Quiescent Current vs. Supply Voltage

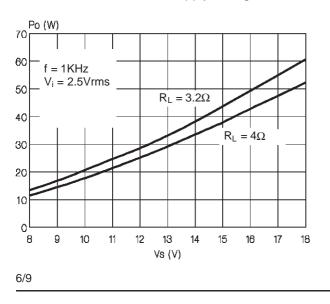

Figure 8: Ouput Power vs. Supply Voltage

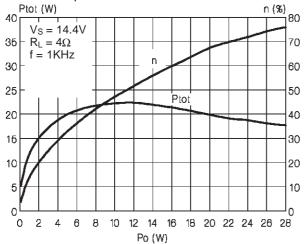

Figure 13: Dissipated Power & Efficiency vs. Output Power

**Figure 12:** THD vs. Output Power ( $R_L = 24\Omega$ )

Figure 14: SVR vs. Frequency

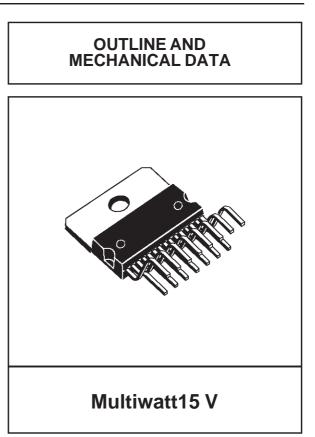

| DIM.   | mm    |       |       | inch  |       |       |

|--------|-------|-------|-------|-------|-------|-------|

| Dilvi. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α      |       |       | 5     |       |       | 0.197 |

| В      |       |       | 2.65  |       |       | 0.104 |

| С      |       |       | 1.6   |       |       | 0.063 |

| D      |       | 1     |       |       | 0.039 |       |

| E      | 0.49  |       | 0.55  | 0.019 |       | 0.022 |

| F      | 0.66  |       | 0.75  | 0.026 |       | 0.030 |

| G      | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |

| G1     | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.710 |

| H1     | 19.6  |       |       | 0.772 |       |       |

| H2     |       |       | 20.2  |       |       | 0.795 |

| L      | 21.9  | 22.2  | 22.5  | 0.862 | 0.874 | 0.886 |

| L1     | 21.7  | 22.1  | 22.5  | 0.854 | 0.870 | 0.886 |

| L2     | 17.65 |       | 18.1  | 0.695 |       | 0.713 |

| L3     | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |

| L4     | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |

| L7     | 2.65  |       | 2.9   | 0.104 |       | 0.114 |

| М      | 4.25  | 4.55  | 4.85  | 0.167 | 0.179 | 0.191 |

| M1     | 4.63  | 5.08  | 5.53  | 0.182 | 0.200 | 0.218 |

| S      | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| S1     | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| Dia1   | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2001 STMicroelectronics - Printed in Italy - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com