# FULLY PROGRAMMABLE FOUR CHANNEL CODEC AND FILTER

PRODUCT PREVIEW

- FULLY PROGRAMMABLE MONOLITHIC 4 CHANNEL CODEC/FILTER

- SINGLE +3.3V SUPPLY

- A/m LAW PROGRAMMABLE

- LINEAR CODING (16 BITS) OPTION

- PCM HIGHWAY FORMAT AUTOMATICALLY DETECTED:1.536 or 1.544 MHz2.048, 4.096, 8192 MHz

- TWO PCM PORTS AVAILABLE

- TX GAIN PROGRAMMING: 15dB RANGE; <0.1dB STEP</p>

- RX GAIN PROGRAMMING:24dB RANGE; <0.1dB STEP</p>

- PROGRAMMABLE SLIC INPUT IMPEDANCE

- PROGRAMMABLE TRANSHYBRID BALANCE FILTER

- PROGRAMMABLE EQUALIZATION (FREQUENCY RESPONSE)

- PROGRAMMABLE TIME SLOT ASSIGNMENT

- DIGITAL AND ANALOG LOOPBACKS

- SLIC CONTROL PORTSTATIC (16 I/Os) DYNAMIC (12 I/Os + 4 CS)

- BUILT-IN TEST MODE WITH TONE GENERATION, MCU ACCESS TO PCM DATA

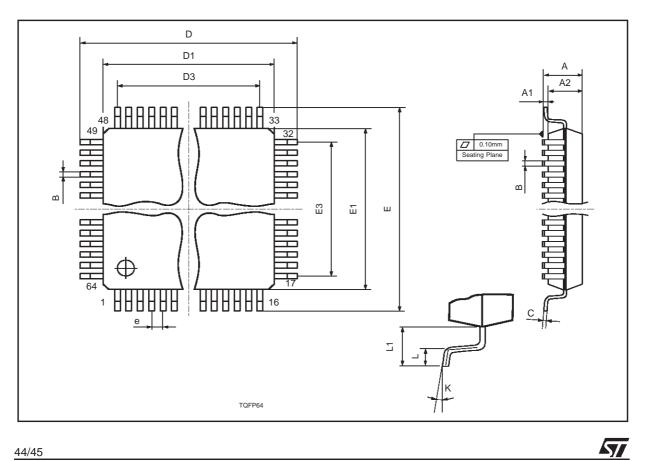

- 64 TQFP (10X10mm) PACKAGE

- PROGRAMMABLE SLIC LINE CURRENT LIMITATION

- PROGRAMMABLE SLIC OFF-HOOK DETECTION THRESHOLD

### DESCRIPTION

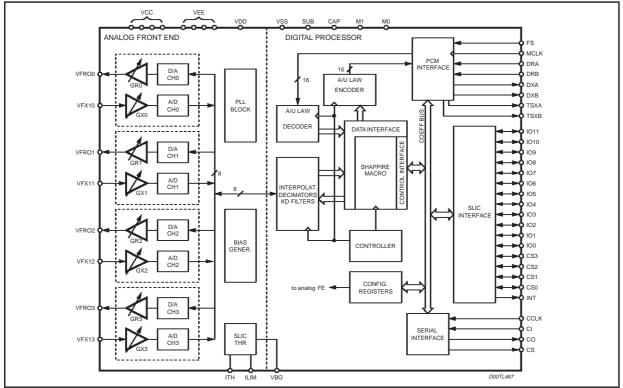

The STLC5048 is a monolithic fully programmable 4 channel CODEC and filter. It operates with a single +3.3V supply.

The analog interface is based on a receive output buffer driving the SLIC RX input and on an amplifier input stage normally driven by the SLIC TX output. Due to the single supply voltage a midsupply reference level is generated internally by the device and all analog signals are referred to this level (AGND). The PCM interface uses one common 8KHz frame sync. pulse for transmit and receive direction. The bit clock is automatically detected between four standards: 1.563/1.544MHz, 2.048MHz, 4.096MHz, 8192MHz.

Two PCM port are provided: the channels can be connected to port A or/and B.

Device programmability is achieved by means of several registers and commands allowing to set the different parameters like TX/RX gains, line impedance, transhybrid balance, equalization (frequency response), encoding law  $(A/\mu)$ , time slot assignment, independent channels power up/down, loopbacks, PCM bits offset.

The STLC5048 can be programmed via serial interface running up to 8 MHz. One interrupt output pin is also provided.

September 2000

This is preliminary information on a new product now in development. Details are subject to change without notice.

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                                                                                       | Value                                        | Unit |

|-------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------|------|

| V <sub>CC</sub>   | V <sub>CC</sub> to V <sub>EE</sub>                                                              | 4.6                                          | V    |

| V <sub>DD</sub>   | V <sub>DD</sub> to V <sub>SS</sub>                                                              | 4.6                                          | V    |

| VD <sub>IN</sub>  | Digital Input Pin Voltage                                                                       | 5.5                                          | V    |

| VAin              | Analog Input Pin Voltage(V <sub>DD</sub> =V <sub>CC</sub> ; V <sub>EE</sub> =V <sub>SUB</sub> ) | V <sub>CC</sub> + 0.5; V <sub>EE</sub> - 0.5 | V    |

| T <sub>STG</sub>  | Storage Temperature Range                                                                       | -65 to +150                                  | °C   |

| T <sub>LEAD</sub> | Lead Temperature (soldering, 10s)                                                               | 300                                          | °C   |

# **OPERATING RANGE**

| Symbol                            | Parameter                   | Value      | Unit |

|-----------------------------------|-----------------------------|------------|------|

| V <sub>CC</sub> , V <sub>DD</sub> | Supply Voltage              | 3.3 +/- 5% | V    |

| T <sub>OP</sub>                   | Operating Temperature Range | -40 to +85 | °C   |

# THERMAL DATA

| Symbol                | Parameter                           | Value | Unit |

|-----------------------|-------------------------------------|-------|------|

| R <sub>th j-amb</sub> | Thermal Resistance Junction-Ambient | 70    | °C/W |

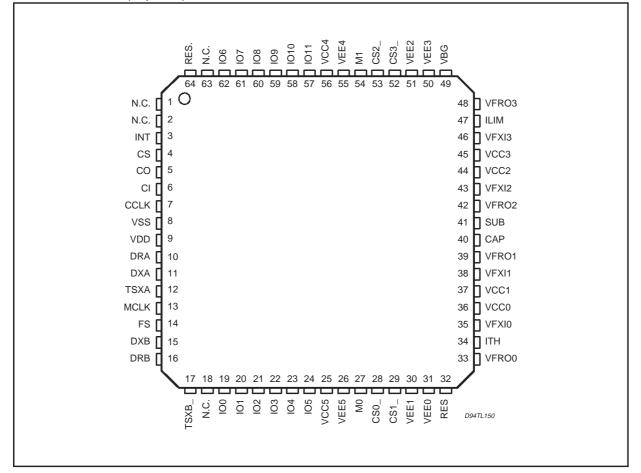

# **PIN CONNECTION** (Top view)

# PIN DESCRIPTION

# I/O DEFINITION

| Туре | Definition              |

|------|-------------------------|

| AI   | Analog Input            |

| AO   | Analog Output           |

| ODO  | Open Drain Output       |

| DI   | Digital Input           |

| DO   | Digital Output          |

| DIO  | Digital Input / Output  |

| DTO  | Digital Tristate Output |

| DPS  | Digital Power Supply    |

| APS  | Analog Power Supply     |

# PIN DESCRIPTION (continued)

ANALOG PIN DESCRIPTION

| No. | Name  | Туре | Description                                                                                                                                       |

|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 33  | VFRO0 | AO   | Receive analog amplifier output channel 0. PCM data received on<br>the programmed Time Slot on DR input is decoded and appears at<br>this output. |

| 39  | VFRO1 | AO   | Receive analog amplifier output channel 1. PCM data received on<br>the programmed Time Slot on DR input is decoded and appears at<br>this output. |

| 42  | VFRO2 | AO   | Receive analog amplifier output channel 2. PCM data received on<br>the programmed Time Slot on DR input is decoded and appears at<br>this output. |

| 48  | VFRO3 | AO   | Receive analog amplifier output channel 3. PCM data received on<br>the programmed Time Slot on DR input is decoded and appears at<br>this output. |

| 35  | VFXI0 | AI   | TX Input Amplifier channel 0. Typ $1M\Omega$ input impedance                                                                                      |

| 38  | VFXI1 | AI   | TX Input Amplifier channel 1. Typ $1M\Omega$ input impedance                                                                                      |

| 43  | VFXI2 | AI   | TX Input Amplifier channel 2. Typ $1M\Omega$ input impedance                                                                                      |

| 46  | VFXI3 | AI   | TX Input Amplifier channel 3. Typ $1M\Omega$ input impedance                                                                                      |

| 40  | CAP   |      | AGND Voltage filter pin: a 100nF capacitor must be connected between ground and this pin.                                                         |

| 34  | ITH   | AO   | SLIC Off Hook detection threshold.                                                                                                                |

| 47  | ILIM  | AO   | SLIC line current limitation.                                                                                                                     |

| 49  | VBG   | AI   | SLIC VBG reference for DC characterisrics programmability.                                                                                        |

# NOT CONNECTED

| 2, 18, 63, 1 | N.C. | Not Connected, must be left open           |

|--------------|------|--------------------------------------------|

| 32, 64       | RES  | Reserved pins, must be connected to ground |

# POWER SUPPLY PIN DESCRIPTION

| 25,36,<br>37,44,<br>45,56 | VCC05 | APS | Total 6 pins: 3.3V analog power supplies, should be shorted together, require 100nF decoupling capacitor to VEE. |

|---------------------------|-------|-----|------------------------------------------------------------------------------------------------------------------|

| 26,30,<br>31,50,<br>51,55 | VEE05 | APS | Total 6 pins: analog ground, should be shorted together.                                                         |

| 9                         | VDD   | DPS | Digital Power supply 3.3V, require 100nF decoupling capacitor to VSS.                                            |

| 8                         | VSS   | DPS | Digital Ground.                                                                                                  |

| 41                        | SUB   | DPS | Substrate connection. Must be shorted together with VEE and VSS pins.                                            |

# PIN DESCRIPTION (continued)

DIGITAL PIN DESCRIPTION

| No.      | Name     | Туре | Description                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|----------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 27<br>54 | M0<br>M1 | DI   | Mode Select.M1M0Mode select00Reset Status10Normal Operation01Not Allowed11Not Allowed                                                                                                                                                                                                                                             |  |  |  |  |  |

| 14       | FS       | DI   | Frame Sync. Pulse. A pulse or a square waveform with an 8kHz repetition rate is applied to this pin to define the start of the receive and transmit frame. Effective start of the frame can be then shifted of up to 7 clock pulses independently in receive and transmit directions by proper programming of the PCMSH register. |  |  |  |  |  |

| 13       | MCLK     | DI   | Master Clock Input.<br>Four possible frequencies can be used:<br>1.536/1.544 MHz; 2.048 MHz; 4.096 MHz; 8.192 MHz.<br>The device automatically detect the frequency applied.<br>This signal is also used as bit clock and it is used to shift data into<br>and out of the DRA/B and DXA/B pins.                                   |  |  |  |  |  |

| 12       | TSXA     | ODO  | Transmit Time Slot (open drain output, 3.2mA). Normally it is floating<br>in high impedance state except when a time slot is active on the DXA<br>output. In this case TSXA output pulls low to enable the backplane<br>line driver.                                                                                              |  |  |  |  |  |

| 11       | DXA      | DTO  | Transmit PCM interface A. It remains in high impedance state except<br>during the assigned time slots during which the PCM data byte is<br>shifted out on the rising edge of MCLK.                                                                                                                                                |  |  |  |  |  |

| 10       | DRA      | DI   | Receive PCM interface A. It remains inactive except during the assigned receive time slots during which the PCM data byte is shifted in on the falling edge of MCLK.                                                                                                                                                              |  |  |  |  |  |

| 24       | 105      | DIO  | General control I/O pin #5. Can be programmed as input or output via DIR register. Depending on content of CONF register can be a static input/output or a dynamic input/output synchronised with the CSn output signals controlling the SLICs.                                                                                   |  |  |  |  |  |

| 62       | IO6      | DIO  | General control I/O pin #6. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 61       | 107      | DIO  | General control I/O pin #7. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 60       | IO8      | DIO  | General control I/O pin #8. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 59       | IO9      | DIO  | General control I/O pin #9. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 58       | IO10     | DIO  | General control I/O pin #10. (see IO5 description).                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 57       | IO11     | DIO  | General control I/O pin #11. (see IO5 description).                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 19       | IO0      | DIO  | General control I/O pin #0. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 20       | IO1      | DIO  | General control I/O pin #1. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 21       | 102      | DIO  | General control I/O pin #2. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 22       | 103      | DIO  | General control I/O pin #3. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 23       | 104      | DIO  | General control I/O pin #4. (see IO5 description).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

\_\_\_\_\_

# PIN DESCRIPTION (continued)

DIGITAL PIN DESCRIPTION (continued

| No. | Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

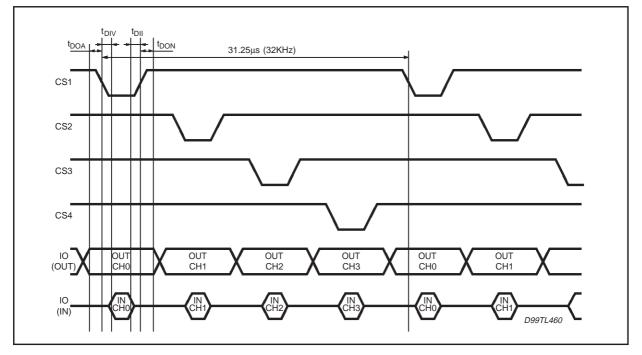

| 28  | CS0  | DIO  | Slic CS control #0. Depending on CONF reg. content can be a CS output for SLIC #0 or a static I/O.<br>When configured as CS output it is automatically generated by the CODEC with a repetition time of 31.25ms. In this mode also the IO011 are synchronised and carry proper data in and out synchronous with CS.<br>When configured as static I/O, the direction is defined by CSDIR register content. |  |  |  |

| 29  | CS1  | DIO  | Slic CS control #1, (see CS0 description).                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 53  | CS2  | DIO  | Slic CS control #2, (see CS0 description).                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 52  | CS3  | DIO  | Slic CS control #3, (see CS0 description).                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4   | CS   | DI   | Chip Select Input, when this pin is low control information can be written to or read from the device via the CI and CO pins.                                                                                                                                                                                                                                                                             |  |  |  |

| 7   | CCLK | DI   | Clock of Serial Control Bus. This clock shifts serial control information into or out of CI or CO when CS input is low depending on the current instruction. CCLK may be asynchronous with the other system clocks.                                                                                                                                                                                       |  |  |  |

| 6   | CI   | DI   | Control Data Input of Serial Control Bus.<br>Control data is shifted in the device when CS is low and clocked by<br>CCLK. Depending on the addressed register different numbers of<br>consecutive bytes can be loaded.                                                                                                                                                                                    |  |  |  |

| 5   | со   | DI   | Control Data Output of Serial Control Bus.<br>Control data is shifted out the device when CS is low and clocked<br>CCLK. Depending on the addressed register different numbers of<br>consecutive bytes can be shifted out.                                                                                                                                                                                |  |  |  |

| 3   | INT  | ODO  | Interrupt output (open drain), goes low when a data change has been detected in the I/O pins or another interrupt source is active. One mask register allows to mask any I/O pin. Interrupt is reset when the I/O register is read.                                                                                                                                                                       |  |  |  |

| 17  | TSXB | ODO  | Transmit Time Slot (open drain output, 3.2mA). Normally it is floating<br>in high impedance state except when a time slot is active on the DXB<br>output. In this case TSXB output pulls low to enable the backplane<br>line driver.                                                                                                                                                                      |  |  |  |

| 15  | DXB  | DTO  | Transmit PCM interface B. It remains in high impedance state except<br>during the assigned time slots during which the PCM data byte is<br>shifted out on the rising edge of MCLK.                                                                                                                                                                                                                        |  |  |  |

| 16  | DRB  | DI   | Receive PCM interface B. It remains inactive except during the assigned receive time slots during which the PCM data byte is shifted in on the falling edge of MCLK.                                                                                                                                                                                                                                      |  |  |  |

# FUNCTIONAL DESCRIPTION

The STLC5048 is a fully programmable device with embedded ROM and RAM. The ROM is used to contain the default state coefficients for the programmable filters, while the RAM is used to load the desired coefficient values.

# POWER ON INITIALIZATION

When power is first applied it is recommended to reset the device (M1=M0=0) in order to set all the internal registers to the reset value (see register description); this means also power down mode for all the four channels and SW reset bit (RES) set in the CONF register.

When the RES bit is set, the only instructions allowed are the one that disable this bit and the REACOM instruction: all other instructions are ignored. It is not possible to disable the RES bit and write the other bits of the CONF register with the same instruction.

Of course, RESET mode can be programmed also by writing the RES bit of the CONF register.

See appendix C for the power up sequence.

During RESET condition all the I/On and CSn pins are set as inputs, DX is in high impedance and all VFROn are set to AGND. After the reset all registers are loaded with the reset value.

It means that the PCM interface and all the VFRO outputs are configured as described in the Power Down State, while no transmit or receive time slot are set.

Then, filters and gain blocks are configured with the coefficient defined in the Default State.

### POWER DOWN STATE

Each of the four channel may be put into power down mode by setting the appropriate bit in the CONF register. In this mode the eventual programmed DX channel is set in high impedance while the VFRO outputs are forced to AGND. When all the channels are set in Power Down mode the device enters the Power Down state: all the blocks related to the data processing are turned off, while the RAM is On or Off according to the PDR bit value in the COMEN register.

# **DEFAULT STATE**

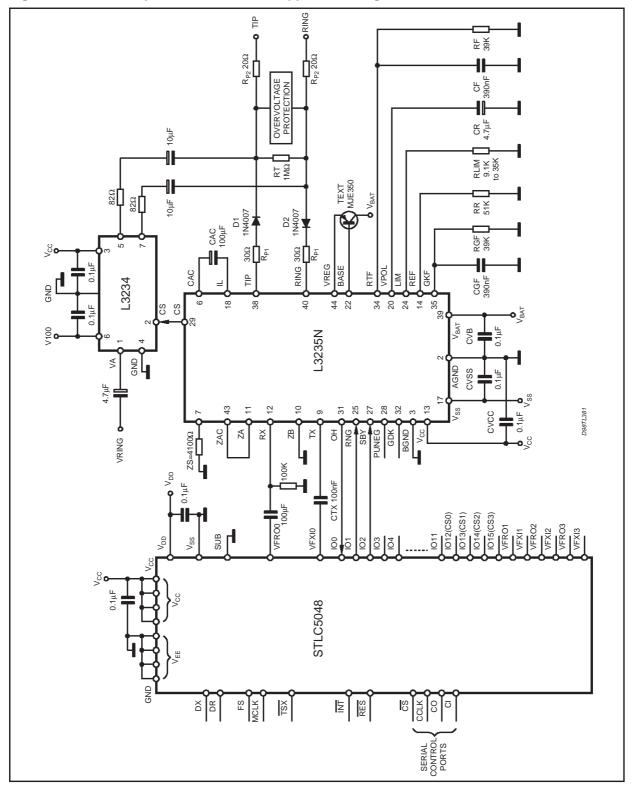

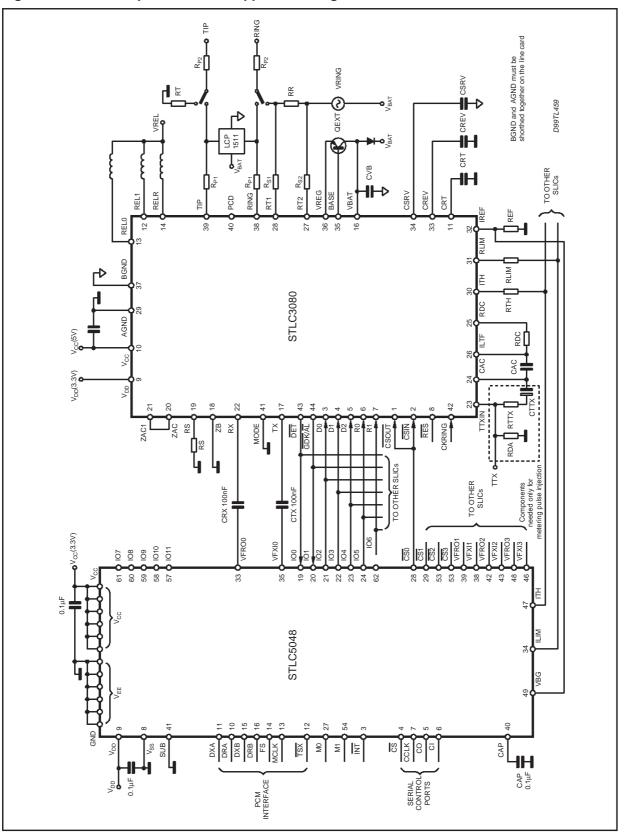

This state corresponds to the default one that the device assumes after the power on initialization. It means B, Z, X, R, KD and KA blocks configured to work in kit with the STLC3080 or L3235N SLICs and a reference impedance of 600 Ohm (without metering pulse management).

To switch to this state a bit (FD0..3) in the COEFST register must be set for every channel.

The programmed values for the previous blocks become active only when the FD and FR (see ringing state) bits are reset.

In this state the gain programmable blocks are set as described for the absolute gain levels (see electrical characteristics)

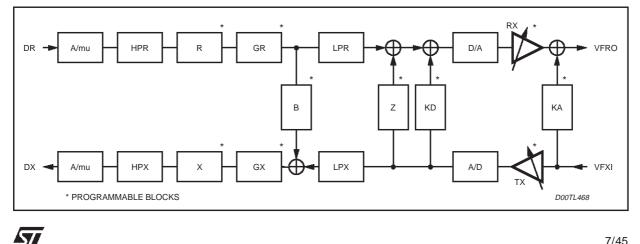

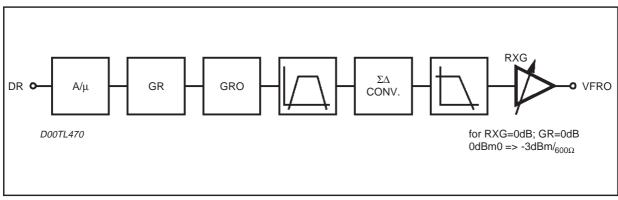

### Figure 1. Block Diagram of a single channel.

# **FUNCTIONAL DESCRIPTION (continued)**

### **RINGING STATE**

This state can be used during the ringing phase in order to transmit a low frequency ringing signal (25-50 Hz). In order to obtain a 1 Vrms ringing signal at VFRO output a digital signal DR equal to -0.78dBm0 must be provided.

This state means B, Z, X, KD and KA blocks equal to open circuits and the R block configured in order to obtain the maximum gain at the frequency of 25-50 Hz. During the ringing state if the TX time slot is enabled the idle PCM code is forced to DX.

To switch to this state, a bit (FR0..3) in the COEFST register must be set for every channel.

The programmed values for the previous blocks become active only when the FR and FD bits are reset.

If both FR and FD bits of a channel are set, the selected coefficient will be those of the Ringing State.

# IMPEDANCE SYNTHESYS

The impedance synthesis is performed by fully digital filters (Z and KD) for complex impedances.

For the 600 and 900 Ohms impedance the analog filter KA together with Z performs the synthesis.

The Z, KD and KA filters report to the receive path the feedback signal coming from the transmit path. The coefficients of the Z, KD and KA filters are programmed via the ZFC, KD and AFE\_CFF commands respectively.

# ECHO CANCELING

The trans-hybrid balance is performed by the digital programmable filter B.

The B filter reports to the transmit path the signal coming from the receive path. The coefficient of the B filter are programmed via the BFC command.

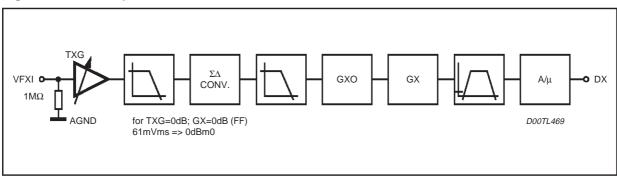

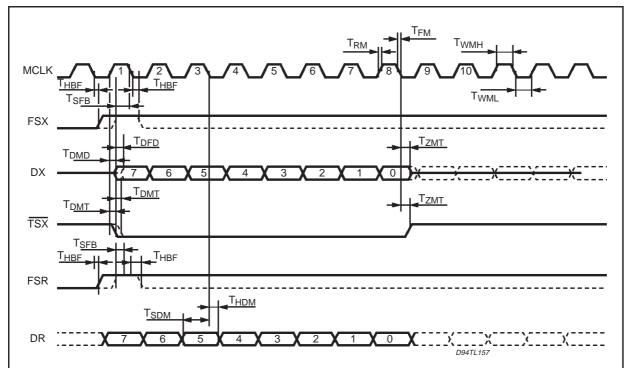

# Figure 2. Transmit path.

# TRANSMIT PATH

The transmit section input consist of the input amplifier, the A/D converter, the equalization filter X, the gain block GX, the encoder and the channel filters (LPX and HPX).

The input amplifier is provided of a programmable gain with a typical input impedance of  $1M\Omega$ . The amplifier gain can be programmed with two different values (0dB, +3.52dB) by means of the TXG Register.

VFXI input must be AC coupled to the signal; the voltage swing allowed is 1.4Vpp when the preamplifier gain is set to 0dB and 0.93Vpp when the gain is 3.52dB; higher levels must be reduced through proper dividers.

Following the input amplifier the signal is converted into digital domain and a X filter block is programmed to equalise together with the HPX and LPX filters the frequency response. The coefficients of the X filter are programmed via the XFC command.

A gain block (GX) allows to set the transmit level in a 12dB range, with steps <0.1dB. This block can be programmed via the GTX command.

# FUNCTIONAL DESCRIPTION (continued)

The needed TX gain can be set by proper programming of the GX block in combination with the TX amplifier.

Setting GTX=00h, the transmitted signal is muted and an idle PCM signal is generated on DX.

Concerning the CODING function, A/m law can be selected writing the CONF register (bit 5 AMU). In addition, via the CONF register (bit 6 LIN) the coding law can be set to linear mode (16 bits). In this case the signal sent on the DX will take two adjacent PCM channels, proper care has to be taken in the time slot selection programming (DXTS register).

The intrinsec non programmable gain GX0 set the TX path gain to 22dB. The absolute gain level (see electrical characteristics) refers to this intrinsec gain.

# **RECEIVE PATH**

The receive path of the STLC5048 consists of the decoder section, the gain block GR, the R filter, the channel filters (LPR, HPR) the D/A converter and the output amplifier.

Concerning the DECODING function, A/m law can be selected writing the CONF register (bit 5 AMU). In addition via the CONF register (bit 6 LIN) the coding law can be set to linear mode (16 bits).

In this case the signal received on the DR input will take two adjacent PCM channels, proper care has to be taken in the time slot selection programming (DRTS register).

The gain block GR is controlled by the GRX command allowing 12dB gain range in 0.1dB steps.

The R filter together the channel filters (LPR and HPR) performs the line equalization. The coefficients of the R filter are programmed via the RFC command.

The signal is converted in the analog domain and amplified by the RX amplifier that can be programmed with four different values (mute, 0dB, -6dB and -12dB) by means of RXG register.

# Figure 3. Receive path.

VFRO output, referred to AGND must be AC coupled to the load, referred to VSS, to prevent a DC current flow. In order to get the best noise performances it is recommended to keep GRX value as close as possible to the maximum (FFh) setting properly the additional attenuation by means of RXG.

The intrinsec non programmable gain GR0 set the RX path gain to -3dB. The absolute gain level (see electrical characteristics) refers to this intrinsec gain.

# PCM INTERFACE

The STLC5048 dedicates eight pins to the interface with the PCM highways.

MCLK represents the bit clock and is also used by the device as a source for the clock of the internal PLL.

Five possible frequencies can be used: 1.536/1.544MHz (24 channels PCM frame); 2048MHz (32 channels PCM frame); 4.096MHz (64 channels PCM frame); 8.192MHz (128 channels PCM frame). The operating fre-

quency is automatically detected by the device the first time both MCLK and FS are applied and becomes active after the second FS period. MCLK synchronises both the transmit data (DXA/B) and the receive data (DRA/B).

The Frame Sync. signal FS is the common time base for all the four channels.

Transmit and Receive programmable Time-Slots are framed by an internal sync. signal that can be coincident with FS or delayed of 1 or 7 MCLK cycles depending on the programming of PCMSH register.

Two PCM ports are available: every channel can be connected to a different PCM port by means of PCMBUS register.

DXA/B represents the transmit PCM interface. It remains in high impedance state except during the assigned time slots during which the PCM data byte is shifted out on the rising/falling edge of MCLK according to the TE bit of PCMCOM register. The four channels can be shifted out in any possible timeslot as defined by the DXTS registers. The assigned Time Slot (Transmit and Receive) takes place in the 8 MCLK cycles following the rising edge of FS.

The data can be shifted out on port A and/or B according to PCMCOM register.

If one CODEC is set in Power Down by software programming the corresponding time slot is set in High Impedance. When linear coding mode is selected by CONF register programming the output channel will need two consecutive time slots (see register description).

DRA/B represents the receive PCM interface. It remains inactive except during the assigned time slots during which the PCM data byte is shifted in on the falling edge of MCLK. The four channels are shifted in any possible time slot as defined by the DRTS registers.

If one Codec is set in Power Down by software programming the corresponding time slot is not loaded and the VFRO output is kept at steady AGND level.

# INSTRUCTION BYTE STRUCTURE

|     | First Byte (Address or command ID) |    |    |    |    |    |    |    |    | Follo | owing E | Bytes (E | Data) |    |    |

|-----|------------------------------------|----|----|----|----|----|----|----|----|-------|---------|----------|-------|----|----|

| 7   | 6                                  | 5  | 4  | 3  | 2  | 1  | 0  | 7  | 6  | 5     | 4       | 3        | 2     | 1  | 0  |

| R/W | 16                                 | 15 | 14 | 13 | 12 | 11 | 10 | D7 | D6 | D5    | D4      | D3       | D2    | D1 | D0 |

R/W=0: Write Operation

R/W=1: Read Operation

I6..10: Instruction Identifier: it can be a register address or a command identifier.

The number of data bytes depends on the instruction type. The first bit of a byte is the MSB, the first byte of an instruction is the LSByte.

When linear coding mode is selected by CONF register programming the input channel will need two consecutive time slots (see register description).

The data can be shifted in from port A or B according to the PCMCOM register.

TSXA/B represents the Transmit Time Slot (open drain output, 3.2mA). Normally it is floating in high impedance state except when a time slot is active on the DXA/B output. In this case TSXA/B output pulls low to enable the backplane line driver. Should be strapped to VSS when not used.

Finally by means of the LOOPB register it is possible to implement a digital or analog loopback on any of the selected channels.

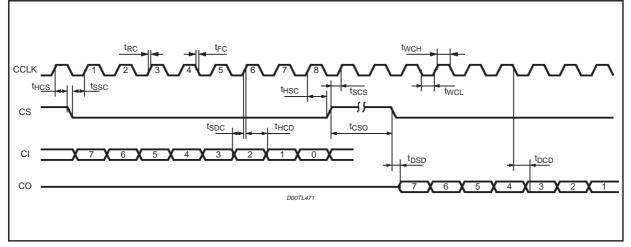

MCU CONTROL INTERFACE

The MCU serial control interface consists of 4 pins.

CCLK: Control Clock

- CI: Serial Data In

- CO: Serial Data Out

- CS: Chip Select Input

Control instructions require at least two bytes: however two single byte instructions are also provided.

In the multiple byte instructions the first one specifies the command or the register address and the access type (Read or Write).

The following bytes contain the data to be loaded into the internal RAM (on CI wire) or carry out the RAM content (on CO wire) depending on the R/W bit of the first byte. CO wire is normally in High Impedance and goes to low impedance only after the first byte in case of Read operation. This allows to use a common wire for both CI/CO. CS, normally High, is set Low during the transmission/reception of a byte, lasting 8 CCLK pulses. Between two consecutive access the CS must be set high.

The CCLK can be a continuos or a gated clock.

The result of any instruction (read/write operation), if negative, can generate an interrupt (maskable). The interrupt register (INT) contains the cause information of the generated interrupt and it is cleared every time that it is read.

Depending on the instruction specified in the first byte, the STLC5048 waits a defined number of data bytes. If the STLC5048 doesn't receive the data byte within a predefined period specified by means of T\_OUT command, an internal time out rejects the instruction. The time-out time is verified between two consecutive MCU interface access (between the falling edge of the CS and the following rising edge).

This feature is used to verify the synchronisation of the MCU interface: however it can be disabled if not desired. To check this synchronisation is provided a specific register (SYNCK) that returns always a predefined value: if the returned value is different the MCU interface is in out of sync state (the device is waiting a data byte while the MCU is writing an address or vice versa). In this case, it is possible to realign it by means of the execution of a specific single byte instruction (REACOM) from 1 to 53 times, depending on the instructions.

Every time an illegal operation (access to not allowed address, time-out violation or clock pulse different than 8 inside a CS active) is performed the MCU interface is put on an error state: to resume it from this state a single REACOM instruction can be used.

Anyway after a REACOM instruction a successful SYNC instruction guarantees the correct synchronisation.

One additional wire provided to the control interface is an open drain interrupt output (INT) that goes low when a change of status is detected on the I/O pins or other interrupt source are active (see INT register). INT is automatically reset after reading of the register corresponding the cause that has generated the interrupt (see INT register description).

A particular register (COMEN) allows to enable a command on different channel at the same time. Every time a command operation is performed at least one channel must be enabled in this register.

This feature is useful when all channels must be configured in the same condition. When a command is used to perform a read operation only one channel can be enabled at the same time.

To check the configuration of the device a checksum value is provided. This value is calculated on all coefficient parameters entered (coefficients of KD, AFE\_CFF, GRX, GTX, RFC, XFC, BFC, ZFC blocks; see CKSUM register description). Two commands are required to get this value: the first one (CKSTART) starts the internal checksum calculation, the second one (CKSUM) returns the calculated value. Between this two commands no other operation are allowed. The checksum value is available within 400us the CKSTART command.

Coefficient checksum is defined by this algorithm:

$$X^{16} + X^{12} + X^5 + 1$$

This algorithm guarantees a fault coverage of  $1 - 2^{-16}$ .

### PROGRAMMING THE DEVICE

After the power up, the filters and gain blocks can be programmed also with all the channels set in Power Down. In this case the PDR bit of the COMEN register must be set to 0.

With the proper setting of the COMEN register, the commands can be applied to more than one channel at the same time.

To read the coefficient values loaded in the RAM, only one channel per time must be enabled in the COMEN register.

# SLIC CONTROL INTERFACE

The device provides 12 I/O pins plus 4 CS signals. The interface can work in dynamic or static mode: it can be selected by means of STA bit of the CONF register.

- Dynamic Mode: the I/O pins are configured as input or output by means of DIR register. The CS signals are used to select the different SLIC interface. In this case the I/O pin can be multiplexed. The data loaded from SLIC #n via I/O pins configured as input can be read in the DATAn register. The data written in a DATAn register will be loaded on the I/O pins configured as output when the Csn signal will be active.

- Static Mode: The CS signal can be used as I/O pins. They can be configured as input or output I/O by means of DATA1 register. The data corresponding to the CS signal can be read or written by means of DATA2 register. All data related to the other I/O pins can be read or written by means of DATA0 register.

# DC SLIC PROGRAMMABILITY

Three additional pins are used to select the On-Hook/Off-Hook detection threshold and the line card limitation of the STLC3080 SLIC. This two values are programmed by ILIM and ITH registers.

The VBG input pin must be connected to the IREF pin of the STLC3080.

When the L3235N is used in kit with STLC5048 the ILIM, ITH and VBG pin must be not connected.

# **BUILT IN TEST**

By means of TONEG register it is possible to inject a tone of variable frequency (25Hz, 1 and 3KHz) and 0dBm0 amplitude into the receive path, replacing any signal coming from the PCM interface. This test can be performed on every channel.

Setting the proper bit of the PCMCOM register is also possible to read the PCM data coming from the transmit path via the MCU interface (PCMRD register).

These two features can be used to test the line interface operation.

| Addr | Name    | Description                        |

|------|---------|------------------------------------|

| 00h  | DIR-L   | I/O Direction (bit 7-0)            |

| 01h  | DIR-H   | I/O Direction (bit 11-8)           |

| 02h  | DATA0-L | I/O Data ch#0 (bit 7-0)            |

| 03h  | DATA0-H | I/O Data ch #0 (bit 11-8)          |

| 04h  | DATA1-L | I/O Data ch#1 (bit 7-0)            |

| 05h  | DATA1-H | I/O Data ch #1 (bit 11-8)          |

| 06h  | DATA2-L | I/O Data ch#2 (bit 7-0)            |

| 07h  | DATA2-H | I/O Data ch #2 (bit 11-8)          |

| 08h  | DATA3-L | I/O Data ch#3 (bit 7-0)            |

| 09h  | DATA3-H | I/O Data ch #3 (bit 11-8)          |

| 0Ah  | PCHK-A  | Persistency Check Time for input A |

| 0Bh  | PCHK-B  | Persistency Check Time for input B |

| 10h  | INT     | Interrupt register                 |

| 11h  | DMASK-L | Int. Mask I/O Port (03h)           |

| 12h  | DMASK-H | Int. Mask I/O Port (04h)           |

57

### **REGISTER ADDRESSES**

# **REGISTER ADDRESSES** (continued)

| Addr | Name    | Description              |

|------|---------|--------------------------|

| 13h  | IMASK   | Interrupt Mask reg.      |

| 14h  | ALARM   | Alarm register           |

| 20h  | CONF    | Configuration register   |

| 21h  | COMEN   | Command Enable reg.      |

| 23h  | SYNCCK  | Synchronous Check reg.   |

| 25h  | CTRLACK | DSP status register      |

| 26h  | CKSUM-L | Cheksum register L       |

| 27h  | CKSUM-H | Cheksum register H       |

| 2Ah  | LOOPB   | Loopback register        |

| 2Bh  | TXG     | Transmit preamp. Gain    |

| 2Ch  | RXG     | Receive preamp. Gain     |

| 2Dh  | ILIM    | SLIC line current lim.   |

| 2Eh  | ITH     | SLIC Off-Hook threshold  |

| 50h  | PCMSH   | PCM Shift register       |

| 51h  | PCMCOM  | PCMCOM register          |

| 52h  | DXTS0   | Transmit Timeslot ch #0  |

| 53h  | DXTS1   | Transmit Timeslot ch #1  |

| 54h  | DXTS2   | Transmit Timeslot ch #2  |

| 55h  | DXTS3   | Transmit Timeslot ch #3  |

| 56h  | DRTS0   | Receive Timeslot ch #0   |

| 57h  | DRTS1   | Receive Timeslot ch #1   |

| 58h  | DRTS2   | Receive Timeslot ch #2   |

| 59h  | DRTS3   | Receive Timeslot ch #3   |

| 5Ah  | PCMWD-L | PCMW Data register       |

| 5Bh  | PCMWD-H | PCMW Data register       |

| 5Ch  | PCMRD-L | PCMR Data register       |

| 5Dh  | PCMRD-H | PCMR Data register       |

| 5Eh  | PCMCTRL | PCM Control register     |

| 60h  | TONEG   | Tone Generation reg.     |

| 61h  | COEFST  | Coefficient State reg.   |

| 70h  | SWRID   | Software rev. ID code    |

| 71h  | HWRID   | Silicon revision ID code |

# **REGISTER DESCRIPTION**

I/O Direction Register (DIR)

Addr=00h; Reset Value=00h Addr=01h; Reset Value=X0h

| BIt7 | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| R/W  | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| 107  | IO <sub>6</sub> | IO <sub>5</sub> | IO <sub>4</sub> | IO <sub>3</sub> | IO <sub>2</sub> | IO <sub>1</sub> | IO <sub>0</sub> |

| Blt7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2               | Bit1            | Bit0            |

|------|------|------|------|------------------|--------------------|-----------------|-----------------|

| R/W  | 0    | 0    | 0    | 0                | 0                  | 0               | 1               |

|      |      |      |      | IO <sub>11</sub> | IO <sub>10</sub> 0 | IO <sub>9</sub> | IO <sub>8</sub> |

IO11..0=0 I/O pin 11..0 is an input, data on the I/O input is written in DATAn register bit 11..0.

IO11..0=1 I/O pin 11..0 is an output, data contained in DATAn register bit 11..0 is transferred to the I/O output.

# I/O Data Register channel #0 (DATA0)

Addr=02h; Reset Value=00h Addr=03h; Reset Value=X0h If bit 4 of CONF register (STA)=0 Dynamic I/O mode:

| BIt7 | Bit6            | Bit5 | Bit4 | Bit3            | Bit2            | Bit1            | Bit0            |

|------|-----------------|------|------|-----------------|-----------------|-----------------|-----------------|

| R/W  | 0               | 0    | 0    | 0               | 0               | 1               | 0               |

| D07  | D0 <sub>6</sub> | D05  | D04  | D0 <sub>3</sub> | D0 <sub>2</sub> | D0 <sub>1</sub> | D0 <sub>0</sub> |

| Blt7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 0    | 0    | 0    | 0    | 1    | 1    |

|      |      |      |      | D011 | D010 | D09  | D08  |

When CS0 is active D011..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding D011..0 will be written by the values applied to those pins while CS0 is low.

If bit 4 of CONF register (STA)=1 Static I/O mode:

| Bit7            | Bit6            | Bit5   | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|-----------------|-----------------|--------|-----------------|-----------------|-----------------|-----------------|-----------------|

| R/W             | 0               | 0      | 0               | 0               | 0               | 1               | 0               |

| DS <sub>7</sub> | DS <sub>6</sub> | $DS_5$ | DS <sub>4</sub> | DS <sub>3</sub> | DS <sub>2</sub> | DS <sub>1</sub> | DS <sub>0</sub> |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1            | Bit0            |

|------|------|------|------|------------------|------------------|-----------------|-----------------|

| R/W  | 0    | 0    | 0    | 0                | 0                | 1               | 1               |

|      |      |      |      | DS <sub>11</sub> | DS <sub>10</sub> | DS <sub>9</sub> | DS <sub>8</sub> |

DS11..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding DS11..0 will be written by the values applied to those pins.

# I/O Data Register channel #1 (DATA1)

Addr=04h; Reset Value=00h Addr=05h; Reset Value=X0h

If bit 4 of CONF register (STA)=0 Dynamic I/O mode:

| Bit7 | Bit6            | Bit5            | Bit4 | Bit3            | Bit2            | Bit1            | Bit0            |

|------|-----------------|-----------------|------|-----------------|-----------------|-----------------|-----------------|

| R/W  | 0               | 0               | 0    | 0               | 1               | 0               | 0               |

| D17  | D1 <sub>6</sub> | D1 <sub>5</sub> | D14  | D1 <sub>3</sub> | D1 <sub>2</sub> | D1 <sub>1</sub> | D1 <sub>0</sub> |

| Blt7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1 | Bit0            |

|------|------|------|------|------------------|------------------|------|-----------------|

| R/W  | 0    | 0    | 0    | 0                | 1                | 0    | 1               |

|      |      |      |      | D1 <sub>11</sub> | D1 <sub>10</sub> | D19  | D1 <sub>8</sub> |

When  $\overline{\text{CS1}}$  is active D111..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding D111..0 will be written by the values applied to those pins while  $\overline{\text{CS1}}$  is low.

If bit 4 of CONF register (STA)=1 Static I/O mode:

In static mode CS pins are used as additional I/O pins. The CIO0..3 bits are used to define the direction of these pins.

| Blt7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1             | Bit0             |

|------|------|------|------|------------------|------------------|------------------|------------------|

| R/W  | 0    | 0    | 0    | 0                | 1                | 0                | 0                |

|      |      |      |      | CIO <sub>3</sub> | CIO <sub>2</sub> | CIO <sub>1</sub> | CIO <sub>0</sub> |

CIO0..3=0 The  $\overline{\text{CS0..3}}$  is a static input, DATA is written in DATA2 register bits 0..3.

CIO0..3=1 The CS0..3 is a static output, DATA is taken from DATA2 register bits 0..3.

# I/O Data Register channel #2 (DATA2)

Addr=06h; Reset Value=00h Addr=07h; Reset Value=X0h

If bit 4 of CONF register (STA)=0 Dynamic I/O mode:

| Bit7            | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| R/W             | 0               | 0               | 0               | 0               | 1               | 1               | 0               |

| D2 <sub>7</sub> | D2 <sub>6</sub> | D2 <sub>5</sub> | D2 <sub>4</sub> | D2 <sub>3</sub> | D2 <sub>2</sub> | D2 <sub>1</sub> | D2 <sub>0</sub> |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1            | Bit0            |

|------|------|------|------|------------------|------------------|-----------------|-----------------|

| R/W  | 0    | 0    | 0    | 0                | 1                | 1               | 1               |

|      |      |      |      | D2 <sub>11</sub> | D2 <sub>10</sub> | D2 <sub>9</sub> | D2 <sub>8</sub> |

When  $\overline{\text{CS2}}$  is active D211..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding D211..0 will be written by the values applied to those pins while  $\overline{\text{CS2}}$  is low.

57

# If bit 4 of CONF register (STA)=1 Static I/O mode:

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2            | Bit1 | Bit0            |

|------|------|------|------|------|-----------------|------|-----------------|

| R/W  | 0    | 0    | 0    | 0    | 1               | 1    | 0               |

|      |      |      |      | CD3  | CD <sub>2</sub> | CD1  | CD <sub>0</sub> |

CD0..3 are transferred to the corresponding CS pin if configured as static output (see register DATA1). For the CS pins configured as static inputs the corresponding CD0..3 will be written by the values applied to those pins.

### I/O Data Register channel #3 (DATA3)

Addr=08h; Reset Value=00h

Addr=09h; Reset Value=X0h

Used only if bit 4 of CONF register (STA)=0; Dynamic I/O mode:

| Bit7            | Bit6            | Bit5            | Bit4 | Bit3            | Bit2            | Bit1            | Bit0            |

|-----------------|-----------------|-----------------|------|-----------------|-----------------|-----------------|-----------------|

| R/W             | 0               | 0               | 0    | 1               | 0               | 0               | 0               |

| D3 <sub>7</sub> | D3 <sub>6</sub> | D3 <sub>5</sub> | D34  | D3 <sub>3</sub> | D3 <sub>2</sub> | D3 <sub>1</sub> | D3 <sub>0</sub> |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1            | Bit0            |

|------|------|------|------|------------------|------------------|-----------------|-----------------|

| R/W  | 0    | 0    | 0    | 1                | 0                | 0               | 1               |

|      |      |      |      | D3 <sub>11</sub> | D3 <sub>10</sub> | D3 <sub>9</sub> | D3 <sub>8</sub> |

When  $\overline{CS3}$  is active D311..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding D311..0 will be written by the values applied to those pins while  $\overline{CS3}$  is low.

If bit4 of CONF register (STA) = 1 Static I/O mode:

D3<sub>3.0</sub>=1: The corresponding CSn cannot generate interrupt.

D33..0=0: The corresponding I/O (programmed as input) can generate interrupt if a change of status is detected.

# Persistency Check Register (PCHK-A/B)

Addr=0Ah; Reset Value=00h Addr=0Bh; Reset Value=00h

Two input signal per channel, labelled A and B, are submitted to persistency check.

In dynamic mode (STA=0), A and B inputs of the four channels, are sampled on the multiplexed lines IO0 (pin 13) and IO1 (pin 14).

In static mode (STA=1) persistency check is performed on four pairs of lines, assigned to each channel according to the table:

| CHAN # | Input A                   | Input B                   |  |  |

|--------|---------------------------|---------------------------|--|--|

| 0      | IO <sub>0</sub> (pin 19)  | IO <sub>1</sub> (pin 14)  |  |  |

| 1      | IO <sub>4</sub> (pin 17)  | IO <sub>5</sub> (pin 18)  |  |  |

| 2      | IO <sub>6</sub> (pin 48)  | IO <sub>7</sub> (pin 47)  |  |  |

| 3      | IO <sub>10</sub> (pin 44) | IO <sub>11</sub> (pin 43) |  |  |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 0    | 0    | 1    | 0    | 1    | 0    |

| TA7  | TA6  | TA5  | TA4  | TA3  | TA2  | TA1  | TA0  |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 0    | 0    | 1    | 0    | 1    | 1    |

| TB7  | TB6  | TB5  | TB4  | TB3  | TB2  | TB1  | TB0  |

TA7..0 and TB7..0, contents of PCHKA and PCHKB registers, define the minimum duration of input A and B to generate interrupt; spurious transitions shorter than the programmed value are ignored.

The time width can be calculated according to the formula:

Time - Width A = (TA7..0)\*64µs

Time - Width B = (TB7..0)\*64µs

If PCHKA/B is programmed to 00h the persistency check is not performed and any detected transition will generate interrupt.

All the inputs, with or without persistency check, are sampled with a repetition rate of 32µs.

### Interrupt Register (INT)

Addr=10h; Reset Value=00h

Read Only

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    |

|      | ITV  | IPCM | ICKF | ID3  | ID2  | ID1  | ID0  |

In dynamic I/O configuration the ID3..0 bits latch the interrupt request from the related channel (SLIC). Any single bit IDn is cleared after reading related I/O register or by setting MCn bit High (i.e. when channel n is disabled to generate interrupt).

In static I/O configuration ID0 and ID2 bits latch the interrupt request from I/O11..0 and CS3..0 respectively:

ID0: is set High when the interrupt is requested from any the I/O11..0 lines.

ID2: is set High when the interrupt is requested from any the CS3..0 (configured as I/O).

ID0 and ID2 are cleared after reading related I/O register.

ID1 and ID3 are don't care.

ITV = 1: If the interrupt has been generated by time-out violation on the MCU serial interface.

IPCM = 1: When transmit PCM data reading/writing test is enabled an interrupt is generated every time valid data are available (RRD bit set to 1) or must be written (WRD bit set to 1). The interrupt is cleared after reading/ writing the data in the PCMRD/PCMWD register via the MCU interface.

ICKF = 1: If the interrupt has been generated by a clock failure on PCM port (MCLK).

The INT register is cleared after reading operation only if signals (alarm cause) are inactive.

# Interrupt Mask Register for I/O port (DMASK)

| Addr=11h; Reset Value=FFh |

|---------------------------|

| Addr=12h; Reset Value=XFh |

| Bit7            | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| R/W             | 0               | 0               | 1               | 0               | 0               | 0               | 1               |

| MD <sub>7</sub> | MD <sub>6</sub> | MD <sub>5</sub> | MD <sub>4</sub> | MD <sub>3</sub> | MD <sub>2</sub> | MD <sub>1</sub> | MD <sub>0</sub> |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3             | Bit2             | Bit1            | Bit0            |

|------|------|------|------|------------------|------------------|-----------------|-----------------|

| R/W  | 0    | 0    | 1    | 0                | 0                | 1               | 0               |

|      |      |      |      | MD <sub>11</sub> | MD <sub>10</sub> | MD <sub>9</sub> | MD <sub>8</sub> |

$MD_{11..0}=1$ : The corresponding I/O doesn't generate interrupt.

MD<sub>11..0</sub>=0: The corresponding I/O (programmed as input) generate interrupt if a change of status is detected.

Input lines with persistency check generate interrupt if the changed status remains stable longer than the time programmed in the persistency check register PCHKA/B. Line without persistency check generate an immediate interrupt request.

Mask register has no effect on those pins configured as outputs, those pins will not generate interrupt.

# Interrupt Mask Register for Interrupt (IMASK)

Addr=13h; Reset Value=FFh

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 0    | 1    | 0    | 0    | 1    | 1    |

| х    | MTV  | MPCM | MCF  | MC3  | MC2  | MC1  | MC0  |

For dynamic I/O configuration, MCn bits are the disable/enable interrupt related to the channel n.

MC3..0=1: Any I/O line of the related channel #n is disabled to generate interrupt independently of DMASK setting.

MC3..0=0: Any I/O line of the related channel #n is enabled to generate interrupt depending on DMASK setting.

For static I/O configuration, MCn bits are the interrupt mask bits related to CSn that are configured as I/O lines. MC0=1: The corresponding I/O cannot generate interrupt independently of DMASK setting.

MC0=0: The corresponding I/O can generate interrupt if a change of status is detected depending of DMASK setting.

MC2=1: The corresponding I/O cannot generate interrupt independently of DATA3\_L setting (bit 3..0).

MC2=0: The corresponding I/O can generate interrupt if a change of status is detected depending of DATA3\_L setting (bit 3..0).

MC3 and MC1 bit are not used in static mode.

Input lines with persistency check generate interrupt if the changed status remains stable longer than the time programmed in the persistency check register PCHKA/B. Line without persistency check generate an immediate interrupt request.

Mask register has no effect on those pins configured as outputs, those pins will not generate interrupt

MCF=1: The corresponding alarm bit (CKF) doesn't generate interrupt.

MCF=0: The corresponding alarm bit (CKF) can generate interrupt.

MTV=1: The corresponding alarm bit (TV) doesn't generate interrupt.

MTV=0: The corresponding alarm bit (TV) can generate interrupt.

MPCM =1 : The IPCM interrupt is masked (generation disabled).

MPCM =0 : The IPCM interrupt is enabled (generation enabled).

# Alarm Register (ALARM)

Addr=14h; Reset Value=01h

### Read Only

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | POR  |

POR=0: No Power On Reset is detected during operation.

POR=1: A Power On Reset is detected during operation.

The ALARM register is cleared after reading operation only if signals (alarm cause) are inactive.

# **Configuration Register (CONF)**

Addr=20h; Reset Value=BFh

| Blt7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 1    | 0    | 0    | 0    | 0    | 0    |

| RES  | LIN  | AMU  | STA  | PD3  | PD2  | PD1  | PD0  |

**RES=0** Normal Operation

RES=1 Device Reset: I/On and Csn are all inputs, DX is H.I. (equivalent to Hw reset).

LIN=0 A or  $\mu$  law PCM encoding

LIN=1 Linear encoding (16 bits), two's complement.

AMU=0  $\mu$  law selection (all bits inverted)

AMU=1 A law selection (even bits inverted)

STA=0 CS0 to CS3 scan the four SLICs connected to the I/O control port, each CS has a 31.25µs repetition time.

STA=1I/O are static, CS0 to CS3 are configured as generic static I/O

PD3..0=0 Codec 3..0 is active

PD3..0=1 Codec 3..0 is in Power Down. When one codec is in Power Down the corresponding VFRO output is set to AGND and the corresponding transmit time slot on DX is set in H.I.

# **Command Enable register (COMEN)**

Addr=21h; Reset Value=80h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3           | Bit2           | Bit1           | Bit0           |

|------|------|------|------|----------------|----------------|----------------|----------------|

| R/W  | 0    | 1    | 0    | 0              | 0              | 0              | 1              |

| PDR  | 0    | 0    | 0    | E <sub>3</sub> | E <sub>2</sub> | E <sub>1</sub> | E <sub>0</sub> |

The En bits enable a command on one or more channels. All enabled channels will receive the entered data. At least one channel must be enabled before every command.

E0..3=0: commands disabled on the corresponding channel 0..3

E0..3=1: commands enabled on the corresponding channel 0..3

PDR = 0: RAM is enabled also in Power Down.

PDR = 1: RAM is disabled in Power Down. In this way it's possible to reduce the power consumption in Power Down.

# Synchronous Check register (SYNCK)

Addr=23h; Reset Value=E4h

### Read Only

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    |

| 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0    |

This register contains a fixed code (E4h) that can be read to check the synchronisation of the MCU interface.

# **DSP Status Register (CTRLACK)**

Addr=25h; Reset Value=01h

Read Only

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0  |

|------|------|------|------|------|------|------|-------|

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1     |

| 0    | 0    | 0    | 0    | 0    | 0    | INIT | CKEND |

CKEND bit is 0 while the checksum calculation is performed: in the other time is always set to 1.

INIT bit becomes active (INIT = 1) after the DSP initialization. Normally it requires 70 us after the reset to be set to 1.

# Checksum register (CKSUM)

Addr=26h; Reset Value=00h Addr=27h; Reset Value=00h Read Only

| Bit7 | Bit6            | Bit5            | Bit4 | Bit3 | Bit2            | Bit1 | Bit0            |

|------|-----------------|-----------------|------|------|-----------------|------|-----------------|

| 1    | 0               | 1               | 0    | 0    | 1               | 1    | 0               |

| CK7  | CK <sub>6</sub> | CK <sub>5</sub> | CK4  | CK3  | CK <sub>2</sub> | CK1  | CK <sub>0</sub> |

| Bit7             | Bit6             | Bit5             | Bit4             | Bit3             | Bit2             | Bit1            | Bit0            |

|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|

| 1                | 0                | 1                | 0                | 0                | 1                | 1               | 1               |

| CK <sub>15</sub> | CK <sub>14</sub> | CK <sub>13</sub> | CK <sub>12</sub> | CK <sub>11</sub> | CK <sub>10</sub> | CK <sub>9</sub> | CK <sub>8</sub> |

The cheksum value is calculated every time the CKSTART instruction is performed and the result is available after a proper delay (max 400  $\mu$ s).

This register contains the cheksum value calculated on the contents of the following coefficient (each of 16 bits): ZERO

KDF0\_0 KDF0\_1 KDF0\_2 KDF1\_0 KDF1\_1 KDF1\_2 KDF2\_0 KDF2\_1 KDF2\_2 KDF3\_0 KDF3\_1 KDF3\_2 AFE\_CFF GRX0 GTX0 RFC0\_0 ...... RFC0\_16 XFC0\_0 ...... XFC0\_16 BFC0\_0 ...... BFC0\_25 ZFC0\_0 ...... ZFC0\_4 GRX1 GTX1 RFC1\_0 ...... RFC1\_16 XFC1\_0 ...... XFC1\_16 BFC1\_0 ...... BFC1\_25 ZFC1\_0 ...... ZFC1\_4 GRX2 GTX2 RFC2\_0 ...... RFC2\_16 XFC2\_0 ...... XFC2\_16 BFC2\_0 ...... BFC2\_25 ZFC2\_0 ...... ZFC2\_4 GRX3 GTX3 RFC3\_0 ...... RFC3\_16 XFC3\_0 ...... XFC3\_16 BFC3\_0 ...... BFC3\_25 ZFC3\_0 ...... ZFC3\_4

# Loopback Register (LOOPB)

Addr=2Ah; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 1    | 0    | 1    | 0    |

| DL3  | DL2  | DL1  | DL0  | AL3  | AL2  | AL11 | AL0  |

DL3..0=0: Normal Operation

DL3..0=1: Codec #3..0 is set in Digital Loopback mode, this means that the receive PCM signal applied to the programmed Receive Time Slot is transferred to the programmed Transmit Time Slot.

AL3..0=0: Normal Operation

AL3..0=1: Codec #3..0 is set in Analog Loopback mode, this means that the VFRO signal is transferred to the VFXI input internally into the Codec.

When loopbacks are enabled the signal appears also at the corresponding VFRO output. It is possible to have no signal on the VFRO output programming the GRX command to 00h in case of digital loopback.

### Transmit Preamplifier Gain Register (TXG)

Addr=2Bh; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 1    | 0    | 1    | 0    | 1    | 1    |

|      |      |      |      | TG3  | TG2  | TG1  | TG0  |

TG3..0=0: Transmit preamplifier gain ch. 3..0 = 0dB

TG3..0=1: Transmit preamplifier gain ch. 3..0 = 3.52dB

Overall transmit gain depends on combination of TXG and GTXn registers.

### **Receive Amplifier Gain Register (RXG)**

Addr=2Ch; Reset Value=00h

| Bit7            | Bit6            | Bit5            | Bit4            | Bit3            | Bit2            | Bit1            | Bit0            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| R/W             | 0               | 1               | 0               | 1               | 1               | 0               | 0               |

| R3 <sub>1</sub> | R3 <sub>0</sub> | R2 <sub>1</sub> | R2 <sub>0</sub> | R1 <sub>1</sub> | R1 <sub>0</sub> | R0 <sub>1</sub> | R0 <sub>0</sub> |

$Rn_0=0, Rn_1=0$ : Receive amp. gain ch #n = mute

$Rn_0=1, Rn_1=0$ : Receive amp. gain ch #n = -12dB

$Rn_0=0, Rn_1=1$ : Receive amp. gain ch #n = -6dB

$Rn_0=1, Rn_1=1$ : Receive amp. gain ch #n = 0dB

Overall receive gain depends on the receive amplifier gain (R3..0) setting in RXG reg. and digital gain (GRXn reg. setting).

# SLIC Line Current Limit reg (ILIM)

Addr=2Dh; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 1    | 0    | 1    | 1    | 0    | 1    |

| 0    | 0    | 0    | D4   | D3   | D2   | D1   | D0   |

D4..0 = 0: Programmed value is 53

D4..0 = 1: Programmed value is 2

The step is 1.6 mA

This register allows to program a line current limitation from 2 to 53mA with a step equal to 1.6mA. These values can be obtained using an external 15KOhm resistor in kit with STLC3080.

# SLIC Off-Hook threshold register (ITH)

Addr=2Eh; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 0    | 1    | 0    | 1    | 1    | 1    | 0    |

| 0    | 0    | 0    | En   | D3   | D2   | D1   | D0   |

D3..0 = 0: Programmed value is 16 mA

D3..0 = 1: Programmed value is 1 mA

The step is equal to 1 mA.

En = 1 The DC SLIC programmability block is enabled (ITH and ILIM)

En = 0 The DC SLIC programmability block is disabled (ITH and ILIM)

This register allows to program a threshold value from 1 to 16 mA with a step equal to 1mA. These values can be obtained using an external 12.5KOhm resistor in kit with STLC3080.

# PCM Shift Register (PCMSH)

Addr=50h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 0    | 0    | 0    |

|      | XS2  | XS1  | XS0  |      | RS2  | RS1  | RS0  |

XS2..0:Effective start of the TX frame is the programmed values of clock pulses (0 to 7) after the FS rising edge. RS2..0:Effective start of the RX frame is the programmed values of clock pulses (0 to 7) after the FS rising edge.

# PCM Command register (PCMCOM)

Addr=51h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit4 Bit3 |      | Bit1 | Bit0 |

|------|------|------|------|-----------|------|------|------|

| R/W  | 1    | 0    | 1    | 0         | 0    | 0    | 1    |

| RR   | WR   | PC1  | PC0  | TE        | RPAB | TPB  | TPA  |

| TPA/B = These two bits are used to enable the DX outputs of the port A or/and B. According to the combination |

|---------------------------------------------------------------------------------------------------------------|

| of these two bits the enabled port will be as follows:                                                        |

| ТРВ | ТРА | Description         |

|-----|-----|---------------------|

| 0   | 0   | Both Ports disabled |

| 0   | 1   | Port A enabled      |

| 1   | 0   | Port B enabled      |

| 1   | 1   | Both ports enabled  |

RPAB = 0: Port A enabled (DRA input selected)

RPAB = 1: Port B enabled (DRB input selected)

TE = 0: Transmit PCM data change on rising edge of MCLK

TE = 1: Transmit PCM data change on falling edge of MCLK

PC1-PC0 = Selection of the channel for the PCM access data via MCU.

| PC0 | PC1 | Description         |

|-----|-----|---------------------|

| 0   | 0   | Channel #0 selected |

| 1   | 0   | Channel #1 selected |

| 0   | 1   | Channel #2 selected |

| 1   | 1   | Channel #3 selected |

WR = 1: Setting this bit, receive PCM data writing via MCU (after A/ $\mu$  decoding) is enabled on selected channel and IPCM interrupt is generated every time FS signal becomes active, together to the set of the WRD bit in the PCMCTRL register.

A data byte must be written every 125µs, if data is not replaced the old value is inserted again but the PMW bit is set to 1 in the PCMCTRL register.

RR = 1: Setting this bit, transmit PCM data reading (after A/ $\mu$  encoding) via MCU is enabled on selected channel and IPCM interrupt is generated every time that data are available, together to the set of the RRD bit in the PC-MCTRL register.

A data byte must be read every  $125\mu$ S, if data is not read the new value is written in the PCM access register but the POW bit is set to 1 in the PCMCTRL register.

# Transmit Time Slot ch #0 (DXTS0)

Addr=52h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 0    | 1    | 0    |

| EN0  | T06  | T05  | T04  | T03  | T02  | T01  | T00  |

EN0=0:Selected transmit time slot on DX output is in H.I.

EN0=1:Selected transmit time slot on DX output is active carrying out the PCM encoded signal of VFXI0. T06..0:Define time slot number (0 to 127) on which PCM encoded signal of VFXI0 is carried out.

If linear mode is selected (LIN=1 of CONF register) the 16 bits will be carried out as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following time slot. Example: if T06..T00=00:

| слатр | <i>i</i> c. II T |    | -00. |    |    |   |   |   |   |   |    |   |   |   |   |

|-------|------------------|----|------|----|----|---|---|---|---|---|----|---|---|---|---|

| TSO   |                  |    |      |    |    |   |   |   |   | т | 51 |   |   |   |   |

| 15    | 14               | 13 | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

# Transmit Time Slot ch #1 (DXTS1)

Addr=53h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 0    | 1    | 1    |

| EN1  | T16  | T15  | T14  | T13  | T12  | T11  | T10  |

EN1=0: Selected transmit time slot on DX output is in H.I.

EN1=1: Selected transmit time slot on DX output is active carrying out the PCM encoded signal of VFXI1.

T16..0: Define time slot number (0 to 127) on which PCM encoded signal of VFXI1 is carried out.

If linear mode is selected (LIN=1 of CONF register) the 16 bits will be carried out as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following time slot.

Example: if T16..T10=00:

|    | TS0 |    |    |    |    |   | TS1 |   |   |   |   |   |   |   |   |

|----|-----|----|----|----|----|---|-----|---|---|---|---|---|---|---|---|

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8   | 6 | 5 | 4 | 3 | 7 | 2 | 1 | 0 |

# Transmit Time Slot ch #2 (DXTS2)

Addr=54h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 1    | 0    | 0    |

| EN2  | T26  | T25  | T24  | T23  | T22  | T21  | T20  |

EN2=0: Selected transmit time slot on DX output is in H.I.

EN2=1: Selected transmit time slot on DX output is active carrying out the PCM encoded signal of VFXI2.

T26..0: Define time slot number (0 to 127) on which PCM encoded signal of VFXI2 is carried out.

If linear mode is selected (LIN=1 of CONF register) the 16 bits will be carried out as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following time slot.

Example: if T26..T20=00:

|    | TS0 |    |    |    |    |   |   | TS1 |   |   |   |   |   |   |   |

|----|-----|----|----|----|----|---|---|-----|---|---|---|---|---|---|---|

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 6   | 5 | 4 | 3 | 7 | 2 | 1 | 0 |

# Transmit Time Slot ch #3 (DXTS3)

Addr=55h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 1    | 0    | 1    |

| EN3  | T36  | T35  | T34  | T33  | T32  | T31  | T30  |

EN3=0: Selected transmit time slot on DX output is in H.I.

EN3=1: Selected transmit time slot on DX output is active carrying out the PCM encoded signal of VFXI3.

T36..0: Define time slot number (0 to 127) on which PCM encoded signal of VFXI3 is carried out.

If linear mode is selected (LIN=1 of CONF register) the 16 bits will be carried out as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following timeslot.

Example: if T36..T30=00:

|    | TS0 |    |    |    |    |   |   | TS1 |   |   |   |   |   |   |   |

|----|-----|----|----|----|----|---|---|-----|---|---|---|---|---|---|---|

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 6   | 5 | 4 | 3 | 7 | 2 | 1 | 0 |

# Receive Time Slot ch #0 (DRTS0)

Addr=56h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 1    | 1    | 0    |

| EN0  | R06  | R05  | R04  | R03  | R02  | R01  | R00  |

EN0=0: Disable reception of selected time slot.

EN0=1: Selected receive time slot on DR input is PCM decoded and transferred to VFRO0 output.

R06..0: Define receive time slot number (0 to 127) on carrying the PCM signal to be decoded and transferred to VFRO0 output. If linear mode is selected (LIN=1 of CONF register) the 16 bits will be used as linear code as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following timeslot.

Example: if R06..R00=00:

|    | TS0 |    |    |    |    |   | TS1 |   |   |   |   |   |   |   |   |

|----|-----|----|----|----|----|---|-----|---|---|---|---|---|---|---|---|

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8   | 6 | 5 | 4 | 3 | 7 | 2 | 1 | 0 |

### Receive Time Slot ch #1 (DRTS1)

Addr=57h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| R/W  | 1    | 0    | 1    | 0    | 1    | 1    | 1    |

| EN1  | R16  | R15  | R14  | R13  | R12  | R11  | R10  |

EN1=0: Disable reception of selected time slot.

EN1=1: Selected receive time slot on DR input is PCM decoded and transferred to VFRO1 output.

R16..0: Define receive time slot number (0 to 127) on carrying the PCM signal to be decoded and transferred to VFRO1 output. If linear mode is selected (LIN=1 of CONF register) the 16 bits will be used as linear code as follows: the 8 most significant bits in the programmed time slot, the 8 least significant bits in the following time slot.

Example: if R16..R10=00:

|    | TS0 |    |    |    |    |   | TS1 |   |   |   |   |   |   |   |   |

|----|-----|----|----|----|----|---|-----|---|---|---|---|---|---|---|---|

| 15 | 14  | 13 | 12 | 11 | 10 | 9 | 8   | 6 | 5 | 4 | 3 | 7 | 2 | 1 | 0 |

### Receive Time Slot ch #2 (DRTS2)

Addr=58h; Reset Value=00h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|