# **GRENOBLE PLANT**

# **Standard Linear ICs, DSG**

# SHORT QUALIFICATION REPORT

LINE : 187X

PRODUCT NAME : TS1871/ TS1872/ TS1874

# LINE DESCRIPTION : LOW POWER RAIL TO RAIL OPERATIONAL AMPLIFIER

#### WAFER CODE : C1871AAH/ C1872AAH/ C1874AAH

PACKAGE : SOT23-5 / SO8 & 14 / TSSOP8 & 14 / DIP8 & 14

Qualification plan REFERENCE :7139748

### CONTENTS

| DEVICE DESCRIPTION                       | page 3 |

|------------------------------------------|--------|

|                                          |        |

| ELECTRICAL CHARACTERISATION PRESENTATION | page 6 |

| QUALIFICATION RESULTS page 7 | <b>QUALIFICATION RESULTS</b> |  | page 7 |

|------------------------------|------------------------------|--|--------|

|------------------------------|------------------------------|--|--------|

PRODUCT DESIGN QUALIFICATION FLOW ...... page 8

## **DEVICE DESCRIPTION**

| Wafer Fab. Process                                            | Asked                                                                                                 | Answer                                                                               |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Device name                                                   | (Part number)                                                                                         | TS1871                                                                               |  |

| Function                                                      | (type)                                                                                                | Single op-amp r/rail low power 1.8V                                                  |  |

| Die name                                                      | (Part number)                                                                                         | P1871AAH                                                                             |  |

| Die size                                                      | (mm * mm)                                                                                             | 1400*880                                                                             |  |

| Shrink                                                        | (Level)                                                                                               | N/A                                                                                  |  |

| Transistor count                                              | (Number)                                                                                              | 181                                                                                  |  |

| Process                                                       | (Name)                                                                                                | HF2CMOS 2µm                                                                          |  |

| Process qualification                                         | (Date)                                                                                                | Q4/96                                                                                |  |

| Wafer fab.                                                    | (Location)                                                                                            | Carrollton                                                                           |  |

| Wafer characteristics                                         | (Diameter)                                                                                            | 6"<br>radius value                                                                   |  |

| Mask set reference                                            | (Tickness)<br>(Dopant type)<br>(Epi type)                                                             | 375μm<br>Ρ<br>Ν<br>1871Α                                                             |  |

| Masks                                                         | (Name)<br>(Number)                                                                                    | 18/1A                                                                                |  |

| Minimum effective dimension(Nature/Width) 2µm (Metal - Metal) |                                                                                                       |                                                                                      |  |

|                                                               |                                                                                                       | 0.17                                                                                 |  |

| Layers(M1,M2,poly1,poly2,etc)                                 | (Nature/Width)<br>M1:<br>M2:<br>Poly1:<br>Dala2:                                                      | Nature Thickness Width PitchAlSiCu0.6μm2μm4.5μmAlSiCu1.05μm2μm4.5μmPoly0.4μm2μm4.5μm |  |

| Frontside metallisation layers                                | <b>Poly2:</b> (Nature / Tickness)                                                                     | Poly 0.4µm 2µm 4.5µm<br>AlSiCu 06µm/ AlSiCu 1.05µm                                   |  |

| Backside metallisation layers                                 | (Nature / Tickness) RAW SILICON / 50µm                                                                |                                                                                      |  |

| Passivation layers<br>Process flow                            | (Nature / Thickness) <b>PVAPOX 0.5µm+NITRIDE 0.6µm</b> (Method) <b>CVD</b> (Reference) <b>HFMS580</b> |                                                                                      |  |

| Fault coverage level                                          | (%)                                                                                                   | 100%                                                                                 |  |

## **DEVICE DESCRIPTION**

| Wafer Fab. Process                                            | Asked                                            | Answer                                                                                               |

|---------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Device name                                                   | (Part number)                                    | TS1872                                                                                               |

| Function                                                      | (type)                                           | Dual op-amp r/rail low power 1.8V                                                                    |

| Die name                                                      | (Part number)                                    | Р1872ААН                                                                                             |

| Die size                                                      | (mm * mm)                                        | 1560*1460                                                                                            |

| Shrink                                                        | (Level)                                          | N/A                                                                                                  |

| Transistor count                                              | (Number)                                         | 362                                                                                                  |

| Process                                                       | (Name)                                           | HF2CMOS 2µm                                                                                          |

| Process qualification                                         | (Date)                                           | Q4/96                                                                                                |

| Wafer fab.                                                    | (Location)                                       | Carrollton                                                                                           |

| Wafer characteristics                                         | (Diameter)                                       | 6"<br>radius value                                                                                   |

|                                                               | (Tickness)<br>(Dopant type)<br>(Epi type)        | 375µm<br>Р<br>N                                                                                      |

| Mask set reference                                            | (Name)                                           | 1872A                                                                                                |

| Masks                                                         | (Number)                                         | 18                                                                                                   |

| Minimum effective dimension(Nature/Width) 2µm (Metal - Metal) |                                                  | (Metal - Metal)                                                                                      |

| Composite defect density                                      | (Defects per cm2                                 | 0.17                                                                                                 |

| Layers(M1,M2,poly1,poly2,etc)                                 | (Nature/Width)<br>M1:<br>M2:<br>Poly1:<br>Poly2: | Nature ThicknessWidth PitchAlSiCu0.6μm2μm4.5μmAlSiCu1.05μm2μm4.5μmPoly0.4μm2μm4.5μmPoly0.4μm2μm4.5μm |

| Frontside metallisation layers                                | (Nature / Tickness)                              | AlSiCu 06µm/ AlSiCu 1.05µm                                                                           |

| Backside metallisation layers                                 | (Nature / Tickness)                              | RAW SILICON / 50µm                                                                                   |

| Passivation layers                                            | (Nature / Thickness)<br>(Method)                 | PVAPOX 0.5µm+NITRIDE 0.6µm<br>CVD                                                                    |

| Process flow                                                  | (Reference)                                      | HFMS580                                                                                              |

| Fault coverage level                                          | (%)                                              | 100%                                                                                                 |

## **DEVICE DESCRIPTION**

| Wafer Fab. Process                                            | Asked                                               | Answer                                                                                                  |

|---------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Device name                                                   | (Part number)                                       | TS1874                                                                                                  |

| Function                                                      | (type)                                              | Quad op-amp r/rail low power 1.8V                                                                       |

| Die name                                                      | (Part number)                                       | Р1874ААН                                                                                                |

| Die size                                                      | (mm * mm)                                           | 2320*1950                                                                                               |

| Shrink                                                        | (Level)                                             | N/A                                                                                                     |

| Transistor count                                              | (Number)                                            | 724                                                                                                     |

| Process                                                       | (Name)                                              | HF2CMOS 2µm                                                                                             |

| Process qualification                                         | (Date)                                              | Q4/96                                                                                                   |

| Wafer fab.                                                    | (Location)                                          | Carrollton                                                                                              |

| Wafer characteristics                                         | (Diameter)                                          | 6"<br>radius value                                                                                      |

| Mask set reference                                            | (Tickness)<br>(Dopant type)<br>(Epi type)<br>(Name) | 375µm<br>Р<br>N<br>1874A                                                                                |

| Masks                                                         | (Number)                                            | 18                                                                                                      |

| Minimum effective dimension(Nature/Width) 2µm (Metal - Metal) |                                                     | (Metal - Metal)                                                                                         |

| Composite defect density                                      | (Defects per cm2                                    | 0.17                                                                                                    |

| Layers(M1,M2,poly1,poly2,etc)                                 | (Nature/Width)<br>M1:<br>M2:<br>Poly1:<br>Poly2:    | Nature Thickness Width PitchAlSiCu 0.6μm2μm4.5μmAlSiCu 1.05μm2μm4.5μmPoly0.4μm2μm4.5μmPoly0.4μm2μm4.5μm |

| Frontside metallisation layers                                | (Nature / Tickness)                                 | AlSiCu 06µm/ AlSiCu 1.05µm                                                                              |

| Backside metallisation layers                                 | (Nature / Tickness)                                 | RAW SILICON / 50µm                                                                                      |

| Passivation layers                                            | (Nature / Thickness)<br>(Method)                    | PVAPOX 0.5µm+NITRIDE 0.6µm<br>CVD                                                                       |

| Process flow                                                  | (Reference)                                         | HFMS580                                                                                                 |

| Fault coverage level                                          | (%)                                                 | 100%                                                                                                    |

#### ELECTRICAL CHARACTERISATION PRESENTATION

Since the process technology and electrical specifications are identical forthese devices, this report covers the entire family. The characterisation was performed on the**TS1871**, **TS1872** & **TS1874** devices.

#### <u>NOTES</u> :

#### ASSURANCE OF THE DEVICE PARAMETERS AT CORNER TEMPERATURES

#### <u>1st level</u>:

During the Design phase the critical parameters are simulated at temperature min and max.

#### 2nd level :

During the Evaluation phase 50 units are tested at temperature min andmax and the results are compared to the simulations and to the specification.

The CPK must be > 2 for 98% of the parameters and > 1.33 for the others.

#### <u>**3rd level :**</u>

The limits of specification at temperature are calculated to include the temperature drift evaluated at the 2nd level compared to the specification at 25°C.

#### 4th level :

The test is made at 25°C with the limits of the specification at 25°C, so with a guard band compared to the limits at temperature.

The test results at 25°C and temperature with the CP/CPK calculation and the specification are available in the qualification report. This report is available for all new products and for redesigned products.

#### **QUALIFICATION RESULTS**

#### a) Electrical results

\* Yield analysis on 3 lots : conform to ST standard results

\* Electrical parameters distribution on 50 pièces at  $T^{\circ}AMB = 25^{\circ}C$  results conform to datasheet specification

#### b) ESD measurement was performed

- \* ESD resistance is > 2 KV to according to MILSTD883C

- \* ESD resistance is > 200V according to Machin Model

- \* ESD resistance is > 1.5 KV according to Charge Device Model

#### c) Latch-up measurement was performed according to ST specification (n°0018695)

\* No latch-up was observed

#### d) Reliability tests were performed according to the qualification plan

| Reliability test                                   | Nb of rejects | Package        |

|----------------------------------------------------|---------------|----------------|

| High temperature bias test (HTB)                   | 0/78 *2       | SO8 1871 &1872 |

| $T^{\circ} AMB = 125^{\circ}C - Duration = 1000h$  | 0/78          | SO14 1874      |

|                                                    | 0/77          | TSSOP8 0922    |

|                                                    | 0/77          | TSSOP14 0924   |

|                                                    | 0/77          | SOT23-5 0951   |

|                                                    | 0/77          | DIP8 0462      |

| Temperature & humidity bias (THB)                  | 0/78*2        | SO8 1871 &1872 |

| $T^{\circ}AMB = 85^{\circ}C$ humidity = 85%        | 0/78          | SO14 1874      |

| Duration = 1000h                                   | 0/77          | SOT23-5 0951   |

|                                                    | 0/77          | TSSOP8 0462    |

|                                                    | 0/77          | TSSOP14 0464   |

|                                                    | 0/77          | DIP8 0462      |

| Temperature cycling (CT)                           | 0/50          | SO8 1871       |

| $T^{\circ}AMB = -65/150^{\circ}C$ Nb cycles = 1000 | 0/50          | SOT23-5 0951   |

|                                                    | 0/50          | TSSOP8 0462    |

|                                                    | 0/50          | TSSOP14 0464   |

|                                                    | 0/50          | DIP8 0462      |

| Presure pot test (PPT)                             | 0/50          | SO8 1871       |

| $T^{\circ}AMB = 121^{\circ}C$                      | 0/50          | SOT23-5 0951   |

| Pressure = $2atm$ - Duration = $240h$              | 0/50          | TSSOP8 0462    |

|                                                    | 0/50          | TSSOP14 0464   |

|                                                    | 0/50          | DIP8 0462      |

#### e) Conclusion

\* Electrical and reliability results meet or exceed the requirements set in the ST qualification program. The devices are qualified for all packages (**TS1871**, **TS1872** and **TS1874**).

NB : Detailed results are available upon request

"WARNING" : Tests results and information contained in this document are for information only. This document does not alter ST Microelectronic's standard warranty or product specification.

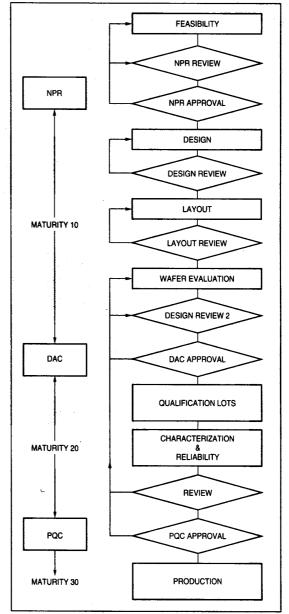

#### **PRODUCT DESIGN QUALIFICATION FLOW**

"Quality is what the customer says it is." Tom Peters

Manufacturing and reliability must be considered at the design level in order to manufacture reliable products meeting customers' expectations.

New product development plans adopt the Quality Function Deployment (QFD) methodology as a basic tool to understand customers' requirements. This formally translates the customers' need into technical requirements as product specifications, process operations and manufacturing process controls, that represent the key points for the product finalization.

In SGS-THOMSON, a corporate procedure defines the product maturity, specifying three maturity levels with rules from one level to the next. They are: design, engineering and production. In addition there are various sub levels. This procedure governs the entire life cycle of a product from new product proposal to its obsolescence. It also determines when and how, engineering samples can be released at sub-maturity levels in a controlled manner by defining "for application study only" or "not yet fully qualified" on the customer documentation.

Each new product begins from the preparation of a target specification and a document called a New Product Request (**NPR**), which contains business and technical details. The purpose of this first control is to evaluate the potential of the product and determine if there is sufficient justification to allocate design resources.

Once the NPR is approved the designers can start work. Designers work to clearly defined design rules which incorporate robust design principles. When the design is complete and the first working samples are available they are evaluated to make sure that the design is acceptable for the next phase, Engineering.

The results of these tests are included in the next key document, the Design Approval Certificate (**DAC**). The approval of the DAC commits the company to a major investment so it is essential to ensure that the product is ready to proceed.

While a product is in design and characterization (maturity 10 & 20), samples may be given to customers with the documentation indicating "engineering samples for application study only and at the customers' risk" under the responsibility of the Division Manager.

New product is prepared for qualification through product characterization and reliability testing. A Product Qualification Certificate (**PQC**) which permits the new product to proceed to manufacturing must be approved by Group Management.

Product design qualification flow