# 4 Mbit (512Kb x8) Low Voltage Low Power SRAM with Output Enable

## PRELIMINARY DATA

- ULTRA LOW DATA RETENTION CURRENT

- 600nA (typical)

- 10µA (max)

- OPERATION VOLTAGE: 2.7 to 3.6V

- 512 Kbit x8 SRAM with OUTPUT ENABLE

- EQUAL CYCLE and ACCESS TIMES: 70ns

- LOW V<sub>CC</sub> DATA RETENTION: 1V

- TRI-STATE COMMON I/O

- CMOS for OPTIMUM SPEED/POWER

- AUTOMATIC POWER-DOWN WHEN DESELECTED

- INTENDED FOR USE WITH ST ZEROPOWER<sup>®</sup> AND TIMEKEEPER<sup>®</sup> CONTROLLERS

### DESCRIPTION

The M68Z512W is a 4 Mbit (4,194,304 bit) CMOS SRAM, organized as 524,288 words by 8 bits. The device features fully static operation requiring no external clocks or timing strobes, with equal address access and cycle times. It requires a single  $3V \pm 10\%$  supply, and all inputs and outputs are TTL compatible.

This device has an automatic power-down feature, reducing the power consumption by over 99% when deselected.

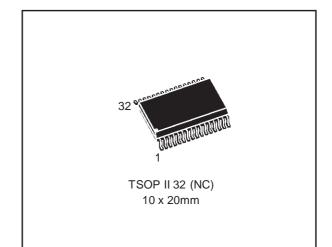

The M68Z512W is available in a 32 lead TSOP II (10 x 20mm) package.

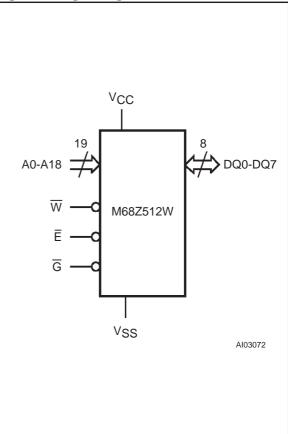

| A0-A18          | Address Inputs    |

|-----------------|-------------------|

| DQ0-DQ7         | Data Input/Output |

| Ē               | Chip Enable       |

| G               | Output Enable     |

| W               | Write Enable      |

| Vcc             | Supply Voltage    |

| V <sub>SS</sub> | Ground            |

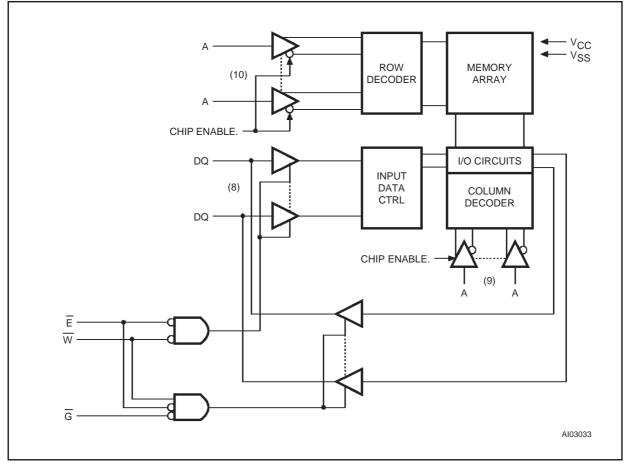

### Figure 1. Logic Diagram

#### September 2000

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

| Symbol                         | Parameter                             | Value                         | Unit |

|--------------------------------|---------------------------------------|-------------------------------|------|

| TA                             | Ambient Operating Temperature 0 to 70 |                               | °C   |

| T <sub>STG</sub>               | Storage Temperature                   | -65 to 150                    | °C   |

| V <sub>IO</sub> <sup>(2)</sup> | Input or Output Voltage               | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| V <sub>CC</sub>                | Supply Voltage                        | -0.3 to 7.0                   | V    |

| I <sub>O</sub> <sup>(3)</sup>  | Output Current                        | 20                            | mA   |

| PD                             | Power Dissipation                     | 1                             | W    |

### Table 2. Absolute Maximum Ratings <sup>(1)</sup>

Note: 1. Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

2. Up to a maximum operating V<sub>CC</sub> of 3.6V only.

3. One output at a time, not to exceed 1 second duration.

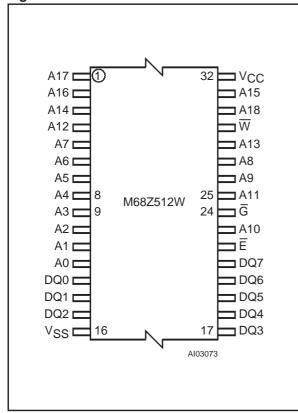

Figure 2. TSOP Connections

### **READ MODE**

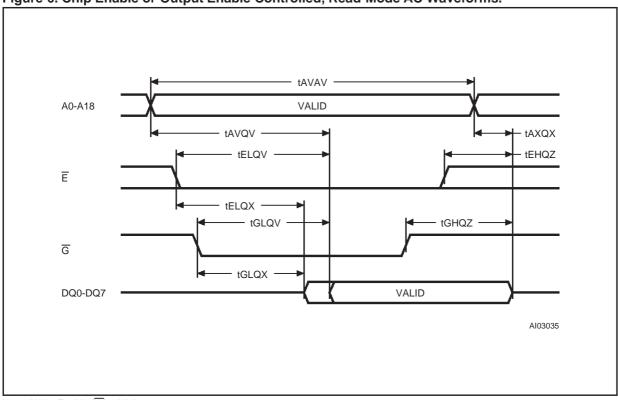

The M68Z512W is in the Read mode whenever Write Enable (W) is High with Output Enable (G) Low, and Chip Enable (E) is asserted. This provides access to data from eight of the 4,194,304 locations in the static memory array, specified by the 19 address inputs. Valid data will be available at the eight output pins within  $t_{AVQV}$  after the last stable address, providing G is Low and E is Low. If Chip Enable or Output Enable access times are not met, data access will be measured from the limiting parameter ( $t_{ELQV}$  or  $t_{GLQV}$ ) rather than the address. Data out may be indeterminate at  $t_{ELQX}$  and  $t_{GLQX}$ , but data lines will always be valid at  $t_{AVQV}$ .

#### WRITE MODE

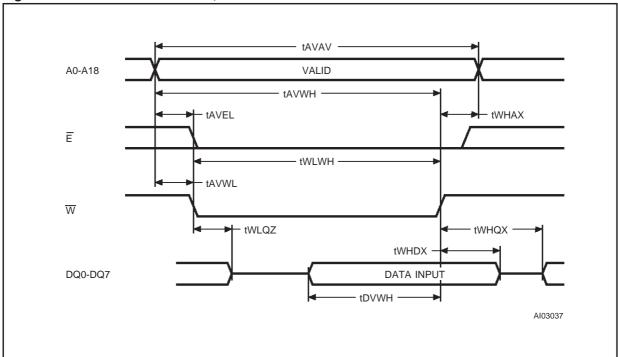

The M68Z512W is in the Write mode whenever the  $\overline{W}$  and  $\overline{E}$  pins are Low. Either the Chip Enable input ( $\overline{E}$ ) or the Write Enable input ( $\overline{W}$ ) must be deasserted during Address transitions for subsequent write cycles. Write begins with the concurrence of Chip Enable being active with  $\overline{W}$  low. Therefore, address setup time is referenced to Write Enable and Chip Enable as t<sub>AVWL</sub> and t<sub>AVEH</sub> respectively, and is determined by the latter occurring edge.

The Write cycle can be terminated by the earlier rising edge of  $\overline{E},$  or  $\overline{W}.$

if the Output is enabled ( $\overline{E}$  = Low and  $\overline{G}$  = Low), then  $\overline{W}$  will return the outputs to high impedance within t<sub>WLQZ</sub> of its falling edge. Care must be taken to avoid bus contention in this type of operation. Data input must be valid for t<sub>DVWH</sub> before the rising edge of Write Enable, or for t<sub>DVEH</sub> before the rising edge of  $\overline{E}$ , whichever occurs first, and remain valid for t<sub>WHDX</sub> or t<sub>EHDX</sub>.

### **Table 3. Operating Modes**

| Operation | Ē               | W               | G               | DQ0-DQ7     | Power   |

|-----------|-----------------|-----------------|-----------------|-------------|---------|

| Read      | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Hi-Z        | Active  |

| Read      | VIL             | VIH             | VIL             | Data Output | Active  |

| Write     | V <sub>IL</sub> | V <sub>IL</sub> | Х               | Data Input  | Active  |

| Deselect  | V <sub>IH</sub> | Х               | Х               | Hi-Z        | Standby |

Note: 1.  $X = V_{IH}$  or  $V_{IL}$ .

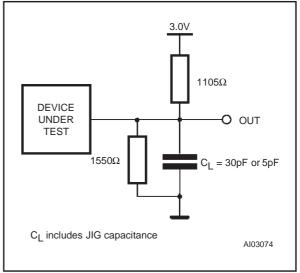

#### **Table 4. AC Measurement Conditions**

| Input Rise and Fall Times             | ≤ 5ns   |

|---------------------------------------|---------|

| Input Pulse Voltages                  | 0 to 3V |

| Input and Output Timing Ref. Voltages | 1.5V    |

Note: Output Hi-Z is defined as the point where data is no longer driven.

#### **OPERATIONAL MODE**

The M68Z512W has a Chip Enable power down feature which invokes an automatic standby mode whenever Chip Enable is de-asserted ( $\overline{E}$  = High). An Output Enable ( $\overline{G}$ ) signal provides a high speed tri-state control, allowing fast read/write cycles to be achieved with the common I/O data bus. Operational modes are determined by device control inputs  $\overline{W}$  and  $\overline{E}$  as summarized in the Operating Modes table.

## Figure 3. AC Testing Load Circuit

| Table 5. Capacitance <sup>(1)</sup> $(T_A = 25^{\circ}C, f = 1 \text{ MH})$ | Table 5. | Capacitance | (1) (T <sub>A</sub> | = 25°C, | , f = 1 | MHz) |

|-----------------------------------------------------------------------------|----------|-------------|---------------------|---------|---------|------|

|-----------------------------------------------------------------------------|----------|-------------|---------------------|---------|---------|------|

| Symbol                          | Parameter                                 | Test Condition                             | Min | Max | Unit |

|---------------------------------|-------------------------------------------|--------------------------------------------|-----|-----|------|

| C <sub>IN</sub>                 | Input Capacitance on all pins (except DQ) | $T_A = 25^{\circ}C, f = 1MHz, V_{CC} = 3V$ |     | 6   | pF   |

| C <sub>OUT</sub> <sup>(2)</sup> | Output Capacitance                        | $T_A = 25^{\circ}C, f = 1MHz, V_{CC} = 3V$ |     | 8   | pF   |

Note: 1. Sampled only, not 100% tested.

2. Outputs deselected.

# Figure 4. Block Diagram

# **Table 6. DC Characteristics**

| Symbol                          | Parameter                     | Test Condition                                            | Min  | Тур | Max                   | Unit |

|---------------------------------|-------------------------------|-----------------------------------------------------------|------|-----|-----------------------|------|

| Ι <sub>LI</sub>                 | Input Leakage Current         | $0V \le V_{IN} \le V_{CC}$                                |      |     | ±1                    | μΑ   |

| I <sub>LO</sub>                 | Output Leakage Current        | $0V \le V_{OUT} \le V_{CC}$                               |      |     | ±1                    | μΑ   |

| ICC1 (1)                        | Supply Current                | V <sub>CC</sub> = 3.6V                                    |      | 7   | 15                    | mA   |

| I <sub>CC2</sub> <sup>(2)</sup> | Supply Current (Standby) TTL  | $V_{CC} = 3.6V, \overline{E} = V_{IH}$                    |      |     | 100                   | μΑ   |

| I <sub>CC3</sub> <sup>(3)</sup> | Supply Current (Standby) CMOS | $V_{CC} = 3.6V, \overline{E} \ge V_{CC} - 0.3V,$<br>f = 0 |      | 2   | 20                    | μΑ   |

| V <sub>IL</sub>                 | Input Low Voltage             |                                                           | -0.3 |     | 0.8                   | V    |

| VIH                             | Input High Voltage            |                                                           | 2.2  |     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OL</sub>                 | Output Low Voltage            | I <sub>OL</sub> = 2.1mA                                   |      |     | 0.4                   | V    |

| V <sub>OH</sub>                 | Output High Voltage           | I <sub>OH</sub> = -1mA                                    | 2.4  |     |                       | V    |

Note: 1. Average AC current, Outputs open, cycling at  $t_{AVAV}$  minimum. 2. All other Inputs at  $V_{IL} \le 0.8V$  or  $V_{IH} \ge 2.2V$ . 3. All other Inputs at  $V_{IL} \le 0.3V$  or  $V_{IH} \ge V_{CC} - 0.3V$ .

# Table 7. Read Mode AC Characteristics

$(T_A = 0 \text{ to } 70^{\circ}\text{C}; V_{CC} = 2.7 \text{ to } 3.6\text{V})$

|                                    |                                         | M68Z | 512W |      |

|------------------------------------|-----------------------------------------|------|------|------|

| Symbol                             | Parameter                               |      | 70   | Unit |

|                                    |                                         | Min  | Мах  |      |

| t <sub>AVAV</sub>                  | Read Cycle Time                         | 70   |      | ns   |

| t <sub>AVQV</sub> <sup>(1)</sup>   | Address Valid to Output Valid           |      | 70   | ns   |

| t <sub>ELQV</sub> <sup>(1)</sup>   | Chip Enable Low to Output Valid         |      | 70   | ns   |

| t <sub>GLQV</sub> <sup>(1)</sup>   | Output Enable Low to Output Valid       |      | 35   | ns   |

| t <sub>ELQX</sub> <sup>(3)</sup>   | Chip Enable Low to Output Transition    | 10   |      | ns   |

| t <sub>GLQX</sub> <sup>(3)</sup>   | Output Enable Low to Output Transition  | 5    |      | ns   |

| t <sub>EHQZ</sub> <sup>(2,3)</sup> | Chip Enable High to Output Hi-Z         |      | 25   | ns   |

| t <sub>GHQZ</sub> <sup>(2,3)</sup> | Output Enable High to Output Hi-Z       |      | 25   | ns   |

| t <sub>AXQX</sub> <sup>(1)</sup>   | Address Transition to Output Transition | 10   |      | ns   |

| t <sub>PU</sub>                    | Chip Enable Low to Power Up             | 0    |      | ns   |

| t <sub>PD</sub>                    | Chip Enable High to Power Down          |      | 70   | ns   |

Note: 1. CL = 100pF.

2. CL = 5pF.

3. At any given temperature and voltage condition, t<sub>EHQZ</sub> is less than t<sub>ELQX</sub> and t<sub>GHQZ</sub> is less than t<sub>GLQX</sub> for any given device.

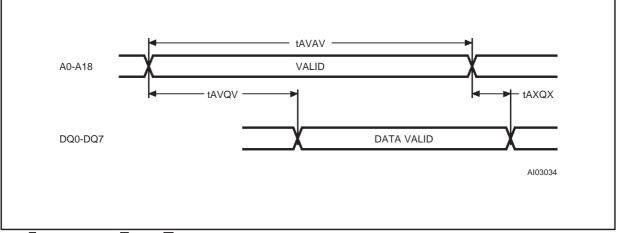

# Figure 5. Address Controlled, Read Mode AC Waveforms

Note:  $\overline{E}$  = Low, E2 = High,  $\overline{G}$  = Low,  $\overline{W}$  = High.

57

Figure 6. Chip Enable or Output Enable Controlled, Read Mode AC Waveforms.

Note: Write Enable  $(\overline{W})$  = High.

# Table 8. Write Mode AC Characteristics (T\_A = 0 to 70°C; V\_{CC} = 2.7 to 3.6V)

|                                  |                                         | M68Z | 512W |      |

|----------------------------------|-----------------------------------------|------|------|------|

| Symbol                           | Parameter                               | -7   | 0    | Unit |

|                                  |                                         | Min  | Max  |      |

| t <sub>AVAV</sub>                | Write Cycle Time                        | 70   |      | ns   |

| t <sub>AVWL</sub>                | Address Valid to Write Enable Low       | 0    |      | ns   |

| tavwh                            | Address Valid to Write Enable High      | 60   |      | ns   |

| t <sub>AVEH</sub>                | Address Valid to Chip Enable High       | 60   |      | ns   |

| twLwH                            | Write Enable Pulse Width                | 50   |      | ns   |

| t <sub>WHAX</sub>                | Write Enable High to Address Transition | 0    |      | ns   |

| t <sub>WHDX</sub>                | Write Enable High to Input Transition   | 0    |      | ns   |

| t <sub>WHQX</sub> <sup>(2)</sup> | Write Enable High to Output Transition  | 10   |      | ns   |

| t <sub>WLQZ</sub> (1,2)          | Write Enable Low to Output Hi-Z         |      | 25   | ns   |

| tAVEL                            | Address Valid to Chip Enable Low        | 0    |      | ns   |

| t <sub>ELEH</sub>                | Chip Enable Low to Chip Enable High     | 60   |      | ns   |

| tEHAX                            | Chip Enable High to Address Transition  | 0    |      | ns   |

| t <sub>DVWH</sub>                | Input Valid to Write Enable High        | 30   |      | ns   |

| t <sub>DVEH</sub>                | Input Valid to Chip Enable High         | 30   |      | ns   |

Note: 1.  $C_L = 5pF$ . 2. At any given temperature and voltage condition,  $t_{WLQZ}$  is less than  $t_{WHQX}$  for any given device.

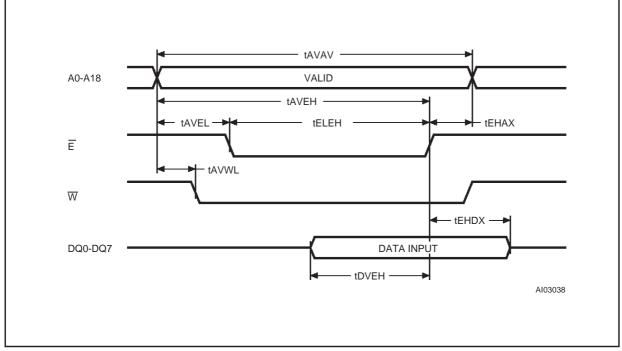

# Figure 8. Write Enable Controlled, Write AC Waveforms

Note: Output Enable  $(\overline{G})$  = Low.

# Figure 9. Chip Enable Controlled, Write AC Waveforms <sup>(1,2)</sup>

57

Note: 1. Output Enable ( $\overline{G}$ ) = High. 2. If  $\overline{E}$  goes High with  $\overline{W}$  high, the output remains in a high-impedance state.

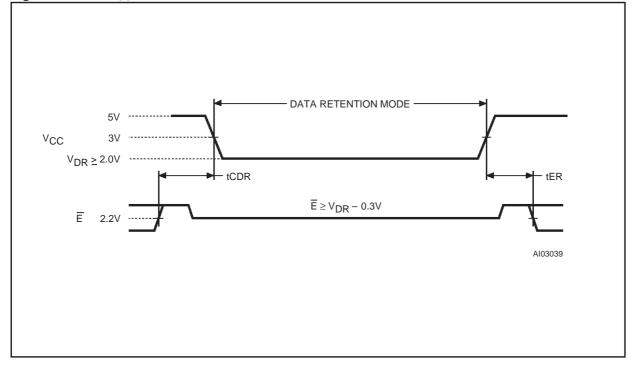

# Table 9. Low V<sub>CC</sub> Data Retention Characteristics (T<sub>A</sub> = 0 to 70°C)

| Symbol                           | Parameter                       | Test Condition                                                               | Min               | Тур | Max | Unit |

|----------------------------------|---------------------------------|------------------------------------------------------------------------------|-------------------|-----|-----|------|

| I <sub>CCDR</sub> <sup>(1)</sup> | Supply Current (Data Retention) | $V_{CC} = 3V, \overline{E} \ge V_{CC} - 0.3V$                                |                   | 0.4 | 10  | μΑ   |

| V <sub>DR</sub>                  | Supply Voltage (Data Retention) | $\overline{E} \geq V_{CC} - 0.3 V \text{ or } E2 \leq 0.3 V \text{, } f$ = 0 | 2                 |     |     | V    |

| t <sub>CDR</sub>                 | Chip Disable to Power Down      | $\overline{E} \geq V_{CC} - 0.3 V \text{ or } E2 \leq 0.3 V \text{, } f = 0$ | 0                 |     |     | ns   |

| t <sub>ER</sub> (2)              | Operation Recovery Time         |                                                                              | t <sub>AVAV</sub> |     |     | ns   |

Note: 1. Typical condition: T<sub>A</sub> = 25°C. 2. See Figure 10 for measurement points. Guaranteed but not tested. t<sub>AVAV</sub> is Read cycle time.

# Figure 10. Low V<sub>CC</sub> Data Retention AC Waveforms

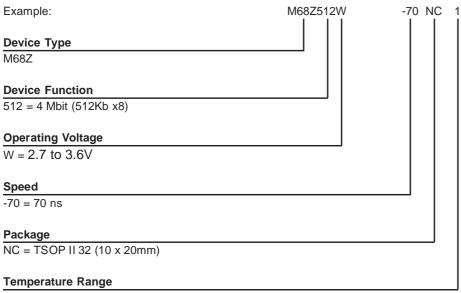

# Table 10. Ordering Information Scheme

1 = 0 to 70 °C

For a list of available options (Speed, Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.

# Table 11. Revision History

| Date      | Revision Details                                                                                |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------|--|--|--|

| July 1999 | First Issue                                                                                     |  |  |  |

| 06/28/00  | TSOP32 II Package Dimension Changed (Table 12)<br>From Target Specification To Preliminary Data |  |  |  |

| 07/26/00  | Ordering Information Scheme changed (Table 10)                                                  |  |  |  |

| 09/21/00  | I <sub>CCDR</sub> Supply Current changed (Table 9)                                              |  |  |  |

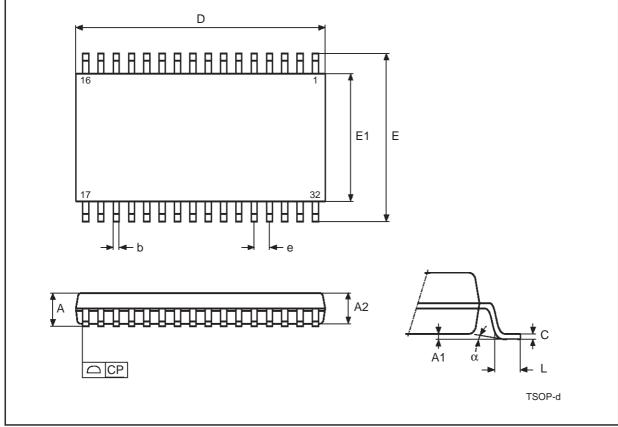

| Symbol | mm   |       |       | inch  |       |       |

|--------|------|-------|-------|-------|-------|-------|

|        | Тур  | Min   | Мах   | Тур   | Min   | Max   |

| A      |      |       | 1.20  |       |       | 0.047 |

| A1     |      | 0.05  | 0.15  |       | 0.002 | 0.006 |

| A2     |      | 0.95  | 1.05  |       | 0.037 | 0.041 |

| b      |      | 0.30  | 0.52  |       | 0.012 | 0.020 |

| С      |      | 0.12  | 0.21  |       | 0.005 | 0.008 |

| СР     |      |       | 0.10  |       |       | 0.004 |

| D      |      | 20.82 | 21.08 |       | 0.820 | 0.830 |

| е      | 1.27 | -     | -     | 0.050 | -     | -     |

| E      |      | 11.56 | 11.96 |       | 0.455 | 0.471 |

| E1     |      | 10.03 | 10.29 |       | 0.395 | 0.405 |

| L      |      | 0.40  | 0.60  |       | 0.016 | 0.024 |

| α      |      | 0°    | 5°    |       | 0°    | 5°    |

| Ν      | 32   |       |       | 32    |       |       |

Table 12. TSOP II 32 - 32 lead Plastic Thin Small Outline II, 10 x 20 mm, Package Mechanical Data

Figure 11. TSOP II 32 - 32 lead Plastic Thin Small Outline II, 10 x 20 mm, Package Outline

Drawing is not to scale.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is registered trademark of STMicroelectronics (8) 2000 STMicroelectronics - All Rights Reserved

All other names are the property of their respective owners.

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com