# PLASMA DATA POWER SWITCH

#### PRELIMINARY DATA

#### **FEATURES**

- High Voltage Low Power Pulse Generator

- 100V Absolute Maximum Supply

- High Load Drive Capability (25nF)

- 5V Compatible Input Logic

- Very Low Stand-by Current

- Power Recovery High Current (±7A)

- Totem Pole High Output Current (±5A)

- Built-in Timing Control & Thermal Protection

- BCD Technology

- Packaging: Multiwatt 15, Power SO20

#### DESCRIPTION

STV7801 is a monolithic integrated circuit implemented in STMicroelectronics BCD proprietary technology designed as a switched power supply generator for data drivers in a Plasma Display Panel (P.D.P.) application.

The high load drive capability of the STV7801 reduces the number of devices necessary to drive a complete PDP (4 to 6 devices for a 42" VGA 16/9 PDP monitor).

The STV7801 high current drive capability provides a high power recovery efficiency coefficient superior to 85% on constant capacitive load.

To limit the number of external components, the device integrates level shifters driven with 5V CMOS compatible levels.

To increase the reliability of the system, the device integrates several protections such as output over-voltage, over-temperature, power-ON protection.

#### Revision 3.6

This is preliminary information on a new product indevident eleptromatic destails greval back to Details aveitably is the state of the

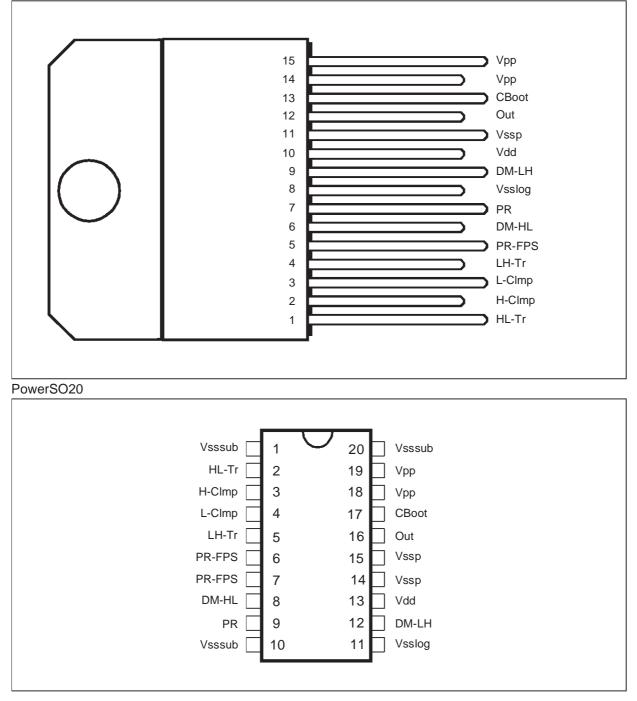

### **1 - PIN CONNECTION**

#### Multiwatt 15

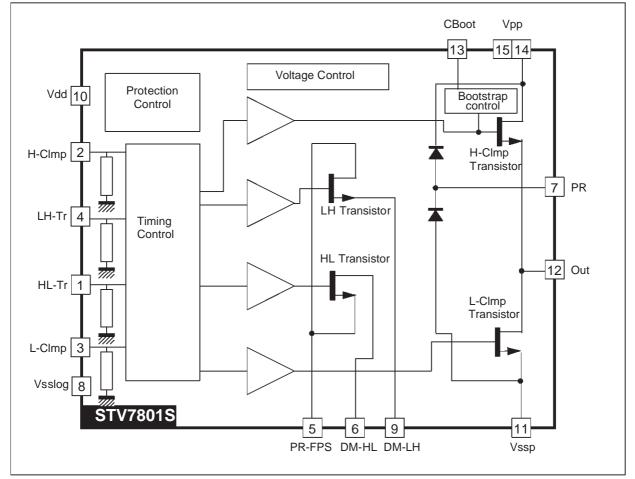

## 2 - BLOC DIAGRAM

**MULTIWATT 15**

# **3 - PIN DESCRIPTION**

#### Multiwatt 15

| Pin Number | Pin Name | Function | Description                                             |

|------------|----------|----------|---------------------------------------------------------|

| 1          | HL-Tr    | Input    | Power Recovery High Level/Low Level Transition          |

| 2          | H-Clmp   | Input    | Main Switch High-Side Clamp Input                       |

| 3          | L-CImp   | Input    | Main Switch Low-Side Clamp Input                        |

| 4          | LH-Tr    | Input    | Power Recovery Low Level/High Level Transition          |

| 5          | PR-FPS   | Input    | Power Recovery Floating Supply                          |

| 6          | DM-HL    | Input    | Current Recirculation- Input Pin - High/Low Transition  |

| 7          | PR       | Output   | Power Recirculation Output Stage                        |

| 8          | Vsslog   | Ground   | Logic Ground/Substrate Ground                           |

| 9          | DM-LH    | Output   | Current Recirculation- Output Pin - Low/High Transition |

| 10         | Vdd      | Supply   | Logic Supply                                            |

| 11         | Vssp     | Ground   | Power Ground                                            |

| 12         | Out      | Output   | Main Switch Output                                      |

| 13         | CBoot    | Input    | Bootstrap Capacitor Input Pin                           |

| 14         | Vpp      | Supply   | High Voltage Supply                                     |

| 15         | Vpp      | Supply   | High Voltage Supply                                     |

PowerSO20

| Pin Number | Pin Name | Function | Description                                             |  |

|------------|----------|----------|---------------------------------------------------------|--|

| 1          | Vssub    | Ground   | Substrate Ground                                        |  |

| 2          | HL-Tr    | Input    | Power Recovery High Level/Low Level Transition          |  |

| 3          | H-CImp   | Input    | Main Switch High-Side Clamp Input                       |  |

| 4          | L-CImp   | Input    | Main Switch Low-Side Clamp Input                        |  |

| 5          | LH-Tr    | Input    | Power Recovery Low Level/High Level Transition          |  |

| 6          | PR-FPS   | Input    | Power Recovery Floating Supply                          |  |

| 7          | PR-FPS   | Input    | Power Recovery Floating Supply                          |  |

| 8          | DM-HL    | Input    | Current Recirculation- Input Pin - High/Low Transition  |  |

| 9          | PR       | Output   | Power Recirculation Output Stage                        |  |

| 10         | Vssub    | Ground   | Substrate Ground                                        |  |

| 11         | Vsslog   | Ground   | Logic Ground/Substrate Ground                           |  |

| 12         | DM-LH    | Output   | Current Recirculation- Output Pin - Low/High Transition |  |

| 13         | Vdd      | Supply   | Logic Supply                                            |  |

| 14         | Vssp     | Ground   | Power Ground                                            |  |

| 15         | Vssp     | Ground   | Power Ground                                            |  |

| 16         | Out      | Output   | Main Switch Output                                      |  |

| 17         | CBoot    | Input    | Bootstrap Capacitor Input Pin                           |  |

| Pin Number | Pin Name | Function | Description         |

|------------|----------|----------|---------------------|

| 18         | Vpp      | Supply   | High Voltage Supply |

| 19         | Vpp      | Supply   | High Voltage Supply |

| 20         | Vssub    | Ground   | Substrate Ground    |

### **4 - CIRCUIT DESCRIPTION**

STV7801 is a monolithic integrated circuit implemented in ST Microelectronics BCD proprietary technology designed as a switched power supply generator for data drivers in a Plasma Display Panel (P.D.P.) application.

The high load drive capability of STV7801 reduces the number of devices necessary to drive a complete PDP (4 to 6 devices for a 42" VGA 16/9 PDP monitor).

STV7801 high current drive capability provides a high power recovery efficiency coefficient superior to 85% on constant capacitive load. The structure of the output stage is implemented with 2 DMOS transistors to minimise the die size. External components like bootstrap capacitor can also be implemented to increase the performances of the circuit.

STV7801 integrates level shifters driven with 5V CMOS compatible levels. This feature reduces the number of discrete components such as voltage translators.

STV7801 integrates several protections like output over-voltage, timing control and over-temperature to increase the reliability of the system.

Over-voltage protection consists in clamping diodes connected between Vpp, Vssp and critical nodes of the devices.

Timing control consists in a monitoring of the output stage control signals to avoid any cross-conduction.

Over-temperature protection is activated when junction temperature reaches the threshold values fixed internally and sets the device in tri-state mode.

STV7801 can drive several data drivers connected to column electrodes of the panel. The maximum amount of data drivers is given by the Power Recovery Current of the device and then the maximum rise/fall time of the signal. The rise and fall time of the AC supply signal is adjusted by the value of the inductance connected to the panel capacitance through the data drivers. The amount of STV7801 needed to generate the AC supply can be reduced by increasing the rise/fall time of the generated AC supply.

| HL-Tr | LH-Tr | L-CImp | H-CImp | Device Output          | Comments           |

|-------|-------|--------|--------|------------------------|--------------------|

| L     | Н     | L      | L      | Low to High Transition | Power Saving Mode  |

| Н     | L     | L      | L      | High to Low Transition | Power Saving Mode  |

| L     | Х     | L      | Н      | Vpp                    | Power Supply Clamp |

| Х     | L     | Н      | L      | Vssp                   | Power Ground Clamp |

| Х     | Х     | Н      | Н      | Tri-State              | Protection Mode    |

| Х     | Н     | Н      | Х      | Tri-State              | Protection Mode    |

| Н     | Х     | Х      | Н      | Tri-State              | Protection Mode    |

| L     | L     | L      | L      | Tri-State              | Protection Mode    |

# **5 - CONTROL SIGNALS TRUTH TABLE**

### 6 - POWER ON SEQUENCE

If Vpp is switched ON before Vdd, the circuit remains in Tri-State mode until Vdd reaches Vdd threshold. If Vddis switched ON before Vpp, the circuit remains in Tri-State mode until Vpp reaches Vpp threshold.

| Symbol                  | Parameter                                          | Value                   | Unit |

|-------------------------|----------------------------------------------------|-------------------------|------|

| Vdd                     | Logic Supply Range                                 | -0.3,+14                | V    |

| Vpp                     | Driver Supply Range                                | -0.3 , + 100            | V    |

| VIn                     | Logic Input Voltage Range                          | -0.3, Vdd+0.3           | °C   |

| Ih-Out                  | Main Switch High Side Current                      | -5                      | A    |

| ll-Out                  | Main Switch Low Side Current                       | 5                       | А    |

| lpr-Hi                  | Power Recovery Current (note1)                     | -7                      | А    |

| Ipr-Lo                  | Power Recovery current (note1)                     | 7                       | A    |

| V <sub>CBoot-Vout</sub> | Difference between Boot voltage and output voltage | 14                      | V    |

| Tjmax                   | Maximum Junction Temperature (note2)               | Internally<br>protected | °C   |

| Тор                     | Operating Temperature Range                        | -20, +70                | °C   |

| Tstg                    | Storage Temperature Range                          | -50, +150               | °C   |

### 7 - ABSOLUTE MAXIMUM RATINGS

Note 1 Peak current as defined in Figure 1 on page 9

**Note 2** These parameters are measured during ST's internal qualification which includes temperature characterization on standard and corner batches of the process. These parameters are not tested on the parts.

# 8 - THERMAL DATA

| Symbol               | Parameter                             | Va         | Unit       |      |

|----------------------|---------------------------------------|------------|------------|------|

| Cymbol               | i arameter                            | PowerSO20  | MW15       | onin |

| R <sub>th(j-a)</sub> | Junction - Ambient Thermal Resistance | 40(note3)  | 35 (note4) | °C/W |

| R <sub>th(j-c)</sub> | Junction - Case Thermal Resistance    | +0.6, +2.5 | -0.6, +2.4 |      |

57

Note 3 Multilayer PCB.

Note 4 Package floating in the air.

### 9 - ELECTRICAL CHARACTERISTICS

(T<sub>amb</sub> = 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

| Symbol                   | Parameter                                                                                              | Test Conditions                                | Min | Тур               | Max             | Unit        |

|--------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-------------------|-----------------|-------------|

| SUPPLY                   |                                                                                                        |                                                |     |                   |                 |             |

| Vdd                      | Logic Supply Voltage                                                                                   |                                                | 11  | 12                | 13              | V           |

| Vpp                      | Power Output Supply Voltage                                                                            |                                                | 20  | -                 | 100             | V           |

| Idd                      | Logic Biasing Current without Transition (Stand-by-mode)                                               |                                                | -   | 5                 | -               | mA          |

| Ірр                      | Power Biasing Current without<br>Transition (Stand-by-mode)                                            |                                                | -   | 6                 | -               | mA          |

| BOOTSTRA                 | PPED SUPPLY VOLTAGE                                                                                    |                                                |     |                   |                 |             |

| V <sub>CBoot-Vout</sub>  | Bootstrap supply voltage                                                                               |                                                |     |                   | 12              | V           |

| I <sub>lkg1Boot</sub>    | Boot leakage current Hiz mode                                                                          | Hiz mode<br>Vpp=100V,<br>VCBoot-Vout = 10V     | -5  | 0                 | 5               | μA          |

| I <sub>lkg2Boot</sub>    | Boot leakage current HCImp                                                                             | HCImp = high<br>Vpp=100V,<br>VCBoot-Vout = 10V | 15  | 30                | 50              | μA          |

| OUTPUTS                  |                                                                                                        | •                                              |     |                   |                 |             |

| V <sub>satH</sub>        | Output Saturation Voltage (high level)<br>Voltage Drop vs <sub>Vpp</sub><br>iH@-1A<br>iH@-3A<br>iH@-4A |                                                |     | 1.5<br>4.5<br>6.5 |                 | V<br>V<br>V |

|                          | Output Saturation Voltage (low level)                                                                  |                                                |     |                   |                 |             |

| V <sub>satL</sub>        | iL@1A<br>iL@3A<br>iL@4A                                                                                |                                                |     | 1.5<br>4.5<br>6.5 |                 | V<br>V<br>V |

| V <sub>satHL</sub>       | Power recirculation - Voltage drop (high<br>to low level)<br>iL@1A<br>iL@3A<br>iL@6A                   | V <sub>PR-FPS</sub> =Vpp/2                     |     | 0.8<br>2.5<br>5   |                 | V<br>V<br>V |

| V <sub>satLH</sub>       | Power recirculation - Voltage drop (low<br>to high level)<br>iL@-1A<br>iL@-3A<br>iL@-6A                | V <sub>PR-FPS</sub> =Vpp/2                     |     | 0.8<br>2<br>5     |                 | V<br>V<br>V |

| PROTECTIC                | ÓN                                                                                                     |                                                |     |                   |                 |             |

| Tth                      | Thermal protection temperature threshold                                                               |                                                | -   | 170               | -               | °C          |

| Vdd <sub>threshold</sub> | Power ON threshold voltage on Vdd                                                                      |                                                |     | 7.5               |                 | V           |

| Vpp <sub>threshold</sub> | Power ON threshold voltage on Vpp                                                                      |                                                |     | 13.3              |                 | V           |

| INPUTS                   |                                                                                                        | -                                              |     |                   |                 |             |

| Vih                      | Input high level (CMOS compatible)                                                                     |                                                | 4   |                   | V <sub>dd</sub> | V           |

| Vil                      | Input low level (CMOS compatible)                                                                      |                                                |     |                   | 0.9             | V           |

| lih                      | High level inut current (Vih= <sub>Vdd</sub> )                                                         | Vih=Vdd=12V                                    | 80  | 120               | 150             | μΑ          |

| lil                      | Low level input current (Vil=0)                                                                        |                                                | -2  | 0                 | +2              | μΑ          |

### **10 - AC TIME REQUIREMENTS**

(T<sub>amb</sub> = 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

| Symbol              | Parameter                                                       | Test Conditions | Min | Тур | Мах | Unit |

|---------------------|-----------------------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>LH</sub>     | Low/High transition high level control<br>pulse                 |                 | 10  | -   | -   | ns   |

| t <sub>HL</sub>     | High/Low transition high level control<br>pulse                 |                 | 10  | -   | -   | ns   |

| t <sub>H</sub>      | Duration of high voltage clamp control<br>pulse at high level   |                 | 10  | -   | -   | ns   |

| tL                  | Duration of low voltage clamp control<br>pulse at low level     |                 | 10  | -   | -   | ns   |

| t <sub>Hsetup</sub> | Set-up time of Vpp voltage clamp after low to high transition   |                 | 10  | -   | -   | ns   |

| t <sub>Lsetup</sub> | Set-up time of Vssp voltage clamp after high to low transition  |                 | 100 | -   | -   | ns   |

| t <sub>Hhold</sub>  | Hold time Vout low before high volt-<br>age clamp control pulse |                 | TBD |     |     |      |

| t <sub>Lhold</sub>  | Hold time Vout high before low volt-<br>age clamp control pulse |                 | TBD |     |     |      |

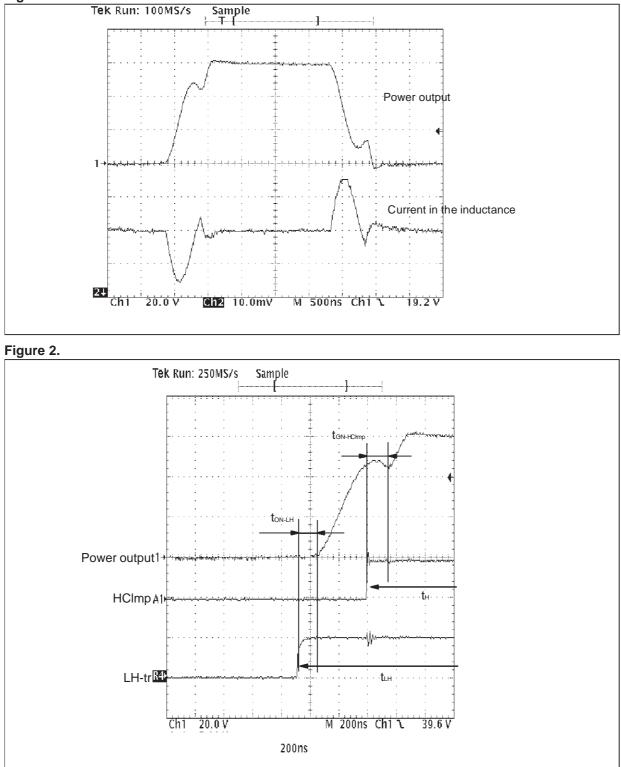

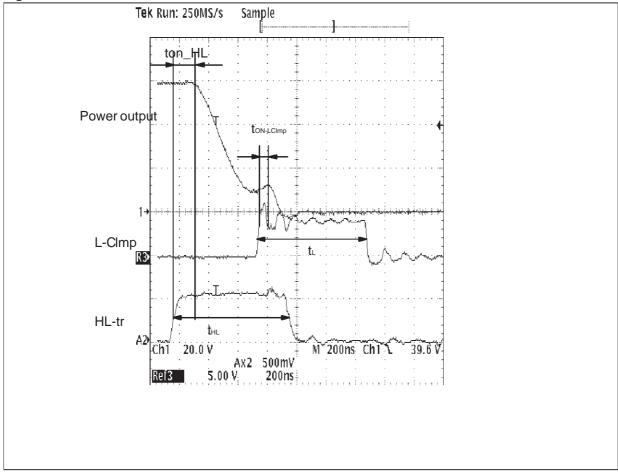

# **11 - AC TIMING CHARACTERISTICS**

(T<sub>amb</sub> = 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

| Symbol                | Parameter                                                               | Test Conditions | Min | Тур | Мах | Unit |

|-----------------------|-------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| t <sub>ON-LH</sub>    | Delay of power output change after recirculation low to high transition | Vpp=40V         | -   | 140 | -   | ns   |

| t <sub>ON-HCImp</sub> | Delay of power output clamp at Vpp after output stage high side ON      |                 | -   | 160 | -   | ns   |

| t <sub>ON-HL</sub>    | Delay of power output change after recirculation high to low transition |                 | -   | 140 | -   | ns   |

| t <sub>ON-LCImp</sub> | Delay of power output clamp at GND after output stage low side ON       |                 | -   | 60  | -   | ns   |

# **12 - AC CHARACTERISTIC WAVEFORMS**

Figure 1.

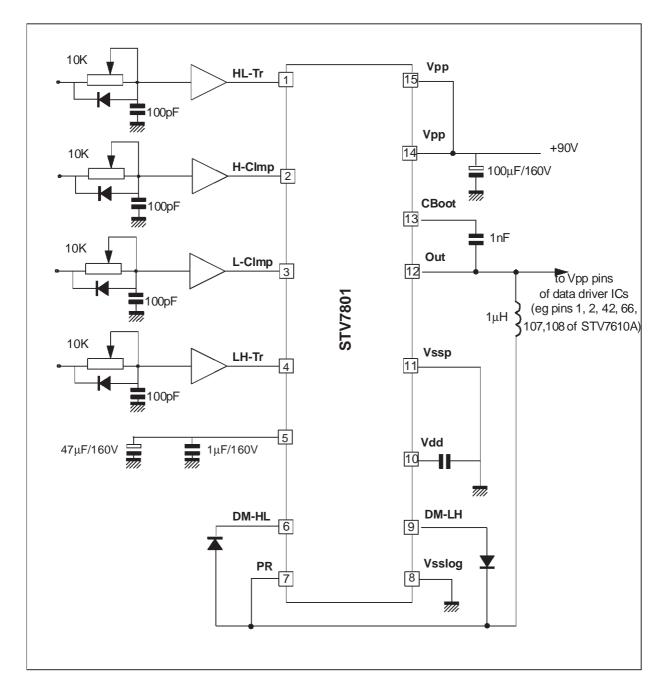

### **13 - APPLICATION DIAGRAM**

57

11/18

The diodes for the recirculation current directly impact the device performances. High Voltage diodes with recovery time inferior to 50ns are recommended. Shorter recovery times will improve the power efficiency of the application.

The rise and fall time of the output signal is adjusted by the value of the inductance for a given capacitive load.

trise (tfall) is calculated by the following formula :

$$t_{rise} = \pi x \sqrt{LxCload}$$

A 1nF bootstrap capacitor is recommended. The bootstrap capacitor allows the output signal to reach the Vpp value. For a given output level, the power efficiency will be increased.

A  $47\mu F$  capacitor is recommended. The ripple on the tank capacitor is reduced by increasing the tank capacitor value.

Decoupling capacitors on the power supplies will minimise the overshoots.

The timing of the control signals will be adjusted by the trimmers of the RC cells. It is recommended to enable the clamp signals (H-Clmp, L-Clmp) after the rising (falling) edge of the output signal has reached its maximum (minimum) value.

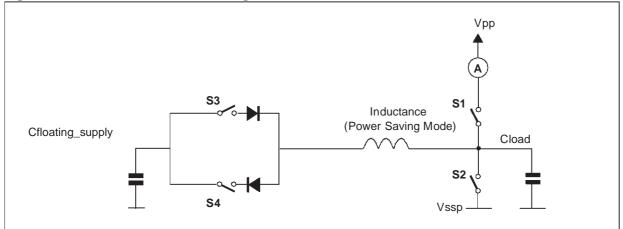

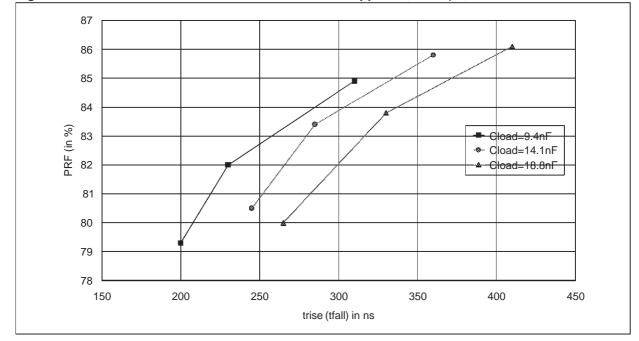

### **14 - RECOVERY FACTOR MEASUREMENT CONDITIONS**

An idealised schematic of the Power Recovery application is defined below. The inductance (power saving mode) and the 2 capacitors (load, floating\_supply) are external components for the D.P.S. device.

#### Figure 4. DPS Device : Functional Diagram

The Power Recovery Factor (PRF) in % is given by the formula :

$$PRF = 100 x (Pc - Pr) / Pc.$$

Pc is the theoretical capacitive power dissipated in the switches S1, S2 of the Data Power Switch device when S3, S4 are not activated. Pc is calculated by the formula :

$$P_{C} = Cload \times Vpp^{2}xF$$

with F=switching frequency.

Cload = equivalent panel capacitance

Pr is the power dissipated in the Data Power Switch device when it is configured in a power recovery mode (S1, S2, S3, S4 activated). Pr is calculated by multiplying the average current given by the current sensor A and the value of the supply voltage Vpp.

PRF is affected by the external components of the DPS device such as the inductance and the decoupling capacitors, also the layout of the application.

<u>/</u>/

12/18

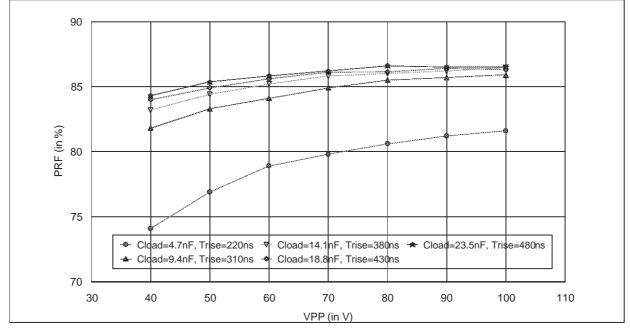

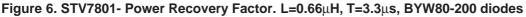

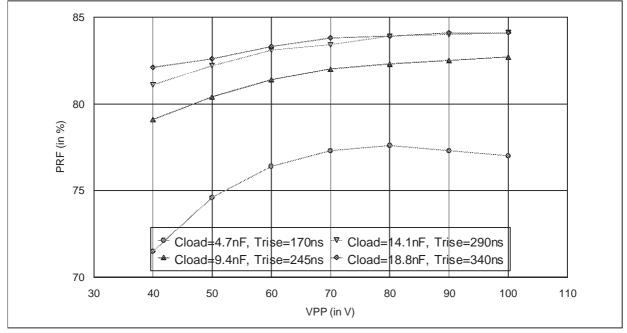

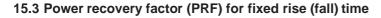

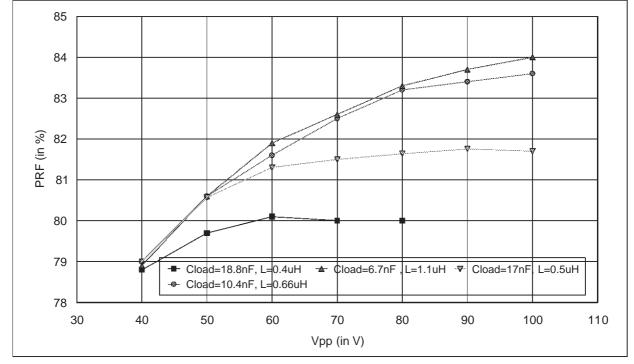

### 15 - RESULTS OF POWER EFFICIENCY

#### 15.1 Power recovery factor for different inductance values

Figure 7. STV7801- Power Recovery Factor - L=0.36µH, T=3.3µs, BYW80-200 diodes

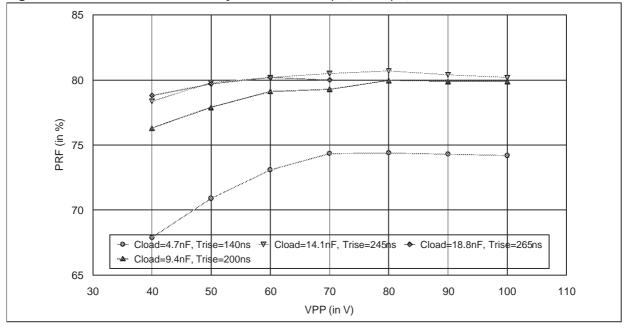

#### 15.2 Power recovery factor (PRF) versus time and Cload

Figure 8. STV7801- PRF versus rise time and Cload - Vpp=70V, T=3.3µs, BYW80-200 diodes

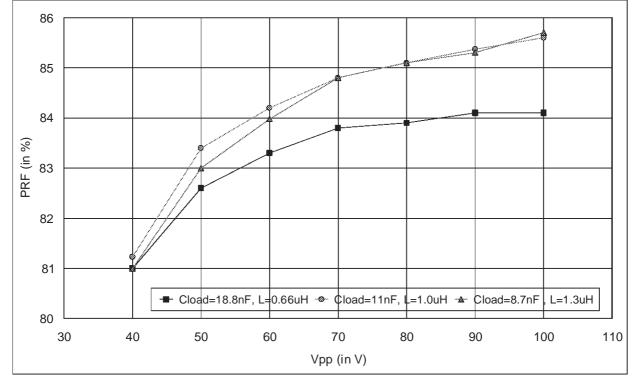

# 16 - PACKAGE MECHANICAL DATA

Multiwatt 15 horizontal, shortleads

|      | Min.  | Тур.  | Max.  | Min.  | Тур.  | Max.  |

|------|-------|-------|-------|-------|-------|-------|

| А    |       |       | 5     |       |       | 0.197 |

| В    |       |       | 2.65  |       |       | 0.104 |

| С    |       |       | 1.6   |       |       | 0.063 |

| E    | 0.49  |       | 0.55  | 0.019 |       | 0.022 |

| F    | 0.66  |       | 0.75  | 0.026 |       | 0.030 |

| G    | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |

| G1   | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.709 |

| H1   | 19.6  |       | 20.2  | 0.772 |       | 0.795 |

| H2   | 19.6  |       | 20.2  | 0.772 |       | 0.795 |

| L1   | 17.8  | 18    | 18.2  | 0.701 | 0.709 | 0.717 |

| L2   | 2.3   | 2.5   | 2.8   | 0.091 | 0.098 | 0.110 |

| L3   | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |

| L4   | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |

| L5   | 2.7   | 3     | 3.3   | 0.106 | 0.118 | 0.130 |

| L7   | 2.65  |       | 2.9   | 0.104 |       | 0.114 |

| R    |       | 1.5   |       |       | 0.059 |       |

| S    | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| S1   | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| Dia1 | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

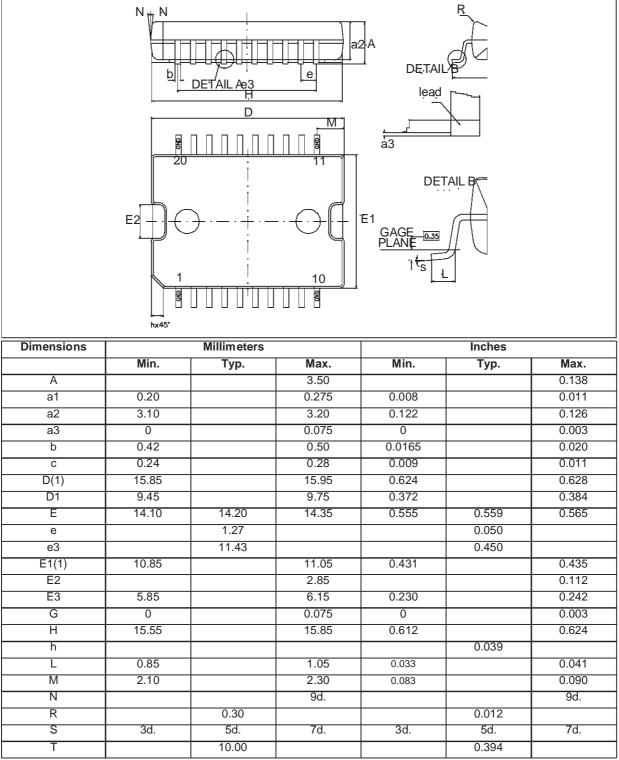

#### PowerSO20

Note 5 "D" and "E1" do not include mold flash or protrusions -Mold flash or protrusions shall not exceed 0.15mm (0.006inc.) -Critical dimensions: "E", "G" and "a3"

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.

#### The ST logo is a registered trademark of STMicroelectronics

#### ©2001 STMicroelectronics - All Rights Reserved.

Purchase of I<sup>2</sup>C Components by STMicroelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

by r mpo.

STMicroelectronics Group of Companies

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -Singapore - Spain Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com