## STE10/100A

# PCI 10/100 ETHERNET CONTROLLER WITH INTEGRATED PHY (3.3V)

PRODUCT PREVIEW

#### 1.0 DESCRIPTION

The STE10/100A is a high performance PCI Fast Ethernet controller with integrated physical layer interface for 10BASE-T and 100BASE-TX application.

It was designed with advanced CMOS technology to provide glueless 32-bit bus master interface for PCI bus, boot ROM interface, CSMA/CD protocol for Fast Ethernet, as well as the physical media interface for 100BASE-TX of IEEE802.3u and 10BASE-T of IEEE802.3. The auto-negotiation function is also supported for speed and duplex detection.

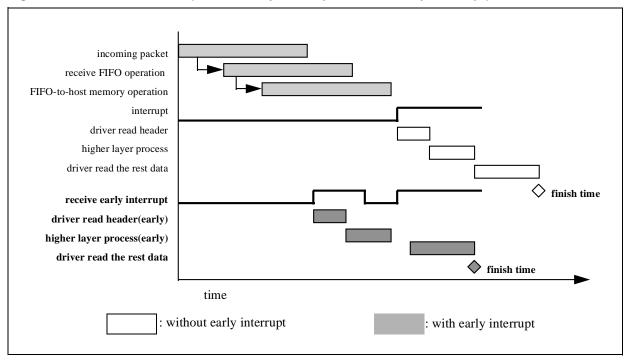

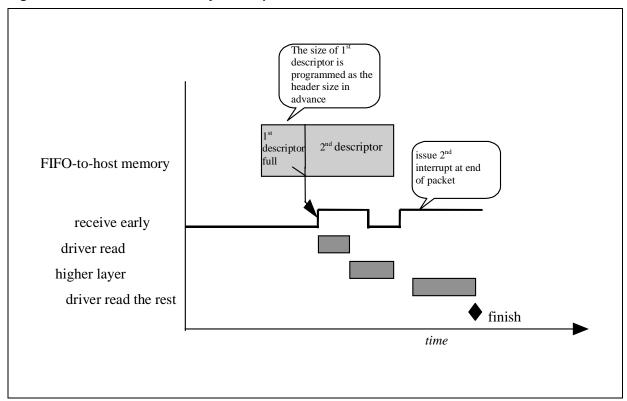

The STE10/100A provides both half-duplex and full-duplex operation, as well as support for full-duplex flow control. It provides long FIFO buffers for transmission and receiving, and early interrupt mechanism to enhance performance. The STE10/100A also supports ACPI and PCI compliant power management function.

#### 2.0 FEATURES

#### 2.1 Industry standard

- IEEE802.3u 100BASE-TX and IEEE802.3 10BASE-T compliant

- Support for IEEE802.3x flow control

- IEEE802.3u Auto-Negotiation support for 10BASE-T and 100BASE-TX

- PCI bus interface Rev. 2.2 compliant

- ACPI and PCI power management standard compliant

- Support PC99 wake on LAN

#### 2.2 FIFO

- Provides independent transmission and receiving FIFOs, each 2k bytes long

- Pre-fetches up to two transmit packets to minimize inter frame gap (IFG) to 0.96us

- Retransmits collided packet without reload from host memory within 64 bytes.

- Automatically retransmits FIFO under-run packet with maximum drain threshold until 3rd time retry failure without influencing the registers and transmit threshold of next packet.

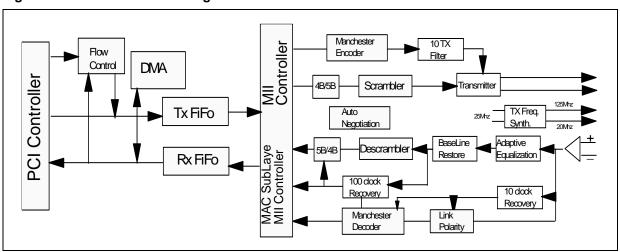

Figure 1. STE10/100A Block Diagram

January 2001 1/66

#### 2.3 PCI I/F

- Provides 32-bit PCI bus master data transfer

- Supports PCI clock with frequency from 0Hz to 33MHz

- Supports network operation with PCI system clock from 20MHz to 33MHz

- Provides performance meter and PCI bus master latency timer for tuning the threshold to enhance the performance

- Provides burst transmit packet interrupt and transmit/receive early interrupt to reduce host CPU utilization

- As bus master, supports memory-read, memory-read-line, memory-read-multiple, memory-write, memory-write-and-invalidate command

- Supports big or little endian byte ordering

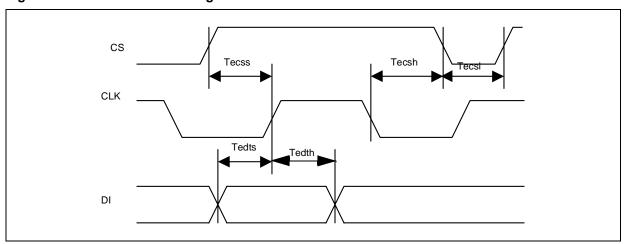

#### 2.4 EEPROM/Boot ROM I/F

- Provides writeable Flash ROM and EPROM as boot ROM, up to 128kB

- Provides PCI to access boot ROM by byte, word, or double word

- Re-writes Flash boot ROM through I/O port by programming register

- Provides serial interface for read/write 93C46 EEPROM

- Automatically loads device ID, vendor ID, subsystem ID, subsystem vendor ID, Maximum-Latency, and Minimum-Grand from the 64 byte contents of 93C46 after PCI reset de-asserted

#### 2.5 MAC/Physical

- Integrates the complete set of Physical layer 100BASE-TX and 10BASE-T functions

- Provides Full-duplex operation in both 100Mbps and 10Mbps modes

- Provides Auto-negotiation (NWAY) function of full/half duplex operation for both 10 and 100 Mbps

- Provides MLT-3 transceiver with DC restoration for Base-line wander compensation

- Provides transmit wave-shaper, receive filters, and adaptive equalizer

- Provides MAC and Transceiver (TXCVR) loop-back modes for diagnostic

- Built-in Stream Cipher Scrambler/ De-scrambler and 4B/5B encoder/decoder

- Supports external transmit and receive transformer with 1:1 turn ratio

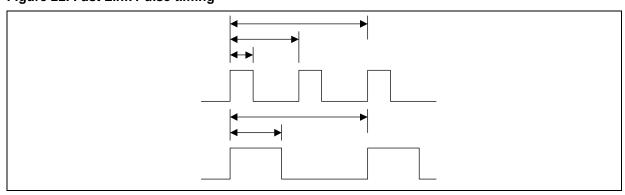

#### 2.6 LED Display

- Provides 2 LED display modes:

- 3 LED displays for

100Mbps (on) or 10Mbps (off)

Link (Remains on when link ok) or Activity (Blinks at 10Hz when receiving or transmitting collision-free) FD (Remains on when in Full duplex mode) or when collision detected (Blinks at 20Hz)

4 LED displays for

100 Link (On when 100M link ok)

10 Link (On when 10M link ok)

Activity (Blinks at 10Hz when receiving or transmitting)

FD (Remains on when in Full duplex mode) or when collision detected (Blinks at 20Hz)

#### 2.7 Miscellaneous

- ACPI and PCI compliant power management functions offer significant power-savings performance

- Provides general purpose timers

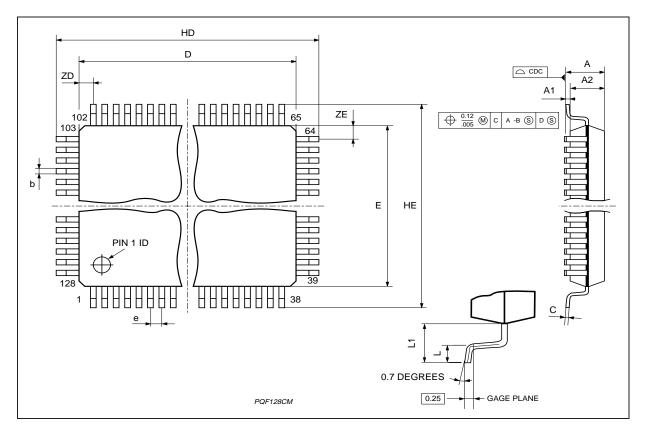

- 128-pin QFP package

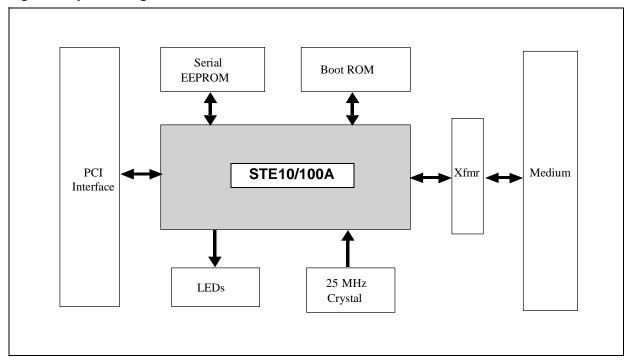

Figure 2. System Diagram of the STE10/100A

#### 3.0 PIN ASSIGNEMENT DIAGRAM

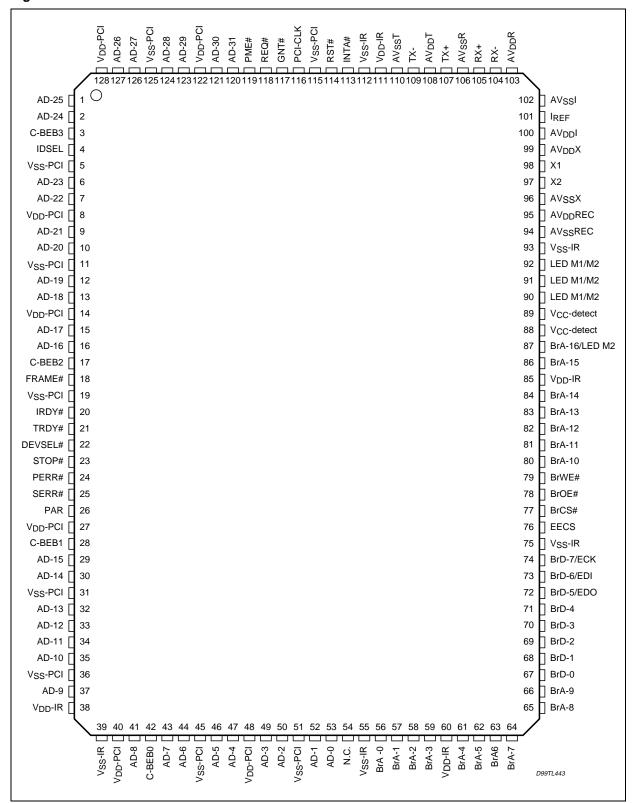

Figure 3. Pin Connection

#### 4.0 4. PIN DESCRIPTION

### **Table 1. Pin Description**

| Pin No.                                                                                                                                 | Name                                                                                                                                                                          | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI bus I                                                                                                                               | nterface                                                                                                                                                                      |         | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 113                                                                                                                                     | INTA#                                                                                                                                                                         | O/D     | PCI interrupt request. STE10/100A asserts this signal when one of the interrupt event is set.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 114                                                                                                                                     | RST#                                                                                                                                                                          | I       | PCI Reset signal to initialize the STE10/100A. The RST signal should be asserted for at least 100μs to ensure that the STE10/100A completes initialization. During the reset period, all the output pins of STE10/100A will be placed in a high-impedance state and all the O/D pins are floated.                                                                                                                                                                                                               |

| 116                                                                                                                                     | PCI-CLK                                                                                                                                                                       | I       | PCI clock input to STE10/100A for PCI Bus functions. The Bus signals are synchronized relative to the rising edge of PCI-CLK PCI-CLK must operate at a frequency in the range between 20MHz and 33MHz to ensure proper network operation                                                                                                                                                                                                                                                                        |

| 117                                                                                                                                     | GNT#                                                                                                                                                                          | I       | PCI Bus Granted. This signal indicates that the STE10/100A has been granted ownership of the PCI Bus as a result of a Bus Request.                                                                                                                                                                                                                                                                                                                                                                              |

| 118                                                                                                                                     | REQ#                                                                                                                                                                          | 0       | PCI Bus Request. STE10/100A asserts this line when it needs access to the PCI Bus.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 119                                                                                                                                     | PME#                                                                                                                                                                          | O<br>OD | The Power Management Event signal is an open drain, active low signal. The STE10/100A will assert PME# to indicate that a power management event has occurred.  When WOL (bit 18 of CSR18) is set, the STE10/100A is placed in Wake On LAN mode. While in this mode, the STE10/100A will activate the PME# signal upon receipt of a Magic Packet frame from the network.  In the Wake On LAN mode, when LWS (bit 17 of CSR18) is set, the LAN-WAKE signal follows HP's protocol; otherwise, it is IBM protocol. |

| 120,121<br>123,124<br>126,127<br>1,2<br>6,7<br>9,10<br>12,13<br>15,16<br>29,30<br>32~35<br>37<br>41<br>43,44<br>46,47<br>49,50<br>52,53 | AD-31,30<br>AD-29,28<br>AD-27,26<br>AD-25,24<br>AD-23,22<br>AD-21,20<br>AD-19,18<br>AD-17,16<br>AD-15,14<br>AD-13~10<br>AD-9<br>AD-8<br>AD-7, 6<br>AD-5,4<br>AD-3,2<br>AD-1,0 | I/O     | Multiplexed PCI Bus address/data pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3<br>17<br>28<br>42                                                                                                                     | C-BEB3<br>C-BEB2<br>C-BEB1<br>C-BEB0                                                                                                                                          | I/O     | Bus command and byte enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                                                                                                                                       | IDSEL                                                                                                                                                                         | I       | Initialization Device Select. This signal is asserted when the host issues configuration cycles to the STE10/100A.                                                                                                                                                                                                                                                                                                                                                                                              |

| 18                                                                                                                                      | FRAME#                                                                                                                                                                        | I/O     | Asserted by PCI Bus master during bus tenure                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20                                                                                                                                      | IRDY#                                                                                                                                                                         | I/O     | Master device is ready to begin data transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                         |                                                                                                                                                                               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**Table 1. Pin Description**

| Pin No.                       | Name                                                         | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------------------------|--------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 21                            | TRDY#                                                        | I/O                    | Target device is ready to begin data transaction                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 22                            | DEVSEL#                                                      | I/O                    | Device select. Indicates that a PCI target device address has been decoded                                                                                                                                                                                                                                                                                                   |  |  |  |

| 23                            | STOP#                                                        | I/O                    | PCI target device request to the PCI master to stop the current transaction                                                                                                                                                                                                                                                                                                  |  |  |  |

| 24                            | PERR#                                                        | I/O                    | ata parity error detected, driven by the device receiving data                                                                                                                                                                                                                                                                                                               |  |  |  |

| 25                            | SERR#                                                        | O/D                    | Address parity error                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 26                            | PAR                                                          | I/O                    | Parity. Even parity computed for AD[31:0] and C/BE[3:0]; master drives PAR for address and write data phase, target drives PAR for read data phase                                                                                                                                                                                                                           |  |  |  |

| BootROM                       | I/EEPROM In                                                  | terface                | ,                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 56~59<br>61~66<br>80~86<br>87 | BrA0~3<br>BrA4~9<br>BrA10~15<br>BrA16/<br>LED M2 -<br>Fd/Col | I/O                    | ROM data bus Provides up to 128kB EPROM or Flash-ROM application space.  This pin can be programmed as mode 2 LED display for Full Duplex or Collision status. It will be driven (LED on) continually when a full duplex configuration is detected, or it will be driven at a 20 Hz blinking frequency when a collision status is detected in the half duplex configuration. |  |  |  |

| 67~71<br>72<br>73<br>74       | BrD0~4<br>BrD5/EDO<br>BrD6/EDI<br>BrD7/ECK                   | O<br>O/I<br>O/O<br>O/O | BootROM data bus (0~7) EDO: Data output of serial EEPROM, data input to STE10/100A EDI:Data input to serial EEPROM, data output from STE10/100A ECK:Clock input to serial EEPROM, sourced by STE10/100A                                                                                                                                                                      |  |  |  |

| 76                            | EECS                                                         | 0                      | Chip Select of serial EEPROM                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 77                            | BrCS#                                                        | 0                      | BootROM Chip Select                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 78                            | BrOE#                                                        | 0                      | BootROM Read Output Enable for flash ROM application                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 79                            | BrWE#                                                        | 0                      | BootROM Write Enable for flash ROM application.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Physical                      | Interface                                                    |                        |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 98                            | X1                                                           | I                      | 25 MHz reference clock input for Physical portion. When an external 25 MHz crystal is used, this pin will be connected to one of its terminals, and X2 will be connected to the other terminal. If an external 25 MHz oscillator is used, then this pin will be connected to the oscillator's output pin.                                                                    |  |  |  |

| 97                            | X2                                                           | 0                      | 25 MHz reference clock output for Physical portion. When an external 25MHz crystal is used, this pin will be connected to one of the crystal terminals (see X1, above). If an external clock source is used, then this pin should be left open.                                                                                                                              |  |  |  |

| 107,109                       | TX+, TX-                                                     | 0                      | The differential Transmit outputs of 100BASE-TX or 10BASE-T, these pins connect directly to Magnetic.                                                                                                                                                                                                                                                                        |  |  |  |

| 105,104                       | RX+, RX-                                                     | I                      | The differential Receive inputs of 100BASE-TX or 10BASE-T, these pins connect directly from Magnetic.                                                                                                                                                                                                                                                                        |  |  |  |

| 101                           | Iref                                                         | 0                      | Reference Resistor connecting pin for reference current, directly connects a 5K Ohm $\pm$ 1% resistor to Vss.                                                                                                                                                                                                                                                                |  |  |  |

**Table 1. Pin Description**

| Pin No.  | Name                                          | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED disp | lay & Miscell                                 | aneous |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 90       | LED M1-<br>LK/Act<br>or<br>LED M2-<br>Act     | 0      | This pin can be programmed as mode 1 or mode 2: For mode 1: LED display for Link and Activity status. This pin will be driven on continually when a good Link test is detected. This pin will be driven at a 10 Hz blinking frequency when either effective receiving or transmitting is detected. For mode 2: LED display for Activity status. This pin will be driven at a 10 Hz blinking frequency when either effective receiving or transmitting is detected.    |

| 92       | LED M1-<br>Speed<br>or<br>LED M2-<br>100 Link | 0      | This pin can be programmed as mode 1 or mode 2: For mode 1: LED display for 100M b/s or 10M b/s speed. This pin will be driven on continually when the 100M b/s network operating speed is detected. For mode 2: LED display for 100Ms/s link status. This pin will be driven on continually when 100Mb/s network operating speed is detected.                                                                                                                        |

| 91       | LED M1-<br>Fd/Col<br>or<br>LED M2-<br>10 Link | 0      | This pin can be programmed as mode 1 or mode 2: For mode 1: LED display for Full Duplex or Collision status. This pin will be driven on continually when a full duplex configuration is detected. This pin will be driven at a 20 Hz blinking frequency when a collision status is detected in the half duplex configuration. For mode 2: LED display for 10Ms/s link status. This pin will be driven on continually when 10Mb/s network operating speed is detected. |

| 89       | Vaux-<br>detect                               | I      | When this pin is asserted, it indicates an auxiliary power source is supported from the system.                                                                                                                                                                                                                                                                                                                                                                       |

| 88       | Vcc-detect                                    | I      | When this pin is asserted, it indicates a PCI power source is supported.                                                                                                                                                                                                                                                                                                                                                                                              |

| Digital Power Pins                          |      |  |  |  |  |

|---------------------------------------------|------|--|--|--|--|

| 5,11,19,31,36,39,45,51,55,75,93,112,115,125 | Vss  |  |  |  |  |

| 8,14,27,38,40,48,60,85,111,122,128          | Vdd  |  |  |  |  |

| Analog Power Pins                           |      |  |  |  |  |

| 94,96,102,106,110                           | AVss |  |  |  |  |

| 95,99,100,103,108                           | AVdd |  |  |  |  |

477

#### 5.0 REGISTERS AND DESCRIPTORS DESCRIPTION

There are three kinds of registers within the STE10/100A: STE10/100A configuration registers, PCI control/status registers, and Transceiver control/status registers.

The STE10/100A configuration registers are used to initialize and configure the STE10/100A and for identifying and querying the STE10/100A.

The PCI control/status registers are used to communicate between the host and STE10/100A. The host can initialize, control, and read the status of the STE10/100A through mapped I/O or memory address space.

The STE10/100A contains 11 16-bit registers to supported Transceiver control and status. They include 7 basic registers which are defined according to clause 22 "Reconciliation Sub-layer and Media Independent Interface" and clause 28 "Physical Layer link signaling for 10 Mb/s and 100 Mb/s Auto-Negotiation on twisted pair" of the IEEE802.3u standard. In addition, 4 special registers are provided for advanced chip control and status.

The STE10/100A also provides receive and transmit descriptors for packet buffering and management.

#### 5.1 STE10/100A Configuration Registers

An STE10/100A software driver can initialize and configure the chip by writing its configuration registers. The contents of configuration registers are set to their default values upon power-up or whenever a hardware reset occurs, but their settings remain unchanged whenever a software reset occurs. The configuration registers are byte, word, and double word accessible.

Table 2. STE10/100A configuration registers list

| Offset | Index | Name | Descriptions                             |

|--------|-------|------|------------------------------------------|

| 00h    | CR0   | LID  | Loaded device ID and vendor ID           |

| 04h    | CR1   | CSC  | Configuration Status and Command         |

| 08h    | CR2   | CC   | Class Code and revision number           |

| 0ch    | CR3   | LT   | Latency Timer                            |

| 10h    | CR4   | IOBA | IO Base Address                          |

| 14h    | CR5   | MBA  | Memory Base Address                      |

| 2ch    | CR11  | SID  | Subsystem ID and vendor ID               |

| 30h    | CR12  | BRBA | Boot ROM Base Address (ROM size = 128KB) |

| 34h    | CR13  | СР   | Capability Pointer                       |

| 3ch    | CR15  | CINT | Configuration Interrupt                  |

| 40h    | CR16  | DS   | driver space for special purpose         |

| 80h    | CR32  | SIG  | Signature of STE10/100A                  |

| c0h    | CR48  | PMR0 | Power Management Register 0              |

| c4h    | CR49  | PMR1 | Power Management Register 1              |

Table 3. STE10/100A configuration registers table

| c4h         | Reserved        |             |                      | ICSR          |       |

|-------------|-----------------|-------------|----------------------|---------------|-------|

| c0h         | PN              | <b>IC</b>   | Next_Item_Ptr        | Cap_ID        |       |

| 80h         |                 | Signature o | f STE10/100A         |               |       |

| <b>40</b> h | Rese            | rved        | Driver Space         | Reserved      | d     |

| 3ch         | Max_Lat*        | Min_Gnt*    | Interrupt pin        | Interrupt lir | ne    |

| 38h         |                 | Res         | erved                |               | -     |

| 34h         |                 | Reserved    |                      | Cap_Ptr       |       |

| 30h         |                 | Boot ROM I  | oase address         |               |       |

| 2ch         | Subsyst         | em ID*      | Subsystem vendor ID* |               |       |

| 18h~<br>28h | Reserved        |             |                      |               |       |

| 14h         |                 | Base mem    | ory address          |               |       |

| 10h         |                 | Base I/C    | ) address            |               |       |

| 0ch         |                 |             | Latency timer        | cache line s  | size  |

| 08h         | Base Class Code | Subclass    |                      | Revision #    | Step# |

| 04h         | Stat            | tus         | Com                  | mand          |       |

| 00h         | Device          | e ID*       | Vend                 | lor ID*       |       |

| offset      | b31             | b16         | b15                  | b0            |       |

Note: \*: automatically recalled from EEPROM when PCI reset is deserted DS(40h), bit15-8, is read/write able register SIG(80h) is hard wired register, read only

## 5.1.1 STE10/100A configuration registers descriptions Table 4. Configuration Registers Descriptions

| Bit #        | Name            | Descriptions                                                                                                                                               | Default Val    | RW Type |

|--------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------|

| CR0(offset = | = 00h), LID - L | Loaded Identification number of Device and Vendor                                                                                                          |                |         |

| 31~16        | LDID            | Loaded Device ID, the device ID number loaded from serial EEPROM.                                                                                          | From<br>EEPROM | R/O     |

| 15~0         | LVID            | Loaded Vendor ID, the vendor ID number loaded from serial EEPROM.                                                                                          | From<br>EEPROM | R/O     |

| From EEPROM  | M: Loaded from  | EEPROM                                                                                                                                                     |                |         |

| CR1(offset = | = 04h), CSC -   | Configuration command and status                                                                                                                           |                |         |

| 31           | SPE             | Status Parity Error.  1: means that STE10/100A detected a parity error. This bit will be set even if the parity error response (bit 6 of CR1) is disabled. | 0              | R/W     |

| 30           | SES             | Status System Error. 1: means that STE10/100A asserted the system error pin.                                                                               | 0              | R/W     |

**Table 4. Configuration Registers Descriptions**

| Bit #  | Name | Descriptions                                                                                                                                                                                                                                                                       | Default Val                   | RW Type |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|

| 29     | SMA  | Status Master Abort. 1: means that STE10/100A received a master abort and has terminated a master transaction.                                                                                                                                                                     | 0                             | R/W     |

| 28     | STA  | Status Target Abort. 1: means that STE10/100A received a target abort and has terminated a master transaction.                                                                                                                                                                     | 0                             | R/W     |

| 27     |      | Reserved.                                                                                                                                                                                                                                                                          |                               |         |

| 26, 25 | SDST | Status Device Select Timing. Indicates the timing of the chip's assertion of device select. 01: indicates a medium assertion of DEVSEL#                                                                                                                                            | 01                            | R/O     |

| 24     | SDPR | Status Data Parity Report.  1: when three conditions are met: a. STE10/100A asserted parity error (PERR#) or it detected parity error asserted by another device. b. STE10/100A is operating as a bus master. c. STE10/100A's parity error response bit (bit 6 of CR1) is enabled. | 0                             | R/W     |

| 23     | SFBB | Status Fast Back-to-Back<br>Always 1, since STE10/100A has the ability to accept fast<br>back to back transactions.                                                                                                                                                                | 1                             | R/O     |

| 22~21  |      | Reserved.                                                                                                                                                                                                                                                                          |                               |         |

| 20     | NC   | New Capabilities. Indicates whether the STE10/100A provides a list of extended capabilities, such as PCI power management.  1: the STE10/100A provides the PCI management function 0: the STE10/100A doesn't provide New Capabilities.                                             | Same as<br>bit 19 of<br>CSR18 | RO      |

| 19~ 9  |      | Reserved.                                                                                                                                                                                                                                                                          |                               |         |

| 8      | CSE  | Command System Error Response 1: enable system error response. The STE10/100A will assert SERR# when it finds a parity error during the address phase.                                                                                                                             | 0                             | R/W     |

| 7      |      | Reserved.                                                                                                                                                                                                                                                                          |                               |         |

| 6      | CPE  | Command Parity Error Response 0: disable parity error response. STE10/100A will ignore any detected parity error and keep on operating. Default value is 0. 1: enable parity error response. STE10/100A will assert system error (bit 13 of CSR5) when a parity error is detected. | 0                             | R/W     |

| 5~ 3   |      | Reserved.                                                                                                                                                                                                                                                                          |                               |         |

| 2      | СМО  | Command Master Operation Ability 0: disable the STE10/100A bus master ability. 1: enable the PCI bus master ability. Default value is 1 for normal operation.                                                                                                                      | 0                             | R/W     |

| 1      | CMSA | Command Memory Space Access 0: disable the memory space access ability. 1: enable the memory space access ability.                                                                                                                                                                 | 0                             | R/W     |

**Table 4. Configuration Registers Descriptions**

| Bit #        | Name             | Descriptions                                                                                                                                                                                                                                                                                                                                                                                       | Default Val | RW Type |

|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|

| 0            | CIOSA            | Command I/O Space Access 0: enable the I/O space access ability. 1: disable the I/O space access ability.                                                                                                                                                                                                                                                                                          | 0           | R/W     |

| R/W: Read an | nd Write able. R | O: Read able only.                                                                                                                                                                                                                                                                                                                                                                                 |             |         |

| CR2(offset   | = 08h), CC - 0   | Class Code and Revision Number                                                                                                                                                                                                                                                                                                                                                                     |             |         |

| 31~24        | BCC              | Base Class Code. It means STE10/100A is a network controller.                                                                                                                                                                                                                                                                                                                                      | 02h         | RO      |

| 23~16        | SC               | Subclass Code. It means STE10/100A is a Fast Ethernet Controller.                                                                                                                                                                                                                                                                                                                                  | 00h         | RO      |

| 15~ 8        |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                          |             |         |

| 7 ~ 4        | RN               | Revision Number, identifies the revision number of STE10/100A.                                                                                                                                                                                                                                                                                                                                     | Ah          | RO      |

| 3 ~ 0        | SN               | Step Number, identifies the STE10/100A steps within the current revision.                                                                                                                                                                                                                                                                                                                          | 1h          | RO      |

| RO: Read On  | ly.              |                                                                                                                                                                                                                                                                                                                                                                                                    |             |         |

| CR3(offset   | = 0ch), LT - L   | atency Timer                                                                                                                                                                                                                                                                                                                                                                                       |             |         |

| 31~16        |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                          |             |         |

| 15~ 8        | LT               | Latency Timer. This value specifies the latency timer of the STE10/100A in units of PCI bus clock cycles. Once the STE10/100A asserts FRAME#, the latency timer starts to count. If the latency timer expires and the STE10/100A is still asserting FRAME#, the STE10/100A will terminate the data transaction as soon as its GNT# is removed.                                                     | 0           | R/W     |

| 7 ~ 0        | CLS              | Cache Line Size. This value specifies the system cache line size in units of 32-bit double words(DW). The STE10/100A supports cache line sizes of 8, 16, or 32 DW. CLS is used by the STE10/100A driver to program the cache alignment bits (bit 14 and 15 of CSR0) which are used for cache oriented PCI commands, e.g., memory-read-line, memory-read-multiple, and memory-write-and-invalidate. | 0           | R/W     |

| CR4(offset   | = 10h), IOBA     | - I/O Base Address                                                                                                                                                                                                                                                                                                                                                                                 |             |         |

| 31~ 7        | IOBA             | I/O Base Address. This value indicate the base address of PCI control and status register (CSR0~28), and Transceiver registers (XR0~10)                                                                                                                                                                                                                                                            | 0           | R/W     |

| 6 ~ 1        |                  | reserved.                                                                                                                                                                                                                                                                                                                                                                                          |             |         |

| 0            | IOSI             | I/O Space Indicator.  1: means that the configuration registers map into I/O space.                                                                                                                                                                                                                                                                                                                | 1           | RO      |

| CR5(offset   | = 14h), MBA      | - Memory Base Address                                                                                                                                                                                                                                                                                                                                                                              |             |         |

| 31~ 7        | MBA              | Memory Base Address. This value indicate the base address of PCI control and status register(CSR0~28), and Transceiver registers(XR0~10)                                                                                                                                                                                                                                                           | 0           | R/W     |

| 6 ~ 1        |                  | reserved.                                                                                                                                                                                                                                                                                                                                                                                          |             |         |

**Table 4. Configuration Registers Descriptions**

| Bit #                     | Name             | Descriptions                                                                                                                                                                                                                                                                            | Default Val            | RW Type        |

|---------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|

| 0                         | IOSI             | Memory Space Indicator.  1: means that the configuration registers map into I/O space.                                                                                                                                                                                                  | 0                      | RO             |

| CR11(offset               | = 2ch), SID -    | Subsystem ID.                                                                                                                                                                                                                                                                           |                        |                |

| 31~16                     | SID              | Subsystem ID. This value is loaded from EEPROM as a result of power-on or hardware reset.                                                                                                                                                                                               | From<br>EEPROM         | RO             |

| 15~ 0                     | SVID             | Subsystem Vendor ID. This value is loaded from EEPROM as a result power-on or hardware reset.                                                                                                                                                                                           | From<br>EEPROM         | RO             |

| CR12(offset<br>boot ROM s |                  | A - Boot ROM Base Address. This register should be initialize                                                                                                                                                                                                                           | ed before ac           | cessing the    |

| 31~10                     | BRBA             | Boot ROM Base Address. This value indicates the address mapping of the boot ROM field as well as defining the boot ROM size. The values of bit 16~10 are set to 0 indicating that the STE10/100A supports up to 128kB of boot ROM.                                                      | X: b31~17<br>0: b16~10 | R/W<br>RO      |

| 9 ~ 1                     |                  | reserved                                                                                                                                                                                                                                                                                |                        | RO R/W R/<br>W |

| 0                         | BRE              | Boot ROM Enable. The STE10/100A will only enable its boot ROM access if both the memory space access bit (bit 1 of CR1) and this bit are set to 1.  1: enable Boot ROM. (if bit 1 of CR1 is also set)                                                                                   | 0                      | R/W            |

| CR13(offset               | t = 34h), CP -   | Capabilities Pointer.                                                                                                                                                                                                                                                                   |                        |                |

| 31~8                      |                  | reserved                                                                                                                                                                                                                                                                                |                        |                |

| 7~0                       | СР               | Capabilities Pointer.                                                                                                                                                                                                                                                                   | СОН                    | RO             |

| CR15(offset               | t = 3ch), CI - ( | Configuration Interrupt                                                                                                                                                                                                                                                                 |                        |                |

| 31~24                     | ML               | Max_Lat register. This value indicates how often the STE10/100A needs to access to the PCI bus in units of 250ns. This value is loaded from serial EEPROM as a result of power-on or hardware reset.                                                                                    | From<br>EEPROM         | RO             |

| 23~16                     | MG               | Min_Gnt register. This value indicates how long the STE10/100A needs to retain the PCI bus ownership whenever it initiates a transaction, in units of 250ns. This value is loaded from serial EEPROM as a result power-on or hardware reset.                                            | From<br>EEPROM         | RO             |

| 15~ 8                     | IP               | Interrupt Pin. This value indicates one of four interrupt request pins to which the STE10/100A is connected. 01h: means the STE10/100A always connects to INTA#                                                                                                                         | 01h                    | RO             |

| 7 ~ 0                     | IL               | Interrupt Line. This value indicates the system interrupt request lines to which the INTA# of STE10/100A is routed. The BIOS will fill this field when it initializes and configures the system. The STE10/100A driver can use this value to determine priority and vector information. | 0                      | R/W            |

| CR16(offset               | t = 40h), DS -   | Driver Space for special purpose.                                                                                                                                                                                                                                                       |                        |                |

|                           | 1                | reserved                                                                                                                                                                                                                                                                                |                        |                |

**Table 4. Configuration Registers Descriptions**

| Bit #                      | Name                                       | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Default Val | RW Type |

|----------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|

| 15~8                       | DS                                         | Driver Space for implementation-specific purpose. Since this area won't be cleared upon software reset, an STE10/100A driver can use this R/W area as user-specified storage.                                                                                                                                                                                                                                                                                                                                                                                                       | 0           | R/W     |

| 7 ~ 0                      |                                            | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |         |

| CR32(offset                | t = 80h), SIG                              | - Signature of STE10/100A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |         |

| 31~16                      | DID                                        | Device ID, the device ID number of the STE10/100A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2774h       | RO      |

| 15~0                       | VID                                        | Vendor ID, the vendor ID number of STMicroelectronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 104Ah       | RO      |

| CR48(offset                | = c0h), PMR                                | 0, Power Management Register0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | !           |         |

| 31<br>30<br>29<br>28<br>27 | PSD3c,<br>PSD3h,<br>PSD2,<br>PSD1,<br>PSD0 | PME_Support. The STE10/100A will assert PME# signal while in the D0, D1, D2, D3hot and D3cold power state. The STE10/100A supports Wake-up from the above five states. Bit 31 (support wake-up from D3cold) is loaded from EEPROM after power-up or hardware reset. To support the D3cold wake-up function, an auxiliary power source will be sensed during reset by the STE10/100A Vaux_detect pin. If sensed low, PSD3c will be set to 0; if sensed high, and if D3CS (bit 31of CSR18) is set (CSR18 bits 16~31 are recalled from EEPROM at reset), then bit 31 will be set to 1. | X1111b      | RO      |

| 26                         | D2S                                        | D2_Support. The STE10/100A supports the D2 Power Management State.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1           | RO      |

| 25                         | D1S                                        | D1_Support. The STE10/100A supports the D1 Power Management State.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1           | RO      |

| 24~22                      | AUXC                                       | Aux Current. These three bits report the maximum 3.3Vaux current requirements for STE10/100A chip. If bit 31 of PMR0 is '1', the default value is 111b, meaning the STE10/100A needs 375 mA to support remote wake-up in D3cold power state. Otherwise, the default value is 000b, meaning the STE10/100A does not support remote wake-up from D3cold power state.                                                                                                                                                                                                                  | XXXb        | RO      |

| 21                         | DSI                                        | The Device Specific Initialization bit indicates whether any special initialization of this function is required before the generic class device driver is able to use it.  0: indicates that the function does not require a device-specific initialization sequence following transition to the D0 uninitialized state.                                                                                                                                                                                                                                                           | 0           | RO      |

| 20                         |                                            | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |         |

| 19                         | PMEC                                       | PME Clock. Indicates that the STE10/100A does not rely on the presence of the PCI clock for PME# operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0           | RO      |

| 18~16                      | VER                                        | Version. The value of 010b indicates that the STE10/100A complies with Revision 1.0a of the PCI Power Management Interface Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 010b        | RO      |

| 15~8                       | NIP                                        | Next Item Pointer. This value is always 0h, indicating that there are no additional items in the Capabilities List.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00h         | RO      |

| 7~0                        | CAPID                                      | Capability Identifier. This value is always 01h, indicating the link list item as being the PCI Power Management Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01h         | RO      |

**Table 4. Configuration Registers Descriptions**

| Bit #      | Name          | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Default Val | RW Type |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|

| CR49(offse | t = c4h), PMR | 11, Power Management Register 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |         |

| 31~16      |               | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |         |

| 15         | PMEST         | PME_Status. This bit is set whenever the STE10/100A detects a wake-up event, regardless of the state of the PME-En bit. Writing a "1" to this bit will clear it, causing the STE10/100A to deassert PME# (if so enabled). Writing a "0" has no effect. If PSD3c (bit 31 of PMR0) is cleared (i.e. it does not support PME# generation from D3cold), this bit is by default 0; otherwise, PMEST is cleared upon power-up reset only and is not modified by either hardware or software reset. | Х           | R/W1C*  |

| 14,13      | DSCAL         | Data_Scale. Indicates the scaling factor to be used when interpreting the value of the Data register. This field is required for any function that implements the Data register. The STE10/100A does not support Data register and Data_Scale.                                                                                                                                                                                                                                               | 00b         | RO      |

| 12~9       | DSEL          | Data_Select. This four bit field is used to select which data is to be reported through the Data register and Data_Scale field. This field is required for any function that implements the Data register.  The STE10/100A does not support Data_select.                                                                                                                                                                                                                                     | 0000b       | R/W     |

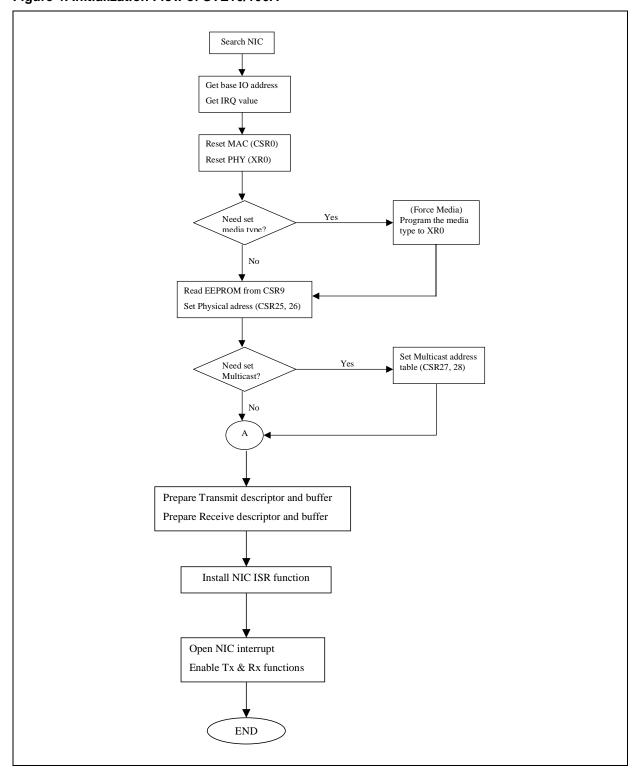

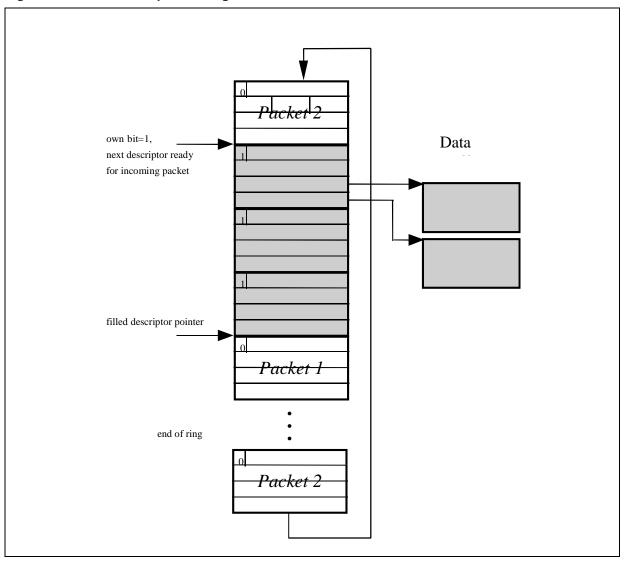

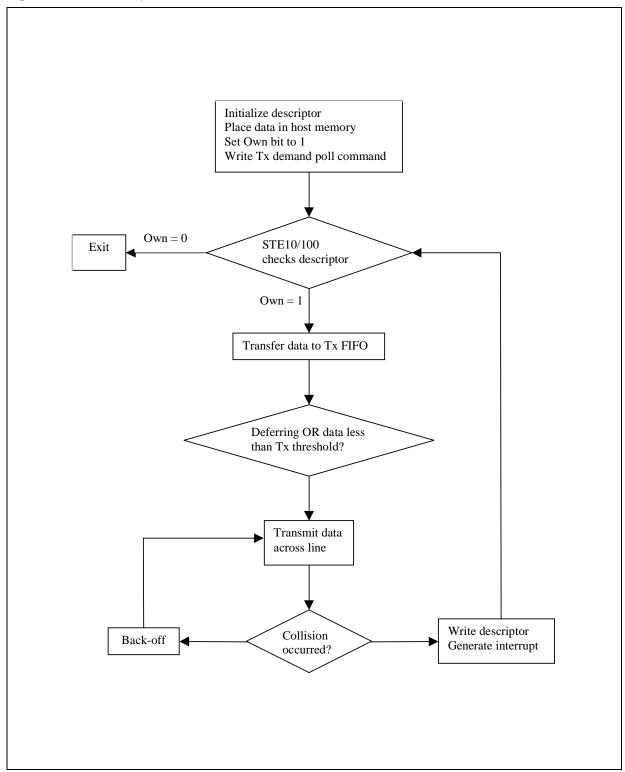

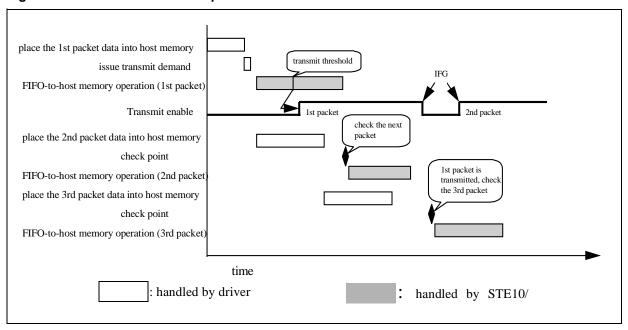

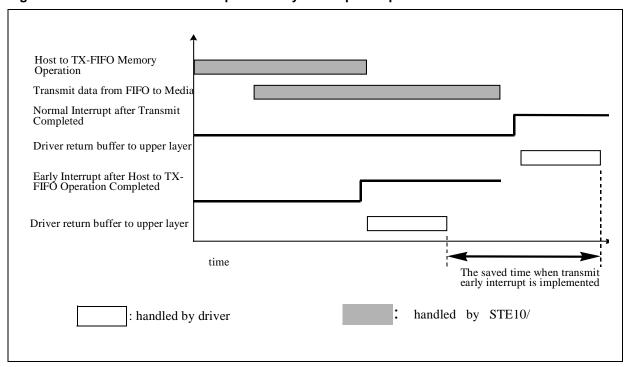

| 8          | PME_En        | PME_En. When set, enables the STE10/100A to assert PME#. When cleared, disables the PME# assertion. If PSD3c (bit 31 of PMR0) is cleared (i.e. it does not support PME# generation from D3cold), this bit is by default 0; otherwise, PME_En is cleared upon power up reset only and is not modified by either hardware or software reset.                                                                                                                                                   | Х           | R/W     |