# Non-volatile electronic potentiometer BU9831 / BU9831F

The BU9831 / BU9831F is a non-volatile electronic potentiometer with an internal 2k bit EEPROM. The resistance value can be set by means of serial communications, and because the product contains an internal memory, conditions can be retained.

In addition, the 2k bit memory capacity enables digital data to be stored in the memory.

## Applications

Portable LCD backlight adjustment devices for notebook computers, and other sound adjustment devices for sets

### Features

- 1) Internal 2k bit EEPROM

- 2)  $100k\Omega$  ( $1k\Omega \times 100$  steps) electronic potentiometer

- 3) Data in memory is automatically read when power supply is turned on, and resistance value is set.

- 4) Resistance value can be set using serial communications.

- 5) Low current consumption

When operating: 3mA (max.) In standby mode: 200µA (max.)

#### Absolute maximum ratings (Ta = 25°C)

| Parameter             |         | Symbol | Symbol Limits        |       |  |

|-----------------------|---------|--------|----------------------|-------|--|

| Applied voltage       |         | Vcc    | - 0.3 ~ <b>+</b> 7.0 | V     |  |

| Power                 | BU9831  | Pd     | 500*1                | mW    |  |

| dissipation           | BU9831F | Pu     | 350*²                | IIIVV |  |

| Storage temperature   |         | Tstg   | - 65 ~ <b>+</b> 125  | °C    |  |

| Operating temperature |         | Topr   | - 20 ~ <b>+</b> 85   | °C    |  |

| Input voltage         |         | _      | - 0.3 ~ Vcc + 0.3    | V     |  |

| Wiper current         |         | lw     | ± 1.0                | mA    |  |

<sup>\*1</sup> Reduced by 5.0mW for each increase in Ta of 1°C over 25°C.

## Recommended operating conditions

| Parameter                        | Symbol | Limits    | Unit |

|----------------------------------|--------|-----------|------|

| Power supply voltage             | Vcc    | 2.7 ~ 5.5 | V    |

| Power supply voltage for writing | Vccwr  | 2.8 ~ 5.5 | V    |

| Input voltage                    | Vin    | 0 ~ Vcc   | V    |

| Voltage at resistor ends         | VRHL   | 0 ~ Vcc   | V    |

| Wiper pin voltage                | Vw     | 0 ~ Vcc   | V    |

<sup>\*2</sup> Reduced by 3.5mW for each increase in Ta of 1°C over 25°C.

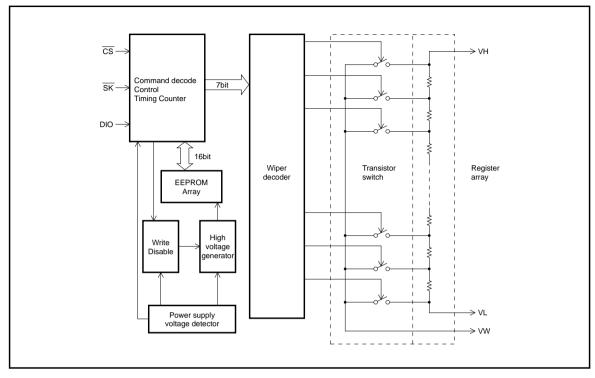

## Block diagram

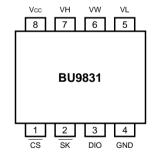

## Pin assignments

## Pin desoriptions

| Pin No. | Pin name | 1/0            | Function                                                      |

|---------|----------|----------------|---------------------------------------------------------------|

| 1       | CS       | I              | Chip select input                                             |

| 2       | SK       | I              | Serial data clock input                                       |

| 3       | DIO      | 1/0            | Input / output of operating codes, addresses, and serial data |

| 4       | GND      | _              | Reference voltage of 0V for all input / output                |

| 5       | VL       | Resistance pin | Resistance low-potential                                      |

| 6       | VW       | Resistance pin | Wiper                                                         |

| 7       | VH       | Resistance pin | Resistance high-potential                                     |

| 8       | Vcc      | _              | Connection for power supply                                   |

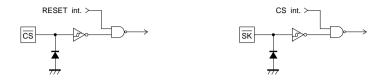

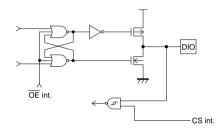

## Input circuits

# Output circuits

# ●Electrical characteristics (unless otherwise noted, Ta = -20 to +85°C, Vcc = 5V ± 10%)

| Parameter                         | Symbol | Min.         | Тур. | Max.         | Unit | Conditions                                                | Measurement<br>Circuit |

|-----------------------------------|--------|--------------|------|--------------|------|-----------------------------------------------------------|------------------------|

| Input low level voltage           | VIL    | _            | _    | 0.2 ×<br>Vcc | V    | CS, SK, DIO pin                                           | _                      |

| Input high level voltage          | VIH    | 0.8 ×<br>Vcc | _    | _            | V    | CS, SK, DIO pin                                           | _                      |

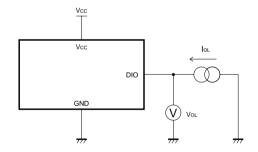

| Output low level voltage          | Vol    | 0            | _    | 0.4          | V    | IoL = 2.1mA                                               | Fig.1                  |

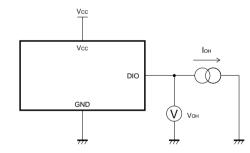

| Output high level voltage         | Vон    | Vcc –<br>0.4 | _    | Vcc          | V    | Iон = - 0.4mA                                             | Fig.6                  |

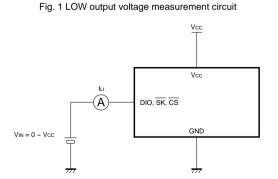

| Input leakage current             | lu     | <b>–</b> 1   | _    | 1            | μΑ   | Vin = 0 ~ Vcc                                             | Fig.3                  |

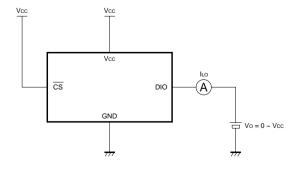

| Output leakage current            | ILO    | <b>–</b> 1   | _    | 1            | μΑ   | Vout = 0 ~ Vcc, $\overline{CS}$ = Vcc                     | Fig.4                  |

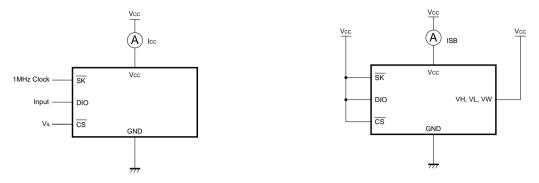

| Operating current consumption     | Icc    | _            | _    | 3            | mA   | f = 1MHz, tE / W = 10ms (WRITE)                           | Fig.5                  |

| Standby current                   | IsB    | _            | _    | 200          | μА   | $\overline{CS}$ , $\overline{SK}$ , DIO, VH, VL, VW = Vcc | Fig.6                  |

| SK frequency                      | fsк    | _            | _    | 1            | MHz  |                                                           | _                      |

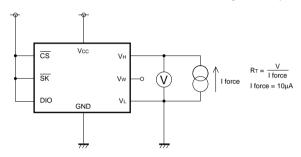

| Total resistance                  | Rт     | _            | 100  | _            | kΩ   | I <sub>f</sub> = 10μA                                     | Fig.7                  |

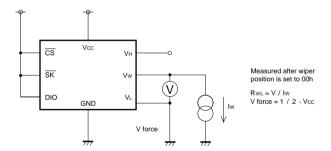

| Wiper resistance                  | Rw     | _            | 0.5  | 1            | kΩ   | Iw = - 1mA                                                | Fig.8                  |

| Resistance potential on High side | VvH    | 0            | _    | Vcc          | V    |                                                           | _                      |

| Resistance potential on Low side  | Vvl    | 0            |      | Vcc          | V    |                                                           |                        |

(unless otherwise noted,  $Ta = -20 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 3V \pm 10\%$ )

| Parameter                         | Symbol | Min.         | Тур. | Max.         | Unit | Conditions                                                | Measurement<br>Circuit |

|-----------------------------------|--------|--------------|------|--------------|------|-----------------------------------------------------------|------------------------|

| Input low level voltage           | VIL    | _            | _    | 0.2 ×<br>Vcc | V    | CS, SK, DIO pin                                           | _                      |

| Input high level voltage          | ViH    | 0.8 ×<br>Vcc | _    | _            | V    | CS, SK, DIO pin                                           | _                      |

| Output low level voltage          | Vol    | 0            | _    | 0.4          | V    | IoL = 100μA                                               | Fig.1                  |

| Output high level voltage         | Vон    | Vcc -<br>0.4 | _    | Vcc          | V    | Іон = — 100µА                                             | Fig.6                  |

| Input leakage current             | ILI    | - 1          | _    | 1            | μΑ   | Vin = 0 ~ Vcc                                             | Fig.3                  |

| Output leakage current            | ILO    | - 1          | _    | 1            | μΑ   | Vout = 0 ~ Vcc, $\overline{CS}$ = Vcc                     | Fig.4                  |

| Operating current consumption     | Icc    | _            | _    | 2            | mA   | f = 1MHz, tE / W = 10ms (WRITE)                           | Fig.5                  |

| Standby current                   | Isв    | _            | _    | 100          | μΑ   | $\overline{CS}$ , $\overline{SK}$ , DIO, VH, VL, VW = Vcc | Fig.6                  |

| SK frequency                      | fsк    | _            | _    | 500          | kHz  |                                                           |                        |

| Total resistance                  | Rт     | _            | 100  | _            | kΩ   | I <sub>f</sub> = 10μA                                     | Fig.7                  |

| Wiper resistance                  | Rw     | _            | 1    | 2            | kΩ   | Iw = - 500μA                                              | Fig.8                  |

| Resistance potential on High side | Vvн    | 0            | _    | Vcc          | V    |                                                           | _                      |

| Resistance potential on Low side  | VvL    | 0            | _    | Vcc          | V    |                                                           | _                      |

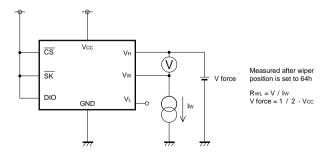

## Measurement circuits

Data set when output is LOW

Fig. 3 Input leakage current measurement circuit

Data set when output is HIGH

Fig. 2 HIGH output voltage measurement circuit

Fig. 4 Output leakage current measurement circuit

Fig. 5 Current consumption measurement circuit

Fig. 6 Standby current measurement circuit

Fig. 7 Total resistance measurement circuit

Fig. 8 Wiper resistance measurement circuit on Low side

Fig. 9 Wiper resistance measurement circuit on High side

#### Command modes

| Command                        | Start bit | Operation code | Address | Data      | Operation           |                                       |

|--------------------------------|-----------|----------------|---------|-----------|---------------------|---------------------------------------|

| Write enabled                  | WEN       | 1010           | 0011    | XXXXXXX   | _                   | _                                     |

| Write disabled                 | WDS       | 1010           | 0000    | XXXXXXX   | _                   | _                                     |

| Wiper counter data output      | WCR       | 1010           | 1011    | XXXXXXX   | D8 - D14 X          | Wiper counter → output                |

| Wiper counter data input       | WCW       | 1010           | 0110    | XXXXXXX   | XXXXXXXX D8 - D14 X | Input → wiper counter                 |

| Data read                      | DRD       | 1010           | 1000    | A0 - A6 X | D0 - D15            | Memory → output                       |

| Data write                     | DWR       | 1010           | 0100    | A0 - A6 X | D0 - D15            | Input → memory                        |

| Transmission memory data read  | TDWR      | 1010           | 1001    | A0 - A6 X | _                   | Memory → wiper counter                |

| Transmission memory data write | TWDW      | 1010           | 0101    | A0 - A6 X | _                   | Wiper counter → memory                |

| Increment / decrement wiper    | INC/DEC   | 1010           | 1111    |           | _                   | Wiper counter $\rightarrow$ INC / DEC |

X: Don't Care (data may be either 0 or 1)

## OAuto recall function (ARF)

• After the power supply is turned on, the data for address 00h is automatically loaded and the wiper position set. At this point, if the data for address 00h is larger than 64h, the wiper position is set to 32h. Since the wiper position is set using seven bits, the eighth bit may be set to any value. This function is carried out 10ms after the power supply is turned on, and subsequently the IC enters the standby state.

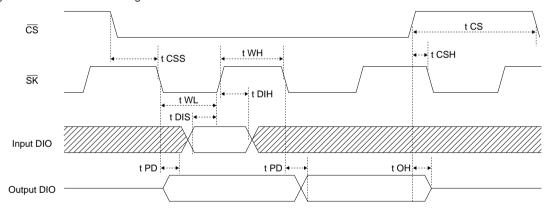

# •Operation timing characteristics (unless otherwise noted, Ta = -20 to +85°C, $Vcc = 5V \pm 10$ %)

| Parameter                                           | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|--------|------|------|------|------|

| CS setup time                                       | tcss   | 200  | _    | _    | ns   |

| CS hold time                                        | tcsH   | 0    | _    | _    | ns   |

| Data setup time                                     | tois   | 150  | _    | _    | ns   |

| Data hold time                                      | tdiH   | 150  | _    | _    | ns   |

| DO rise delay time                                  | tPD1   |      | _    | 350  | ns   |

| DO fall delay time                                  | tPD0   | _    | _    | 350  | ns   |

| Self-timed programming cycle                        | tE / W | _    | _    | 10   | ms   |

| CS minimum HIGH time                                | tcs    | 1    | _    | _    | μs   |

| Time during which READY / BUSY display is effective | tsv    | -    | _    | 1    | μs   |

| Time that DO is HIGH-Z from (CS)                    | tон    | 0    | _    | 400  | ns   |

| Data clock HIGH time                                | twн    | 450  | _    | _    | ns   |

| Data clock LOW time                                 | twL    | 450  | _    | _    | ns   |

| Resistance value stabilization time                 | taw    | _    | _    | 500  | μs   |

(unless otherwise noted,  $Ta = -20 \text{ to} + 85^{\circ}\text{C}$ ,  $Vcc = 5V \pm 10\%$ )

| Parameter                                           | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------|--------|------|------|------|------|

| CS setup time                                       | tcss   | 400  | _    | _    | ns   |

| CS hold time                                        | tcsH   | 0    | _    | _    | ns   |

| Data setup time                                     | tois   | 300  | _    | _    | ns   |

| Data hold time                                      | tdiH   | 300  | _    | _    | ns   |

| DO rise delay time                                  | tPD1   |      | _    | 700  | ns   |

| DO fall delay time                                  | tPD0   | -    | _    | 700  | ns   |

| Self-timed programming cycle                        | tE/W   | _    | _    | 15   | ms   |

| CS minimum HIGH time                                | tcs    | 2    | _    | _    | μs   |

| Time during which READY / BUSY display is effective | tsv    | _    | _    | 2    | μs   |

| Time that DO is HIGH-Z from (CS)                    | tон    | 0    | _    | 800  | ns   |

| Data clock HIGH time                                | twн    | 900  | _    | _    | ns   |

| Data clock LOW time                                 | twL    | 900  | _    | _    | ns   |

| Resistance value stabilization time                 | taw    | I    | _    | 1000 | μs   |

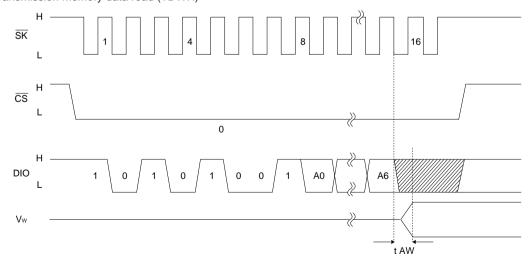

## Synchronous data I / O timing

Fig. 10 Synchronous data I / O timing

- $\bigcirc$ Reading of input data is done at the rising edge of  $\overline{SK}$ .

- $\bigcirc$ Output of data is synchronized to the falling edge of  $\overline{SK}$ .

- $\bigcirc \text{Between commands, CS}$  should be set to HIGH for longer than tCS.

If  $\overline{\text{CS}}$  remains LOW, the next command cannot be received.

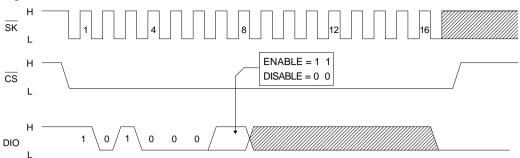

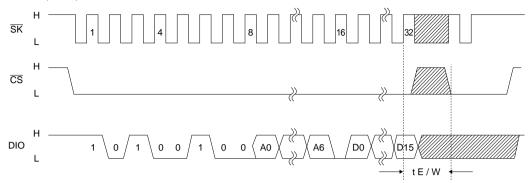

## Timing charts

(1) Writing enabled / disabled

Fig. 11 Writing enabled and disabled

- 1) When the power supply is turned on, the writing recognition latch is reset in the same way as when the write disable command is executed. The write enable command must be input before the write command is input.

- 2) Once the write enable command has been set, it remains effective until either the write disable command is input, or the power supply is turned off.

- 3) No clocks longer than 16 clocks are required. These will be ignored by the IC if input. The command is received following the clock input for the eight bits of the address subsequent to input of the operation code. The contents of the address are not related to either of these commands, however, and will be ignored.

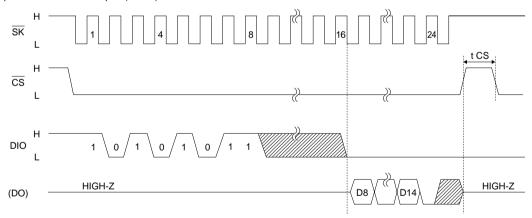

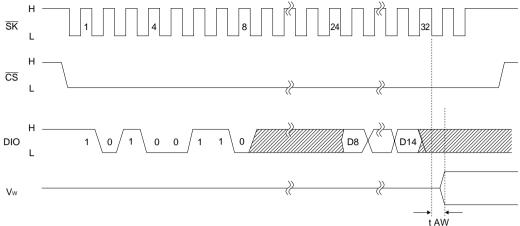

## (2) Wiper counter data output (WCR)

Fig. 12 Wiper counter data output

1) When the Wiper Counter Data Output (WCR) command is received, seven bits of the data at the current wiper position are output to D8, D9, D10, ..., D14, in sequential order. If a clock of longer than 24 clocks is input, indefinite data may be output. (For the DIO output, the data may change at the tPD0 and tPD1 time delays, in response to the internal circuit delay starting from the falling edge of the  $\overline{SK}$  signal. During the tPD0 and tPD1 time internals, data should be loaded after the tPD time has been assured, in case the previous data is indefinite. Refer to Fig. 10, Synchronous data I / O timing.)

## (3) Wiper counter data input (WCW)

Fig. 13 Wiper counter data input

1) This command is used for direct input of wiper position data. Since the data is 7-bit data sequentially input in the order of D8, D9, D10, ..., D14, it determines one wiper position among 100 taps. Since no address exists at this point, the address is ignored. The resistance stabilizes after an interval of tAW from the rise of the 32nd clock.

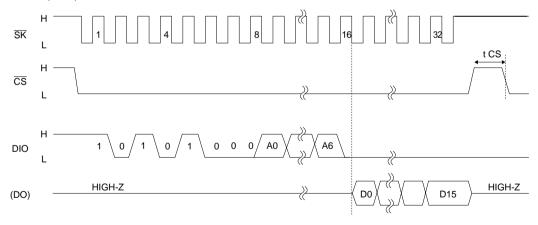

## (4) Data read (DRD)

Fig. 14 Data read

- 1) When the data read (DRD) command is received, data is output from the addresses specified by A1 and A0.

- 2) Output is synchronized to the fall of  $\overline{SK}$ , in order of D0, D1, D2, ..., D15, at the fall of the 16th clock. After 32 clocks have elapsed, the D15 data is retained even if other clocks are input.

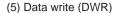

Memory ICs BU9831 / BU9831F

Fig. 15 Data write

- 1) This command stores the input data in the address specified by A0 to A6.

- 2)  $\overline{\text{CS}}$  must be LOW during the write mode input, but once writing begins,  $\overline{\text{CS}}$  may be either HIGH or LOW.

- 3) The internal timer circuit in the IC begins to function after the rising edge of the  $\overline{SK}$  at which the last data D0 was read, and data is written to memory cells during the time period tE / W. The process is terminated automatically.

- At this point, the SK input during the tE / W time period may be either HIGH or LOW.

- 4) The time period between input of this command and the automatic termination of the writing of data is the time during which data is written to the internal non-volatile memory, so commands input during this interval will not be accepted. The maximum time interval must be within tE / W.

- 5) After the write command has been input, if  $\overline{CS}$  is set to LOW after having been set to HIGH, command reception is enabled following termination of the automatic data writing. Data can then be received from  $\overline{SK}$  and DIO. If  $\overline{CS}$  is left at LOW following input of the command, however, without being set to HIGH, input of the command is canceled.

## (6) Transmission memory data read (TDWR)

Fig. 16 Transmission memory data read

1) This command transmits the data from the addresses specified by A0 to A6 to the wiper counter. The wiper moves to the position indicated by the seven bits D8 to D14 of the specified address, and the resistance value stabilizes after the tAW time period starting with the fall of the 15th clock. Data subsequent to the 16th clock is ignored.

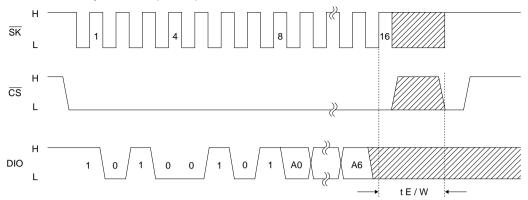

(7) Transmission memory data write (TWDW)

Fig. 17 Transmission memory data write

- 1) This command transmits the wiper position data to the addresses specified by A0 to A6. The data from the seven bits D8 to D14 of the specified address are stored in the memory during the time tE / W, starting from the rise of the 16th clock.

- 2) Writing is done to the internal non-volatile memory during the time when this command is input and automatic writing of the data is completed. Commands input during this time will not be accepted. The maximum time for this period must be within tE / W.

- 3) After the write command has been input, if  $\overline{CS}$  is set to LOW after having been set to HIGH, command reception is enabled following termination of the automatic data writing. Data can then be received from  $\overline{SK}$  and DIO. If  $\overline{CS}$  is left at LOW following input of the command, however, without being set to HIGH, input of the command is canceled.

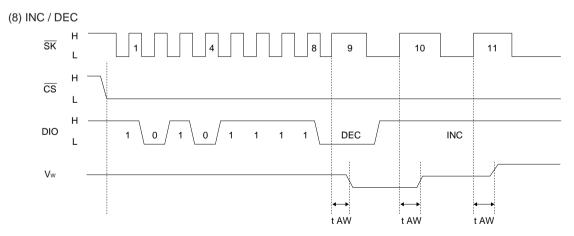

Fig. 18 Increment / decrement wiper

- 1) The wiper position is incremented or decremented starting from the next clock following input of the INC / DEC command, based on the status of the INC pin.

- DIO = H: Incremented. The wiper position moves from the VL to the VH side by 1 tap per clock.

- DIO = L: Decremented. The wiper position moves from the VH to the VL side by 1 tap per clock.

- 2) The tap is moved at each rise of the clock, until  $\overline{\text{CS}}$  is set to HIGH.

When the tap is farthest to the VH side, incrementing is ignored.

In the same way, when the tap is farthest to the VL side, decrementing is ignored.

Memory ICs BU9831 / BU9831F

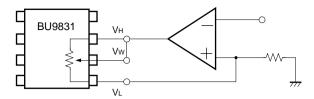

#### Application examples

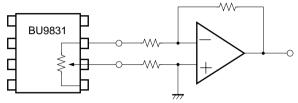

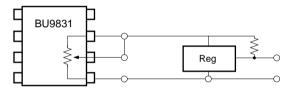

Fig. 19 Operation amplifier gain adjustment

Fine adjustment of the input offset voltage can be done in order to suppress the error voltage of the output based on the input voltage.

Fig. 20 Adjustment of the operation amplifier offset voltage

Output current can be adjusted by adjusting the output load.

Fig. 21 Variable output adjustment of regulator

## Operation notes

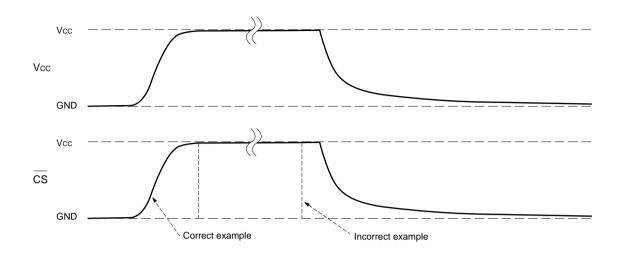

- (1) When turning the power supply on and off

- 1) When turning the power supply on and off,  $\overline{CS}$  should be set to HIGH (= Vcc).

- 2) When  $\overline{CS}$  is LOW, the BU9831 is active, meaning that input can be received. If the power supply is turned on in this state, noise and other factors can cause malfunctioning and erroneous writing. To prevent this, when turning the power supply on, make sure that  $\overline{CS}$  is HIGH (= Vcc).

(Example of proper operation) The  $\overline{\text{CS}}$  pin is pulled up to Vcc.

After turning the power supply off, wait at least 10ms before turning it on again.

If the power supply is turned on without observing this condition, please be aware that there may be times when the circuits in the IC are not reset.

(Example of incorrect operation) The CS pin is LOW when the power supply is turned on or off.

In this case,  $\overline{\text{CS}}$  is normally LOW, and the EEPROM may cause malfunctioning or erroneous writing because of noise.

\* Be aware that the case shown in this example may occur even if the CS input is HIGH-Z.

## (2) Noise countermeasures

## 1) SK noise

If there is noise in the rise of the  $\overline{SK}$  clock input, the system may recognize more clocks than were actually input, and malfunctioning may occur because of offset bits.

## 2) Vcc noise

Noise and surges in the power supply line can cause malfunctioning. To eliminate these factors, we recommend installing a bypass capacitor between the power supply and the ground.

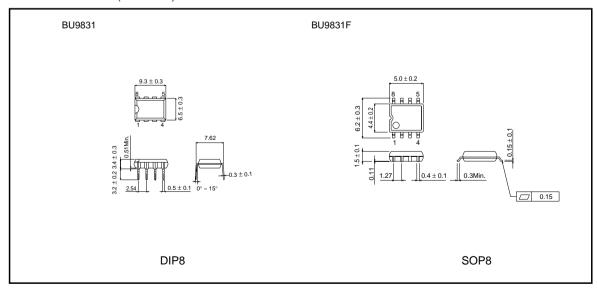

## External dimension (Units: mm)