# Servo signal processor for CD use BU9321BKS

The BU9321BKS is a servo signal processor for CD players that incorporates a double-speed, no-adjustment PLL, program servo, and signal processing block on one chip. It operates off a low power supply voltage, and has low power consumption.

## Applications

Portable CD players, radio cassette players, and minicomponent systems.

### Features

- PLL on chip. Bit clock extraction possible with just a few external components. EFM data modulation is possible.

- Frame synchronizing signal detection and protection.

- Servo filters for focus, tracking, and sled are on chip. Characteristics can be controlled using commands from the controller.

- 4) Sub-code serial output pin provided.

- 5) Output pins for both P-code and Q-code.

- CLV sequencer automatically determines the CLV mode.

- Track jump sequencer on chip. Possible to jump any number of tracks.

- 8) De-interleave function, and 2-level error detection, correction and flag processing for C1 and C2.

- The signal to the DAC is output by the MSB first 2'SCOMP serial out, and offset circuit ON and OFF can be controlled for CD-ROM compatibility.

- 10) 16 kilobits of on-chip SRAM absorb ±4 frames of jitter.

- 11) Double-speed playback is possible.

### ● Absolute maximum ratings (Ta = 25°C)

| Parameter             | Symbol          | Limits          | Unit |

|-----------------------|-----------------|-----------------|------|

| Power supply voltage  | V <sub>DD</sub> | 4.5             | V    |

| Power dissipation     | Pd              | 400 *           | mW   |

| Operating temperature | Topr            | <b>−25~+75</b>  | °C   |

| Storage temperature   | Tstg            | <b>−55∼+125</b> | °C   |

#### • Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol          | Min. | Тур. | Max. | Unit |

|----------------------|-----------------|------|------|------|------|

| Power supply voltage | V <sub>DD</sub> | 2.6  | 1    | 3.5  | V    |

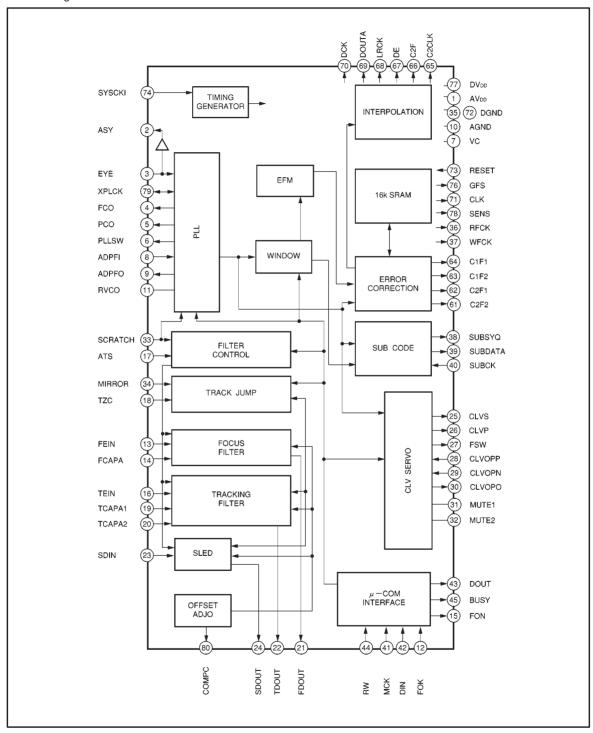

## Block diagram

Optical disc ICs BU9321BKS

## Pin descriptions

| Pin No. | Pin name | Analog/digital | 1/0 | Function                                             | I/O circuit |

|---------|----------|----------------|-----|------------------------------------------------------|-------------|

| 1       | AVDD     | _              | _   | Analog power supply                                  | _           |

| 2       | ASY      | Digital        | 0   | EFM signal slice level control output                | 4           |

| 3       | EYE      | Digital        | I   | EFM signal input pin from the RF amplifier           | 1           |

| 4       | FCO      | Analog         | 0   | PLL frequency comparator output (R=15Ω)              | 8           |

| 5       | PCO      | Analog         | 0   | PLL phase comparison error voltage output (R=5Ω)     | 8           |

| 6       | PLLSW    | Analog         | 0   | PLL time constant switch pin                         | 6           |

| 7       | VC       | Analog         | I   | Bias voltage input                                   | 7           |

| 8       | ADPFI    | Analog         | 1   | PLL addition amplifier inversion signal              | 7           |

| 9       | ADPFO    | Analog         | 0   | PLL addition amplifier output                        | 7           |

| 10      | AGND     | _              | ı   | Analog ground                                        | _           |

| 11      | RVCO     | Analog         | 1   | PLL VCO oscillator frequency adjustment              | 7           |

| 12      | FOK      | Digital        | ı   | Focus OK signal input                                | 1           |

| 13      | FEIN     | Analog         | ı   | Focus error signal input                             | 7           |

| 14      | FCAPA    | Analog         | 0   | For connection of capacitor for focus servo filter   | 7           |

| 15      | FON      | Digital        | 0   | Focus on signal output                               | 2           |

| 16      | TEIN     | Analog         | 1   | Tracking error signal input                          | 7           |

| 17      | ATS      | Analog         |     | Anti-shock detector window comparator input          | 7           |

| 18      | TZC      | Analog         | 1   | Tracking/zero cross comparator input                 | 7           |

| 19      | TCAPA1   | Analog         | 0   | For connection of switch 1 for tracking servo filter | 7           |

| 20      | TCAPA2   | Analog         | 0   | For connection of switch 2 for tracking servo filter | 7           |

| 21      | FDOUT    | Analog         | 0   | Focus drive output                                   | 7           |

| 22      | TDOUT    | Analog         | 0   | Tracking drive output                                | 7           |

| 23      | SDIN     | Analog         | ı   | Sled amplifier input                                 | 7           |

| 24      | SDOUT    | Analog         | 0   | Sled drive output                                    | 7           |

| 25      | CLVS     | Analog         | 0   | CLV speed control output                             | 7           |

| 26      | CLVP     | Analog         | 0   | CLV phase control output                             | 7           |

| 27      | FSW      | Analog         | 0   | CLV filter time constant switch                      | 6           |

| 28      | CLVOPP   | Analog         | ı   | CLV addition amplifier non-inverted input            | 7           |

| 29      | CLVOPN   | Analog         | 1   | CLV addition amplifier inverted input                | 7           |

| 30      | CLVOPO   | Analog         | 0   | CLV addition amplifier output                        | 7           |

| 31      | MUTE1    | Analog         | 1/0 | CLV mute switch 1                                    | 7           |

| 32      | MUTE2    | Analog         | 1/0 | CLV mute switch 2                                    | 7           |

| 33      | SCRATCH  | Digital        | ı   | Scratch signal input                                 | 1           |

| 34      | MIRROR   | Digital        | ı   | Mirror signal input                                  | 1           |

| 35      | DGND     | _              | _   | Digital ground                                       | _           |

| 36      | RFCK     | Digital        | 0   | Read frame clock output                              | 2           |

| 37      | WFCK     | Digital        | 0   | Write frame clock output                             | 2           |

| 38      | SUBSYQ   | Digital        | 0   | Sub-code sync signal S1 output                       | 2           |

| 39      | SUBDATA  | Digital        | 0   | Sub-code serial output                               | 2           |

| 40      | SUBCK    | Digital        | 1   | Clock input for sub-code read                        | 1           |

| Pin No. | Pin name         | Analog/digital | 1/0 | Function                                                              | I/O circuit |

|---------|------------------|----------------|-----|-----------------------------------------------------------------------|-------------|

| 41      | мск              | Digital        | 1   | Clock input for command read and sub-code read                        | 1           |

| 42      | DIN              | Digital        | I   | Command serial input from microprocessor                              | 1           |

| 43      | DOUT             | Digital        | 0   | Sub-Q code serial output                                              | 4           |

| 44      | RW               | Digital        | 0   | Read/write switch input                                               | 1           |

| 45      | BUSY             | Digital        | 0   | Busy output ("L" during track jump)                                   | 2           |

| 46      | N.C.             | _              | _   | _                                                                     | _           |

| 47      | N.C.             | _              | _   | _                                                                     | _           |

| 48      | N.C.             | _              | _   | _                                                                     | _           |

| 49      | N.C.             | _              | _   | _                                                                     | _           |

| 50      | N.C.             | _              | _   | _                                                                     | _           |

| 51      | N.C.             | _              | _   | _                                                                     | _           |

| 52      | N.C.             | _              | _   | _                                                                     | _           |

| 53      | N.C.             | _              |     | _                                                                     | _           |

| 54      | N.C.             | _              | _   | _                                                                     | _           |

| 55      | N.C.             | _              | _   | _                                                                     | _           |

| 56      | N.C.             | _              | _   | _                                                                     | _           |

| 57      | N.C.             | _              |     | _                                                                     | _           |

| 58      | N.C.             | _              | _   | _                                                                     | _           |

| 59      | N.C.             | _              | _   | _                                                                     | _           |

| 60      | N.C.             | _              | _   | _                                                                     | _           |

| 61      | C2F2             | Digital        | 0   | C22 correction flag output                                            | 2           |

| 62      | C2F1             | Digital        | 0   | C21 correction flag output                                            | 2           |

| 63      | C1F2             | Digital        | 0   | C12 correction flag output                                            | 2           |

| 64      | C1F1             | Digital        | 0   | C11 correction flag output                                            | 2           |

| 65      | C2CLK            | Digital        | 0   | Strobe signal (f=176.4kHz)                                            | 2           |

| 66      | C2F              | Digital        | 0   | Correction status output                                              | 2           |

| 67      | DE               | Digital        | 0   | Strobe signal (f=88.2kHz)                                             | 2           |

| 68      | LRCK             | Digital        | 0   | Strobe signal (f=44.1kHz)                                             | 2           |

| 69      | DOUTA            | Digital        | 0   | Audio data output (2'SCOMP)                                           | 2           |

| 70      | DOCK             | Digital        | 0   | Bit clock for DOUT (f=2.1168MHz)                                      | 2           |

| 71      | CLK              | Digital        | 0   | Clock output (select from four types using &hE4 command)              | 2           |

| 72      | DGND2            | _              | _   | Digital ground                                                        | _           |

| 73      | RESET            | Digital        | ı   | Internal circuit reset                                                | 3           |

| 74      | SYSCKI           | Digital        | I   | System clock input (f=16.93MHz)                                       | 1           |

| 75      | N.C.             | _              | _   | _                                                                     | _           |

| 76      | GFS              | Digital        | 0   | GFS monitor output (select from four types using &hE4 command)        | 2           |

| 77      | DV <sub>DD</sub> | _              | _   | Digital power supply                                                  | _           |

| 78      | SENS             | Digital        | 0   | Monitor output pin (&hE4 command setting or offset comparator output) | 2           |

| 79      | XPLCK            | Digital        | 1/0 | PLL playback clock output or external PLL playback clock input        | 5           |

| 80      | COMPC            | Analog         | 0   | Offset adjustment smoothing (analog offset measurement is possible)   | 7           |

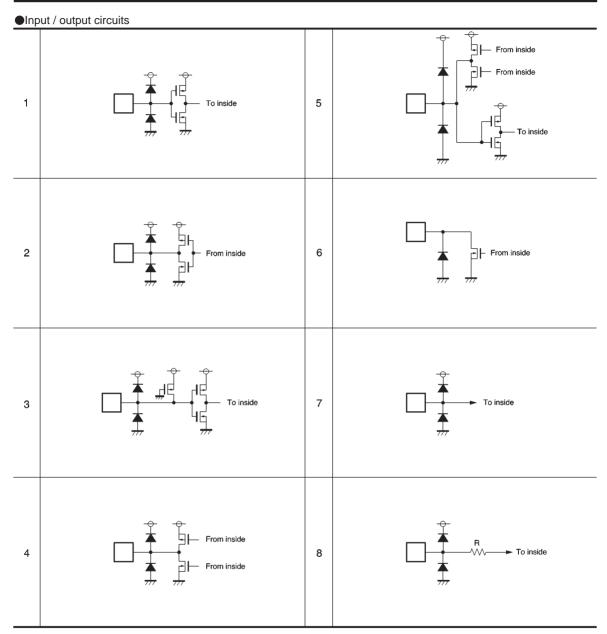

#### Pin types

\* 1 CMOS inputs.

EYE (3pin), FOK (12pin), SCRATCH (33pin), MIRROR (34pin), SUBCK (40pin), MCK (41pin), DIN (42pin), RW (44pin), SYSCKI (74pin)

- \* 2 Inputs with pullups.

- RESET (73pin)

FON (15pin), RFCK (36pin), WFCK (37pin), SUBSYQ (38pin), SUBDATA (39pin), BUSY (45pin), C2F2 (61pin), C2F1 (62pin), C1F2 (63pin), C1F1 (64pin), C2CLK (65pin), C2F (66pin), DE (67pin), LRCK (68pin), DOUTA (69pin), DOCK (70pin), CLK (71pin), GFS (76pin), SENS (78pin), XPLCK (79pin)

- \* 4 Tri-state outputs.

- ASY (2pin), DOUT (43pin)

- \* 5 Open drain.

PLLSW (6pin), FSW (27pin)

# •Electrical characteristics (digital system)

DC characteristics (unless otherwise noted, Ta = 25°C and  $V_{DD} = 2.6V$ )

| Pa           | arameter           | Symbol | Min. | Тур. | Max. | Unit | Conditions              | Applicable pin |

|--------------|--------------------|--------|------|------|------|------|-------------------------|----------------|

| Input        | High level voltage | Vін    | 1.9  | _    | _    | ٧    | lo=1mA                  | *1, 2          |

| voltage      | Low level voltage  | VIL    | _    | _    | 0.5  | ٧    | Io=-1mA                 | *1, 2          |

| Reset pin    | input current      | lıн    | 15   | 40   | 100  | μA   | V <sub>IN</sub> =0V     | *2             |

| Input curr   | ent                | lu     | _    | _    | ±5   | μΑ   | V <sub>IN</sub> =0~2.6V | *1             |

| Output       | High level voltage | Vон    | 2.2  | _    | _    | ٧    | _                       | *3, 4          |

| voltage      | Low level voltage  | Vol    | _    | _    | 0.5  | ٧    | _                       | *3, 4, 5       |

| Tri-state or | utput leak current | Іохн   | _    | _    | ±5   | μV   | Vo=0~2.6V               | *4, 5          |

Optical disc ICs BU9321BKS

## Electrical characteristics (analog system)

(unless otherwise noted, Ta =  $25^{\circ}$ C,  $V_{DD}$  = 2.6V,  $R_{L}$  =  $10k\Omega$  and  $V_{C}$  reference)

| Parameter                               | Symbol             | Min. | Тур. | Max.     | Unit | Conditions                       | Setting command  |

|-----------------------------------------|--------------------|------|------|----------|------|----------------------------------|------------------|

| Quiescent current                       | la                 | 3.0  | 6.5  | 10       | mA   | _                                | _                |

| ⟨Focus servo⟩                           |                    |      |      |          |      |                                  |                  |

| DC voltage gain                         | GFD1               | 23   | 26   | 29       | dB   | IN=1Hz, 20mV <sub>P-P</sub>      | 10×F, 1462       |

| AC voltage gain 1                       | GFDF1              | 3    | 6    | 9        | dB   | IN=1kHz, 100mV <sub>P-P</sub>    | 10×F, 1462       |

| AC voltage gain 2                       | GFDF2              | -4   | -1   | 2        | dB   | IN=300Hz, 100mV <sub>P-P</sub>   | 10×F, 1462       |

| Maximum output voltage                  | V <sub>FD1</sub>   | 1.0  | _    | _        | V    | _                                | _                |

| Minimum output voltage                  | V <sub>FD2</sub>   | _    | _    | -1.0     | V    | _                                | _                |

| Offset voltage                          | VFOF               | -600 | _    | 600      | mV   | _                                | 10×F, 1462       |

| ⟨Tracking servo⟩                        | 1                  |      |      |          |      |                                  |                  |

| DC voltage gain                         | Gт <sub>D1</sub>   | 22   | 25   | 28       | dB   | IN=1Hz, 20mV <sub>P-P</sub>      | 10D×, 1159, 1207 |

| AC voltage gain 1                       | GTDF1              | 4    | 7    | 10       | dB   | IN=1kHz, 100mV <sub>P-P</sub>    | 10D×, 1159, 1207 |

| AC voltage gain 2                       | GTDF2              | -3   | 0    | 3        | dB   | IN=300Hz, 100mV <sub>P-P</sub>   | 10D×, 1159, 1207 |

| AC voltage gain 3                       | GтDF3              | 25   | 28   | 31       | dB   | IN=1kHz, 20mV <sub>P-P</sub> *1  | 10D×, 1159, 1207 |

| AC voltage gain 4                       | GTDF4              | 20   | 23   | 26       | dB   | IN=300Hz, 20mV <sub>P-P</sub> *1 | 10D×, 1159, 1207 |

| Maximum output voltage                  | V <sub>TD1</sub>   | 1.0  | _    | _        | V    | _                                | _                |

| Minimum output voltage                  | V <sub>TD2</sub>   | _    | _    | -1.0     | V    | _                                | _                |

| Offset voltage                          | VTOF               | -530 | _    | 530      | mV   | _                                | 10D×, 1159, 1207 |

| Jump output voltage                     | V <sub>JP1</sub>   | 1.0  | 1.2  | _        | V    | _                                | 13×F             |

| Jump output voltage                     | V <sub>JP2</sub>   | _    | -1.2 | -1.0     | V    | _                                | 13F×             |

| ATS threshold voltage 1                 | V <sub>AT\$1</sub> | 10   | _    | 50       | mV   | _                                | _                |

| ATS threshold voltage 2                 | V <sub>ATS2</sub>  | -50  | _    | -10      | mV   | _                                | _                |

| TZC threshold voltage                   | VTZC               | -50  | _    | 50       | mV   | _                                | _                |

| ON resistance between TCAPA1 and TCAPA2 | RTON               | _    | 50   | 150      | Ω    | I=0.1mA                          | 1EX1             |

| ⟨Sled servo⟩                            | 1                  |      |      | '        |      |                                  |                  |

| DC voltage gain                         | G <sub>SD1</sub>   | 23   | 26   | 29       | dB   | IN=100Hz, 20mV <sub>P-P</sub>    | 124×             |

| Maximum output voltage                  | V <sub>SD1</sub>   | 1.0  | _    | _        | V    | _                                | _                |

| Minimum output voltage                  | V <sub>SD2</sub>   | _    | _    | -1.0     | V    | _                                | _                |

| Offset voltage                          | Vsor               | -200 | 0    | 200      | mV   | _                                | 124×             |

| Kick output voltage 1                   | V <sub>KC1</sub>   | 1.0  | 1.2  | <u> </u> | V    | _                                | 18×F             |

| Kick output voltage 2                   | V <sub>KC2</sub>   | _    | -1.2 | -1.0     | V    | _                                | 18F×             |

<sup>\$1</sup> AC gain for gain amplifier (100k  $\Omega$  between TCAPA1 and TCAPA2).

ONot designed for radiation resistance.

| Parameter                 | Symbol            | Min.           | Тур. | Max. | Unit | Conditions      | Setting command |

|---------------------------|-------------------|----------------|------|------|------|-----------------|-----------------|

| ⟨CLV amplifier⟩           |                   |                |      |      |      |                 |                 |

| Maximum output voltage    | V <sub>OPD1</sub> | 1.0            | _    | _    | V    | _               | _               |

| Minimum output voltage    | Vopd2             | _              | _    | 1.0  | V    | _               | _               |

| Input offset voltage      | Vopof             | <del>-15</del> | 0    | 15   | mV   | _               | _               |

| ⟨CLV mute switch⟩         |                   |                |      |      |      |                 |                 |

| ON resistance             | Ron               | _              | 260  | 800  | Ω    | I=1mA           | E0              |

| ⟨Offset adjustment block⟩ |                   |                |      |      |      |                 |                 |

| Offset variable range 1   | Δ VoF1            | ±620           | ±710 | _    | mV   | Focus, tracking |                 |

| Offset variable range 2   | ΔV0F2             | ±300           | ±390 | _    | mV   | Sled            | 124×            |

| ⟨PLL block⟩               | 1                 |                |      |      |      |                 |                 |

| VCO oscillator frequency  | fvco              | 13             | _    | 21   | MHz  | _               | _               |

$<sup>\</sup>pm 1$  AC gain for gain amplifier (100k  $\Omega$  between TCAPA1 and TCAPA2).

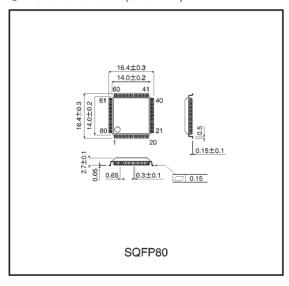

## External dimensions (Units: mm)

ONot designed for radiation resistance.