## Universal Balancing Techniques

IC op amps are widely accepted as a universal analog component. Although the circuit designs may vary, most devices are functionally interchangeable. However, offset voltage balancing remains a personality trait of the particular amplifier design. The techniques shown here allow offset voltage balancing without regard to the internal circuitry of the amplifier.

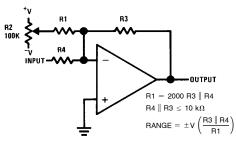

FIGURE 1. Offset Voltage Adjustment for Inverting Amplifiers Using 10 k $\Omega$  Source Resistance or Less

The circuit shown in Figure 1 is used to balance out the offset voltage of inverting amplifiers having a source resistance of 10 k $\Omega$  or less. A small current is injected into the summing node of the amplifier through R $_1$ . Since R $_1$  is 2000 times as large as the source resistance the voltage at the arm of the pot is attenuated by a factor of 2000 at the summing node. With the values given and  $\pm\,15V$  supplies the output may be zeroed for offset voltages up to  $\pm\,7.5$  mW.

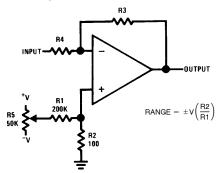

If the value of the source resistance is much larger than 10  $k\Omega,$  the resistance needed for  $R_1$  becomes too large. In this case it is much easier to balance out the offset by supplying a small voltage at the non-inverting input of the amplifier. Figure 2 shows such a scheme. Resistors  $R_1$  and  $R_2$  divide the voltage at the arm of the pot to supply a  $\pm 7.5$  mW adjustment range with  $\pm 15 V$  supplies.

National Semiconductor Linear Brief 9 August 1969

This adjustment method is also useful when the feedback element is a capacitor or non-linear device.

TL/H/8460-2

FIGURE 2. Offset Voltage Adjustment for Inverting Amplifiers Using Any Type of Feedback Element

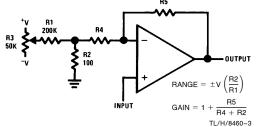

This technique of supplying a small voltage effectively in series with the input is also used for adjusting non-inverting amplifiers. As is shown in Figure 3, divider R<sub>1</sub>, R<sub>2</sub> reduces the voltage at the arm of the pot to  $\pm 7.5$  mW for offset adjustment. Since R<sub>2</sub> appears in series with R<sub>4</sub>, R<sub>2</sub> should be considered when calculating the gain. If R<sub>4</sub> is greater than 10 k $\Omega$  the error due to R<sub>2</sub> is less than 1%.

FIGURE 3. Offset Voltage Adjustment for Non-Inverting Amplifiers

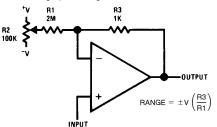

A voltage follower may be balanced by the technique shown in Figure 4. R<sub>1</sub> injects a current which produces a voltage drop across R3 to cancel the offset voltage. The addition of the adjustment resistors causes a gain error, increasing the gain by 0.05%. This small error usually causes no problem. The adjustment circuit essentially causes the offset voltage to appear at full output, rather than at low output levels, where it is a large percentage error.

TL/H/8460-4

FIGURE 4. Offset Voltage Adjustment for Voltage Followers

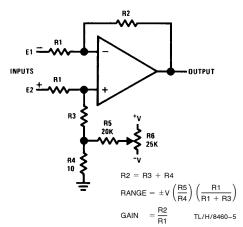

Differential amplifiers are somewhat more difficult to balance. The offset adjustment used for a differential amplifier can degrade the common mode rejection ratio. Figure 5 shows an adjustment circuit which has minimal effect on the common mode rejection. The voltage at the arm of the pot is divided by R4 and R5 to supply an offset correction of  $\pm 7.5$  mV.  $R_4$  and  $R_5$  are chosen such that the common mode rejection ratio is limited by the amplifer for values of  $R_3$  greater than 1 k $\Omega$ . If  $R_3$  is less than 1k the shunting of  $R_4$ by R<sub>5</sub> must be considered when choosing the value of R<sub>3</sub>.

FIGURE 5. Offset Voltage Adjustment for **Differential Amplifiers**

The techniques described for balancing offset voltage at the input of the amplifier offer two main advantages: First, they are universally applicable to all operational amplifiers and allow device interchangeability with no modifications to the balance circuitry. Second, they permit balancing without interfering with the internal circuitry of the amplifier. The electrical parameters of the amplifiers are tested and guaranteed without balancing. Although it doesn't usually happen, balancing could degrade performance.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation

1111 West Bardin Road

Arlington, TX 76017

Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 **National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408