# **CLC532 Evaluation Board**

Part Number CLC730028

August 1996

The 730028 (Rev. B) evaluation board is designed to aid in the evaluation and characterization of the CLC532, 2:1 analog multiplexer. Designed for very wide dynamic range systems, the CLC532 provides a wideband, unity gain, two-channel multiplexer with exceptional switching speeds. High channel isolation and fast pulse settling, make the CLC532 ideal for 12-bit ADC input-multiplexing applications. The CLC532 data sheet provides more detailed performance and applications information.

## **Basic Operation**

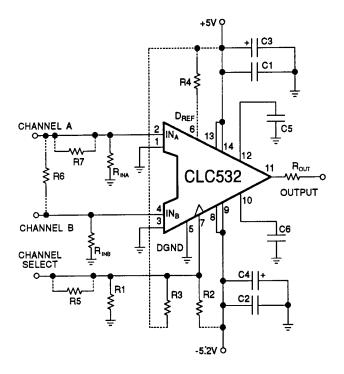

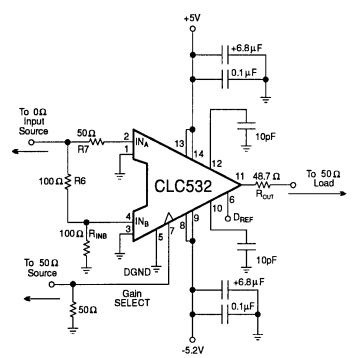

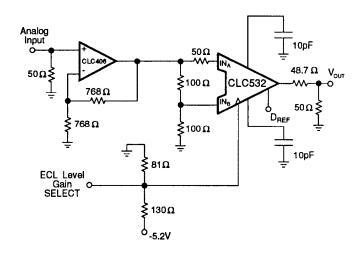

The complete circuit schematic of the 730028 evaluation board, including components for optional circuit configurations, is illustrated in Figure 1. The primary connections are shown with solid lines while the optional input and digital interface connections are shown with dashed lines.

Figure 1: CLC532 Evaluation Board Schematic

The CHANNEL A and B (pins 2 & 4) analog inputs of the CLC532 are buffered high-impedance pins. The two input termination resistors ( $R_{\text{INA}}$  &  $R_{\text{INB}}$ ) provide impedance

matching for the analog sources; a  $50\Omega$  environment is assumed. The closed-loop active output of the CLC532 provides a very low output impedance, typically  $1.2\Omega$ . For driving  $50\Omega$  systems, a  $48.7\Omega$  series output resistor (R<sub>OUT</sub>) will provide a close back matched impedance for  $50\Omega$  cables.

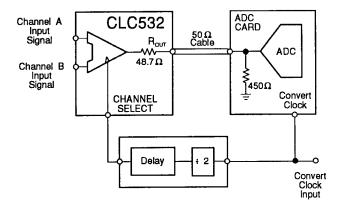

Figure 2: Driving Remote A/D Converter Inputs

Figure 2 illustrates the CLC532 evaluation board connections when driving the high-impedance input of a remote A/D converter. Most high quality, high-resolution, A/D converters employ a high-impedance input stage. This allows the CLC532 to operate with relatively high load resistors (>200 $\Omega$ ), greatly improving CLC532 distortion performance. When the CLC532 drives the A/D converter remotely from a separate board, a 48.7 $\Omega$  series output resistor prior to a 50 $\Omega$  connecting cable followed by a 450 $\Omega$  termination resistor at the input of the A/D converter, results in an effective 500 $\Omega$  load. When driving A/D converter inputs directly, a 500 $\Omega$  termination load is recommended with no series resistance.

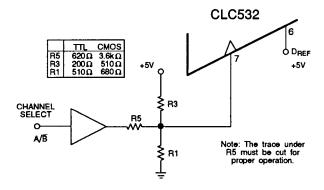

The CLC532 is capable of functioning with ECL, TTL, and CMOS logic families. Logic compatibility is controlled by  $D_{\text{REF}}$ . In normal operation,  $D_{\text{REF}}$  is left floating and the channel SELECT responds to ECL level signals. For TTL and CMOS level SELECT inputs,  $D_{\text{REF}}$  should be tied to +5V (the CLC532  $D_{\text{REF}}$  input is internally buffered through a 2300 $\Omega$  resistor). TTL and CMOS operation requires the use of a resistor input network for the channel SELECT. Without the input network, SELECT logic levels above 3V will cause internal junction saturation and slow switching speeds.

The CLC532 evaluation board is labeled for  $\pm 5$ V supplies. Normal ECL logic, and many A/D converters, employ a -5.2V  $V_{EE}$  supply rather than the indicated -5.0V supply. Either value is acceptable with negligible impact on performance.

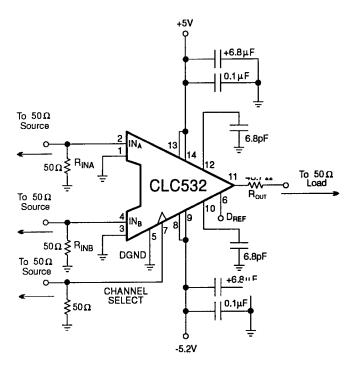

Figure 3: Basic Evaluation Schematic

Figure 3 illustrates the basic CLC532 multiplexer configuration. This configuration terminates both inputs with  $50\Omega$  and places a  $48.7\Omega$  back-terminating resistor (R<sub>OUT</sub>) at the output. With D<sub>REF</sub> left floating (ECL logic levels), the channel SELECT input is terminated with a  $50\Omega$  resistor to ground. This configuration assumes a  $50\Omega$ signal source provides the channel SELECT input. If standard ECL logic devices are available to drive the channel SELECT input directly, the evaluation board can be configured for standard Thevinen equivalent input terminations. A  $50\Omega$  termination resistor to a -2V bias supply can also be used. See Channel SELECT Logic Interfaces section. The overall gain seen at the matched load is 0.5V/V (-6dB). The compensation capacitors (C5 & C6) have been selected for a maximally-flat frequency response.

### **Compensation Capacitors**

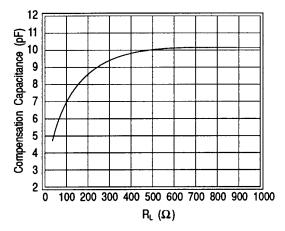

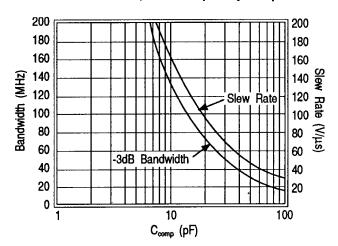

The compensation capacitors (C5 & C6) are used to *tune* the CLC532's frequency response for a given load. Figure 4 provides the compensation capacitor values for a maximally-flat frequency response. For symmetric slew rates, C5 and C6 should be equal. Figure 5 provides the -3dB bandwidth and slew rate vs. compensation capacitor values. The compensation capacitors can be used to limit the CLC532's noise-bandwidth. Given a single-pole frequency response, the noise bandwidth will be approximately ... (1.57)(f<sub>.3dB</sub>).

Figure 4: Maximally Flat Frequency Response

Figure 5: Slew Rate and Bandwidth vs. Compensation

### **Channel SELECT Logic Interfaces**

The CLC532 accepts channel SELECT inputs from a variety of logic families and sources. During evaluation, a signal generator is commonly used to drive the channel SELECT input. Accordingly, the evaluation board has been initially configured with a  $50\Omega$  SELECT input termination resistor to ground. When driving channel SELECT with actual ECL, TTL or CMOS logic gates, it will be necessary to add an appropriate input network. The 730028 evaluation board provides the necessary component locations for these networks, and Figure 6 illustrates the recommended TTL and CMOS configurations.

Figure 6. Recommended TTL/CMOS Interface Networks

The TTL and CMOS networks limit the maximum voltage swing at the channel SELECT input (pin 7) to less than 3.0V. Exceeding 3.0V will saturate the internal switching logic and cause slower switching speeds. If the input of the TTL or the CMOS networks is left floating, CHANNEL A will be selected. Use of the series resistor (R5) requires the cutting of the channel SELECT input trace below R5. This is easily accomplished on the back side of the evaluation board.

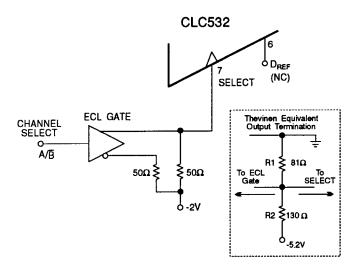

Driving the CLC532 with standard ECL logic gates requires one of the standard ECL terminations at the channel SELECT input. The network of Figure 7 provides a Thevinen equivalent termination of  $50\Omega$  to -2V. If a -2V bias supply is available, the standard  $50\Omega$  to -2V is certainly acceptable. Allowing the input to this network to float will select CHANNEL B.

Figure 7: Standard ECL Terminations

# **Signal Input Options**

The CLC532 evaluation board is capable of implementing a switched gain stage by driving CHANNEL B with an attenuated version of the CHANNEL A input signal. Illustrated in Figure 8, this circuit quickly switches between the full amplitude signal at CHANNEL A and the -6dB version of that signal at the input of CHANNEL B. This circuit provides a simple  $50\Omega$  termination for the channel SELECT input, although any of the previous circuits are equally acceptable. The series resistor at the input of CHANNEL A (R7) matches its source impedance to that of CHANNEL B (ie. R7=R6||R<sub>INB</sub>), generating equal poles from the parasitic input capacitances . This type of source impedance matching will also minimize input bias current induced offset errors.

Figure 8: Basic Gain Select Configuration

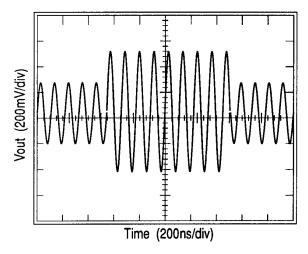

The switched-gain circuit of Figure 8 should be driven from a low output impedance, wideband, amplifier. Figure 9 uses a CLC406 at a gain of +2V/V to drive both inputs of the CLC532 switched gain circuit. With CHANNEL A selected, the signal at  $V_{\text{OUT}}$  will be a 0dB (unity gain) version of the input signal. With CHANNEL B selected, the CLC532 will produce a -6dB (0.5V/V) representation of the input signal at  $V_{\text{OUT}}$ . Figure 10 shows the signal at  $V_{\text{OUT}}$  using a 10MHz analog input signal, with the channel SELECT toggled at 500kHz. This approach can be easily extended to different gain settings.

Figure 9: CLC406 Driver for the Switched Gain Configuration

Figure 10: Gain Select Output with 500kHz Toggle Rate

## **Board Layout Suggestions**

The 730028 board has been designed to provide the maximum channel isolation and best fine-scale pulse-settling performance. Channel isolation requires good trace separation between the two inputs, while a ground plane placed between the inputs and the output will serve to isolate the unselected channel from the output.

On the CLC532 evaluation board, the ground connections for the analog input terminating resistors play a strong role in channel isolation performance. The input termination resistor ground connection for CHANNEL B has been placed immediately adjacent to its input SMA connector. The input termination resistor ground connection for CHANNEL A has been placed at right angles to the input trace, and away from the CHANNEL B input. The optimum geometry for input termination resistor ground connections will likely vary from design to design. Some empirical testing may be required.

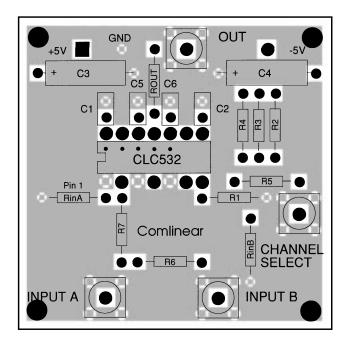

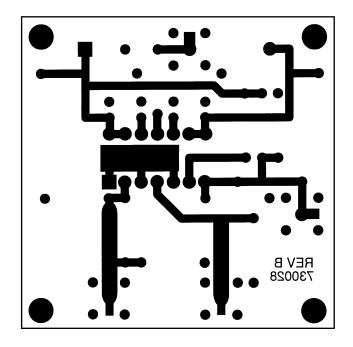

To achieve high-speed 14-bit settling accuracy, careful attention must be given to ground currents and the electrolytic power supply bypass capacitors. The ground connections of the electrolytic bypass capacitors must have a short and symmetric path to the ground connection of the CLC532 output load. In the case of the 730028 evaluation board, the output SMA connector provides the ground connection for the output load/return currents. Figures 11 and 12 illustrate the layout for the 730028 evaluation board.

The I/O connectors are SMA (straight) Amphenol 901-144 and SMA (right angled) Amphenol 901-143

The device thru holes are large enough to accommodate flush mount socket pins if socketing is desired. These should be-Cambion P/N 450-2598 or equivalent. Standard DIP sockets are specifically not recommended; the relatively long socket leads will severely degrade the ac performance of the CLC532.

Figure 11: 730028 Top Metal - Ground Plane (top view)

Figure 12: 730028 Bottom Metal (top view)

This page intentionally left blank.

## **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at 1-800-272-9959 or fax 1-800-737-7018.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **National Semiconductor** Corporation 1111 West Bardin Road

Arlington, TX 76017 Tel: 1(800) 272-9959

Fax: 1(800) 737-7018

# **National Semiconductor**

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32

Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

#### **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui. Kowloon Hong Kong

Tel: (852) 2737-1600 Fax: (852) 2736-9960

### **National Semiconductor** Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.